#### FAIRCHILD

SEMICONDUCTOR

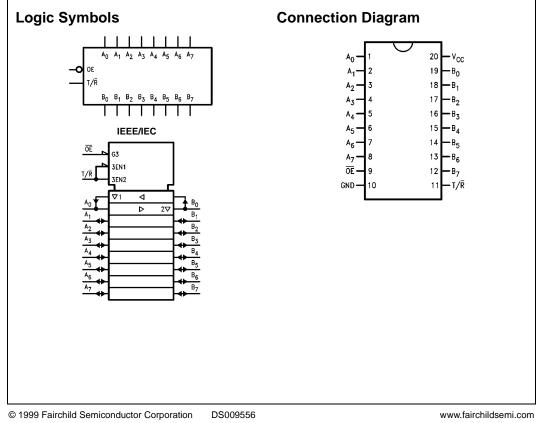

### 74F545 **Octal Bidirectional Transceiver with 3-STATE Outputs**

#### **General Description**

The 74F545 is an 8-bit, 3-STATE, high-speed transceiver. It provides bidirectional drive for bus-oriented microprocessor and digital communications systems. Straight through bidirectional transceivers are featured, with 24 mA bus drive capability on the A Ports and 64 mA bus drive capability on the B Ports.

One input, Transmit/Receive  $(T/\overline{R})$  determines the direction of logic signals through the bidirectional transceiver. Transmit enables data from A-to-B Ports; Receive enables data from B-to-A Ports. The Output Enable input disables both A and B Ports by placing them in a 3-STATE condition.

#### **Features**

- Higher drive than 8304

- 8-bit bidirectional data flow reduces system package count

April 1988

Revised August 1999

- 3-STATE inputs/outputs for interfacing with bus-oriented systems

- 24 mA and 64 mA bus drive capability on A and B Ports, respectively

- Transmit/Receive and Output Enable simplify control logic

- Guaranteed 4000V minimum ESD protection

#### **Ordering Code:**

| Order Number                                                                                           | der Number Package Number Package Description |                                                                           |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|

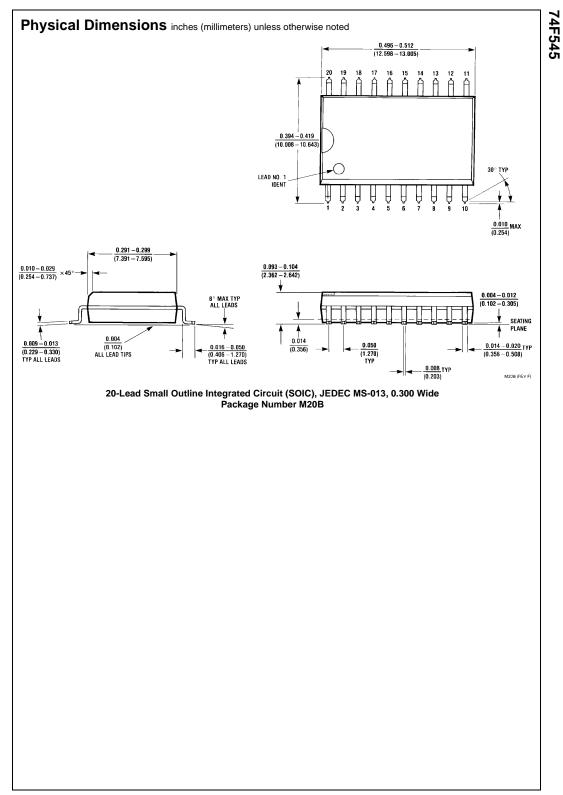

| 74F545SC                                                                                               | M20B                                          | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |  |  |  |  |  |

| 74F545PC                                                                                               | N20A                                          | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide     |  |  |  |  |  |

| Devises also subjects in Tana and Deal Creative by encoding the suffix latter "V" to the ordering code |                                               |                                                                           |  |  |  |  |  |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

## 74F545

#### Unit Loading/Fan Out

| Dia Managa                     | Description                      | U.L.           | Input I <sub>IH</sub> /I <sub>IL</sub>  |  |  |  |  |

|--------------------------------|----------------------------------|----------------|-----------------------------------------|--|--|--|--|

| Pin Names                      | Description                      | HIGH/LOW       | Output I <sub>OH</sub> /I <sub>OL</sub> |  |  |  |  |

| OE                             | Output Enable Input (Active LOW) | 1.0/2.0        | 20 μA/–1.2 mA                           |  |  |  |  |

| T/R                            | Transmit/Receive Input           | 1.0/2.0        | 20 μA/–1.2 mA                           |  |  |  |  |

| A <sub>0</sub> -A <sub>7</sub> | Side A 3-STATE Inputs or         | 3.5/1.083      | 70 μA/–650 μA                           |  |  |  |  |

|                                | 3-STATE Outputs                  | 150/40 (33.3)  | –3 mA/24 mA (20 mA)                     |  |  |  |  |

| B <sub>0</sub> -B <sub>7</sub> | Side B 3-STATE Inputs or         | 3.5/1.083      | 70 μA/–650 μA                           |  |  |  |  |

|                                | 3-STATE Outputs                  | 600/106.6 (80) | –12 mA/64 mA (48 mA)                    |  |  |  |  |

#### **Truth Table**

| Inp | uts | Outputs             |

|-----|-----|---------------------|

| OE  | T/R |                     |

| L   | L   | Bus B Data to Bus A |

| L   | Н   | Bus A Data to Bus B |

| Н   | Х   | High Z              |

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial

Z = High Impedance

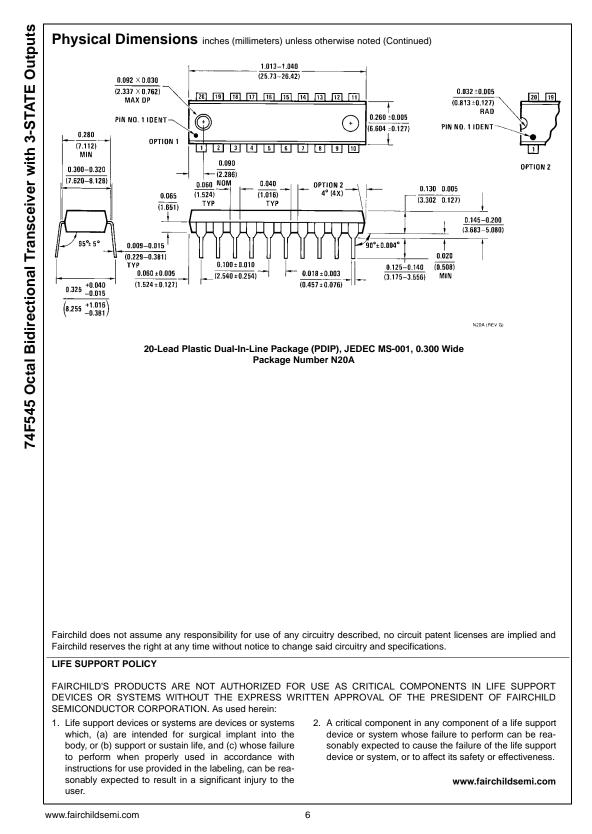

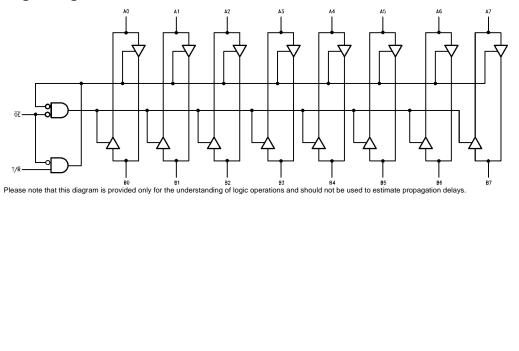

#### Logic Diagram

www.fairchildsemi.com

2

#### Absolute Maximum Ratings(Note 1)

|                                      | •                                    |

|--------------------------------------|--------------------------------------|

| Storage Temperature                  | -65°C to +150°C                      |

| Ambient Temperature under Bias       | $-55^{\circ}C$ to $+125^{\circ}C$    |

| Junction Temperature under Bias      | -55°C to +150C                       |

| $V_{CC}$ Pin Potential to Ground Pin | -0.5V to +7.0V                       |

| Input Voltage (Note 2)               | -0.5V to +7.0V                       |

| Input Current (Note 2)               | -30 mA to +5.0 mA                    |

| Voltage Applied to Output            |                                      |

| in HIGH State (with $V_{CC} = 0V$ )  |                                      |

| Standard Output                      | –0.5V to V <sub>CC</sub>             |

| 3-STATE Output                       | -0.5V to +5.5V                       |

| Current Applied to Output            |                                      |

| in LOW State (Max)                   | twice the rated I <sub>OL</sub> (mA) |

| ESD Last Passing Voltage (Min)       | 4000V                                |

|                                      |                                      |

### Recommended Operating Conditions

Free Air Ambient Temperature Supply Voltage 74F545

$0^{\circ}C$  to  $+70^{\circ}C$

+4.5V to +5.5V

ote 1: Absolute maximum ratings are values beyond which the devi

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

#### **DC Electrical Characteristics**

| Symbol                             | Parameter                   |                     | Min  | Тур | Max  | Units | V <sub>cc</sub> | Conditions                                                |  |

|------------------------------------|-----------------------------|---------------------|------|-----|------|-------|-----------------|-----------------------------------------------------------|--|

| VIH                                | Input HIGH Voltage          |                     | 2.0  |     |      | V     |                 | Recognized as a HIGH Signa                                |  |

| V <sub>IL</sub>                    | Input LOW Voltage           |                     |      |     | 0.8  | V     |                 | Recognized as a LOW Signal                                |  |

| V <sub>CD</sub>                    | Input Clamp Diode Voltage   |                     |      |     | -1.2 | V     | Min             | $I_{IN} = -18 \text{ mA} (\overline{OE}, T/\overline{R})$ |  |

| V <sub>OH</sub>                    | Output HIGH                 | 10% V <sub>CC</sub> | 2.5  |     |      |       |                 | $I_{OH} = -1 \text{ mA} (A_n)$                            |  |

|                                    | Voltage                     | 10% V <sub>CC</sub> | 2.4  |     |      |       |                 | $I_{OH} = -3 \text{ mA} (A_n)$                            |  |

|                                    |                             | 10% V <sub>CC</sub> | 2.0  |     |      | V     | Min             | $I_{OH} = -15 \text{ mA} (B_n)$                           |  |

|                                    |                             | 5% $V_{CC}$         | 2.7  |     |      |       |                 | $I_{OH} = -1 \text{ mA} (A_n)$                            |  |

|                                    |                             | 5% $V_{CC}$         | 2.7  |     |      |       |                 | $I_{OH} = -3 \text{ mA} (A_n)$                            |  |

| V <sub>OL</sub>                    | Output LOW                  | 10% V <sub>CC</sub> |      |     | 0.5  | V     | Min             | I <sub>OL</sub> = 24 mA (A <sub>n</sub> )                 |  |

|                                    | Voltage                     | 10% V <sub>CC</sub> |      |     | 0.55 | v     | IVIIII          | I <sub>OL</sub> = 64 mA (B <sub>n</sub> )                 |  |

| IIH                                | Input HIGH                  |                     |      |     | 5.0  | μA    | Max             | $V_{IN} = 2.7V (\overline{OE}, T/\overline{R})$           |  |

|                                    | Current                     |                     |      |     |      |       |                 | TIN 2.14 (OE, 1/14)                                       |  |

| I <sub>BVI</sub>                   | Input HIGH Current          |                     |      |     | 7.0  | μA    | Max             | $V_{IN} = 7.0V (\overline{OE}, T/\overline{R})$           |  |

|                                    | Breakdown Test              |                     |      |     | 7.0  | μι    | Max             | VIN - 7.00 (OE, 1710)                                     |  |

| I <sub>BVIT</sub>                  | Input HIGH Current          | •                   |      |     | 0.5  | mA    | Max             | $V_{IN} = 5.5V (A_n, B_n)$                                |  |

|                                    | Breakdown (I/O)             |                     |      |     | 0.0  | 110 ( | Max             | $v_{\rm IN} = 0.0 v_{\rm (} v_{\rm n}, D_{\rm n})$        |  |

| I <sub>CEX</sub>                   | Output HIGH                 |                     |      |     | 50   | μA    | Max             | $V_{OUT} = V_{CC}$                                        |  |

|                                    | Leakage Current             |                     |      |     |      | μι    | max             |                                                           |  |

| V <sub>ID</sub>                    | Input Leakage               |                     | 4.75 |     |      | V     | 0.0             | I <sub>ID</sub> = 1.9 μA                                  |  |

|                                    | Test                        |                     |      |     |      | -     |                 | All Other Pins Grounded                                   |  |

| l <sub>OD</sub>                    | Output Leakage              |                     |      |     | 3.75 | μA    | 0.0             | $V_{IOD} = 150 \text{ mV}$                                |  |

|                                    | Circuit Current             |                     |      |     | 0.70 | μι    | 0.0             | All Other Pins Grounded                                   |  |

| IIL                                | Input LOW Current           |                     |      |     | -1.2 | mA    | Max             | $V_{IN} = 0.5V \ (\overline{OE}, \ T/R)$                  |  |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Current      |                     |      |     | 70   | μΑ    | Max             | $V_{OUT} = 2.7V (A_n, B_n)$                               |  |

| I <sub>IL</sub> + I <sub>OZL</sub> | Output Leakage Current      |                     |      |     | -650 | μΑ    | Max             | $V_{OUT} = 0.5V (A_n, B_n)$                               |  |

| l <sub>os</sub>                    | Output Short-Circuit Curren | nt                  | -60  |     | -150 | mA    | Max             | $V_{OUT} = 0V (A_n)$                                      |  |

|                                    |                             |                     | -100 |     | -225 | 110 ( | Max             | $V_{OUT} = 0V (B_n)$                                      |  |

| I <sub>zz</sub>                    | Bus Drainage Test           |                     |      |     | 500  | μΑ    | 0.0V            | $V_{OUT} = 5.25V$                                         |  |

| I <sub>ССН</sub>                   | Power Supply Current        |                     |      | 70  | 90   | mA    | Max             | V <sub>O</sub> = HIGH                                     |  |

| I <sub>CCL</sub>                   | Power Supply Current        |                     |      | 95  | 120  | mA    | Max             | $V_0 = LOW$                                               |  |

| I <sub>CCZ</sub>                   | Power Supply Current        |                     |      | 85  | 110  | mA    | Max             | V <sub>O</sub> = HIGH Z                                   |  |

# 74F545

#### **AC Electrical Characteristics**

| Symbol           | Parameter                                                            |     | $T_{A} = +25^{\circ}C$<br>$V_{CC} = +5.0V$<br>$C_{L} = 50 \text{ pF}$ |     |     | $T_A = -55^{\circ}C \text{ to } +125^{\circ}C$ $V_{CC} = +5.0V$ $C_L = 50 \text{ pF}$ |     | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$<br>$V_{CC} = +5.0V$<br>$C_L = 50 \text{ pF}$ |    |

|------------------|----------------------------------------------------------------------|-----|-----------------------------------------------------------------------|-----|-----|---------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------|----|

|                  |                                                                      | Min | Тур                                                                   | Max | Min | Max                                                                                   | Min | Max                                                                                      |    |

| t <sub>PLH</sub> | Propagation Delay                                                    | 2.5 | 4.2                                                                   | 6.0 | 2.0 | 7.5                                                                                   | 2.5 | 7.0                                                                                      | ns |

| t <sub>PHL</sub> | A <sub>n</sub> to B <sub>n</sub> or B <sub>n</sub> to A <sub>n</sub> | 2.5 | 4.6                                                                   | 6.0 | 2.0 | 7.5                                                                                   | 2.5 | 7.0                                                                                      |    |

| t <sub>PZH</sub> | Output Enable Time                                                   | 3.0 | 5.3                                                                   | 7.0 | 2.5 | 9.0                                                                                   | 3.0 | 8.0                                                                                      |    |

| t <sub>PZL</sub> |                                                                      | 3.5 | 6.0                                                                   | 8.0 | 3.0 | 10.0                                                                                  | 3.5 | 9.0                                                                                      |    |

| t <sub>PHZ</sub> | Output Disable Time                                                  | 3.0 | 5.0                                                                   | 6.5 | 2.5 | 9.0                                                                                   | 3.0 | 7.5                                                                                      | ns |

| t <sub>PLZ</sub> |                                                                      | 2.0 | 5.0                                                                   | 6.5 | 2.0 | 10.0                                                                                  | 2.0 | 7.5                                                                                      |    |

www.fairchildsemi.com

5