### LM4985 Boomer® Audio Power Amplifier Series

# Stereo 135mW Low Noise Headphone Amplifier with Selectable Capacitively Coupled or Output Capacitor-less (OCL) Output and Digitally Controlled (I<sup>2</sup>C) Volume Control

### **General Description**

The LM4985 is a stereo audio power amplifier with internal digitally controlled volume control. This amplifier is capable of delivering  $68mW_{RMS}$  per channel into a  $16\Omega$  load or  $38mW_{RMS}$  per channel into a  $32\Omega$  load at 1% THD when powered by a 3.6V power supply and operating in the OCL mode.

Boomer audio power amplifiers were designed specifically to provide high quality output power with a minimal amount of external components. To that end, the LM4985 features two functions that optimize system cost and minimize PCB area: an integrated, digitally controlled (I²C bus) volume control and an operational mode that eliminates output signal coupling capacitors (OCL mode). Since the LM4985 does not require bootstrap capacitors, snubber networks, or output coupling capacitors, it is optimally suited for low-power, battery powered portable systems. For added design flexibility, the LM4985 can also be configured for single-ended capacitively coupled outputs.

The LM4985 features a current shutdown mode for micropower dissipation and thermal shutdown protection.

### Key Specifications ( $V_{DD} = 3.6V$ )

■ PSRR: 217Hz and 1kHz

Output Capacitor-less (OCL)

| f <sub>RIPPLE</sub> = 217Hz | 77dB (typ) |

|-----------------------------|------------|

| f <sub>RIPPLE</sub> = 1kHz  | 76dB (typ) |

| Capacitor Coupled (C-CUPL)  |            |

|                             | 00 ID (I ) |

$f_{RIPPLE} = 217Hz$  63dB (typ)  $f_{RIPPLE} = 1kHz$  62dB (typ)

Output Power per channel

$(f_{IN} = 1kHz, THD+N = 1\%),$  $R_{I} = 16\Omega,OCL$

$V_{DD} = 2.5V$  31mW (typ)  $V_{DD} = 3.6V$  68mW (typ)  $V_{DD} = 5.0V$  135mW (typ)

■ THD+N (f = 1kHz)

$$\begin{split} R_{LOAD} &= 16\Omega, \ OCL, \ P_{OUT} = 60 mW \\ R_{LOAD} &= 32\Omega, \ OCL, \ P_{OUT} = 33 mW \end{split} \tag{0.60}$$

■ Shutdown Current 0.1µA (typ)

#### **Features**

- OCL or capacitively coupled outputs (patent pending)

- I<sup>2</sup>C Digitally Controlled Volume Control

- Available in space-saving 0.4mm lead-pitch micro SMD package

- Volume control range: -76dB to +18dB

- Ultra low current shutdown mode

- 2.3V 5.5V operation

- Ultra low noise

### **Applications**

- Mobile Phones

- PDAs

- Portable electronics devices

- MP3 Players

Boomer® is a registered trademark of National Semiconductor Corporation.

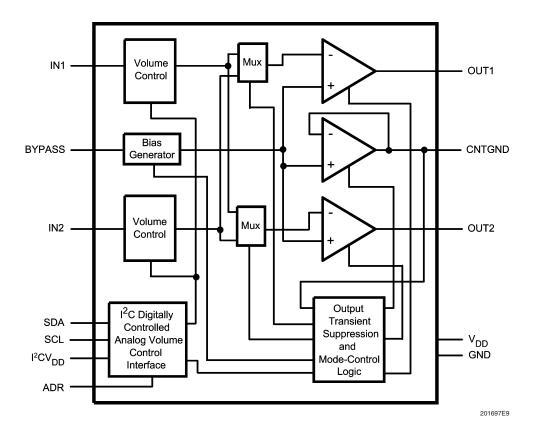

### **Block Diagram**

FIGURE 1. Block Diagram

2

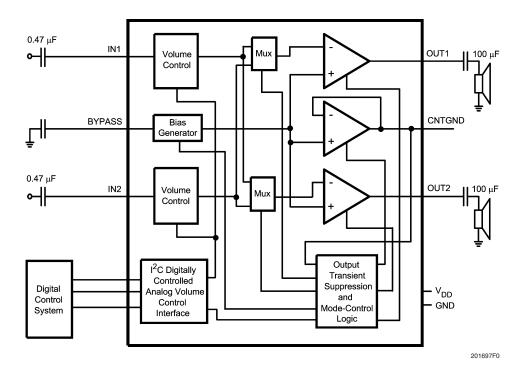

### **Typical Application**

FIGURE 2. Typical Capacitively Coupled Output Configuration Circuit

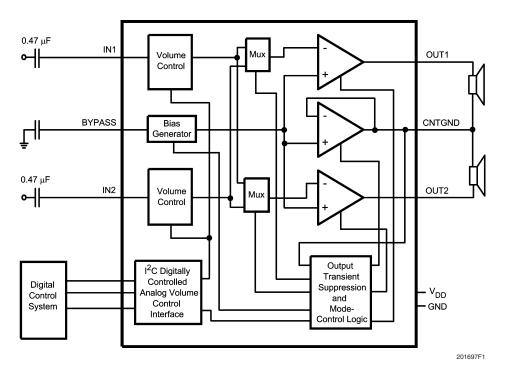

FIGURE 3. Typical OCL Output Configuration Circuit

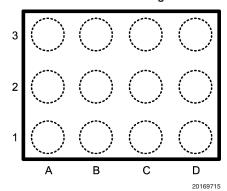

### **Connection Diagrams**

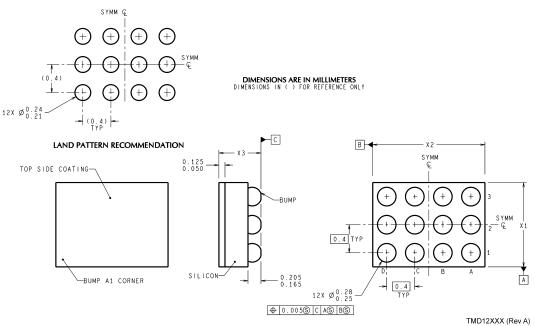

#### micro SMD Package

Top View Order Number LM4985TM See NS Package Number TMD12AAA

#### micro SMD Marking

20169730

Top View

X - Date Code

T - Die Traceability

G - Boomer Family

H2 - LM4985TM

#### Pin Reference, Name, and Function

| Reference | Name                            | Function                                                                                                                                |

|-----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| A1        | ADR                             | I <sup>2</sup> C serial interface address input.                                                                                        |

| A2        | IN2                             | Analog signal input two.                                                                                                                |

| A3        | OUT2                            | Power amplifier two output.                                                                                                             |

| B1        | SDA                             | I <sup>2</sup> C serial interface data input.                                                                                           |

| B2        | BYPASS                          | The internal V <sub>DD</sub> /2 ac bypass node.                                                                                         |

| В3        | CNTGND                          | In OCL mode, this is the ac ground return. It is biased to $V_{\rm DD}/2$ . Leave unconnected for C-CUPL mode.                          |

| C1        | SCL                             | I2C serial interface clock input.                                                                                                       |

| C2        | GND                             | The LM4985's power supply ground input.                                                                                                 |

| C3        | $V_{DD}$                        | The LM4985's power supply voltage input.                                                                                                |

| D1        | I <sup>2</sup> CV <sub>DD</sub> | I <sup>2</sup> C serial interface power supply input. Can be connected to the same supply that is connected to the V <sub>DD</sub> pin. |

| D2        | IN1                             | Analog signal input one.                                                                                                                |

| D3        | OUT1                            | Power amplifier one output.                                                                                                             |

### Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{DD}$ ,  $I^2CV_{DD}$ ) 6.0V Storage Temperature -65°C to +150°C Input Voltage (IN1, IN2, OUT1, OUT2, BYPASS, CNTGND, GND

pins relative to the  $V_{DD}$  pin) -0.3V to  $V_{DD}$  + 0.3V

Input Voltage (ADR, SDA, SCL

pins, relative to the  $I^2CV_{DD}$  pin) -0.3V to  $I^2CV_{DD} + 0.3V$ Power Dissipation (Note 3) Internally Limited ESD Susceptibility (Note 4) 2000V ESD Susceptibility (Note 5) 200V

Junction Temperature 150°C

Thermal Resistance

109°C/W

### **Operating Ratings**

Temperature Range

$T_{MIN} \le T_A \le T_{MAX}$   $-40^{\circ}C \le T_A \le 85^{\circ}C$

Supply Voltage

$\theta_{\mathsf{JA}}$

$$\begin{split} V_{DD} & 2.3V \leq V_{CC} \leq 5.5V \\ I^2CV_{DD} & 1.7V \leq I^2CV_{DD} \leq 5.5V \end{split}$$

### Electrical Characteristics $V_{DD} = 5V$ (Notes 1, 2)

The following specifications apply for  $R_L = 16\Omega$ , f = 1 kHz, and  $C_B = 4.7 \mu \text{F}$  unless otherwise specified. Limits apply to  $T_A = 25 \,^{\circ}\text{C}$ .

| Symbol            | Parameter                         | Conditions                                                                                                                                                                                                                                                       | LM                           | Units                    |          |

|-------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------|----------|

|                   |                                   |                                                                                                                                                                                                                                                                  | Typ<br>(Note 6)              | Limit<br>(Notes 7,<br>8) | (Limits) |

| I <sub>DD</sub>   | Quiescent Power Supply Current    | V <sub>IN</sub> = 0V, I <sub>OUT</sub> = 0A Single-Channel no load OCL Single-Channel no load C-CUPL Dual-Channel no load OCL Dual-Channel no load C-CUPL                                                                                                        | 2<br>1.5<br>3<br>2.3         | 4.9<br>3.8               | mA (max) |

| I <sub>SD</sub>   | Shutdown Current                  | V <sub>SHUTDOWN</sub> = GND                                                                                                                                                                                                                                      | 0.1                          | 1.0                      | μΑ (max) |

| V <sub>SDIH</sub> | Logic Voltage Input High          | - SHOTDOWN                                                                                                                                                                                                                                                       |                              | 3.5                      | V (min)  |

| V <sub>SDIL</sub> | Logic Voltage Input Low           |                                                                                                                                                                                                                                                                  |                              | 1.5                      | V (max)  |

| P <sub>o</sub>    | Output Power                      | THD $\leq$ 1%; f <sub>IN</sub> = 1kHz<br>R <sub>LOAD</sub> = 16 $\Omega$ OCL<br>R <sub>LOAD</sub> = 16 $\Omega$ C-CUPL<br>R <sub>LOAD</sub> = 32 $\Omega$ OCL<br>R <sub>LOAD</sub> = 32 $\Omega$ C-CUPL                                                          | 135<br>135<br>79<br>80       | 115<br>70                | mW (min) |

| THD+N             | Total Harmonic Distortion + Noise | $\begin{split} R_{LOAD} &= 16\Omega \text{ OCL, } P_O = 100\text{mW} \\ R_{LOAD} &= 16\Omega \text{ C-CUPL, } P_O = 100\text{mW} \\ R_{LOAD} &= 32\Omega \text{ OCL, } P_O = 60\text{mW} \\ R_{LOAD} &= 32\Omega \text{ C-CUPL, } P_O = 70\text{mW} \end{split}$ | 0.08<br>0.02<br>0.04<br>0.01 |                          | %        |

| V <sub>ON</sub>   | Output Noise Voltage              | $V_{IN} = AC GND, A_{V} = 0dB, A-weighted$                                                                                                                                                                                                                       | 15                           |                          | μV       |

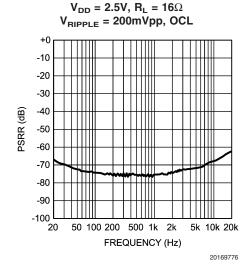

| PSRR              | Power Supply Rejection Ratio      | V <sub>RIPPLE</sub> = 200mVp-p (Note 9)<br>f <sub>IN</sub> = 217Hz sinewave<br>OCL<br>C-CUPL                                                                                                                                                                     | 77<br>65                     | 57                       | dB (min) |

|                   |                                   | f <sub>IN</sub> = 1kHz sinewave<br>OCL<br>C-CUPL                                                                                                                                                                                                                 | 77<br>65                     | 60                       |          |

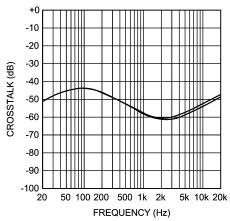

| Xtalk             | Channel-to-channel Crosstalk      | $\begin{aligned} & P_{out} = 40 \text{mW. OCL} \\ & R_{LOAD} = 16 \Omega \\ & R_{LOAD} = 32 \Omega \\ & P_{out} = 50 \text{mW. C-CUPL} \\ & R_{LOAD} = 16 \Omega \end{aligned}$                                                                                  | 51<br>56<br>58               |                          | dB<br>dB |

**Electrical Characteristics V\_{DD} = 5V** (Notes 1, 2) (Continued) The following specifications apply for  $R_L = 16\Omega$ , f = 1kHz, and  $C_B = 4.7\mu F$  unless otherwise specified. Limits apply to  $T_A = 25^{\circ}C$ .

| Symbol            | Parameter                  | Conditions                            | LM       | LM4985    |                  |  |

|-------------------|----------------------------|---------------------------------------|----------|-----------|------------------|--|

|                   |                            |                                       | Тур      | Limit     | (Limits)         |  |

|                   |                            |                                       | (Note 6) | (Notes 7, |                  |  |

|                   |                            |                                       |          | 8)        |                  |  |

|                   |                            | C <sub>BYPASS</sub> = 4.7µF (Note 11) | ·        |           |                  |  |

|                   |                            | WT1 = 0, WT0 = 0                      |          |           |                  |  |

|                   |                            | OCL                                   | 75       |           |                  |  |

|                   |                            | C-CUPL                                | 285      |           |                  |  |

|                   |                            | WT1 = 0, WT0 = 1                      |          |           |                  |  |

|                   |                            | OCL                                   | 110      |           |                  |  |

| $T_{WU}$          | Wake Up Time form Shutdown | C-CUPL                                | 530      |           |                  |  |

|                   |                            | WT1 = 1, WT0 = 0                      |          |           | - msec           |  |

|                   |                            | OCL                                   | 180      |           |                  |  |

|                   |                            | C-CUPL                                | 1030     |           |                  |  |

|                   |                            | WT1 = 1, WT0 = 1                      |          |           |                  |  |

|                   |                            | OCL                                   | 320      |           |                  |  |

|                   |                            | C-CUPL                                | 2050     |           |                  |  |

|                   | Innut Desistance           | Stereo mode                           | 20       |           | l <sub>1</sub> O |  |

| $R_{IN}$          | Input Resistance           | Mono mode                             | 10       |           | kΩ               |  |

| A <sub>VMIN</sub> | Minimum Gain               | Code = 00000                          | -76      |           | dB (min)         |  |

| A <sub>VMAX</sub> | Maximum Gain               | Code = 11111                          | 18       |           | dB (min)         |  |

| $\Delta A_V$      | Online Annual and Others   | $18dB \ge A_V \ge -44dB$              | ±0.5     |           | -ID              |  |

|                   | Gain Accuracy per Step     | $-44dB \ge A_V \ge -76dB$             | ±1.0     |           | dB               |  |

|                   |                            | OCL                                   |          |           |                  |  |

| $V_{OS}$          | Output Offset Voltage      | $R_{LOAD} = 32\Omega$                 | 2.0      | 20        | mV (max)         |  |

|                   |                            | V <sub>IN</sub> = AC GND              |          |           |                  |  |

**Electrical Characteristics V\_{DD}=3.6V** (Notes 1, 2) The following specifications apply for  $R_L=16\Omega$ , f = 1kHz, and  $C_B=4.7\mu F$  unless otherwise specified. Limits apply to  $T_A=25^{\circ}C$ .

| Symbol            | Parameter                      | Conditions                           | LM <sup>2</sup> | LM4985    |               |  |

|-------------------|--------------------------------|--------------------------------------|-----------------|-----------|---------------|--|

|                   |                                |                                      | Тур             | Limit     | (Limits)      |  |

|                   |                                |                                      | (Note 6)        | (Notes 7, |               |  |

|                   |                                |                                      |                 | 8)        |               |  |

|                   |                                | $V_{IN} = 0V, I_{OUT} = 0A$          |                 |           |               |  |

|                   |                                | Single-Channel no load OCL           | 1.8             | 3.1       |               |  |

| $I_{DD}$          | Quiescent Power Supply Current | Single-Channel no load C-CUPL        | 1.0             |           | ma Λ (ma αν.) |  |

|                   |                                | Dual-Channel no load OCL             | 2.1             | 4         | mA (max)      |  |

|                   |                                | Dual-Channel no load C-CUPL          | 2.3             | 3         |               |  |

| I <sub>SD</sub>   | Shutdown Current               | V <sub>SHUTDOWN</sub> = GND          | 0.1             | 1.0       | μA (max)      |  |

| V <sub>SDIH</sub> | Logic Voltage Input High       |                                      |                 | 2.52      | V (min)       |  |

| V <sub>SDIL</sub> | Logic Voltage Input Low        |                                      |                 | 1.08      | V (max)       |  |

|                   |                                | THD+N < 1%, $f_{IN} = 1kHz$          |                 |           |               |  |

|                   |                                | $R_{LOAD} = 16\Omega OCL$            | 68              | 60        |               |  |

| $P_{O}$           | Output Power                   | $R_{LOAD} = 16\Omega \text{ C-CUPL}$ | 70              |           | mW (min)      |  |

|                   |                                | $R_{LOAD} = 32\Omega \text{ OCL}$    | 38              | 34        |               |  |

|                   |                                | $R_{LOAD} = 32\Omega \text{ C-CUPL}$ | 41              |           |               |  |

**Electrical Characteristics V**<sub>DD</sub> = **3.6V** (Notes 1, 2) (Continued) The following specifications apply for R<sub>L</sub> =  $16\Omega$ , f = 1kHz, and C<sub>B</sub> =  $4.7\mu F$  unless otherwise specified. Limits apply to T<sub>A</sub> =  $25^{\circ}C$ .

| Symbol                                    | Parameter                    | Conditions                                                                                                                                                                                                                                           | LM <sup>2</sup>                        | Units                    |          |

|-------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------|----------|

|                                           |                              |                                                                                                                                                                                                                                                      | Typ<br>(Note 6)                        | Limit<br>(Notes 7,<br>8) | (Limits) |

| THD+N Total Harmonic Distortion + Noise R |                              | $\begin{aligned} &R_{LOAD} = 16\Omega \; OCL, \; P_{O} = 60 mW \\ &R_{LOAD} = 16\Omega \; C\text{-CUPL}, \; P_{O} = 60 mW \\ &R_{LOAD} = 32\Omega \; OCL, \; P_{O} = 33 mW \\ &R_{LOAD} = 32\Omega \; C\text{-CUPL}, \; P_{O} = 38 mW \end{aligned}$ | 0.06<br>0.03<br>0.03<br>0.03           |                          | %        |

| V <sub>ON</sub>                           | Output Noise Voltage         | V <sub>IN</sub> = AC GND, A <sub>V</sub> = 0dB, A-weighted                                                                                                                                                                                           | 15                                     |                          | μV       |

| PSRR                                      | Power Supply Rejection Ratio | $V_{\text{RIPPLE}}$ = 200mVp-p (Note 9)<br>$f_{\text{IN}}$ = 217Hz sinewave<br>OCL<br>C-CUPL<br>$f_{\text{IN}}$ = 1kHz sinewave<br>OCL<br>C-CUPL                                                                                                     | 77<br>63<br>76<br>62                   | 55<br>57                 | dB (min) |

| Xtalk                                     | Channel-to-Channel Crosstalk | $P_{out}$ = 40mW. OCL $R_{LOAD}$ = 16 $\Omega$ $R_{LOAD}$ = 32 $\Omega$ $P_{out}$ = 50mW. C-CUPL                                                                                                                                                     | 51<br>56                               |                          | dB       |

|                                           |                              | $R_{LOAD} = 16\Omega$<br>$R_{LOAD} = 32\Omega$                                                                                                                                                                                                       | 58<br>69                               |                          | dB       |

| Twu                                       | Wake Up Time from Shutdown   | C <sub>BYPASS</sub> = 4.7µF (Note 11)  WT1 = 0, WT0 = 0  OCL C-CUPL  WT1 = 0, WT0 = 1  OCL C-CUPL  WT1 = 1, WT0 = 0  OCL C-CUPL  WT1 = 1, WT0 = 1  OCL C-CUPL  WT1 = 1, WT0 = 1  OCL C-CUPL                                                          | 92<br>405<br>143<br>774<br>246<br>1532 | 93                       | msec     |

| R <sub>IN</sub>                           | Input Resistance             | Stereo mode<br>Mono mode                                                                                                                                                                                                                             | 20<br>10                               |                          | kΩ       |

| A <sub>VMIN</sub>                         | Minimum Gain                 | Code = 00000                                                                                                                                                                                                                                         | -76                                    | -72                      | dB (max) |

| A <sub>VMAX</sub>                         | Maximum Gain                 | Code = 11111                                                                                                                                                                                                                                         | 18                                     | 17                       | dB (min) |

| $\Delta A_V$                              | Gain Accuracy per Step       | $18dB \ge A_V \ge -44dB$ $-44dB \ge A_V \ge -76dB$                                                                                                                                                                                                   | ± 0.5<br>± 1.0                         | ± 1.0<br>± 2.0           | dB       |

| V <sub>OS</sub>                           | Output Offset Voltage        | OCL $R_{LOAD} = 32\Omega$ $V_{IN} = AC GND$                                                                                                                                                                                                          | 2.0                                    | 20                       | mV (max) |

**Electrical Characteristics V\_{DD} = 2.5V (Notes 1, 2)** The following specifications apply for R<sub>L</sub> = 16Ω, f = 1kHz, and C<sub>B</sub> = 4.7μF unless otherwise specified. Limits apply to T<sub>A</sub> = 25°C.

| Symbol                                                             | Parameter                         | Conditions                                                                                                                                                                                                                             | LM <sup>2</sup>              | Units                    |          |  |

|--------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------|----------|--|

|                                                                    |                                   |                                                                                                                                                                                                                                        | Typ<br>(Note 6)              | Limit<br>(Notes 7,<br>8) | (Limits) |  |

| I <sub>DD</sub> Quiescent Power Supply Current Single-I<br>Dual-Ci |                                   | V <sub>IN</sub> = 0V, I <sub>OUT</sub> = 0A Single-Channel no load OCL Single-Channel no load C-CUPL Dual-Channel no load OCL Dual-Channel no load C-CUPL                                                                              | 1.6<br>1<br>2.1<br>1.6       |                          | mA       |  |

| I <sub>SD</sub>                                                    | Shutdown Current                  | V <sub>SHUTDOWN</sub> = GND                                                                                                                                                                                                            | 0.1                          |                          | μA       |  |

| V <sub>SDIH</sub>                                                  | Logic Voltage Input High          |                                                                                                                                                                                                                                        |                              | 1.75                     | V (min)  |  |

| V <sub>SDIL</sub>                                                  | Logic Voltage Input Low           |                                                                                                                                                                                                                                        |                              | 0.75                     | V (max)  |  |

| P <sub>o</sub>                                                     | Output Power                      | $THD+N < 1\%, f_{IN} = 1kHz$ $R_{LOAD} = 16\Omega \text{ OCL}$ $R_{LOAD} = 16\Omega \text{ C-CUPL}$ $R_{LOAD} = 32\Omega \text{ OCL}$ $R_{LOAD} = 32\Omega \text{ C-CUPL}$                                                             | 31<br>33<br>19<br>19         |                          | mW       |  |

| THD+N                                                              | Total Harmonic Distortion + Noise | $\begin{aligned} &R_{LOAD} = 16\Omega \; OCL, \; P_{O} = 26 mW \\ &R_{LOAD} = 16\Omega \; C-CUPL, \; P_{O} = 20 mW \\ &R_{LOAD} = 32\Omega \; OCL, \; P_{O} = 16 mW \\ &R_{LOAD} = 32\Omega \; C-CUPL, \; P_{O} = 15 mW \end{aligned}$ | 0.07<br>0.05<br>0.06<br>0.04 |                          | %        |  |

| $V_{ON}$                                                           | Output Noise Voltage              | $V_{IN}$ = AC GND, $A_V$ = 0dB, A-weighted                                                                                                                                                                                             | 10                           |                          | μV       |  |

| PSRR                                                               | Power Supply Rejection Ratio      | f <sub>IN</sub> = 217Hz sinewave OCL C-CUPL f <sub>IN</sub> = 1kHz sinewave OCL C-CUPL                                                                                                                                                 | 75<br>59<br>75<br>59         |                          | dB       |  |

| Xtalk                                                              | Channel-to-Channel Crosstalk      | $\begin{aligned} & P_{out} = 20 \text{mW}, \text{ OCL} \\ & R_{LOAD} = 16 \Omega \\ & R_{LOAD} = 32 \Omega \\ & P_{out} = 20 \text{mW}. \text{ C-CUPL} \\ & R_{LOAD} = 16 \Omega \end{aligned}$                                        | 50<br>55<br>58               |                          | dB<br>dB |  |

|                                                                    |                                   | $R_{LOAD} = 32\Omega$                                                                                                                                                                                                                  | 67                           |                          |          |  |

| T <sub>wu</sub>                                                    | Wake Up Time from Shutdown        | C <sub>BYPASS</sub> = 4.7µF (Note 11)  WT1 = 0, WT0 = 0  OCL C-CUPL  WT1 = 0, WT0 = 1  OCL C-CUPL  WT1 = 1, WT0 = 0  OCL C-CUPL  WT1 = 1, WT0 = 1  OCL C-CUPL                                                                          | 92<br>544<br>145<br>1053     |                          | msec     |  |

| R <sub>IN</sub>                                                    | Input Resistance                  | C-CUPL Stereo mode Mono mode                                                                                                                                                                                                           | 2098<br>20<br>10             |                          | kΩ       |  |

| A <sub>VMIN</sub>                                                  | Minimum Gain                      | Code = 00000                                                                                                                                                                                                                           | -76                          | 1                        | dB       |  |

**Electrical Characteristics V\_{DD}=2.5V** (Notes 1, 2) (Continued) The following specifications apply for  $R_L=16\Omega$ , f = 1kHz, and  $C_B=4.7\mu F$  unless otherwise specified. Limits apply to  $T_A=160$  to  $T_A=160$

| Symbol            | Parameter               | Conditions               | LM4      | Units     |          |  |

|-------------------|-------------------------|--------------------------|----------|-----------|----------|--|

|                   |                         |                          | Тур      | Limit     | (Limits) |  |

|                   |                         |                          | (Note 6) | (Notes 7, |          |  |

|                   |                         |                          |          | 8)        |          |  |

| A <sub>VMAX</sub> | Maximum Gain            | Code = 11111             | 18       |           | dB       |  |

| $\Delta A_V$      | Gain Accuracy per Step  | $18dB \ge A_V \ge -44dB$ | ± 0.5    |           | dB       |  |

| ΔA <sub>V</sub>   | Gaill Accuracy per Step | $-44dB \ge A_V > -76dB$  | ± 1.0    |           | ub       |  |

|                   |                         | OCL                      |          |           |          |  |

| Vos               | Output Offset Voltage   | $R_{LOAD} = 32\Omega$    | 2.0      |           | mV       |  |

|                   |                         | V <sub>IN</sub> = AC GND |          |           |          |  |

Note 1: All voltages are measured with respect to the GND pin unless otherwise specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by TJMAX,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4985, see power derating currents for more information.

Note 4: Human Body Model: 100pF discharged through a 1.5k $\Omega$  resistor.

Note 5: Machine Model:  $200pF \le C_{mm} \le 220pF$  discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 9:  $10\Omega$  terminated input.

Note 10: The LDA10A package has its exposed-DAP soldered to an exposed 1.2in<sup>2</sup> area of 1oz. Printed circuit board copper.

Note 11: The wake-up time  $(T_{WU})$  is calculated using the following formula;  $T_{WU} = [C_{BYPASS} (VDD) / 2 (I_{BYPASS})] + 40 ms.$

### **External Components Description** (Figure 2)

| Comp | onents                                                           | Functional Description                                                                                                              |  |  |

|------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.   | Cı                                                               | Input coupling capacitor which blocks the DC voltage at the amplifier's input terminals. Also creates a                             |  |  |

|      |                                                                  | high-pass filter with $R_i$ at $f_c = 1/(2\pi R_i C_i)$ . Refer to the section <b>Proper Selection of External Components</b> , for |  |  |

|      | an explanation of how to determine the value of C <sub>i</sub> . |                                                                                                                                     |  |  |

| 2.   | Cs                                                               | Supply bypass capacitor which provides power supply filtering. Refer to the Power Supply Bypassing                                  |  |  |

|      |                                                                  | section for information concerning proper placement and selection of the supply bypass capacitor.                                   |  |  |

| 3.   | Св                                                               | Bypass pin capacitor which provides half-supply filtering. Refer to the section, Proper Selection of Proper                         |  |  |

|      |                                                                  | Components, for information concerning proper placement and selection of C <sub>B</sub>                                             |  |  |

| 6.   | C <sub>o</sub>                                                   | Output coupling capacitor which blocks the DC voltage at the amplifier's output. Forms a high pass filter with                      |  |  |

|      |                                                                  | $R_L$ at $f_o = 1/(2\pi R_L C_o)$                                                                                                   |  |  |

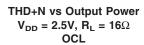

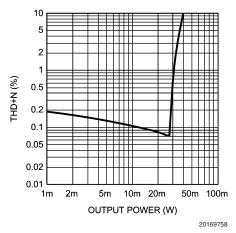

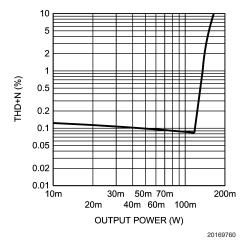

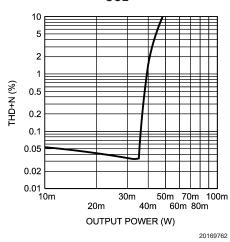

### **Typical Performance Characteristics**

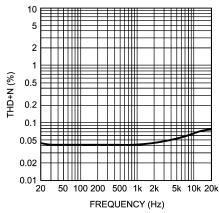

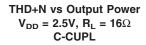

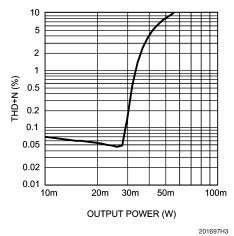

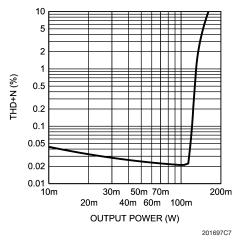

$T_A = 25$ °C,  $A_V = 0$ dB,  $f_{IN} = 1$ kHz unless otherwise stated.

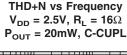

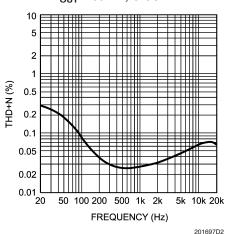

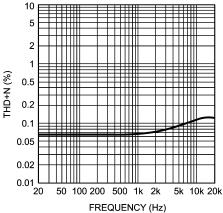

THD+N vs Frequency  $V_{DD}$  = 5V,  $R_L$  = 16 $\Omega$   $P_{OUT}$  = 50mW, C-CUPL

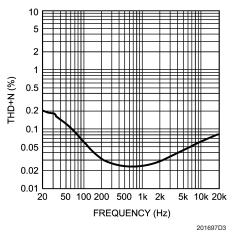

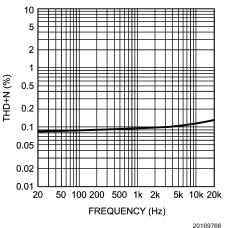

THD+N vs Frequency  $V_{DD}$  = 3.6V,  $R_L$  = 32 $\Omega$   $P_{OUT}$  = 35mW, C-CUPL

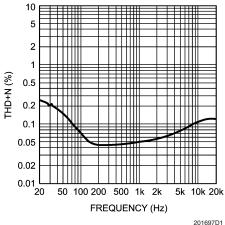

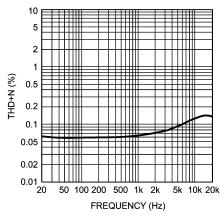

THD+N vs Frequency  $V_{DD}$  = 3.6V,  $R_{L}$  = 16 $\Omega$   $P_{OUT}$  = 50mW, C-CUPL

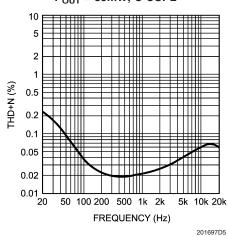

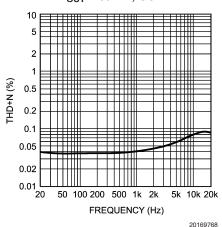

THD+N vs Frequency  $\begin{aligned} \text{V}_{\text{DD}} &= 2.5\text{V}, \, \text{R}_{\text{L}} = 32\Omega \\ \text{P}_{\text{OUT}} &= 15\text{mW}, \, \text{C-CUPL} \end{aligned}$

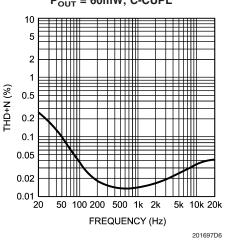

THD+N vs Frequency  $\begin{aligned} \text{V}_{\text{DD}} &= 5.0 \text{V}, \, \text{R}_{\text{L}} = 32 \Omega \\ \text{P}_{\text{OUT}} &= 60 \text{mW}, \, \text{C-CUPL} \end{aligned}$

20169764

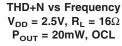

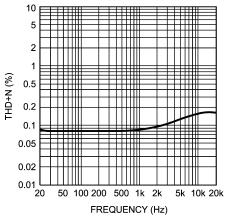

THD+N vs Frequency  $V_{DD} = 3.6V, R_{L} = 16\Omega$  $P_{OUT} = 50mW, OCL$

20169765

THD+N vs Frequency  $V_{DD} = 5.0V, R_L = 16\Omega$  $P_{OUT} = 50mW, OCL$

THD+N vs Frequency  $V_{DD} = 2.5V, R_{L} = 32\Omega$  $P_{OUT} = 15mW, OCL$

20169767

THD+N vs Frequency  $V_{DD} = 3.6V, R_{L} = 32\Omega$  $P_{OUT} = 35mW, OCL$

THD+N vs Frequency  $V_{DD} = 5.0V, R_{L} = 32\Omega$  $P_{OUT} = 60mW, OCL$

20169769

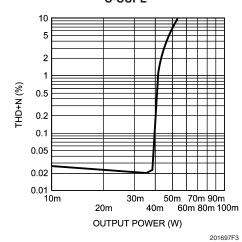

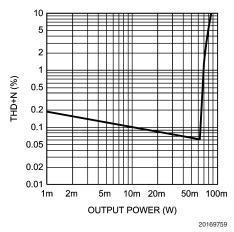

THD+N vs Output Power  $V_{DD}$  = 5.0V,  $R_{L}$  = 16 $\Omega$  C-CUPL

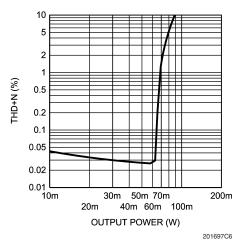

THD+N vs Output Power  $V_{DD}$  = 3.6V,  $R_{L}$  = 32 $\Omega$  C-CUPL

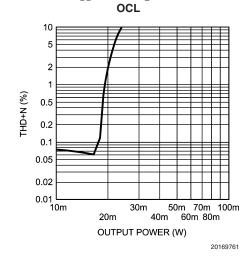

THD+N vs Output Power  $V_{DD}$  = 3.6V,  $R_L$  = 16 $\Omega$  C-CUPL

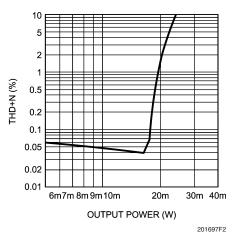

THD+N vs Output Power  $V_{DD}$  = 2.5V,  $R_L$  = 32 $\Omega$  C-CUPL

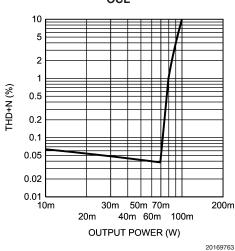

THD+N vs Output Power  $V_{DD}$  = 5.0V,  $R_L$  = 32 $\Omega$  C-CUPL

THD+N vs Output Power  $V_{DD}$  = 5.0V,  $R_{L}$  = 16 $\Omega$  OCL

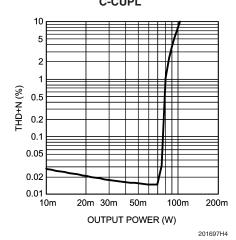

THD+N vs Output Power  $\label{eq:VDD} {\rm V_{DD}} = 3.6 {\rm V}, \, {\rm R_L} = 32 \Omega \\ {\rm OCL}$

THD+N vs Output Power  $V_{DD}$  = 3.6V,  $R_L$  = 16 $\Omega$  OCL

THD+N vs Output Power  $V_{DD} = 2.5V$ ,  $R_L = 32\Omega$

THD+N vs Output Power  $V_{DD}$  = 5.0V,  $R_L$  = 32 $\Omega$  OCL

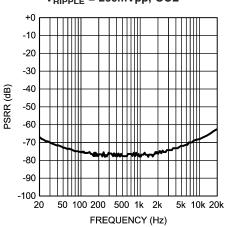

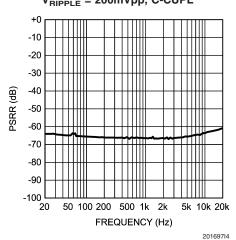

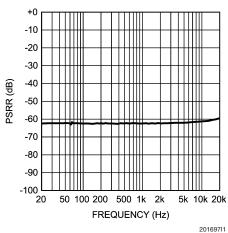

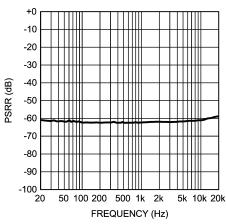

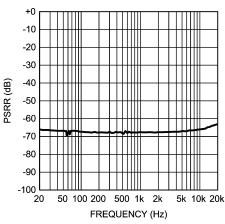

**PSRR vs Frequency**

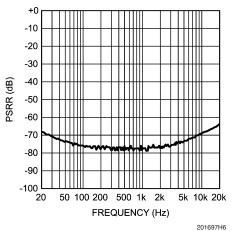

PSRR vs Frequency  $V_{DD}$  = 5.0V,  $R_{L}$  = 16 $\Omega$   $V_{RIPPLE}$  = 200mVpp, OCL

PSRR vs Frequency  $V_{DD}$  = 3.6V,  $R_L$  = 32 $\Omega$   $V_{RIPPLE}$  = 200mVpp, OCL

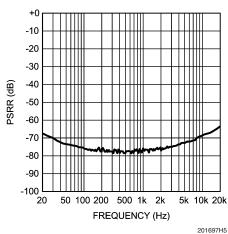

$\begin{aligned} & \text{PSRR vs Frequency} \\ & \text{V}_{\text{DD}} = 3.6 \text{V}, \, \text{R}_{\text{L}} = 16 \Omega \\ & \text{V}_{\text{RIPPLE}} = 200 \text{mVpp, OCL} \end{aligned}$

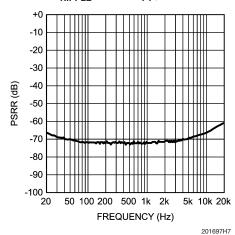

PSRR vs Frequency  $V_{DD}$  = 2.5V,  $R_{L}$  = 32 $\Omega$   $V_{RIPPLE}$  = 200mVpp, OCL

PSRR vs Frequency  $V_{DD}$  = 5.0V,  $R_L$  = 32 $\Omega$   $V_{RIPPLE}$  = 200mVpp, OCL

201697H9

PSRR vs Frequency  $\begin{aligned} \mathbf{V_{DD}} &= 5.0 \text{V}, \, \mathbf{R_L} = 16 \Omega \\ \mathbf{V_{RIPPLE}} &= 200 \text{mVpp, C-CUPL} \end{aligned}$

20169710

PSRR vs Frequency  $\begin{aligned} \mathbf{V_{DD}} &= 3.6 \text{V}, \, \mathbf{R_L} = 32 \Omega \\ \mathbf{V_{RIPPLE}} &= 200 \text{mVpp, C-CUPL} \end{aligned}$

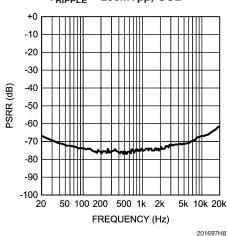

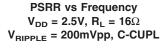

PSRR vs Frequency  $V_{DD}$  = 3.6V,  $R_L$  = 16 $\Omega$   $V_{RIPPLE}$  = 200mVpp, C-CUPL

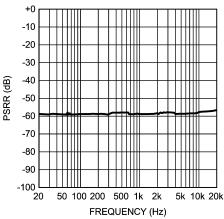

PSRR vs Frequency  $V_{DD} = 2.5V$ ,  $R_L = 32\Omega$

$V_{RIPPLE} = 200 \text{mVpp}, C-CUPL}$

20169713

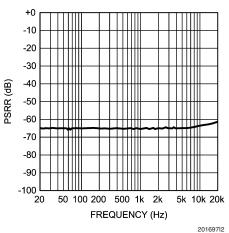

PSRR vs Frequency  $\begin{aligned} \mathbf{V}_{\text{DD}} &= 5.0 \text{V}, \, \mathbf{R}_{\text{L}} = 32 \Omega \\ \mathbf{V}_{\text{RIPPLE}} &= 200 \text{mVpp, C-CUPL} \end{aligned}$

20169715

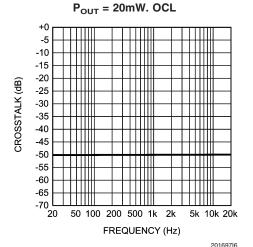

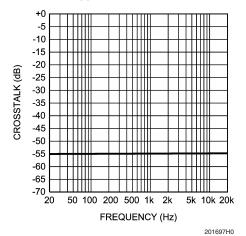

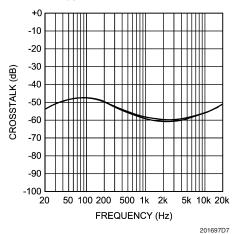

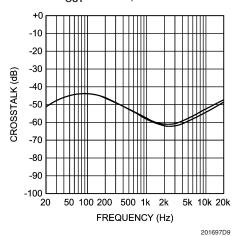

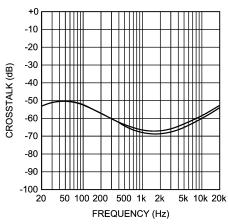

Crosstalk vs Frequency

$V_{DD} = 2.5V, R_L = 16\Omega$

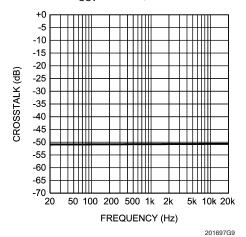

Crosstalk vs Frequency  $V_{DD}$  = 5.0V,  $R_L$  = 16 $\Omega$   $P_{OUT}$  = 40mW, OCL

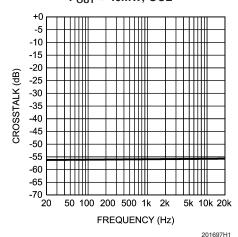

Crosstalk vs Frequency  $V_{DD}$  = 3.6V,  $R_L$  = 32 $\Omega$   $P_{OUT}$  = 40mW, OCL

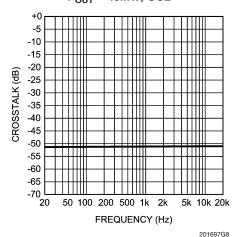

$\begin{aligned} &\text{Crosstalk vs Frequency} \\ &\text{V}_{\text{DD}} = 3.6\text{V}, \, \text{R}_{\text{L}} = 16\Omega \\ &\text{P}_{\text{OUT}} = 40\text{mW}, \, \text{OCL} \end{aligned}$

Crosstalk vs Frequency

$V_{DD}$  = 2.5V,  $R_L$  = 32 $\Omega$  $P_{OUT}$  = 20mW, OCL

Crosstalk vs Frequency

$V_{DD}$  = 5.0V,  $R_L$  = 32 $\Omega$  $P_{OUT}$  = 50mW, OCL

201697H2

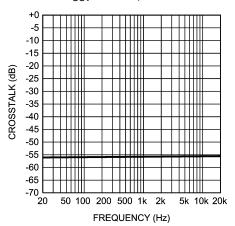

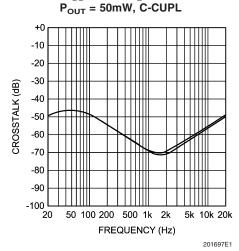

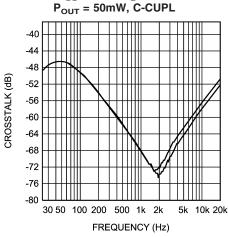

#### Crosstalk vs Frequency $V_{DD}$ = 5.0V, $R_L$ = 16 $\Omega$ P<sub>OUT</sub> = 50mW, C-CUPL

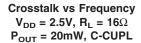

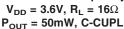

### Crosstalk vs Frequency $V_{DD}$ = 3.6V, $R_L$ = 32 $\Omega$

## Crosstalk vs Frequency

201697D8

#### Crosstalk vs Frequency $m V_{DD}$ = 2.5V, $m R_L$ = 32 $m \Omega$ P<sub>OUT</sub> = 20mW, C-CUPL

201697E0

#### Crosstalk vs Frequency $V_{DD}$ = 5.0V, $R_L$ = 32 $\Omega$

201697E2

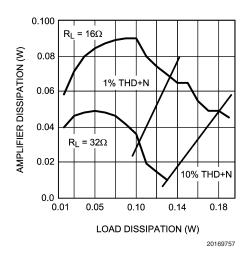

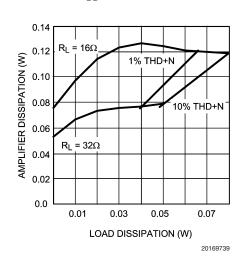

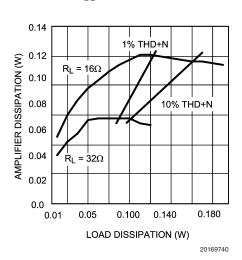

Load Dissipation vs Amplifier Dissipation  $V_{DD}$  = 2.5V, C-CUPL

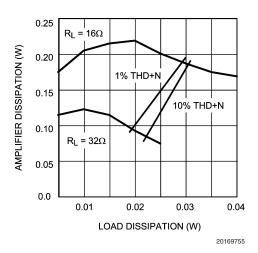

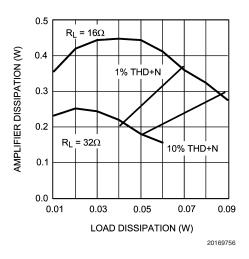

Load Dissipation vs Amplifier Dissipation  $V_{DD}$  = 5.0V, C-CUPL

Load Dissipation vs Amplifier Dissipation  $V_{DD} = 3.6V, OCL$

Load Dissipation vs Amplifier Dissipation  $V_{DD} = 3.6V, \, \text{C-CUPL}$

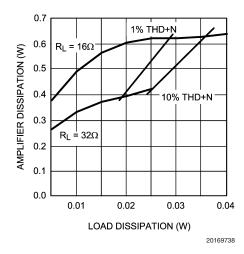

Load Dissipation vs Amplifier Dissipation  $V_{DD} = 2.5V$ , OCL

Load Dissipation vs Amplifier Dissipation  $V_{DD} = 5.0V$ , OCL

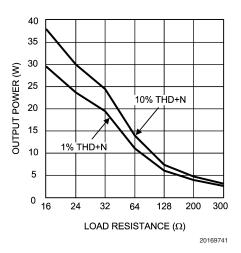

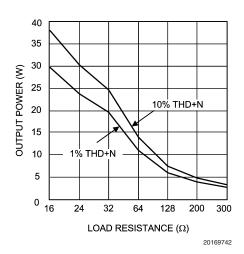

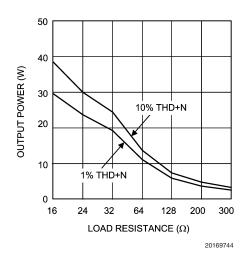

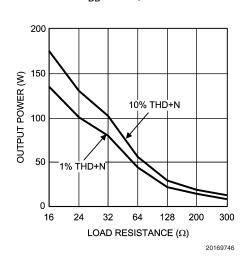

Output Power vs Load Resistance  $V_{DD} = 2.5V$ , C-CUPL

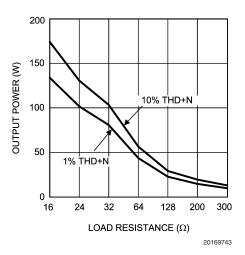

Output Power vs Load Resistance  $V_{DD} = 5.0V$ , C-CUPL

Output Power vs Load Resistance  $V_{DD} = 3.6V$ , OCL

# Output Power vs Load Resistance $V_{DD} = 3.6V, C\text{-}CUPL$

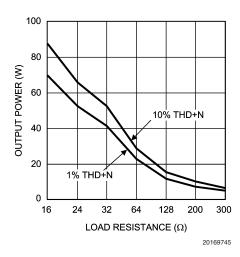

Output Power vs Load Resistance  $V_{DD} = 2.5V$ , OCL

Output Power vs Load Resistance  $V_{DD} = 5.0V$ , OCL

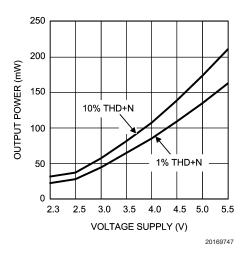

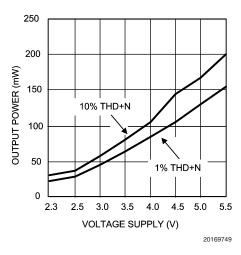

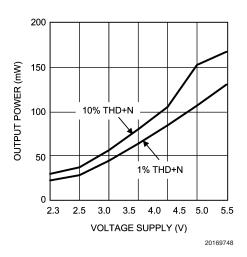

Output Power vs Supply Voltage  $R_L = 16\Omega$ , C-CUPL

Output Power vs Supply Voltage  $R_L = 16\Omega$ , OCL

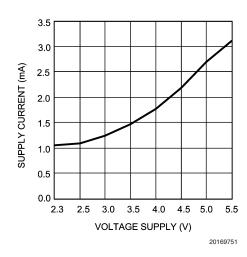

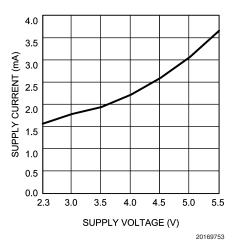

Supply Current vs Supply Voltage  $R_L = 16\Omega$ , C-CUPL

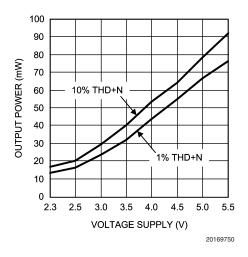

Output Power vs Supply Voltage  $R_L = 32\Omega$ , C-CUPL

Output Power vs Supply Voltage  $R_L = 32\Omega$ , OCL

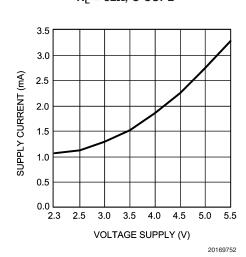

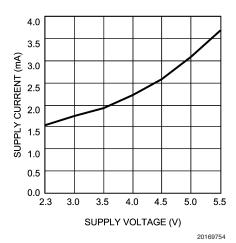

Supply Current vs Supply Voltage  $R_L = 32\Omega, C\text{-}CUPL$

Supply Current vs Supply Voltage  $R_L = 16\Omega$ , OCL

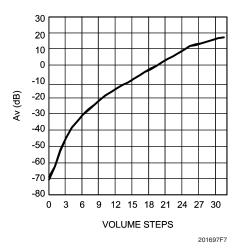

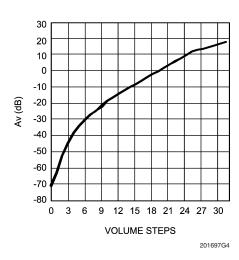

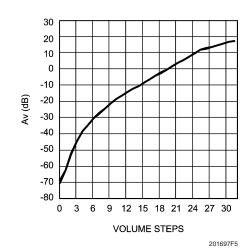

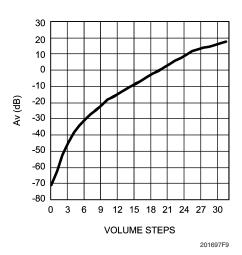

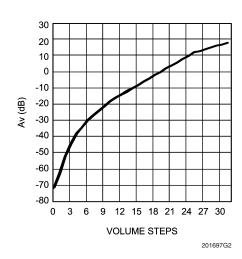

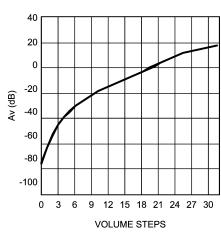

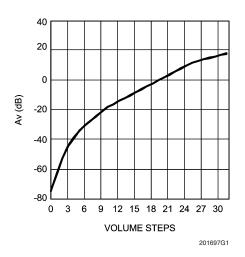

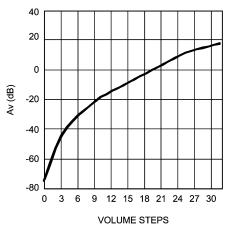

Gain vs Volume Steps  $V_{CC} = 2.5V$ ,  $R_L = 16\Omega$ , OCL

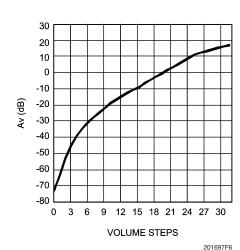

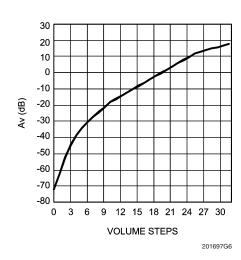

Gain vs Volume Steps  $V_{CC}$  = 5V,  $R_L$  = 16 $\Omega$ , OCL

Supply Current vs Supply Voltage  $R_L = 32\Omega$ , OCL

Gain vs Volume Steps  $V_{CC}$  = 3.6V,  $R_L$  = 16 $\Omega$ , OCL

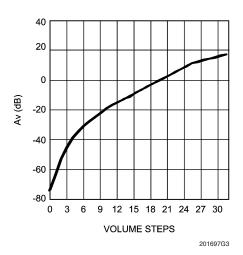

Gain vs Volume Steps  $V_{CC}$  = 2.5V,  $R_L$  = 16 $\Omega$ , C-CUPL

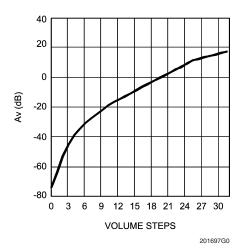

Gain vs Volume Steps  $\label{eq:Vcc} \textbf{V}_{\text{CC}} = \textbf{3.6V}, \ \textbf{R}_{\text{L}} = \textbf{16}\Omega, \ \textbf{C-CUPL}$

Gain vs Volume Steps  $V_{CC}$  = 2.5V,  $R_L$  = 32 $\Omega$ , OCL

Gain vs Volume Steps  $V_{CC} = 5V$ ,  $R_L = 32\Omega$ , OCL

Gain vs Volume Steps  $V_{CC}$  = 5V,  $R_L$  = 16 $\Omega$ , C-CUPL

Gain vs Volume Steps  $V_{CC}$  = 3.6V,  $R_L$  = 32 $\Omega$ , OCL

Gain vs Volume Steps  $\label{eq:Vcc} \textbf{V}_{\text{CC}} = \textbf{2.5V}, \ \textbf{R}_{\text{L}} = \textbf{32}\Omega, \ \textbf{C-CUPL}$

201697F8

Gain vs Volume Steps  $\label{eq:Vcc} \text{V}_{\text{CC}} = 3.6\text{V}, \, \text{R}_{\text{L}} = 32\Omega, \, \text{C-CUPL}$

# Gain vs Volume Steps $\label{eq:Vcc} \text{V}_{\text{CC}} = 5\text{V}, \ \text{R}_{\text{L}} = 32\Omega, \ \text{C-CUPL}$

201697G5

### **Application Information**

#### **AMPLIFIER CONFIGURATION EXPLANATION**

As shown in Figure 1, the LM4985 has three internal power amplifiers. Two of the amplifiers which amplify signals applied to their inputs, have internally configurable gain. The remaining third amplifier provides both half-supply output bias and AC ground return.

Loads, such as a headphone speaker, are connected between OUT1 and CNTGND or OUT2 and CNTGND. This configuration does not require an output coupling capacitor. The classical single-ended amplifier configuration, where one side of the load is connected to ground, requires large, expensive output coupling capacitors.

A configuration such as the one used in the LM4985 has a major advantage over single supply, single-ended amplifiers. Since the outputs OUT1, OUT2, and CNTGND are all biased at  $1/2~V_{\rm DD}$ , no net DC voltage exists across each load. This eliminates the need for output coupling capacitors which are required in a single-supply, single-ended amplifier configuration. Without output coupling capacitors in a typical single-supply, single-ended amplifier, the bias voltage is placed across the load resulting in both increased internal IC power dissipation and possible loudspeaker damage.

The LM4985 eliminates these output coupling capacitors when operating in Output Capacitor-less (OCL) mode. Unless shorted to ground, VoC is internally configured to apply a 1/2  $V_{\rm DD}$  bias voltage to a stereo headphone jack's sleeve. This voltage matches the bias voltage present on VoA and VoB outputs that drive the headphones. The headphones operate in a manner similar to a bridge-tied load (BTL). Because the same DC voltage is applied to both headphone speaker terminals this results in no net DC current flow through the speaker. AC current flows through a headphone speaker as an audio signal's output amplitude increases on the speaker's terminal.

The headphone jack's sleeve is not connected to circuit ground when used in OCL mode. Using the headphone output jack as a line-level output will place the LM4985's 1/2  $V_{\rm DD}$  bias voltage on a plug's sleeve connection. This presents no difficulty when the external equipment uses capacitively coupled inputs. For the very small minority of equipment that is DC coupled, the LM4985 monitors the current supplied by the amplifier that drives the headphone jack's sleeve. If this current exceeds  $500 {\rm mA}_{\rm PEAK}$ , the amplifier is shutdown, protecting the LM4985 and the external equipment.

#### POWER DISSIPATION

Power dissipation is a major concern when using any power amplifier. When operating in capacitor-coupled mode (C-CUPL), Equation 1 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = 2(V_{DD})^{2} / (2\pi^{2}R_{L})$$

(1)

When operating in the OCL mode, the LM4985's three operational amplifiers produce a maximum power dissipation given in Equation 2:

$$P_{DMAX} = [2(V_{DD})^{2} / (2\pi^{2}R_{L})] + [V_{DD}^{2} / (4\pi R_{L})]$$

(2)

The maximum power dissipation point obtained from Equation 1 or Equation 2 must not be greater than the power dissipation that results from Equation 3:

$$P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$$

(3)

For package TMD12AAA,  $\theta_{JA} = 190^{\circ} \text{C/W}$ .  $T_{JMAX} = 150^{\circ} \text{C}$  for the LM4985. Depending on the ambient temperature,  $T_A$ , of the system surroundings, Equation 3 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 2 is greater than that of Equation 3, then either the supply voltage must be decreased, the load impedance increased or  $T_A$  reduced.

For a typical application using a 3.6V power supply, with a  $32\Omega$  load, the maximum ambient temperature possible without violating the maximum junction temperature is approximately  $144^{\circ}C$  provided that device operation is around the maximum power dissipation point. Thus, for typical applications, power dissipation is not an issue. Power dissipation is a function of output power and thus, if typical operation is not around the maximum power dissipation point, the ambient temperature may be increased accordingly. Refer to the Typical Performance Characteristics curves for power dissipation information for lower output powers.

#### **POWER SUPPLY BYPASSING**

As with any amplifier, proper supply bypassing is important for low noise performance and high power supply rejection. The capacitor location on the power supply pins should be as close to the device as possible.

Typical applications employ a regulator with 10µF tantalum or electrolytic capacitor and a ceramic bypass capacitor which aid in supply stability. This does not eliminate the need for bypassing the supply nodes of the LM4985. A bypass capacitor value in the range of 0.1µF to 1µF is recommended for  $C_{\rm S}$ .

#### MICRO POWER SHUTDOWN

The LM4985's micropower shutdown is activated or deactivated through its I<sup>2</sup>C digital interface . Please refer to Table 1 for the I<sup>2</sup>C Address, Register Select, and Mode Control registers. Each amplifier within the LM4985 can be shutdown individually.

Please observe the following protocol when placing an individual amplifier channel in shutdown while the other channel remains active. The protocol requires activating both channels' shutdown simultaneously, then deactivating the shutdown of the channel whose output is desired (or leaving the desire channel in shutdown mode). Also, when operating in the C-CUPL mode, a short delay time is required between activating one channel after placing both channels in shutdown. If the user finds that both channels activate when only one was chosen, increase the delay.

#### **SELECTION OF INPUT CAPACITOR SIZE**

Amplifying the lowest audio frequencies requires a high value input coupling capacitor, C<sub>i</sub>. A high value capacitor can be expensive and may compromise space efficiency in portable designs. In many cases, however, the headphones used in portable systems have little ability to reproduce signals below 60Hz. Applications using headphones with this limited frequency response reap little improvement by using a high value input capacitor.

In addition to system cost and size, turn on time is affected by the size of the input coupling capacitor  $C_i$ . A larger input

### **Application Information** (Continued)

coupling capacitor requires more charge to reach its quiescent DC voltage. This charge comes from the output via the feedback Thus, by minimizing the capacitor size based on necessary low frequency response, turn-on time can be minimized. A small value of  $C_i$  (in the range of 0.22 $\mu$ F to 0.68 $\mu$ F), is recommended.

# MAXIMIZING OCL MODE CHANNEL-to-CHANNEL SEPARATION

The OCL mode AC ground return (CNT\_GND pin) is shared by both amplifiers. As such, any resistance between the CNT\_GND pin and the load will create a voltage divider with respect to the load resistance. In a typical circuit, the amount of CNT\_GND resistance can be very small, but still significant. It is significant because of the relatively low load impedances for which the LM4985 was designed to drive:  $16\Omega$

to  $32\Omega$ . The ratio of this voltage divider will determine the magnitude of any residual signal present at the CNT\_GND pin. It is this residual signal that leads to channel-to-channel separation (crosstalk) degradation.

For example, for a 60dB channel-to-channel separation while driving a  $16\Omega$  load, the resistance between the LM4985's CNT\_GND pin and the load must be less than  $16m\Omega.$  This is achieved by ensuring that the trace that connects the CNT\_GND pin to the headphone jack sleeve should be as short and massive as possible, given the physical constraints of any specific printed circuit board layout and design.

#### **DEMONSTRATION BOARD AND PCB LAYOUT**

Information concerning PCB layout considerations and demonstration board use and performance is found in Application Note AN-1452.

# I<sup>2</sup>C Control Register

Table 1 shows the actions that are implemented by manipulating the bits within the two internal  $I^2C$  control registers.

Table 1. LM4985 I<sup>2</sup>C Control Register Addressing and Data Format Chart

|          | LM4985 I2C Contorl Register Addressing and Data Chart |     |     |     |       |       |        | t      |                                 |

|----------|-------------------------------------------------------|-----|-----|-----|-------|-------|--------|--------|---------------------------------|

| I2C      |                                                       | A6  | A5  | A4  | А3    | A2    | A1     | A0     | Function                        |

| Address  |                                                       | 1   | 1   | 0   | 0     | 1     | 1      | A0     |                                 |

|          | D7                                                    | D6  | D5  | D4  | D3    | D2    | RS1    | RS0    |                                 |

| Register | 0                                                     | 0   | 0   | 0   | 0     | 0     | 0      | 0      | Read and write the mode         |

| Select   |                                                       |     |     |     |       |       |        |        | control register                |

| Jelect   | 0                                                     | 0   | 0   | 0   | 0     | 0     | 0      | 1      | Read and write the volume       |

|          |                                                       |     |     |     |       |       |        |        | control register                |

|          | D7                                                    | D6  | D5  | D4  | D3    | D2    | D1     | D0     |                                 |

|          |                                                       | WT1 | WT0 | PHG | SDCH1 | SDCH2 | CHSEL1 | CHSEL2 |                                 |

|          | 0                                                     | Х   | Х   | Х   | Х     | Х     | Х      | Х      | D7 must always be set to 0      |

|          | _                                                     | 0   | 0   | Х   | Х     | Х     | Х      | Х      | Wake-up time: 80ms (OCL),       |

|          |                                                       |     |     |     |       |       |        |        | 250ms (C-CUPL)                  |

|          | _                                                     | 0   | 1   | Х   | Х     | Χ     | Х      | Х      | Wake-up time: 110ms (OCL),      |

|          |                                                       |     |     |     |       |       |        |        | 450ms (C-CUPL)                  |

|          | _                                                     | 1   | 0   | Х   | Х     | Χ     | Х      | Х      | Wake-up time: 170ms (OCL),      |

|          |                                                       |     |     |     |       |       |        |        | 850ms (C-CUPL)                  |

|          | _                                                     | 1   | 1   | X   | X     | Χ     | Х      | Х      | Wake-up time: 290ms (OCL),      |

|          |                                                       |     |     |     |       |       |        |        | 1650ms (C-CUPL)                 |

|          | _                                                     | X   | Х   | 1   | X     | Χ     | X      | Х      | Output capacitor-less mode      |

|          |                                                       |     |     |     |       |       |        |        | active                          |

| Mode     | _                                                     | X   | Х   | 0   | X     | Χ     | Х      | Х      | Output capacitor-less mode      |

| Control  |                                                       |     |     |     |       |       |        |        | inactive                        |

| Register | _                                                     | X   | Х   | X   | 0     | 0     | Х      | Х      | Amplifier's SHUTDOWN            |

|          |                                                       |     |     |     |       |       |        |        | mode active                     |

|          | _                                                     | X   | Х   | Х   | 0     | 1     | Х      | Х      | Illegal mode                    |

|          | _                                                     | Х   | Х   | Х   | 1     | 0     | Х      | Х      | Illegal mode                    |

|          | _                                                     | X   | Х   | X   | 1     | 1     | Х      | Х      | Amplifier's SHUTDOWN            |

|          |                                                       |     |     |     |       |       |        |        | mode inactive                   |

|          | _                                                     | X   | Х   | X   | X     | Χ     | 0      | 02     | Amplifier's Chan. 1 is Input 1, |

|          |                                                       |     |     |     |       |       |        |        | Chan 2. is Input 2              |

|          | _                                                     | X   | Х   | X   | X     | Χ     | 0      | 1      | Amplifier's Chan. 1 is Input 1, |

|          |                                                       |     |     |     |       |       |        |        | Chan 2. is Input 1              |

|          | _                                                     | X   | Х   | X   | X     | Χ     | 1      | 0      | Amplifier's Chan. 1 is Input 2, |

|          |                                                       |     |     |     |       |       |        |        | Chan 2. is Input 2              |

|          | _                                                     | X   | Х   | X   | X     | Χ     | 1      | 1      | Amplifier's Chan. 1 is Input 2, |

|          |                                                       |     |     |     |       |       |        |        | Chan 2. is Input 1              |

### **Volume Control Settings Binary Values**

The minimum volume setting is set to -76dB when 00000 is loaded into the volume control register. Incrementing the volume control register in binary fashion increases the volume control setting, reaching full scale at 11111. Table C1 shows the value of the gain for each of the 32 binary volume control settings.

Table C1. Binary Values for the Different Volume Control Gain Settings

| 18<br>17<br>16<br>15<br>14 | 1<br>1<br>1<br>1 | 1<br>1<br>1 | 1 1 | 1 1 0 | 1 0 |

|----------------------------|------------------|-------------|-----|-------|-----|

| 16<br>15                   | 1<br>1<br>1      | 1           | 1   |       |     |

| 15                         | 1                | 1           |     | 0     | 4   |

|                            | 1                |             | 4   |       | 1   |

| 14                         |                  |             | 1   | 0     | 0   |

| '7                         |                  | 1           | 0   | 1     | 1   |

| 13                         | 1                | 1           | 0   | 1     | 0   |

| 12                         | 1                | 1           | 0   | 0     | 1   |

| 10                         | 1                | 1           | 0   | 0     | 0   |

| 8                          | 1                | 0           | 1   | 1     | 1   |

| 6                          | 1                | 0           | 1   | 1     | 0   |

| 4                          | 1                | 0           | 1   | 0     | 1   |

| 2                          | 1                | 0           | 1   | 0     | 0   |

| 0                          | 1                | 0           | 0   | 1     | 1   |

| -2                         | 1                | 0           | 0   | 1     | 0   |

| -4                         | 1                | 0           | 0   | 0     | 1   |

| -6                         | 1                | 0           | 0   | 0     | 0   |

| -8                         | 0                | 1           | 1   | 1     | 1   |

| -10                        | 0                | 1           | 1   | 1     | 0   |

| -12                        | 0                | 1           | 1   | 0     | 1   |

| -14                        | 0                | 1           | 1   | 0     | 0   |

| -16                        | 0                | 1           | 0   | 1     | 1   |

| -18                        | 0                | 1           | 0   | 1     | 0   |

| -21                        | 0                | 1           | 0   | 0     | 1   |

| -24                        | 0                | 1           | 0   | 0     | 0   |

| -27                        | 0                | 0           | 1   | 1     | 1   |

| -30                        | 0                | 0           | 1   | 1     | 0   |

| -34                        | 0                | 0           | 1   | 0     | 1   |

| -38                        | 0                | 0           | 1   | 0     | 0   |

| -44                        | 0                | 0           | 0   | 1     | 1   |

| -52                        | 0                | 0           | 0   | 1     | 0   |

| -62                        | 0                | 0           | 0   | 0     | 1   |

| -76                        | 0                | 0           | 0   | 0     | 0   |

## **Revision History**

| Rev | Date     | Description          |

|-----|----------|----------------------|

| 1.0 | 05/17/06 | Initial WEB release. |

#### Physical Dimensions inches (millimeters) unless otherwise noted

$\begin{array}{c} \text{micro SMD} \\ \text{Order Number LM4985TM} \\ \text{NS Package Number TMD12AAA} \\ X_1 = 1.215 \text{mm} \pm 0.03 \text{mm} \quad X_2 = 1.615 \text{mm} \pm 0.03 \text{mm} \quad X_3 = 0.600 \text{mm} \pm 0.075 \text{mm} \end{array}$

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor follows the provisions of the Product Stewardship Guide for Customers (CSP-9-111C2) and Banned Substances and Materials of Interest Specification (CSP-9-111S2) for regulatory environmental compliance. Details may be found at: www.national.com/quality/green.

Lead free products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560