### **General Description**

The MAX9201/MAX9202/MAX9203 high-speed, lowpower, quad/dual/single comparators feature TTL logic outputs with active internal pullups. Fast propagation delay (7ns typ at 5mV overdrive) makes these devices ideal for fast A/D converters and sampling circuits, line receivers, V/F converters, and many other data-discrimination, signal restoration applications.

All comparators can be powered from separate analog and digital power supplies or from a single combined supply voltage. The analog input common-mode range includes the negative rail, allowing ground sensing when powered from a single supply. The MAX9201/ MAX9202/MAX9203 consume only 9mW per comparator when powered from a +5V supply.

The MAX9202/MAX9203 feature output latches with TTL compatible inputs. The comparator output states are held when the latch inputs are driven low. The MAX9201 provides all the same features as the MAX9202/MAX9203 with the exception of the latches.

The MAX9201/MAX9202/MAX9203 are lower power and lower cost upgrades to the MAX901/MAX902/MAX903 offering a 50% power savings and smaller packaging.

Applications

High-Speed A/D Converters High-Speed V/F Converters Line Receivers High-Speed Signal Squaring/Restoration Threshold Detectors Input Trigger Circuitry High-Speed Data Sampling PWM Circuits

### \_Features

- Fast 7ns Propagation Delay

- Low 9mW/Comparator Power Consumption

- Separate Analog and Digital Supplies

- Flexible Analog Supply: +5V to +10V or ±5V

- Input Voltage Range Includes Negative Supply Rail

- TTL-Compatible Outputs

- TTL-Compatible Latch Inputs (MAX9202/MAX9203)

- Available in Space-Saving Packages 8-Pin SOT23 (MAX9203) 14-Pin TSSOP (MAX9202) 16-Pin TSSOP (MAX9201)

### **Ordering Information**

| PART                 | TEMP RANGE     | PIN-PACKAGE  |

|----------------------|----------------|--------------|

| MAX9201EUE           | -40°C to +85°C | 16 TSSOP     |

| MAX9201ESE           | -40°C to +85°C | 16 Narrow SO |

| MAX9202EUD           | -40°C to +85°C | 14 TSSOP     |

| MAX9202ESD           | -40°C to +85°C | 14 Narrow SO |

| <b>MAX9203</b> EKA-T | -40°C to +85°C | 8 SOT23-8    |

| MAX9203ESA           | -40°C to +85°C | 8 Narrow SO  |

|                      |                |              |

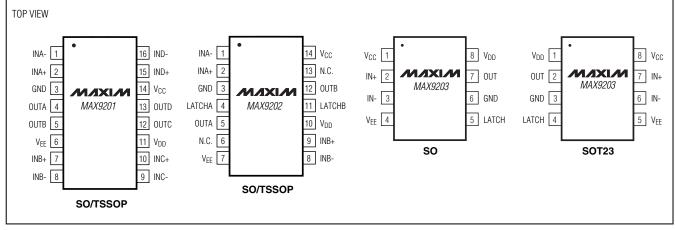

### Pin Configurations

### M/X/M

Maxim Integrated Products 1

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| Analog Supply Voltage (V <sub>CC</sub> - V <sub>EE</sub> )+12V                 |

|--------------------------------------------------------------------------------|

| Digital Supply Voltage (V <sub>DD</sub> )+7V                                   |

| Differential Input Voltage(V <sub>EE</sub> - 0.3V) to (V <sub>CC</sub> + 0.3V) |

| Common Mode Input Voltage(VEE - 0.3V) to (VCC + 0.3V)                          |

| Latch Input Voltage                                                            |

| (MAX9202/MAX9203 only)0.3V to (V <sub>DD</sub> + 0.3V)                         |

| Output Short-Circuit Duration                                                  |

| To GNDContinuous                                                               |

| To V <sub>DD</sub> 1min                                                        |

|                                                                                |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|-------------------------------------------------------|

| 8-Pin SOT23-8 (derate 9.1mW/°C above +70°C)727mW/°C   |

| 8-Pin SO (derate 5.9mW/°C above +70°C)471mW/°C        |

| 14-Pin TSSOP (derate 9.1mW/°C above +70°C)727mW/°C    |

| 14-Pin SO (derate 8.3mW/°C above +70°C)667mW/°C       |

| 16-Pin TSSOP (derate 9.4mW/°C above +70°C)755mW/°C    |

| 16-Pin SO (derate 8.7mW/°C above +70°C)696mW/°C       |

| Operating Temperature Range45°C to +85°C              |

| Junction Temperature+150°C                            |

| Storage Temperature Range65°C to +150°C               |

| Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ELECTRICAL CHARACTERISTICS

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, GND = 0, V_{CM} = 0, LATCH_ = logic high, T_A = -40^{\circ}C$  to +85°C. Typical values are at T<sub>A</sub> = +25°C, T\_A = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                             | SYMBOL                            | CON                                            | DITIONS                                                                   | MIN                   | ТҮР  | MAX                       | UNITS |

|---------------------------------------|-----------------------------------|------------------------------------------------|---------------------------------------------------------------------------|-----------------------|------|---------------------------|-------|

| Analog Supply Voltage Range           | V <sub>CC</sub> - V <sub>EE</sub> | Referenced to VEE                              | Referenced to V <sub>EE</sub>                                             |                       |      | 10.5                      | V     |

| Digital Supply Voltage Range          | V <sub>DD</sub>                   | Referenced to GND                              | Referenced to GND                                                         |                       |      | 5.25                      | V     |

|                                       |                                   | $V_{CM} = 0,$                                  | $T_A = +25^{\circ}C$                                                      |                       | 1    | 4                         |       |

| Input Offset Voltage                  | V <sub>OS</sub>                   | $V_{OUT}= 1.4V$                                | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                             |                       |      | 7.5                       | mV    |

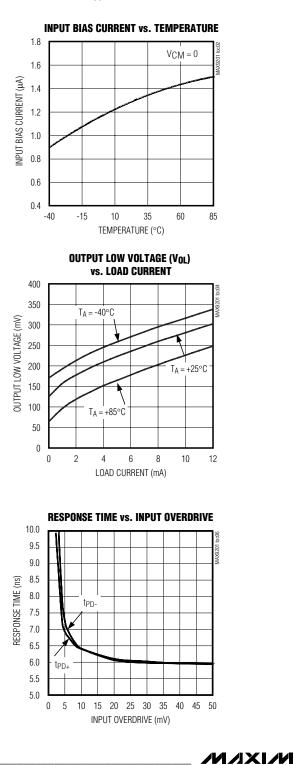

| Input Bias Current                    | Ι <sub>Β</sub>                    | I <sub>IN+</sub> or I <sub>IN-</sub>           | $T_A = +25^{\circ}C$                                                      |                       | 1.25 | 5                         | μA    |

|                                       | ıВ                                | IIN+ OF IIN-                                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                             |                       |      | 7.0                       | μΑ    |

| Input Offset Current                  | loo                               | $V_{CM} = 0,$                                  | $T_A = +25^{\circ}C$                                                      |                       | 50   | 250                       | nA    |

|                                       | IOS                               | $V_{OUT} = 1.4V$                               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                             |                       |      | 450                       | ПА    |

| Common-Mode Input Voltage<br>Range    | V <sub>CM</sub>                   | Note 2                                         |                                                                           | V <sub>EE</sub> - 0.1 |      | V <sub>CC</sub> -<br>2.25 | V     |

| Common-Mode Rejection                 |                                   | -5.1V < V <sub>CM</sub> < +2.75V               | $T_A = +25^{\circ}C$                                                      |                       | 50   | 150                       |       |

| Ratio                                 | CMRR                              | $V_{OUT} = 1.4V$                               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                             |                       |      | 250                       | μ٧/٧  |

|                                       |                                   | Note 0                                         | lote 3 $T_A = +25^{\circ}C$ $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                       | 50   | 150                       | μV/V  |

| Power-Supply Rejection Ratio          | PSRR                              | INOTE 3                                        |                                                                           |                       |      | 250                       |       |

| Output High Voltage                   | VOH                               | (V <sub>IN+</sub> - V <sub>IN-</sub> ) > 250mV | $V_{IN+} - V_{IN-}$ ) > 250mV, I <sub>SOURCE</sub> = 1mA                  |                       | 3.5  |                           | V     |

| Output Low Voltage                    | Vol                               | $(V_{IN+} - V_{IN-}) < -250m$                  | / <sub>IN+</sub> - V <sub>IN-</sub> ) < -250mV, I <sub>SINK</sub> = 8mA   |                       | 0.25 | 0.4                       | V     |

| Latch Input Threshold Voltage<br>High | $V_{LH}$                          | Note 4                                         | lote 4                                                                    |                       | 1.4  | 2                         | V     |

| Latch Input Threshold Voltage<br>Low  | V <sub>LL</sub>                   | Note 4                                         |                                                                           | 0.8                   | 1.4  |                           | V     |

| Latch Input Current High              | ILH                               | V <sub>LH</sub> = 3.0V, Note 4                 |                                                                           |                       | 0.5  | 3                         | μΑ    |

| Latch Input Current Low               | ارر                               | V <sub>LL</sub> = 0.3V, Note 4                 | V <sub>LL</sub> = 0.3V, Note 4                                            |                       | 0.5  | 3                         | μA    |

| Input Capacitance                     | CIN                               |                                                |                                                                           |                       | 4    |                           | рF    |

| Differential Input Impedance          | RIND                              |                                                |                                                                           |                       | 5    |                           | MΩ    |

| Common-Mode Input<br>Impedance        | RINCM                             |                                                |                                                                           |                       | 5.5  |                           | MΩ    |

| Desitive Anales Oversity              |                                   |                                                | MAX9201                                                                   |                       | 4.7  | 7                         |       |

| Positive Analog Supply<br>Current     | Icc                               | Note 5                                         | MAX9202                                                                   |                       | 2.5  | 4.0                       | mA    |

| Current                               |                                   |                                                | MAX9203                                                                   |                       | 1.3  | 2                         |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, GND = 0, V_{CM} = 0, LATCH_ = logic high, T_A = -40^{\circ}C to +85^{\circ}C.$  Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                         | SYMBOL | CO                                        | NDITIONS                 | MIN     | ТҮР | MAX | UNITS |    |

|-----------------------------------|--------|-------------------------------------------|--------------------------|---------|-----|-----|-------|----|

|                                   |        |                                           | MAX9201                  |         | 3.4 | 5.0 |       |    |

| Negative Analog Supply<br>Current | IEE    | Note 5                                    | MAX9202                  |         | 1.8 | 3.0 | mA    |    |

| ourrent                           |        |                                           | MAX9203                  |         | 1.0 | 1.6 |       |    |

|                                   |        |                                           | MAX9201                  |         | 2   | 3.0 |       |    |

| Digital Supply Current            | IDD    | Note 5                                    | MAX9202                  |         | 1   | 1.5 | mA    |    |

|                                   |        |                                           | MAX9203                  |         | 0.5 | 0.8 |       |    |

|                                   |        |                                           | MAX9201                  |         | 33  | 44  |       |    |

| Power Dissipation                 | PD     | $V_{CC} = V_{DD} = +5V,$<br>$V_{EE} = 0V$ | $V_{CC} = V_{DD} = +5V,$ | MAX9202 |     | 17  | 24    | mW |

|                                   |        | VEE - OV                                  | MAX9203                  |         | 9   | 13  |       |    |

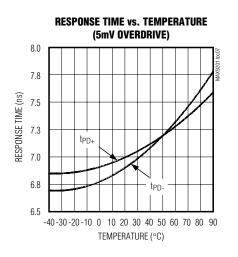

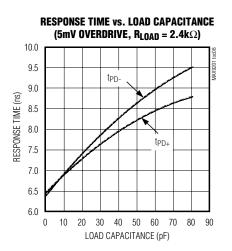

### **TIMING CHARACTERISTICS**

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, GND = 0, V_{CM} = 0, LATCH_ = logic high, T_A = -40^{\circ}C to +85^{\circ}C.$  Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Notes 1, 6)

| PARAMETER                             | SYMBOL               |                                                     | CONDITIONS                                                             | MIN | TYP | MAX     | UNITS |

|---------------------------------------|----------------------|-----------------------------------------------------|------------------------------------------------------------------------|-----|-----|---------|-------|

| Input-to-Output High<br>Response Time | tPD+                 | $V_{OD} = 5mV,$<br>$C_L = 15pF,$<br>$I_{OUT} = 2mA$ | $T_{A} = +25^{\circ}C$ $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ |     | 7   | 9<br>12 | ns    |

| Input-to-Output Low                   |                      | $V_{OD} = 5mV$ ,                                    | T <sub>A</sub> = +25°C                                                 |     | 7   | 9       |       |

| Response Time                         | tpD-                 | C <sub>L</sub> = 15pF,<br>I <sub>OUT</sub> = 2mA    | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                          |     |     | 12      | ns    |

| Rise Time                             | t <sub>R</sub>       | $C_L = 15pF,$<br>$I_{OUT} = 2mA$                    | $T_A = +25^{\circ}C$                                                   |     | 2.0 |         | ns    |

| Fall Time                             | tF                   | $C_L = 15pF,$<br>I <sub>OUT</sub> = 2mA             | $T_A = +25^{\circ}C$                                                   |     | 1.0 |         | ns    |

| Difference in Response Time           | Atap                 | Note 7                                              | $T_A = +25^{\circ}C$                                                   |     | 0.5 | 1.5     |       |

| Between Outputs                       | $\Delta t_{PD}$      | Note 7                                              | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                          |     |     | 2.5     | ns    |

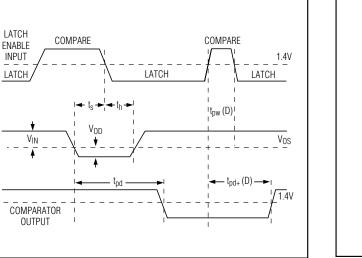

| Latch Disable to Output High<br>Delay | t <sub>PD</sub> +(D) | Note 4                                              |                                                                        |     | 10  |         | ns    |

| Latch Disable to Output Low<br>Delay  | t <sub>PD</sub> -(D) | Note 4                                              |                                                                        |     | 10  |         | ns    |

| Minimum Setup Time                    | ts                   | Note 4                                              |                                                                        |     | 2   |         | ns    |

| Minimum Hold Time                     | t <sub>N</sub>       | Note 4                                              |                                                                        |     | 1   |         | ns    |

| Minimum Latch Disable<br>Pulse Width  | t <sub>PW</sub> (D)  | Note 4                                              |                                                                        |     | 8   |         | ns    |

Note 1: All devices are 100% production tested at  $T_A = +25$ °C. All temperature limits are guaranteed by design.

Note 2: Inferred by CMRR test.

**Note 3:** Tested for +4.75V <  $V_{CC}$  < +5.25V, and -5.25V <  $V_{EE}$  < -4.75V with  $V_{DD}$  = +5V, although permissible analog power-supply range is 4.75V <  $V_{CC}$  < +10.5V for single supply operation with  $V_{EE}$  grounded.

Note 4: Specification does not apply to MAX9201.

**Note 5**:  $I_{CC}$  tested for  $4.75V < V_{CC} < +10.5V$  with V<sub>EE</sub> grounded.  $I_{EE}$  tested for  $-5.25V < V_{EE} < -4.75V$  with  $V_{CC} = +5V$ .  $I_{DD}$  tested for  $+4.75V < V_{DD} < +5.25V$  with all comparator outputs low, worst-case condition.

Note 6: Guaranteed by design. Times are for 100mV step inputs (see propagation delay characteristics in Figures 2 and 3)

**Note 7**: Maximum difference in propagation delay between two comparators in the MAX9201/MAX9202.

MIXIM

### **Typical Operating Characteristics**

(V<sub>CC</sub> = +5V, V<sub>EE</sub> = -5V, V<sub>DD</sub> = +5V, GND = 0, V<sub>CM</sub> = 0, LATCH\_ = logic high, V<sub>OUT</sub> = 1.4V, T<sub>A</sub> = +25°C, unless otherwise noted.)

**INPUT OFFSET VOLTAGE vs. TEMPERATURE** 1.5 1.0 INPUT OFFSET VOLTAGE (mV) 0.5 0 -0.5 -1.0 -1.5 -40 -15 10 35 60 85 TEMPERATURE (°C) **OUTPUT HIGH VOLTAGE (VOH)** vs. LOAD CURRENT 4.0 3.8 T<sub>A</sub> = +85°C **OUTPUT HIGH VOLTAGE (V)** 3.6 3.4  $T_A = +25^{\circ}C$ 3.2 3.0 -40°C T<sub>A</sub> = 2.8 0 2 10 4 6 8 12 LOAD CURRENT (mA) ICC SUPPLY CURRENT (PER COMPARATOR) vs. V<sub>CC</sub> SUPPLY VOLTAGE 1.6 1.5 ICC SUPPLY CURRENT (mA) TA = +85°C 1.4 1.3 1.2  $T_A = +25^{\circ}C$ 1.1 1.0  $T_A = -40^{\circ}C$ 0.9

$V_{EE} = GND$

10

9

4

0.8

5

6

7

VCC SUPPLY VOLTAGE (V)

### **Typical Operating Characteristics (continued)**

$(V_{CC} = +5V, V_{EE} = -5V, V_{DD} = +5V, GND = 0, V_{CM} = 0, LATCH_ = logic high, V_{OUT} = 1.4V, T_A = +25^{\circ}C, unless otherwise noted.)$

# MAX9201/MAX9202/MAX9203

### **MAX9201**

|                 | -               |                                         |

|-----------------|-----------------|-----------------------------------------|

| PIN             | NAME            | FUNCTION                                |

| 1, 8, 9,<br>16  | IN              | Negative Input (Channels A, B, C,<br>D) |

| 2, 7, 10,<br>15 | IN_+            | Positive Input (Channels A, B, C,<br>D) |

| 3               | GND             | Ground                                  |

| 4, 5, 12,<br>13 | OUT_            | Output (Channels A, B, C, D)            |

| 6               | VEE             | Negative Analog Supply and Substrate    |

| 11              | V <sub>DD</sub> | Positive Digital Supply                 |

| 14              | V <sub>CC</sub> | Positive Analog Supply                  |

| MAX9202 |                 |                                      |  |  |  |  |  |

|---------|-----------------|--------------------------------------|--|--|--|--|--|

| PIN     | NAME            | FUNCTION                             |  |  |  |  |  |

| 1, 8    | IN              | Negative Input (Channels A, B)       |  |  |  |  |  |

| 2, 9    | IN_+            | Positive Input (Channels A, B)       |  |  |  |  |  |

| 3       | GND             | Ground                               |  |  |  |  |  |

| 4, 11   | LATCH_          | Latch Input (Channels A, B)          |  |  |  |  |  |

| 5, 12   | OUT_            | Output (Channels A, B)               |  |  |  |  |  |

| 6, 13   | N.C.            | No Connection                        |  |  |  |  |  |

| 7       | VEE             | Negative Analog Supply and Substrate |  |  |  |  |  |

| 10      | V <sub>DD</sub> | Positive Digital Supply              |  |  |  |  |  |

| 14      | V <sub>CC</sub> | Positive Analog Supply               |  |  |  |  |  |

**Pin Description**

### \_\_\_\_

MAX9201/9202/9203

### Pin Description (continued)

### **MAX9203**

| MAX9203 |     |                 |                                      |  |          |  |  |  |

|---------|-----|-----------------|--------------------------------------|--|----------|--|--|--|

| P       | PIN |                 |                                      |  | FUNCTION |  |  |  |

| SO      | SOT | NAME            | FUNCTION                             |  |          |  |  |  |

| 1       | 8   | Vcc             | Positive Analog Supply               |  |          |  |  |  |

| 2       | 7   | IN+             | Positive Input                       |  |          |  |  |  |

| 3       | 6   | IN-             | Negative Input                       |  |          |  |  |  |

| 4       | 5   | V <sub>EE</sub> | Negative Analog Supply and Substrate |  |          |  |  |  |

| 5       | 4   | LATCH           | Latch Input                          |  |          |  |  |  |

| 6       | 3   | GND             | Ground                               |  |          |  |  |  |

| 7       | 2   | OUT             | Output                               |  |          |  |  |  |

| 8       | 1   | V <sub>DD</sub> | Positive Digital Supply              |  |          |  |  |  |

### Applications Information Circuit Layout

Because of the large gain-bandwidth transfer function of the MAX9201/MAX9202/MAX9203 special precautions must be taken to realize their full high-speed capability. A printed circuit board with a good, lowinductance ground plane is mandatory. All decoupling capacitors (the small 100nF ceramic type is a good choice) should be mounted as close as possible to the power-supply pins. Separate decoupling capacitors for analog V<sub>CC</sub> and for digital V<sub>DD</sub> are also recommended. Close attention should be paid to the bandwidth of the decoupling and terminating components. Short lead lengths on the inputs and outputs are essential to avoid unwanted parasitic feedback around the comparators. Solder the device directly to the printed circuit board instead of using a socket.

### **Input Slew-Rate Requirements**

As with all high-speed comparators, the high gain-bandwidth product of the MAX9201/MAX9202/ MAX9203 can create oscillation problems when the input traverses the linear region. For clean output switching without oscillation or steps in the output waveform, the input must meet minimum slew-rate requirements (0.5V/s typ). Oscillation is largely a function of board layout and of coupled source impedance and stray input capacitance. Both poor layout and large source impedance will cause the part to oscillate and increase the minimum slew-rate requirement. In some applications, it may be helpful to apply some positive feedback between the output and positive input. This pushes the output through the transition region clearly, but applies a hysteresis in threshold seen at the input terminals.

### **TTL Output and Latch Inputs**

The comparator TTL output stages are optimized for driving low-power Schottky TTL with a fan-out of four.

When the latch is connected to a logic high level, the comparator is transparent and immediately responds to changes at the input terminals. When the latch is connected to a TTL low level, the comparator output latches (in the same state) the instant that the latch command is applied, and will not respond to subsequent changes at the input. No latch is provided on the MAX9201.

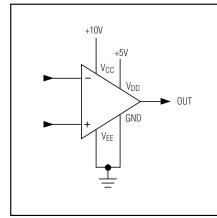

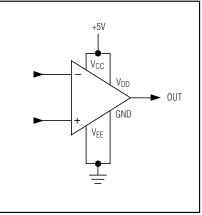

Figure 1a. Separate Analog Supply, Common Ground

Figure 1b. Single +5V Supply, Common Ground

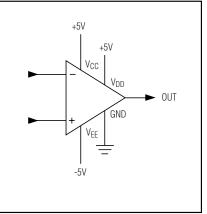

### **Typical Power-Supply Alternatives**

Figure 1c. Split ±5V Supply, Separate Ground

### **Power Supplies**

The MAX9201/MAX9202/MAX9203 can be powered from separate analog and digital supplies or from a single +5V supply. The analog supply can range from +5V to +10V with VEE grounded for single-supply operation (Figures 1a and 1b) or from a split  $\pm$ 5V supply (Figure 1c). The VDD digital supply always requires +5V.

In high-speed, mixed-signal applications where a common ground is shared, a noisy digital environment can adversely affect the analog input signal. When set up with separate supplies, the MAX9201/MAX9202/MAX9203 isolate analog and digital signals by providing a separate analog ground ( $V_{EE}$ ) and digital ground (GND).

### **Definition of Terms**

- **Vos Input Offset Voltage:** Voltage applied between the two input terminals to obtain TTL logic threshold (+1.4V) at the output.

- VIN Input Voltage Pulse Amplitude: Usually set to 100mV for comparator specifications.

- VoD Input Voltage Overdrive: Usually set to 5mV and in opposite polarity to V<sub>IN</sub> for comparator specifications.

- tpd+ Input to Output High Delay: The propagation delay measured from the time the input signal crosses the input offset voltage to the TTL logic threshold (+1.4V) of an output low to high transition.

- tpd-Input to Output Low Delay: The propagation delay measured from the time the input signal crosses the input offset voltage to the TTL logic threshold (+1.4V) of an output high to low transition.

- tpd+ (D) Latch Disable to Output High Delay: The propagation delay measured from the latch signal crossing the TTL logic threshold (+1.4V) in a low to high transition to the point of the output crossing TTL threshold (+1.4V) in a low to high transition.

- **tpd- (D)** Latch Disable to Output Low Delay: The propagation delay measured from the latch signal crossing the TTL threshold (+1.4V) in a low to high transition to the point of the output crossing TTL threshold (+1.4V) in a high to low transition.

- ts Minimum Setup Time: The minimum time, before the negative transition of the latch signal, that an input signal change must be present in order to be acquired and held at the outputs.

- th Minimum Hold Time: The minimum time, after the negative transition of the latch signal, that an input signal must remain unchanged in order to be acquired and held at the output.

- **tpw (D) Minimum Latch Disable Pulse Width:** The minimum time that the latch signal must remain high in order to acquire and hold an input signal change.

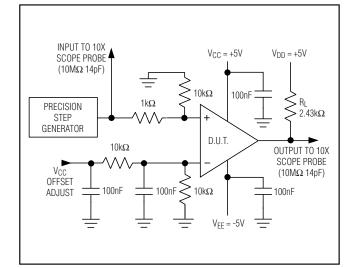

Figure 2. MAX9201/MAX9202/MAX9203 Diagram

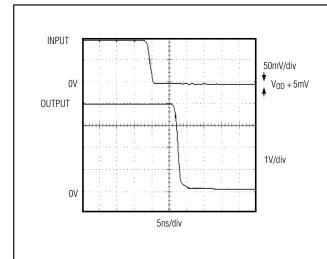

Figure 3. t<sub>PD+</sub> Response Time to 5mV Overdrive

Figure 4. tpp- Response Time to 5mV Overdrive

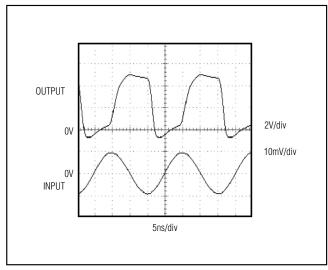

Figure 6. Response to 50MHz Sine Wave

### Chip Information

Printed USA

MAX9201 TRANSISTOR COUNT: 348 MAX9202 TRANSISTOR COUNT: 176 MAX9203 TRANSISTOR COUNT: 116 PROCESS: Bipolar

Figure 5. Response-Time Setup

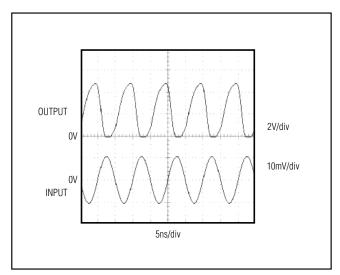

Figure 7. Response to 100MHz Sine Wave

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

| 8 | Maxim Integrated Product | ts, 120 San Gabriel Drive, | Sunnyvale, CA | 94086 408-737-7600 |

|---|--------------------------|----------------------------|---------------|--------------------|

|   |                          |                            |               |                    |

© 2005 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products.