# SINGLE-CHIP 1 TO 16 MINUTES DURATION VOICE RECORD/PLAYBACK DEVICES WITH DIGITAL STORAGE CAPABILITY

Publication Release Date: Oct 31, 2008 Revision 1.42

- 1 -

# nuvoTon

| 1. GENE   | RAL DESCRIPTION                                           | 4  |

|-----------|-----------------------------------------------------------|----|

| 2. FEATL  | JRES                                                      | 5  |

| 3. BLOCk  | CDIAGRAM                                                  | 6  |

| 4. PIN CO | ONFIGURATION                                              | 7  |

| 5. PIN DE | ESCRIPTION                                                | 8  |

| 6. FUNC   | TIONAL DESCRIPTION                                        | 9  |

| 6.1. O    | verview                                                   | 9  |

| 6.1.1     | Speech/Voice Quality                                      | 9  |

| 6.1.2     | Duration                                                  | 9  |

| 6.1.3     | Flash Technology                                          | 9  |

| 6.1.4     | Microcontroller Interface                                 | 9  |

| 6.1.5     | Programming                                               | 10 |

| 6.2. Fu   | unctional Details                                         | 10 |

| 6.2.1     | Internal Registers                                        | 11 |

| 6.2.2     | Memory Architecture                                       | 11 |

| 6.3. O    | perational Modes Description                              | 12 |

| 6.3.1     | I <sup>2</sup> C Interface                                | 12 |

| 6.3.2     | I <sup>2</sup> C Control Registers                        | 16 |

| 6.3.3     | Opcode Summary                                            | 17 |

| 6.3.4     | Data Bytes                                                | 19 |

| 6.3.5     | Configuration Register Bytes                              | 20 |

| 6.3.6     | Power-up Sequence                                         | 21 |

| 6.3.7     | Feed Through Mode                                         | 22 |

| 6.3.8     | Call Record                                               | 24 |

| 6.3.9     | Memo Record                                               | 25 |

| 6.3.10    | Memo and Call Playback                                    | 26 |

| 6.3.11    | Message Cueing                                            | 27 |

| 6.4. Aı   | nalog Mode                                                | 28 |

| 6.4.1     | Aux In and Ana In Description                             | 28 |

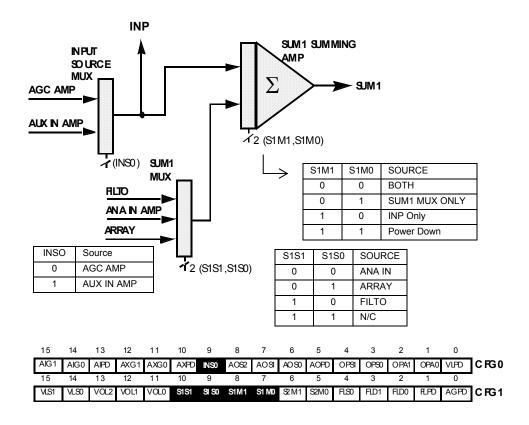

| 6.4.2     | ISD5100 Series Analog Structure (left half) Description   | 29 |

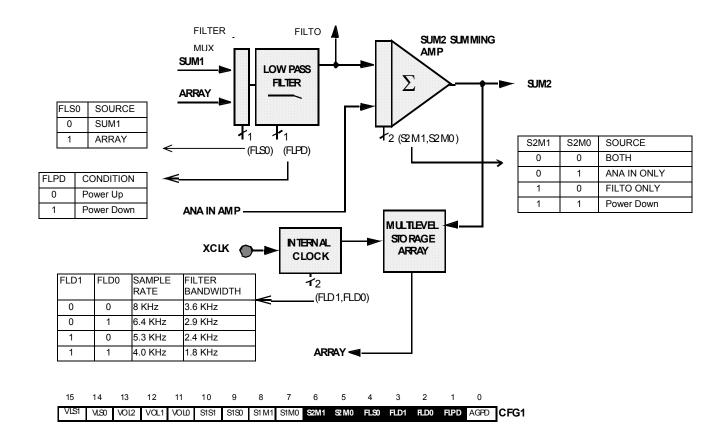

| 6.4.3     | ISD5100 Series Aanalog Structure (right half) Description | 30 |

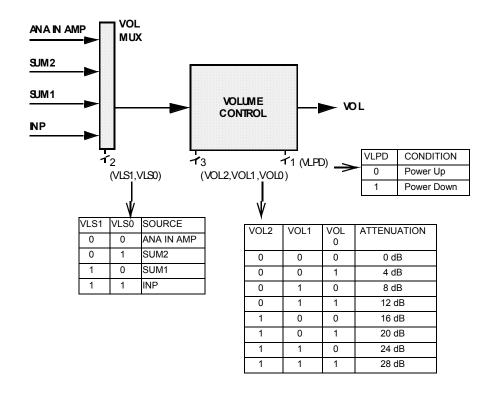

| 6.4.4     | Volume Control Description                                | 31 |

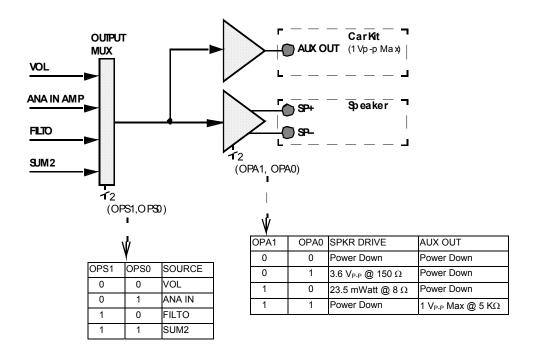

| 6.4.5     | Speaker and Aux Out Description                           | 32 |

| 6.4.6     | Ana Out Description                                       | 33 |

| 6.4.7     | Analog Inputs                                             | 33 |

# nuvoton

| 6.5.    | Digital Mode                                                            | 36 |

|---------|-------------------------------------------------------------------------|----|

| 6.5     | 5.1 Erasing Digital Data                                                | 36 |

| 6.5     | 5.2 Writing Digital Data                                                | 36 |

| 6.5     | 5.3 Reading Digital Data                                                | 37 |

| 6.5     | 5.4 Example Command Sequences                                           | 37 |

| 6.6.    | Pin Details                                                             | 48 |

| 6.6     | 6.1 Digital I/O Pins                                                    | 48 |

| 6.6     | S.2 Analog I/O Pins                                                     | 50 |

| 6.6     | S.3 Power and Ground Pins                                               | 54 |

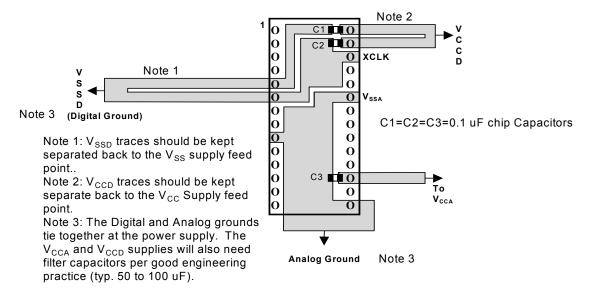

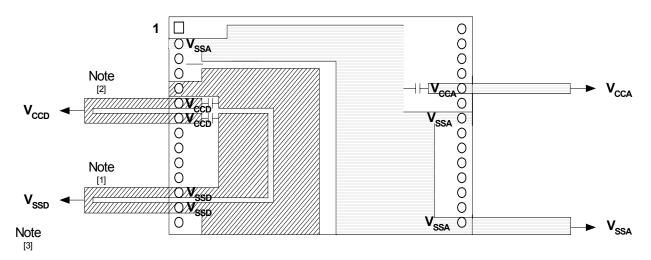

| 6.6     | 6.4 PCB Layout Examples                                                 | 55 |

| 7. TIM  | IING DIAGRAMS                                                           | 57 |

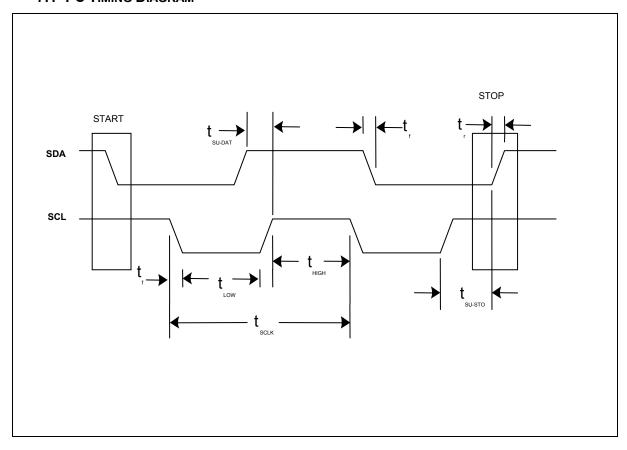

| 7.1     | I <sup>2</sup> C Timing Diagram                                         | 57 |

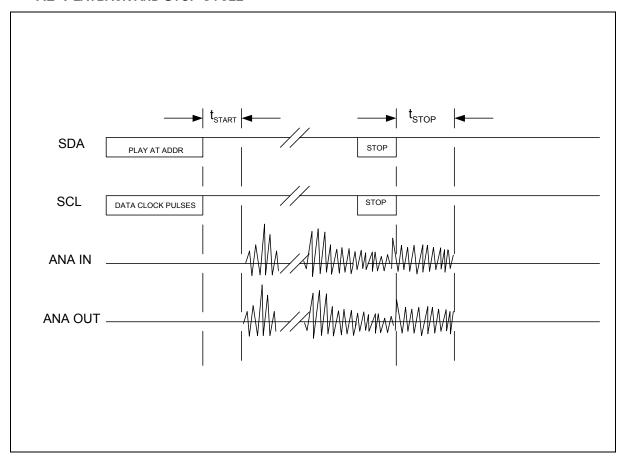

| 7.2     | Playback and Stop Cycle                                                 | 59 |

| 7.3     | Example of Power Up Command (first 12 bits)                             | 60 |

| 8. AB   | SOLUTE MAXIMUM RATINGS                                                  | 61 |

| 9. ELI  | ECTRICAL CHARACTERISTICS                                                | 63 |

| 9.1.    | General Parameters                                                      | 63 |

| 9.2.    | Timing Parameters                                                       | 64 |

| 9.3.    | Analog Parameters                                                       | 66 |

| 9.4.    | Characteristics of The I <sup>2</sup> C Serial Interface                |    |

| 9.5.    | I <sup>2</sup> C Protocol                                               | 73 |

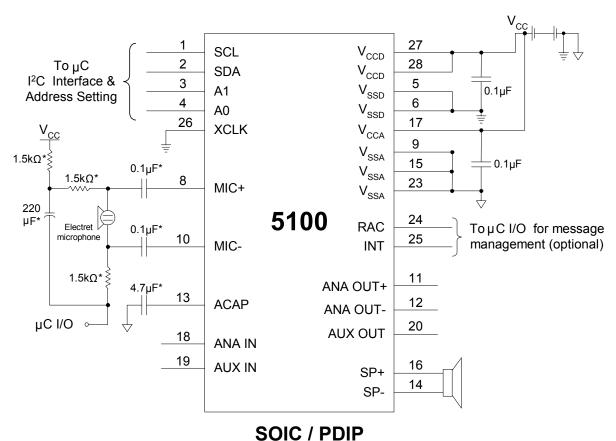

| 10. TYI | PICAL APPLICATION CIRCUIT                                               | 75 |

| 11. PA  | CKAGE SPECIFICATION                                                     | 76 |

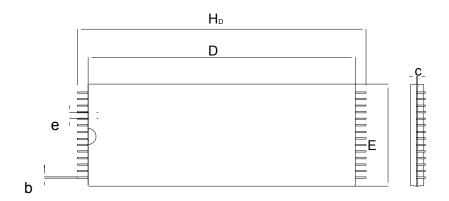

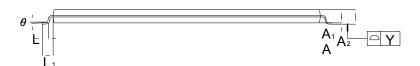

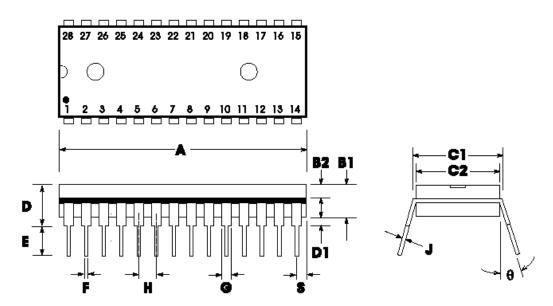

| 11.1.   | 28-Lead 8x13.4mm Plastic Thin Small Outline Package (TSOP) Type 1 - IQC | 76 |

| 11.2.   | 28-Lead 8x13.4mm Plastic Thin Small Outline Package (TSOP) Type 1       | 77 |

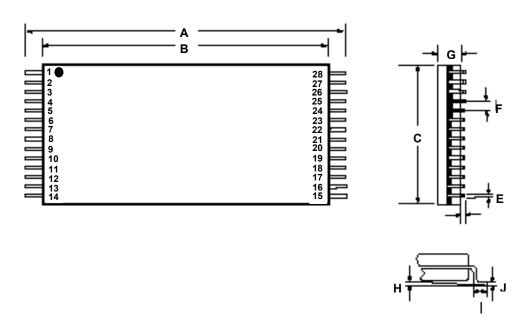

| 11.3.   | 28-Lead 300-Mil Plastic Small Outline Integrated Circuit (SOIC)         | 78 |

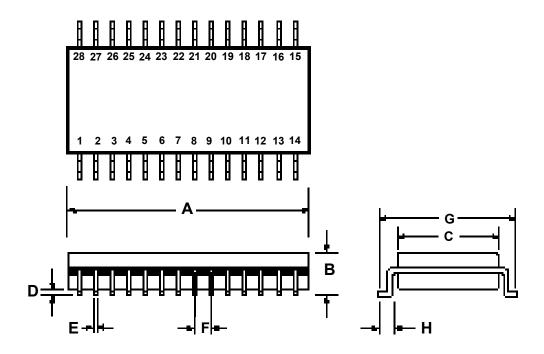

| 11.4.   | 28-Lead 600-Mil Plastic Dual Inline Package (PDIP)                      | 79 |

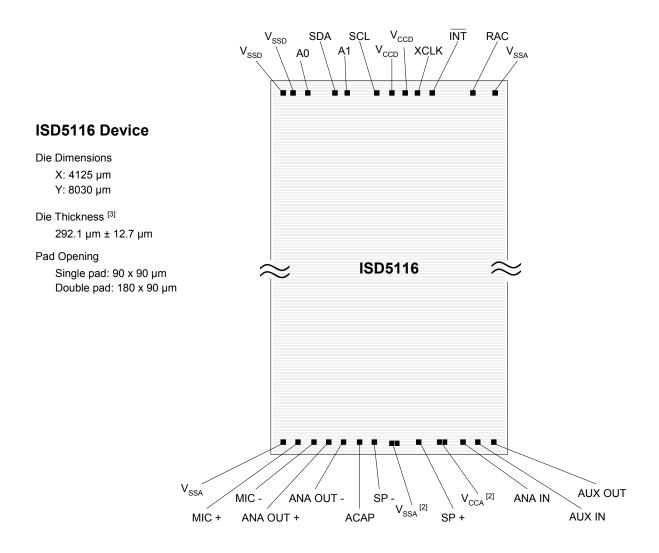

| 11.5.   | ISD5116 Die Information                                                 | 80 |

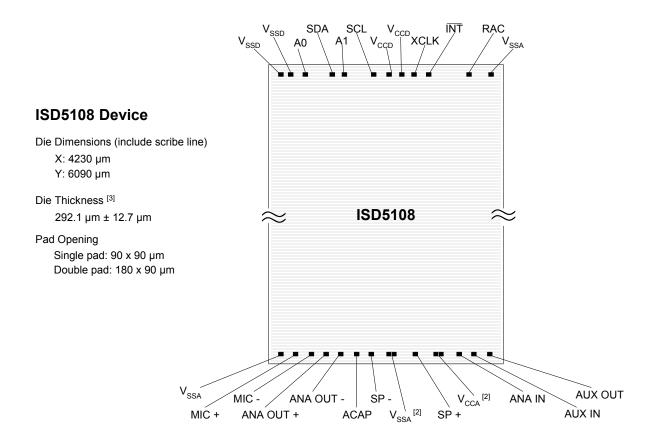

| 11.6.   | ISD5108 Die Information                                                 | 82 |

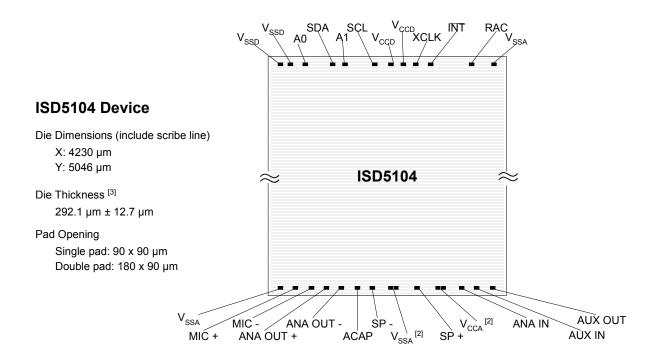

| 11.7.   | ISD5104 Die Information                                                 | 84 |

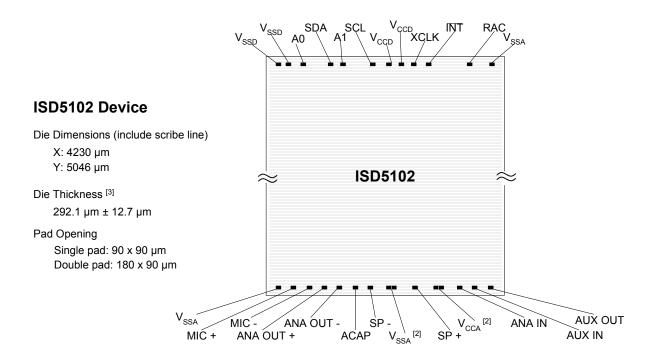

| 11.8.   | ISD5102 Die Information                                                 | 86 |

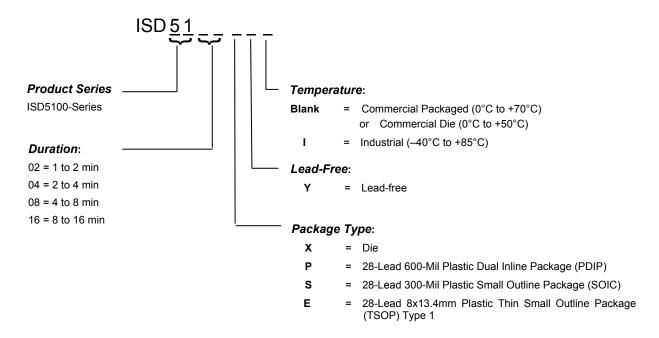

| 12. OR  | DERING INFORMATION                                                      | 88 |

| 13 V/F  | RSION HISTORY                                                           | 80 |

# 1. GENERAL DESCRIPTION

The ISD5100 ChipCorder® Series provide high quality, fully integrated, single-chip Record/Playback solutions for 1- to 16-minute messaging applications that are ideal for use in cellular phones, automotive communications, GPS/navigation systems and other portable products. The ISD5100 Series products are an enhancement of the ISD5000 architecture, providing: 1) the I²C serial port - address, control and duration selection are accomplished through an I²C interface to minimize pin count (ONLY two control lines required); 2) the capability of storing digital data, in addition to analog data. This feature allows customers to store phone numbers, system configuration parameters and message address locations for message management capability; 3) Various internal circuit blocks can be individually powered-up or -down for power saving.

#### The ISD5100 Series include:

- ISD5116 from 8 to 16 minutes

- ISD5108 from 4 to 8 minutes

- ISD5104 from 2 to 4 minutes

- ISD5102 from 1 to 2 minutes

Analog functions and audio gating have also been integrated into the ISD5100 Series products to allow easy interface with integrated digital cellular chip sets on the market. Audio paths have been designed to enable full duplex conversation record, voice memo, answering machine (including outgoing message playback) and call screening features. This product enables playback of messages while the phone is in standby, AND both simplex and duplex playback of messages while on a phone call.

Additional voice storage features for digital cellular phones include: 1) a personalized outgoing message can be sent to the person by getting caller-ID information from the host chipset, 2) a private call announce while on call can be heard from the host by giving caller-ID on call waiting information from the host chipset.

Logic Interface Options of 2.0V and 3.0V are supported by the ISD5100 Series to accommodate portable communication products (2.0- and 3.0-volt required).

Like other ChipCorder® products, the ISD5100 Series integrate the sampling clock, anti-aliasing and smoothing filters, and the multi-level storage array on a single-chip. For enhanced voice features, the ISD5100 Series eliminate external circuitry by integrating automatic gain control (AGC), a power amplifier/speaker driver, volume control, summing amplifiers, analog switches, and a car kit interface. Input level adjustable amplifiers are also included, providing a flexible interface for multiple applications.

Recordings are stored into on-chip nonvolatile memory cells, providing zero-power message storage. This unique, single-chip solution is made possible through Nuvoton's patented multilevel storage technology. Voice and audio signals are stored directly into solid-state memory in their natural, uncompressed form, providing superior quality on voice and music reproduction.

# 2. FEATURES

#### **Fully-Integrated Solution**

- Single-chip voice record/playback solution

- Dual storage of digital and analog data

- Durations

| Device   | ISD5102        | ISD5104        | ISD5108        | ISD5116         |

|----------|----------------|----------------|----------------|-----------------|

| Duration | 1 to 2 minutes | 2 to 4 minutes | 4 to 8 minutes | 8 to 16 minutes |

# **Low Power Consumption**

- Supply Voltage

- Commercial Temperature = +2.7V to +3.3V

- Industrial Temperature = +2.7V to +3.3V (+2.7V to +3.6V for ISD5108 only)

- Supports 2.0V and 3.0V interface logic

- Operating Current:

- > I<sub>CC Play</sub> = 15 mA (typical)

- > I<sub>CC Rec</sub> = 30 mA (typical)

- ➤ I<sub>CC Feedthrough</sub> = 12 mA (typical)

- Standby Current:

- ightharpoonup I<sub>SB</sub> = 1 $\mu$ A (typical)

- Most stages can be individually powered down to minimize power consumption

#### **Enhanced Voice Features**

- One or two-way conversation record

- · One or two-way message playback

- Voice memo record and playback

- Private call screening

- In-terminal answering machine

- · Personalized outgoing message

- Private call announce while on call

# **Digital Memory Features**

| -       |             |            |            |            |

|---------|-------------|------------|------------|------------|

| Device  | ISD5102     | ISD5104    | ISD5108    | ISD5116    |

| Storage | Up to 512Kb | Up to 1 Mb | Up to 2 Mb | Up to 4 Mb |

Storage of phone numbers, system configuration parameters and message address table in some application

# **Easy-to-use and Control**

- No compression algorithm development required

- User-controllable sampling rates

- Programmable analog interface

- Standard & Fast mode I<sup>2</sup>C serial interface (100kHz 400 kHz)

- · Fully addressable for multiple messages

## **High Quality Solution**

- High quality voice and music reproduction

- Nuvoton's standard 100-year message retention (typical)

- 100K record cycles (typical) for analog data

- 10K record cycles (typical) for digital data

#### **Options**

- Available in die form, TSOP and SOIC and PDIP (ISD5116 Only)

- Temperature: Commercial Packaged (0 to +70°C) & die (0 to +50°C); Industrial (-40 to +85°C)

- 5 -

Pb-free package

Publication Release Date: Oct 31, 2008

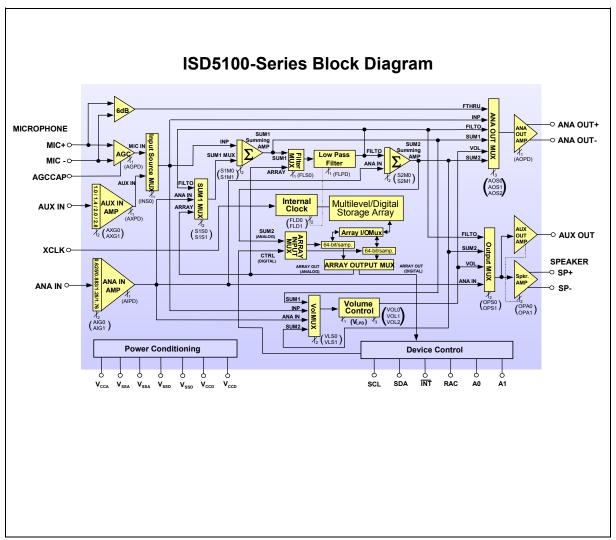

# 3. BLOCK DIAGRAM

Downloaded from **Elcodis.com** electronic components distributor

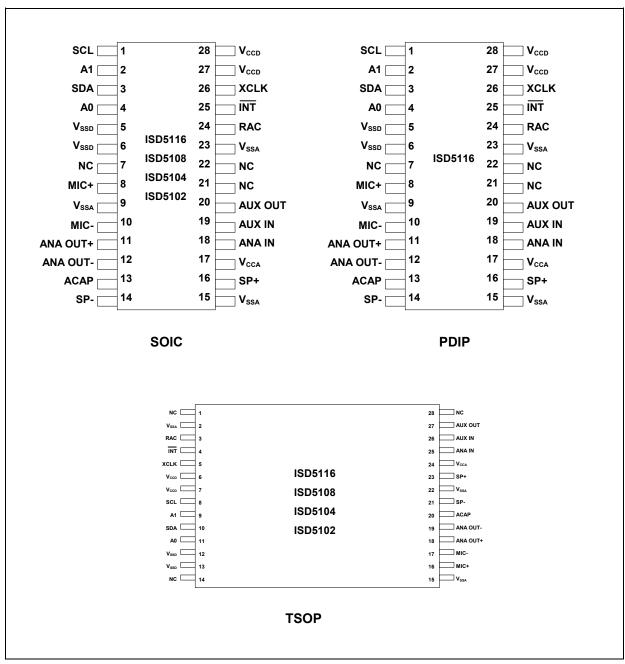

# 4. PIN CONFIGURATION

# 5. PIN DESCRIPTION

| Pin Name         | SOIC/PDIP | TSOP    | Functionality                                                                                                                                                                                                             |  |  |

|------------------|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SCL              | 1         | 8       | I <sup>2</sup> C Serial Clock Line: to clock the data into and out of the I <sup>2</sup> C interface.                                                                                                                     |  |  |

| A1               | 2         | 9       | Input pin that supplies the LSB +1 bit for the I <sup>2</sup> C Slave Address.                                                                                                                                            |  |  |

| SDA              | 3         | 10      | I <sup>2</sup> C Serial Data Line: Data is passed between devices on the bus over this line.                                                                                                                              |  |  |

| A0               | 4         | 11      | Input pin that supplies the LSB for the I <sup>2</sup> C Slave Address.                                                                                                                                                   |  |  |

| $V_{SSD}$        | 5,6       | 12,13   | Digital Ground.                                                                                                                                                                                                           |  |  |

| NC               | 7,21,22   | 1,14,28 | No Connect.                                                                                                                                                                                                               |  |  |

| MIC+             | 8         | 16      | Differential Positive Input for the microphone amplifier.                                                                                                                                                                 |  |  |

| $V_{SSA}$        | 9,15,23   | 2,15,22 | Analog Ground.                                                                                                                                                                                                            |  |  |

| MIC-             | 10        | 17      | Differential Negative Input for the microphone amplifier.                                                                                                                                                                 |  |  |

| ANA OUT+         | 11        | 18      | Differential Positive Analog Output for ANA OUT.                                                                                                                                                                          |  |  |

| ANA OUT-         | 12        | 19      | Differential Negative Analog Output for ANA OUT.                                                                                                                                                                          |  |  |

| ACAP             | 13        | 20      | AGC/AutoMute Capacitor: Required for the on-chip AGC amplifier during record and AutoMute function during playback.                                                                                                       |  |  |

| SP-              | 14        | 21      | Differential Negative Speaker Output: When the speaker outputs are in use, the AUX OUT output is disabled.                                                                                                                |  |  |

| SP+              | 16        | 23      | Differential Positive Speaker Output.                                                                                                                                                                                     |  |  |

| V <sub>CCA</sub> | 17        | 24      | Analog Supply Voltage: This pin supplies power to the analog sections of the device. It should be carefully bypassed to Analog Ground to insure correct device operation.                                                 |  |  |

| ANA IN           | 18        | 25      | Analog Input: one of the analog inputs with selectable gain.                                                                                                                                                              |  |  |

| AUX IN           | 19        | 26      | Auxiliary Input: one of the analog inputs with selectable gain.                                                                                                                                                           |  |  |

| AUX OUT          | 20        | 27      | Auxiliary Output: one the analog outputs of the device. When this output is used, the SP+ and SP- outputs are disabled.                                                                                                   |  |  |

| RAC              | 24        | 3       | Row Address Clock; an open drain output. The RAC pin goes LOW $T_{RACL}^{[1]}$ before the end of each row of memory and returns HIGH at exactly the end of each row of memory.                                            |  |  |

| INT              | 25        | 4       | Interrupt Output; an open drain output that indicates that a set EOM bit has been found during Playback or that the chip is in an Overflow (OVF) condition. This pin remains LOW until a Read Status command is executed. |  |  |

| XCLK             | 26        | 5       | This pin must be grounded for utilizing internal clock. For precision timing control, external clock signal can be applied through this pin.                                                                              |  |  |

| V <sub>CCD</sub> | 27,28     | 6,7     | Digital Supply Voltage. These pins supply power to the digital sections of the device. They must be carefully bypassed to Digital Ground to insure correct device operation.                                              |  |  |

Publication Release Date: Oct 31, 2008 Revision 1.42

-8-

<sup>[1]</sup> See the <u>Parameters section</u>

#### 6. FUNCTIONAL DESCRIPTION

#### 6.1. OVERVIEW

# 6.1.1 Speech/Voice Quality

The ISD5100 ChipCorder Series can be configured via software to operate at 4.0, 5.3, 6.4 or 8.0 kHz sampling frequency to select appropriate voice quality. Increasing the duration decreases the sampling frequency and bandwidth, which affects audio quality. The table in the following section shows the relationship between sampling frequency, duration and filter pass band.

#### 6.1.2 Duration

To meet system requirements, the ISD5100 Series are single-chip solution, which provide 1 to 16 minutes of voice record and playback, depending upon the sample rates chosen.

| Sample Rate |               | Typical Filter |              |              |            |

|-------------|---------------|----------------|--------------|--------------|------------|

| (kHz)       | ISD5116       | ISD5108        | ISD5104      | ISD5102      | Knee (kHz) |

| 8.0         | 8 min 44 sec  | 4 min 22 sec   | 2 min 11 sec | 1 min 5 sec  | 3.4        |

| 6.4         | 10 min 55 sec | 5 min 27 sec   | 2 min 43 sec | 1 min 21 sec | 2.7        |

| 5.3         | 13 min 6 sec  | 6 min 33 sec   | 3 min 17 sec | 1 min 38 sec | 2.3        |

| 4.0         | 17 min 28 sec | 8 min 44 sec   | 4 min 22 sec | 2 min 11 sec | 1.7        |

<sup>[1]</sup> Minus any pages selected for digital storage

## 6.1.3 Flash Technology

One of the benefits of Nuvoton's ChipCorder technology is the use of on-chip Flash memory, which provides zero-power message storage. The message is retained for up to 100 years (typically) without power. In addition, the device can be re-recorded over 10,000 times (typically) for the digital data and over 100,000 times (typically) for the analog messages.

A new feature has been added that allows memory space in the ISD5100 Series to be allocated to either digital or analog storage when recorded. The fact that a section has been assigned digital or analog data is stored in the Message Address Table by the system microcontroller when the recording is made.

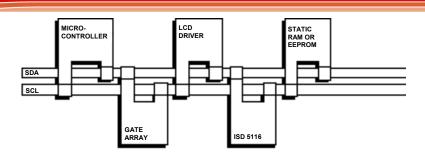

# 6.1.4 Microcontroller Interface

The ISD5100 Series are controlled through an I<sup>2</sup>C 2-wire interface. This synchronous serial port allows commands, configurations, address data, and digital data to be loaded into the device, while allowing status, digital data and current address information to be read back from the device. In addition to the serial interface, two other status pins can feedback to the microcontroller for enhanced

- 9 -

Publication Release Date: Oct 31, 2008

interface. These are the RAC timing pin and the INT pin for interrupts to the controller. Communications with all the internal registers of any operations are through the serial bus, as well as digital memory Read and Write operations.

# 6.1.5 Programming

The ISD5100 Series are also ideal for playback-only applications, where single or multiple messages may be played back when desired. Playback is controlled through the I<sup>2</sup>C interface. Once the desired message configuration is created, duplicates can easily be generated via a third-party programmer. For more information on available application tools and programmers, please see the Nuvoton web site at www.Nuvoton-usa.com

# **6.2. FUNCTIONAL DETAILS**

The ISD5100 Series are single chip solutions for analog and digital data storage. The array can be divided between analog and digital storage according to user's choice, when the device is configured.

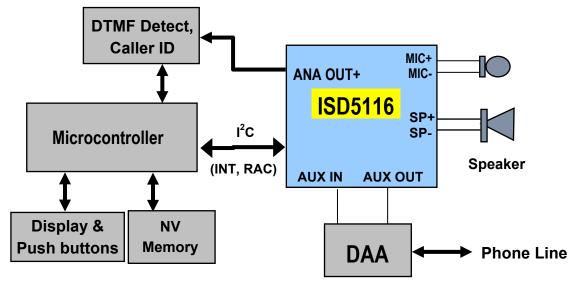

The below block diagram shows that the ISD5116 device can be easily designed into a telephone answering machine (TAD). Both Mic inputs transmit the voice input signal from the microphone to perform OGM recording, as well as to record the speech during phone conversation (simplex).

When the TAD is activated, the voice of the other party from the phone line feeds into the AUX IN, and is recorded into the ISD5116 device. Then the new message is usually indicated with blinking new message LED. Hence, during playback, the recorded message is sent out to speaker with volume control. Two I<sup>2</sup>C pins are used for all communications between the ChipCorder and the microcontroller for analog and/or digital storage, and the two outputs, INT and RAC are feedback to microcontroller for message management.

For duplex recording, speech from Mic inputs and message from received path can be directly recorded into the array simultaneously, then playback afterwards. In addition, for speaker phone

operation, voice from Mic inputs are fed to AUX OUT and transmitted to the phone line, while message from other party is input from the AUX IN, then fed through to the speaker for listening.

The ISD5100 device has the flexibility for other applications, because the audio paths can be configured differently, with each circuit block being powered-up or –down individually, according to the applications requirement.

# 6.2.1 Internal Registers

The ISD5100 Series have multiple internal registers that are used to store the address information and the configuration or set-up of the device. The two 16-bit configuration registers control the audio paths through the device, the sample frequency, the various gains and attenuations, power up and down of different sections, and the volume settings. These registers are discussed in detail in section 7.3.5.

# 6.2.2 Memory Architecture

The ISD5100 Series memory array are arranged in various pages (or rows) of each 2048 bits as follows. The primary addressing for the pages are handled by 11 bits of address input in the analog mode.

A memory page is 2048 bits organized as thirty-two 64-bit "blocks" when used for digital storage. The contents of a page are either analog or digital. This is determined by instruction (opcode) at the time the data is written. A record of where is analog and where is digital, is stored in a message address table (MAT) by the system microcontroller. The MAT is a table kept in the microcontroller memory that defines the status of each message "page". It can be stored back into the ISD5100 Series if the power fails or the system is turned off. Using this table allows efficient message management. Segments of messages can be stored wherever there is available space in the memory array. [This is explained in detail for the ISD5008 in Applications Note #9 and will be similarly described in a later Note for the ISD5100-Series.]

| Products | Pages (Rows) | Bits/Page | Memory Size    |

|----------|--------------|-----------|----------------|

| ISD5116  | 2048         | 2048      | 4,194,304 bits |

| ISD5108  | 1024         | 2048      | 2,097,152 bits |

| ISD5104  | 512          | 2048      | 1,048,576 bits |

| ISD5102  | 256          | 2048      | 524,288 bits   |

When a page is used for analog storage, the same 32 blocks are present but there are 8 EOM (End-of-Message) markers. This means that for each 4 blocks there is an EOM marker at the end. Thus, when recording, the analog recording will stop at any one of eight positions. At 8 kHz sampling frequency, this results in a resolution of 32 msec when ENDING an analog recording. Beginning an analog recording is limited to the 256 msec resolution provided by the 11-bit address. A recording does not immediately stop when the Stop command is given, but continues until the 32 millisecond block is filled. Then a bit is placed in the EOM memory to develop the interrupt that signals a message is finished playing in the Playback mode.

Digital data is sent and received serially over the I<sup>2</sup>C interface. The data is serial-to-parallel converted and stored in one of two alternating (commutating) 64-bit shift registers. When an input register is full, it becomes the register that is parallel written into the array. The prior write register becomes the new serial input register. A mechanism is built-in to ensure there is always a register available for storing new data.

Storing data in the memory is accomplished by accepting data one byte at a time and issuing an acknowledge. If data is coming in faster than it can be written, the chip issues an acknowledge to the host microcontroller, but holds SCL LOW until it is ready to accept more data. (See section 7.5.2 for details).

The read mode is the opposite of the write mode. Data is read into one of two 64-bit registers from the array and serially sent to the  $I^2C$  interface. (See section 7.5.3 for details).

#### 6.3. OPERATIONAL MODES DESCRIPTION

#### 6.3.1 I<sup>2</sup>C Interface

To use more than four ISD5100 Series devices in an application requires some external switching of the I<sup>2</sup>C interface.

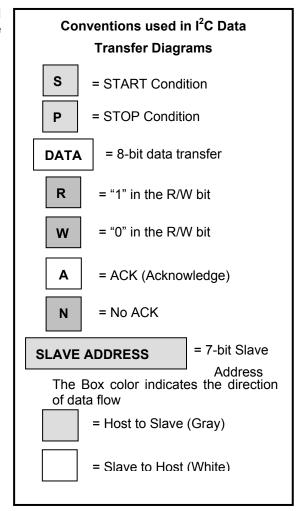

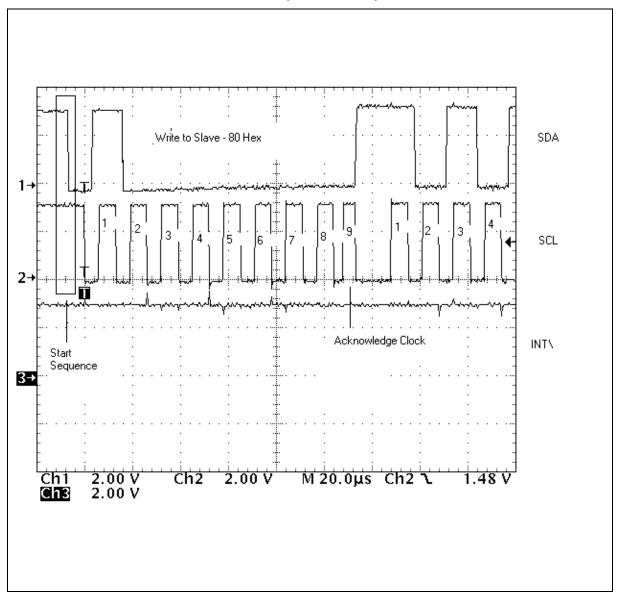

#### I<sup>2</sup>C interface

**Important note:** The rest of this data sheet will assume that the reader is familiar with the  $l^2C$  serial interface. Additional information on  $l^2C$  may be found in <u>section 10</u> on page 72 of this document. If you are not familiar with this serial protocol, please read this section to familiarize yourself with it. A large amount of additional information on  $l^2C$  can also be found on the Philips web page at <a href="http://www.philips.com/">http://www.philips.com/</a>.

#### I<sup>2</sup>C Slave Address

The ISD5100 Series have 7-bit slave address of <100 00xy> where x and y are equal to the state, respectively, of the external address pins A1 and A0. Because all data bytes are required to be 8 bits, the LSB of the address byte is the Read/Write selection bit that tells the slave whether to transmit or receive data. Therefore, there are 8 possible slave addresses for the ISD5100-Series. These are:

#### **Pinout Table**

| A1 | A0 | Slave<br>Address | R/W Bit | HEX Value |

|----|----|------------------|---------|-----------|

| 0  | 0  | <100 0000>       | 0       | 80        |

| 0  | 1  | <100 0001>       | 0       | 82        |

| 1  | 0  | <100 0010>       | 0       | 84        |

| 1  | 1  | <100 0011>       | 0       | 86        |

| 0  | 0  | <100 0000>       | 1       | 81        |

| 0  | 1  | <100 0001>       | 1       | 83        |

| 1  | 0  | <100 0010>       | 1       | 85        |

| 1  | 1  | <100 0011>       | 1       | 87        |

# ISD5100 Series I<sup>2</sup>C Operation Definitions

There are many control functions used to operate the ISD5100-Series. Among them are:

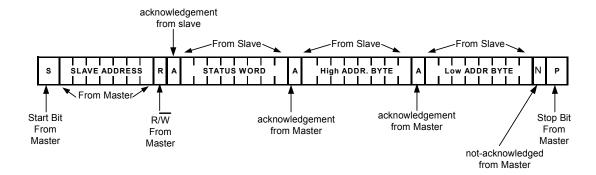

#### 6.3.1.1. Read Status Command:

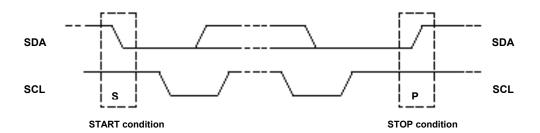

The Read Status command is a read request from the Host processor to the ISD5100 Series without delivering a Command Byte. The Host supplies all the clocks (SCL). In each case, the entity sending the data drives the data line (SDA). The Read Status Command is executed by the following  $I^2C$  sequence.

- 1. Host executes I<sup>2</sup>C START

- 2. Send Slave Address with R/W bit = "1" (Read) 81h

- 3. Slave (ISD5100-Series) responds back to Host an Acknowledge (ACK) followed by 8-bit Status word

- 4. Host sends an Acknowledge (ACK) to Slave

- 5. Wait for SCL to go HIGH

- 6. Slave responds with Upper Address byte of internal address register

- 7. Host sends an ACK to Slave

- 8. Wait for SCL to go HIGH

- 9. Slave responds with Lower Address byte of internal address register (A[4:0] will always return set to 0.)

- 10. Host sends a NO ACK to Slave, then executes I<sup>2</sup>C STOP

# nuvoton

Note that the processor could have sent an I<sup>2</sup>C STOP after the Status Word data transfer and aborted the transfer of the Address bytes.

A graphical representation of this operation is found below. See the caption box above for more explanation.

| S | SLAVE ADDRESS | R      | Α | DATA | Α        | DATA | Α  | DATA  | N   | Р |  |

|---|---------------|--------|---|------|----------|------|----|-------|-----|---|--|

|   |               |        |   |      |          |      |    |       |     | \ |  |

|   |               | Status |   | Н    | igh Addr |      | Lo | w Add | dr. |   |  |

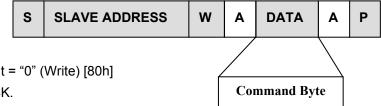

# 6.3.1.2. Load Command Byte Register (Single Byte Load):

A single byte may be written to the Command Byte Register in order to power up the device, start or stop Analog Record (if no address information is needed), or do a Message Cueing function. The Command Byte Register is loaded as follows:

- 1. Host executes I<sup>2</sup>C START

- 2. Send Slave Address with R/W bit = "0" (Write) [80h]

- 3. Slave responds back with an ACK.

- 4. Wait for SCL to go HIGH

- 5. Host sends a command byte to Slave

- 6. Slave responds with an ACK

- 7. Wait for SCL to go HIGH

- 8. Host executes I<sup>2</sup>C STOP

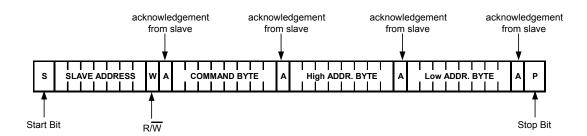

# 6.3.1.3. Load Command Byte Register (Address Load)

For the normal addressed mode the Registers are loaded as follows:

- 1. Host executes I<sup>2</sup>C START

- 2. Send Slave Address with R/W bit = "0" (Write)

- 3. Slave responds back with an ACK.

- 4. Wait for SCL to go HIGH

- 5. Host sends a byte to Slave (Command Byte)

- 6. Slave responds with an ACK

- 7. Wait for SCL to go HIGH

- 8. Host sends a byte to Slave (High Address Byte)

- 9. Slave responds with an ACK

- 10. Wait for SCL to go HIGH

- 11. Host sends a byte to Slave (Low Address Byte)

- 12. Slave responds with an ACK

- 13. Wait for SCL to go HIGH

- 14. Host executes I<sup>2</sup>C STOP

Publication Release Date: Oct 31, 2008

# 6.3.2 I<sup>2</sup>C Control Registers

The ISD5100 Series are controlled by loading commands to, or, reading from, the internal command, configuration and address registers. The Command byte sent is used to start and stop recording, write or read digital data and perform other functions necessary for the operation of the device.

# **Command Byte**

Control of the ISD5100 Series are implemented through an 8-bit command byte, sent after the 7-bit device address and the 1-bit Read/Write selection bit. The 8 bits are:

- Global power up bit

- DAB bit: determines whether device is performing an analog or digital function

- 3 function bits: these determine which function the device is to perform in conjunction with the DAB bit.

- 3 register address bits: these determine if and when data is to be loaded to a register

| Power Up<br>Bit | C7 | C6  | C5       | C4     | C3  | C2        | C1  | C0  |

|-----------------|----|-----|----------|--------|-----|-----------|-----|-----|

|                 | PU | DAB | FN2      | FN1    | FN0 | RG2       | RG1 | RG0 |

|                 |    |     | Function | n Bits | Re  | egister B | its |     |

#### **Function Bits**

The command byte function bits are detailed in the table to the right. C6, the DAB bit, determines whether the device is performing an analog or digital function. The other bits are decoded to produce the individual commands. Not all decode combinations are currently used, and are reserved for future use. Out of 16 possible codes, the ISD5100 Series uses 7 for normal operation. The other 9 are undefined

|     | Function | on Bits | Function |                      |

|-----|----------|---------|----------|----------------------|

| C6  | C5       | C4      | C3       |                      |

| DAB | FN2      | FN1     | FN0      |                      |

| 0   | 0        | 0       | 0        | STOP (or do nothing) |

| 0   | 1        | 0       | 1        | Analog Play          |

| 0   | 0        | 1       | 0        | Analog Record        |

| 0   | 1        | 1       | 1        | Analog MC            |

| 1   | 1        | 0       | 0        | Digital Read         |

| 1   | 0        | 0       | 1        | Digital Write        |

| 1   | 0        | 1       | 0        | Erase (row)          |

# **Register Bits**

The register load may be used to modify a command sequence (such as load an address) or used with the null command sequence to load a configuration or test register. Not all registers are accessible to the user. [RG2 is always 0 as the four additional combinations are undefined.]

| RG2 | RG1 | RG0 | Function  |

|-----|-----|-----|-----------|

| C2  | C1  | C0  |           |

| 0   | 0   | 0   | No action |

| 0   | 0   | 1   | Reserved  |

| 0   | 1   | 0   | Load CFG0 |

| 0   | 1   | 1   | Load CFG1 |

# 6.3.3 Opcode Summary

# **OpCode Command Description**

The following commands are used to access the chip through the I<sup>2</sup>C interface.

- Play: analog play command

- Record: analog record command

- Message Cue: analog message cue command

- Read: digital read command

- Write: digital write command

- Erase: digital page and block erase command

- Power up: global power up/down bit. (C7)

- Load CFG0: load configuration register 0

- Load CFG1: load configuration register 1

- Read STATUS: Read the interrupt status and address register, including a hardwired device ID

# **OPCODE COMMAND BYTE TABLE**

|                            |     | Pwr        | Function Bits |     |     |     | Re  | gister E | Bits |

|----------------------------|-----|------------|---------------|-----|-----|-----|-----|----------|------|

| OPCODE                     | HEX | PU         | DAB           | FN2 | FN1 | FN0 | RG2 | RG1      | RG0  |

| COMMAND BIT NUMBER         | CMD | <b>C</b> 7 | C6            | C5  | C4  | C3  | C2  | C1       | C0   |

|                            |     |            |               |     |     |     |     |          |      |

| POWER UP                   | 80  | 1          | 0             | 0   | 0   | 0   | 0   | 0        | 0    |

| POWER DOWN                 | 00  | 0          | 0             | 0   | 0   | 0   | 0   | 0        | 0    |

| STOP (DO NOTHING) STAY ON  | 80  | 1          | 0             | 0   | 0   | 0   | 0   | 0        | 0    |

| STOP (DO NOTHING) STAY OFF | 00  | 0          | 0             | 0   | 0   | 0   | 0   | 0        | 0    |

| LOAD CFG0                  | 82  | 1          | 0             | 0   | 0   | 0   | 0   | 1        | 0    |

| LOAD CFG1                  | 83  | 1          | 0             | 0   | 0   | 0   | 0   | 1        | 1    |

| RECORD ANALOG              | 90  | 1          | 0             | 0   | 1   | 0   | 0   | 0        | 0    |

| RECORD ANALOG @ ADDR       | 91  | 1          | 0             | 0   | 1   | 0   | 0   | 0        | 1    |

| PLAY ANALOG                | A8  | 1          | 0             | 1   | 0   | 1   | 0   | 0        | 0    |

| PLAY ANALOG @ ADDR         | A9  | 1          | 0             | 1   | 0   | 1   | 0   | 0        | 1    |

| MSG CUE ANALOG             | В8  | 1          | 0             | 1   | 1   | 1   | 0   | 0        | 0    |

| MSG CUE ANALOG @ ADDR      | В9  | 1          | 0             | 1   | 1   | 1   | 0   | 0        | 1    |

| ENTER DIGITAL MODE         | C0  | 1          | 1             | 0   | 0   | 0   | 0   | 0        | 0    |

| EXIT DIGITAL MODE          | 40  | 0          | 1             | 0   | 0   | 0   | 0   | 0        | 0    |

| DIGITAL ERASE PAGE         | D0  | 1          | 1             | 0   | 1   | 0   | 0   | 0        | 0    |

| DIGITAL ERASE PAGE @ ADDR  | D1  | 1          | 1             | 0   | 1   | 0   | 0   | 0        | 1    |

| DIGITAL WRITE              | C8  | 1          | 1             | 0   | 0   | 1   | 0   | 0        | 0    |

| DIGITAL WRITE @ ADDR       | C9  | 1          | 1             | 0   | 0   | 1   | 0   | 0        | 1    |

| DIGITAL READ               | E0  | 1          | 1             | 1   | 0   | 0   | 0   | 0        | 0    |

| DIGITAL READ @ ADDR        | E1  | 1          | 1             | 1   | 0   | 0   | 0   | 0        | 1    |

| READ STATUS <sup>1</sup>   | N/A | N/A        | N/A           | N/A | N/A | N/A | N/A | N/A      | N/A  |

|                            |     |            |               |     |     |     |     |          |      |

<sup>1.</sup> See section 7.2 on page 12 for details.

# 6.3.4 Data Bytes

In the  $I^2C$  write mode, the device can accept data sent after the command byte. If a register load option is selected, the next two bytes are loaded into the selected register. The format of the data is MSB first, the  $I^2C$  standard. Thus to load DATA<15:0> into the device, DATA<15:8> is sent first, the byte is acknowledged, and DATA<7:0> is sent next. The address register consists of two bytes. The format of the address is as follows:

ADDRESS<15:0> = PAGE ADDRESS<10:0>, BLOCK ADDRESS<4:0>

Note: if an analog function is selected, the block address bits must be set to 00000. Digital Read and Write are block addressable.

When the device is polled with the Read Status command, it will return three bytes of data. The first byte is the status byte, the next the upper address byte and the last the lower address byte. The status register is one byte long and its bit function is:

STATUS<7:0> = EOM, OVF, READY, PD, PRB, DEVICE\_ID<2:0>

Lower address byte will always return the block address bits as zero, either in digital or analog mode.

The functions of the bits are:

| EOM       | BIT 7       | Indicates whether an EOM interrupt has occurred.                                                                        |  |  |  |  |  |  |

|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| OVF       | BIT 6       | Indicates whether an overflow interrupt has occurred.                                                                   |  |  |  |  |  |  |

| READY     | BIT 5       | Indicates the internal status of the device – if READY is LOW no new commands should be sent to device, i.e. Not Ready. |  |  |  |  |  |  |

| PD        | BIT 4       | Device is powered down if PD is HIGH.                                                                                   |  |  |  |  |  |  |

| PRB       | BIT 3       | Play/Record mode indicator. HIGH=Play/LOW=Record.                                                                       |  |  |  |  |  |  |

| DEVICE_ID | BIT 0, 1, 2 | An internal device ID. ISD5116 = 001; ISD5108 = 010; ISD5104 = 100 and ISD5102 = 101.                                   |  |  |  |  |  |  |

It is recommended that you read the status register after a Write or Record operation to ensure that the device is ready to accept new commands. Depending upon the design and the number of pins available on the controller, the polling overhead can be reduced. If INT and RAC are tied to the microcontroller, it does not have to poll as frequently to determine the status of the ISD5100-SERIES.

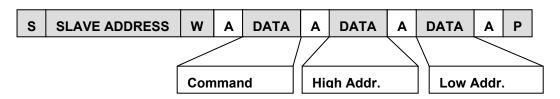

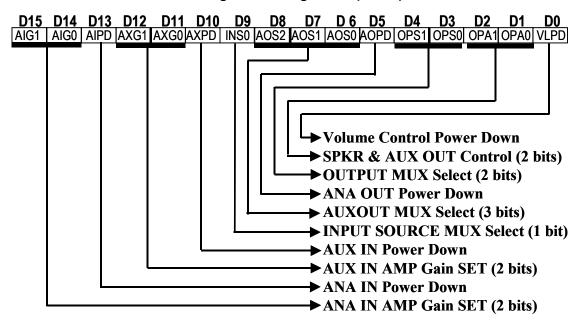

# 6.3.5 Configuration Register Bytes

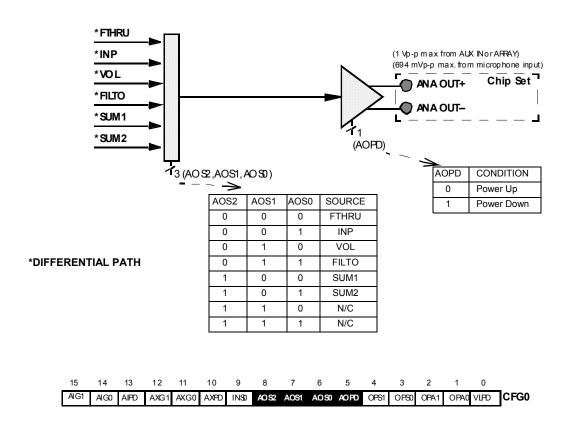

The configuration register bytes are defined, in detail, in the drawings of section 7.4 on page 29. The drawings display how each bit enables or disables a function of the audio paths in the ISD5100-Series. The tables below give a general illustration of the bits. There are two configuration registers, CFG0 and CFG1, so there are four 8-bit bytes to be loaded during the set-up of the device.

# **Configuration Register 0 (CFG0)**

# **Configuration Register 1 (CFG1)**

# 6.3.6 Power-up Sequence

This sequence prepares the ISD5100 Series for an operation to follow, waiting the Tpud time before sending the next command sequence.

- Send I<sup>2</sup>C POWER UP

- 2. Send one byte 10000000 {Slave Address, R/W = 0} 80h

- 3. Slave ACK

- 4. Wait for SCL High

- 5. Send one byte 10000000 (Command Byte = Power Up) 80h

- 6. Slave ACK

- 7. Wait for SCL High

- 8. Send I<sup>2</sup>C STOP

# **Playback Mode**

The command sequence for an analog Playback operation can be handled several ways. The most straightforward approach would be to incorporate a single four byte exchange, which consists of the Slave Address (80h), the Command Byte (A9h) for Play Analog @ Address, and the two address bytes.

#### **Record Mode**

The command sequence for an Analog Record would be a four byte sequence consisting of the Slave Address (80h), the Command Byte (91h) for Record Analog @ Address, and the two address bytes. See <u>"Load Command Byte Register (Address Load)" in section 7.3.2</u> on page 17.

#### 6.3.7 Feed Through Mode

The previous examples were dependent upon the device already being powered up and the various paths being set through the device for the desired operation. To set up the device for the various paths requires loading the two 16-bit Configuration Registers with the correct data. For example, in the Feed Through Mode the device only needs to be powered up and a few paths selected.

This mode enables the ISD5100 Series to connect to a cellular or cordless base band phone chip set without affecting the audio source or destination. There are two paths involved, the transmit path and the receive path. The transmit path connects the Nuvoton chip's microphone source through to the microphone input on the base band chip set. The receive path connects the base band chip set's speaker output through to the speaker driver on the Nuvoton chip. This allows the Nuvoton chip to substitute for those functions and incidentally gain access to the audio to and from the base band chip set.

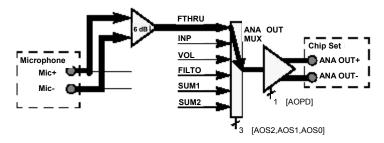

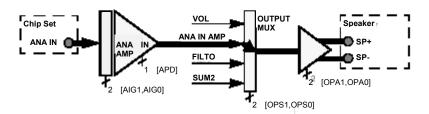

To set up the environment described above, a series of commands need to be sent to the ISD5100-Series. First, the chip needs to be powered up as described in this section. Then the Configuration Registers must be filled with the specific data to connect the paths desired. In the case of the Feed Through Mode, most of the chip can remain powered down. The following figure illustrates the affected paths.

The figure above shows the part of the ISD5100 Series block diagram that is used in Feed Through Mode. The rest of the chip will be powered down to conserve power. The bold lines highlight the audio paths. Note that the Microphone to ANA OUT +/- path is differential.

# nuvoton

To select this mode, the following control bits must be configured in the ISD5100 Series configuration registers. To set up the transmit path:

- 1. Select the FTHRU path through the ANA OUT MUX—Bits AOS0, AOS1 and AOS2 control the state of the ANA OUT MUX. These are the D6, D7 and D8 bits respectively of Configuration Register 0 (CFG0) and they should all be ZERO to select the FTHRU path.

- 2. Power up the ANA OUT amplifier—Bit AOPD controls the power up state of ANA OUT. This is bit D5 of CFG0 and it should be a ZERO to power up the amplifier.

#### To set up the receive path:

- 1. Set up the ANA IN amplifier for the correct gain—Bits AIG0 and AIG1 control the gain settings of this amplifier. These are bits D14 and D15 respectively of CFG0. The input level at this pin determines the setting of this gain stage. The <u>ANA IN Amplifier Gain Settings table</u> on page 36 will help determine this setting. In this example, we will assume that the peak signal never goes above 1 volt p-p single ended. That would enable us to use the 9 dB attenuation setting, or where D14 is ONE and D15 is ZERO.

- 2. Power up the ANA IN amplifier—Bit AIPD controls the power up state of ANA IN. This is bit D13 of CFG0 and should be a ZERO to power up the amplifier.

- 3. Select the ANA IN path through the OUTPUT MUX—Bits OPS0 and OPS1 control the state of the OUTPUT MUX. These are bits D3 and D4 respectively of CFG0 and they should be set to the state where D3 is ONE and D4 is ZERO to select the ANA IN path.

- 4. Power up the Speaker Amplifier—Bits OPA0 and OPA1 control the state of the Speaker and AUX amplifiers. These are bits D1 and D2 respectively of CFG0. They should be set to the state where D1 is ONE and D2 is ZERO. This powers up the Speaker Amplifier and configures it for its higher gain setting for use with a piezo speaker element and also powers down the AUX output stage.

The status of the rest of the functions in the ISD5100 Series chip must be defined before the configuration registers settings are updated:

- Power down the Volume Control Element—Bit VLPD controls the power up state of the Volume Control. This is bit D0 of CFG0 and it should be set to a ONE to power down this stage.

- 2. Power down the AUX IN amplifier—Bit AXPD controls the power up state of the AUX IN input amplifier. This is bit D10 of CFG0 and it should be set to a ONE to power down this stage.

- 3. Power down the SUM1 and SUM2 Mixer amplifiers—Bits S1M0 and S1M1 control the SUM1 mixer and bits S2M0 and S2M1 control the SUM2 mixer. These are bits D7 and D8 in CFG1 and bits D5 and D6 in CFG1 respectively. All 4 bits should be set to a ONE to power down these two amplifiers.

- 4. Power down the FILTER stage—Bit FLPD controls the power up state of the FILTER stage in the device. This is bit D1 in CFG1 and should be set to a ONE to power down the stage.

- 5. Power down the AGC amplifier—Bit AGPD controls the power up state of the AGC amplifier. This is bit D0 in CFG1 and should be set to a ONE to power down this stage.

Publication Release Date: Oct 31, 2008 Revision 1.42

- 23 -

# nuvoton

6. Don't Care bits—The following stages are not used in Feed Through Mode. Their bits may be set to either level. In this example, we will set all the following bits to a ZERO. (a). Bit INSO, bit D9 of CFG0 controls the Input Source Mux. (b). Bits AXG0 and AXG1 are bits D11 and D12 respectively in CFG0. They control the AUX IN amplifier gain setting. (c). Bits FLD0 and FLD1 are bits D2 and D3 respectively in CFG1. They control the sample rate and filter band pass setting. (d). Bit FLS0 is bit D4 in CFG1. It controls the FILTER MUX. (e). Bits S1S0 and S1S1 are bits D9 and D10 of CFG1. They control the SUM1 MUX. (f). Bits VOL0, VOL1 and VOL2 are bits D11, D12 and D13 of CFG1. They control the setting of the Volume Control. (g). Bits VLS0 and VLS1 are bits D14 and D15 of CFG1. They control the Volume Control MUX.

The end result of the above set up is

CFG0=0100 0100 0000 1011 (hex 440B)

and

CFG1=0000 0001 1110 0011 (hex 01E3).

Since both registers are being loaded, CFG0 is loaded, followed by the loading of CFG1. These two registers must be loaded in this order. The internal set up for both registers will take effect synchronously with the rising edge of SCL.

#### 6.3.8 Call Record

The call record mode adds the ability to record an incoming phone call. In most applications, the ISD5100 Series would first be set up for Feed Through Mode as described above. When the user wishes to record the incoming call, the setup of the chip is modified to add that ability. For the purpose of this explanation, we will use the 6.4 kHz sample rate during recording.

The block diagram of the ISD5100 Series shows that the Multilevel Storage array is always driven from the SUM2 SUMMING amplifier. The path traces back from there through the LOW PASS Filter, THE FILTER MUX, THE SUM1 SUMMING amplifier, the SUM1 MUX, then from the ANA in amplifier. Feed Through Mode has already powered up the ANA IN amp so we only need to power up and enable the path to the Multilevel Storage array from that point:

- 1. Select the ANA IN path through the SUM1 MUX—Bits S1S0 and S1S1 control the state of the SUM1 MUX. These are bits D9 and D10 respectively of CFG1 and they should be set to the state where both D9 and D10 are ZERO to select the ANA IN path.

- Select the SUM1 MUX input (only) to the S1 SUMMING amplifier—Bits S1M0 and S1M1 control the state of the SUM1 SUMMING amplifier. These are bits D7 and D8 respectively of CFG1 and they should be set to the state where D7 is ONE and D8 is ZERO to select the SUM1 MUX (only) path.

# nuvoton

- 3. Select the SUM1 SUMMING amplifier path through the FILTER MUX—Bit FLS0 controls the state of the FILTER MUX. This is bit D4 of CFG1 and it must be set to ZERO to select the SUM1 SUMMING amplifier path.

- 4. Power up the LOW PASS FILTER—Bit FLPD controls the power up state of the LOW PASS FILTER stage. This is bit D1 of CFG1 and it must be set to ZERO to power up the LOW PASS FILTER STAGE.

- 5. Select the 6.4 kHz sample rate—Bits FLD0 and FLD1 select the Low Pass filter setting and sample rate to be used during record and playback. These are bits D2 and D3 of CFG1. To enable the 6.4 kHz sample rate, D2 must be set to ONE and D3 set to ZERO.

- Select the LOW PASS FILTER input (only) to the S2 SUMMING amplifier—Bits S2M0 and S2M1 control the state of the SUM2 SUMMING amplifier. These are bits D5 and D6 respectively of CFG1 and they should be set to the state where D5 is ZERO and D6 is ONE to select the LOW PASS FILTER (only) path.

In this mode, the elements of the original PASS THROUGH mode do not change. The sections of the chip not required to add the record path remain powered down. In fact, CFG0 does not change and remains

CFG0=0100 0100 0000 1011 (hex 440B).

CFG1 changes to

CFG1=0000 0000 1100 0101 (hex 00C5).

Since CFG0 is not changed, it is only necessary to load CFG1. Note that if only CFG0 was changed, it would be necessary to load both registers.

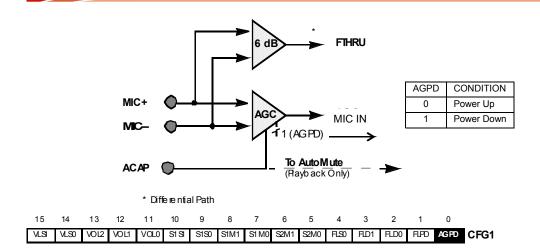

# 6.3.9 Memo Record

The Memo Record mode sets the chip up to record from the local microphone into the chip's Multilevel Storage Array. A connected cellular telephone or cordless phone chip set may remain powered down and is not active in this mode. The path to be used is microphone input to AGC amplifier, then through the INPUT SOURCE MUX to the SUM1 SUMMING amplifier. From there the path goes through the FILTER MUX, the LOW PASS FILTER, the SUM2 SUMMING amplifier, then to the MULTILEVEL STORAGE ARRAY. In this instance, we will select the 5.3 kHz sample rate. The rest of the chip may be powered down.

- Power up the AGC amplifier—Bit AGPD controls the power up state of the AGC amplifier. This

is bit D0 of CFG1 and must be set to ZERO to power up this stage.

- 2. Select the AGC amplifier through the INPUT SOURCE MUX—Bit INS0 controls the state of the INPUT SOURCE MUX. This is bit D9 of CFG0 and must be set to a ZERO to select the AGC amplifier.

- 3. Select the INPUT SOURCE MUX (only) to the S1 SUMMING amplifier—Bits S1M0 and S1M1 control the state of the SUM1 SUMMING amplifier. These are bits D7 and D8 respectively of CFG1 and they should be set to the state where D7 is ZERO and D8 is ONE to select the INPUT SOURCE MUX (only) path.

# nuvoTon

- 4. Select the SUM1 SUMMING amplifier path through the FILTER MUX—Bit FLS0 controls the state of the FILTER MUX. This is bit D4 of CFG1 and it must be set to ZERO to select the SUM1 SUMMING amplifier path.

- 5. Power up the LOW PASS FILTER—Bit FLPD controls the power up state of the LOW PASS FILTER stage. This is bit D1 of CFG1 and it must be set to ZERO to power up the LOW PASS FILTER STAGE.

- 6. Select the 5.3 kHz sample rate—Bits FLD0 and FLD1 select the Low Pass filter setting and sample rate to be used during record and playback. These are bits D2 and D3 of CFG1. To enable the 5.3 kHz sample rate, D2 must be set to ZERO and D3 set to ONE.

- 7. Select the LOW PASS FILTER input (only) to the S2 SUMMING amplifier—Bits S2M0 and S2M1 control the state of the SUM2 SUMMING amplifier. These are bits D5 and D6 respectively of CFG1 and they should be set to the state where D5 is ZERO and D6 is ONE to select the LOW PASS FILTER (only) path.

To set up the chip for Memo Record, the configuration registers are set up as follows:

CFG0=0010 0100 0010 0001 (hex 2421).

CFG1=0000 0001 0100 1000 (hex 0148).

Only those portions necessary for this mode are powered up.

# 6.3.10 Memo and Call Playback

This mode sets the chip up for local playback of messages recorded earlier. The playback path is from the MULTILEVEL STORAGE ARRAY to the FILTER MUX, then to the LOW PASS FILTER stage. From there, the audio path goes through the SUM2 SUMMING amplifier to the VOLUME MUX, through the VOLUME CONTROL then to the SPEAKER output stage. We will assume that we are driving a piezo speaker element. This audio was previously recorded at 8 kHz. All unnecessary stages will be powered down.

- Select the MULTILEVEL STORAGE ARRAY path through the FILTER MUX—Bit FLS0, the state of the FILTER MUX. This is bit D4 of CFG1 and must be set to ONE to select the MULTILEVEL STORAGE ARRAY.

- 2. Power up the LOW PASS FILTER—Bit FLPD controls the power up state of the LOW PASS FILTER stage. This is bit D1 of CFG1 and it must be set to ZERO to power up the LOW PASS FILTER STAGE.

- 3. Select the 8.0 kHz sample rate—Bits FLD0 and FLD1 select the Low Pass filter setting and sample rate to be used during record and playback. These are bits D2 and D3 of CFG1. To enable the 8.0 kHz sample rate, D2 and D3 must be set to ZERO.

- 4. Select the LOW PASS FILTER input (only) to the S2 SUMMING amplifier —Bits S2M0 and S2M1 control the state of the SUM2 SUMMING amplifier. These are bits D5 and D6 respectively of CFG1 and they should be set to the state where D5 is ZERO and D6 is ONE to select the LOW PASS FILTER (only) path.

# nuvoTon

- Select the SUM2 SUMMING amplifier path through the VOLUME MUX—Bits VLS0 and VLS1 control the state VOLUME MUX. These bits are bits D14 and D15, respectively of CFG1. They should be set to the state where D14 is ONE and D15 is ZERO to select the SUM2 SUMMING amplifier.

- 6. Power up the VOLUME CONTROL LEVEL—Bit VLPD controls the power-up state of the VOLUME CONTROL attenuator. This is Bit D0 of CFG0. This bit must be set to a ZERO to power-up the VOLUME CONTROL.

- 7. Select a VOLUME CONTROL LEVEL—Bits VOL0, VOL1, and VOL2 control the state of the VOLUME CONTROL LEVEL. These are bits D11, D12, and D13, respectively, of CFG1. A binary count of 000 through 111 controls the amount of attenuation through that state. In most cases, the software will select an attenuation level according to the desires of the current users of the product. In this example, we will assume the user wants an attenuation of –12 dB. For that setting, D11 should be set to ONE, D12 should be set to ONE, and D13 should be set to a ZERO.

- 8. Select the VOLUME CONTROL path through the OUTPUT MUX—These are bits D3 and D4, respectively, of CFG0. They should be set to the state where D3 is ZERO and D4 is a ZERO to select the VOLUME CONTROL.

- 9. Power up the SPEAKER amplifier and select the HIGH GAIN mode—Bits OPA0 and OPA1 control the state of the speaker (SP+ and SP-) and AUX OUT outputs. These are bits D1 and D2 of CFG0. They must be set to the state where D1 is ONE and D2 is ZERO to power-up the speaker outputs in the HIGH GAIN mode and to power-down the AUX OUT.

To set up the chip for Memo or Call Playback, the configuration registers are set up as follows:

CFG0=0010 0100 0010 0100 (hex 2424).

CFG1=0101 1001 1101 0001 (hex 59D1).

Only those portions necessary for this mode are powered up.

# 6.3.11 Message Cueing

Message cueing allows the user to skip through analog messages without knowing the actual physical location of the message. This operation is used during playback. In this mode, the messages are skipped 512 times faster than in normal playback mode. It will stop when an EOM marker is reached. Then, the internal address counter will be pointing to the next message.

Publication Release Date: Oct 31, 2008 Revision 1.42

- 27 -

#### 6.4. ANALOG MODE

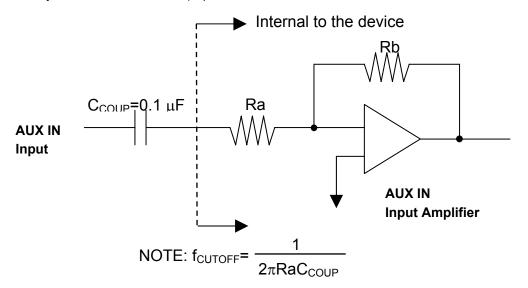

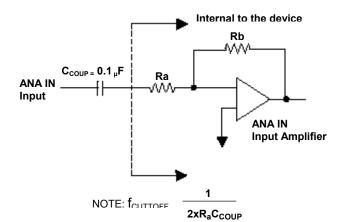

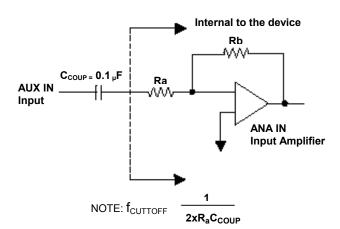

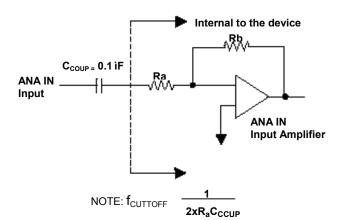

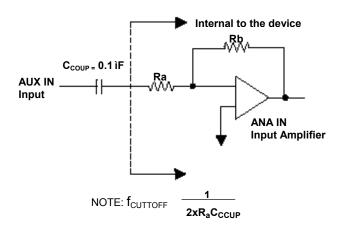

# 6.4.1 Aux In and Ana In Description

The AUX IN is an additional audio input to the ISD5100-Series, such as from the microphone circuit in a mobile phone "car kit." This input has a nominal 694 mV p-p level at its minimum gain setting (0 dB). See the <u>AUX IN Amplifier Gain Settings table</u> on page 37. Additional gain is available in 3 dB steps (controlled by the I<sup>2</sup>C serial interface) up to 9 dB.

The ANA IN pin is the analog input from the telephone chip set. It can be switched (by the serial bus) to the speaker output, the array input or to various other paths. This pin is designed to accept a nominal 1.11 Vp-p when at its minimum gain (6 dB) setting. See the **ANA IN Amplifier Gain Settings** table on page 37. There is additional gain available in 3 dB steps controlled from the I<sup>2</sup>C interface, if required, up to 15 dB.

# 6.4.2 ISD5100 Series Analog Structure (left half) Description

# 6.4.3 ISD5100 Series Aanalog Structure (right half) Description

# 6.4.4 Volume Control Description

| AlG1 | AIG0 | AIPD | AXG1 | AXG0 | AXPD  | INS0 | AOS2 | AOS1  | AOS0 | AOPD | OPS1 | OPS0 | OPA1 | OPA0 | VLPD | CFG0 |

|------|------|------|------|------|-------|------|------|-------|------|------|------|------|------|------|------|------|

| 15   | 14   | 13   | 12   | 11   | 10    | 9    | 8    | 7     | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

| VLS1 | VLS0 | VOI2 | VOL1 | νош  | SI S1 | S1S0 | S1M1 | 31 M0 | S2M1 | S2M0 | FLS0 | FLD1 | FLD0 | FLPD | AGPD | CFG1 |

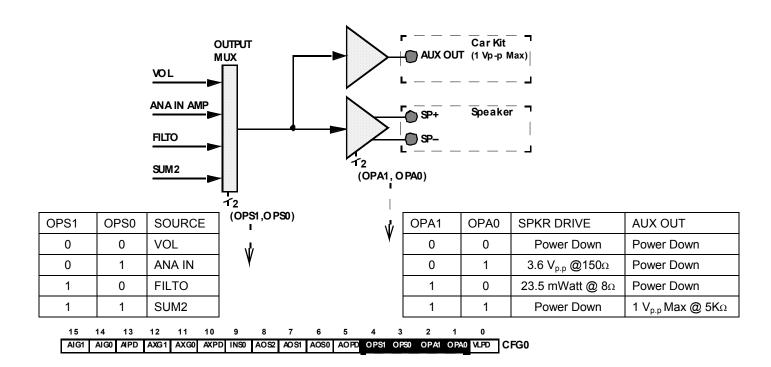

# 6.4.5 Speaker and Aux Out Description

| 15   | 14   | 13  | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|------|------|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| AlG1 | AIG0 | APD | AXG1 | AXG0 | AXPD | INS0 | AOS2 | AOS1 | AOS0 | AOPD | OPS1 | OPS) | OPA1 | OPA0 | VLPD | CFG0 |

# 6.4.6 Ana Out Description

# 6.4.7 Analog Inputs

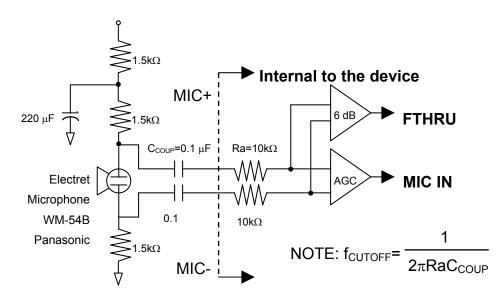

#### **Microphone Inputs**

The microphone inputs transfer the voice signal to the on-chip AGC preamplifier or directly to the ANA OUT MUX, depending on the selected path. The direct path to the ANA OUT MUX has a gain of 6 dB so a 208 mV p-p signal across the differential microphone inputs would give 416 mV p-p across the ANA OUT pins. The AGC circuit has a range of 45 dB in order to deliver a nominal 694 mV p-p into the storage array from a typical electric microphone output of 2 to 20 mV p-p. The input impedance is typically  $10k\Omega$ .

The ACAP pin provides the capacitor connection for setting the parameters of the microphone AGC circuit. It should have a 4.7  $\mu$ F capacitor connected to ground. It cannot be left floating. This is because the capacitor is also used in the playback mode for the AutoMute circuit. This circuit reduces the amount of noise present in the output during quiet pauses. Tying this pin to ground gives maximum gain; to VCCA gives minimum gain for the AGC amplifier but will cancel the AutoMute function.

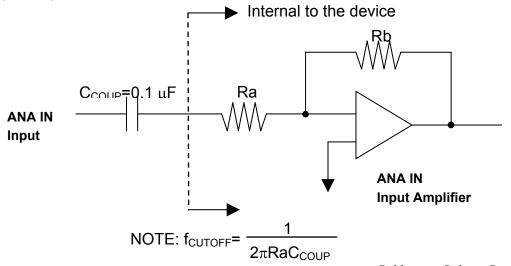

# **ANA IN (Analog Input)**

The ANA IN pin is the analog input from the telephone chip set. It can be switched (by the  $I^2C$  interface) to the speaker output, the array input or to various other paths. This pin is designed to accept a nominal 1.11 V p-p when at its minimum gain (6 dB) setting. There is additional gain available, if required, in 3 dB steps, up to 15 dB. The gain settings are controlled from the  $I^2C$  interface.

| Gain<br>Setting | Resistor Ratio<br>(Rb/Ra) | Gain  | Gain <sup>2</sup><br>(dB) |

|-----------------|---------------------------|-------|---------------------------|

| 00              | 63.9 / 102                | 0.625 | -4.1                      |

| 01              | 77.9 / 88.1               | 0.883 | -1.1                      |

| 10              | 92.3 / 73.8               | 1.250 | 1.9                       |

| 11              | 106 / 60                  | 1.767 | 4.9                       |

Note: Ra & Rb are in  $k\Omega$

# **ANA IN Amplifier Gain Settings**

| Setting <sup>(1)</sup> | OTLP Input      | CF   | G0   | Gain <sup>(2)</sup> | Array                   | Speaker                             |

|------------------------|-----------------|------|------|---------------------|-------------------------|-------------------------------------|

|                        | $V_{P-P}^{(3)}$ | AIG1 | AIG0 |                     | In/Out V <sub>P-P</sub> | Out V <sub>P-P</sub> <sup>(4)</sup> |

| 6 dB                   | 1.110           | 0    | 0    | 0.625               | 0.694                   | 2.22                                |

| 9 dB                   | 0.785           | 0    | 1    | 0.883               | 0.694                   | 2.22                                |

| 12 dB                  | 0.555           | 1    | 0    | 1.250               | 0.694                   | 2.22                                |

| 15 dB                  | 0.393           | 1    | 1    | 1.767               | 0.694                   | 2.22                                |

- 1. Gain from ANA IN to SP+/-

- 2. Gain from ANA IN to ARRAY IN

- 3. OTLP Input is the reference Transmission Level Point that is used for testing. This level is typically 3 dB below clipping

- 4. Speaker Out gain set to 1.6 (High). (Differential)

# **AUX IN (Auxiliary Input)**

The AUX IN is an additional audio input to the ISD5100-Series, such as from the microphone circuit in a mobile phone "car kit." This input has a nominal 694 mV p-p level at its minimum gain setting (0 dB). See the following table. Additional gain is available in 3 dB steps (controlled by the I<sup>2</sup>C interface) up to 9 dB.

# **AUX IN Input Modes**

| Gain<br>Setting | Resistor Ratio<br>(Rb/Ra) | Gain  | Gain <sup>(2)</sup><br>(dB) |

|-----------------|---------------------------|-------|-----------------------------|

| 00              | 40.1 / 40.1               | 1.0   | 0                           |

| 01              | 47.0 / 33.2               | 1.414 | 3                           |

| 10              | 53.5 / 26.7               | 2.0   | 6                           |

| 11              | 59.2 / 21                 | 2.82  | 9                           |

Note: Ra & Rb are in  $k\Omega$

# **AUX IN Amplifier Gain Settings**

| Setting <sup>(1)</sup> | 0TLP Input      | CF   | G0   | Gain <sup>(2)</sup> | Array                   | Speaker                             |

|------------------------|-----------------|------|------|---------------------|-------------------------|-------------------------------------|

|                        | $V_{P-P}^{(3)}$ | AXG1 | AXG0 |                     | In/Out V <sub>P-P</sub> | Out V <sub>P-P</sub> <sup>(4)</sup> |

| 0 dB                   | 0.694           | 0    | 0    | 1.00                | 0.694                   | 0.694                               |

| 3 dB                   | 0.491           | 0    | 1    | 1.41                | 0.694                   | 0.694                               |

| 6 dB                   | 0.347           | 1    | 0    | 2.00                | 0.694                   | 0.694                               |

| 9 dB                   | 0.245           | 1    | 1    | 2.82                | 0.694                   | 0.694                               |

- 1. Gain from AUX IN to ANA OUT

- 2. Gain from AUX IN to ARRAY IN

- 3. OTLP Input is the reference Transmission Level Point that is used for testing. This level is typically 3 dB below clipping

- 4. Differential

#### 6.5. DIGITAL MODE

# 6.5.1 Erasing Digital Data

The Digital Erase command can only erase an entire page at a time. This means that the D1 command only needs to include the 11-bit page address; the 5-bit for block address are left at 00000.

Once a page has been erased, each block may be written separately, 64 bits at a time. But, if a block has been previously written then the entire page of 2048 bits must be erased in order to re-write (or change) a block.

A sequence might be look like:

- read the entire page

- store it in RAM

- change the desired bit(s)

- erase the page

- write the new data from RAM to the entire page

# 6.5.2 Writing Digital Data

The Digital Write function allows the user to select a portion of the array to be used as digital memory. The partition between analog and digital memory is left up to the user. A page can only be either Digital or Analog, but not both. The minimum addressable block of memory in the digital mode is one block or 64 bits, when reading or writing. The address sent to the device is the 11-bit row (or page) address with the 5-bit scan (or block) address. However, one must send a Digital Erase before attempting to change digital data on a page. This means that even when changing only one of the 32 blocks, all 32 blocks will need to be rewritten to the page. Command Sequence: The chip enters digital mode by sending the ENTER DIGITAL MODE command from power down. Send the DIGITAL WRITE @ ADDR command with the row address. After the address is entered, the data is sent in one-byte packets followed by an I<sup>2</sup>C acknowledge generated by the chip. Data for each block is sent MSB first. The data transfer is ended when the master generates an I<sup>2</sup>C STOP condition. If only a partial block of data is sent before the STOP condition, "zero" is written in the remaining bytes; that is, they are left at the erase level. An erased page (row) will be read as all zeros. The device can buffer up to two blocks of data. If the device is unable to accept more data due to the internal write process, the SCL line will be held LOW indicating to the master to halt data transfer. If the device encounters an overflow condition, it will respond by generating an interrupt condition and an I<sup>2</sup>C Not Acknowledge signal after the last valid byte of data. Once data transfer is terminated, the device needs up to two cycles (64 us) to complete its internal write cycle before another command is sent. If an active command is sent before the internal cycle is finished, the part will hold SCL LOW until the current command is finished. After writing is complete, send the EXIT DIGITAL MODE command.

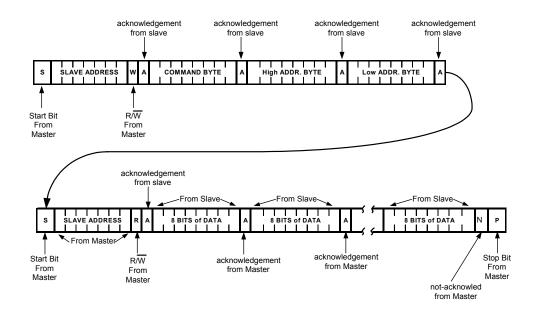

#### 6.5.3 Reading Digital Data

The Digital Read command utilizes the combined  $I^2C$  command format. That is, a command is sent to the chip using the write data direction. Then the data direction is reversed by sending a repeated start condition, and the slave address with R/W set to 1. After this, the slave device (ISD5100-Series) begins to send data to the master until the master generates a NACK. If the part encounters an overflow condition, the  $\overline{INT}$  pin is pulled LOW. No other communication with the master is possible due to the master generating ACK signals.

Digital Write and Digital Read can be done a "block" at a time. Thus, only 64 bits need be read in each Digital Read command sequence.

#### 6.5.4 Example Command Sequences

An explanation and graphical representation of the Erase, Write and Read operations are found below.

Note: All sequences assumes that the chip is in power-down mode before the commands are sent.

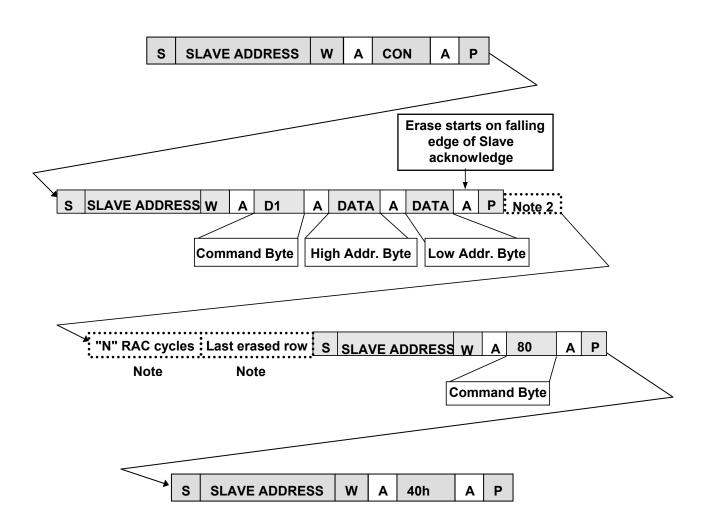

#### 6.5.4.1. Erase Digital Data

**Erase**

=====

**I2CStart**

SendByte(0x80) - Write, Slave address zero

WaitACK

WaitSCLHigh

SendByte(0xc0) - Enter Digital Mode Command

WaitACK

WaitSCLHigh

**I2CStop**

**I2CStart**

SendByte(0x80) - Write, Slave address zero

WaitACK

WaitSCLHigh

SendByte(0xd1) - Digital Erase Command

WaitACK

WaitSCLHigh

Publication Release Date: Oct 31, 2008

#### nuvoton

```

SendByte(row/256) - high address byte

WaitACK

WaitSCLHigh

SendByte(row%256) - low address byte

WaitACK

WaitSCLHigh

I2CStop

repeat until the number of RAC pulses are one less

than the number of rows to delete

{

wait RAC low

WAIT RAC high

}

Note: If only one row is going to be erased,

send the following STOP command immediately after

ERASE command and skip the loop above

I2CStart

SendByte(0x80)

- Write, Slave address zero

WaitACK

WaitSCLHigh

SendByte(0xc0)

- Stop digital erase

WaitACK

WaitSCLHigh

I2CStop

wait until erase of the last row has completed

wait RAC low

WAIT RAC high

}

I2CStart

SendByte(0x80)

- Write, Slave address zero

```

WaitACK

WaitSCLHigh

SendByte(0x40)

- Exit Digital Mode Command

WaitACK

WaitSCLHigh

I2Cstop

#### Notes

- 1. Erase operations must be addressed on a Row boundary. The 5 LSB bits of the Low Address Byte will be ignored.

- 2. I<sup>2</sup>C bus is released while erase proceeds. Other devices may use the bus until it is time to execute the STOP command that causes the end of the Erase operation.

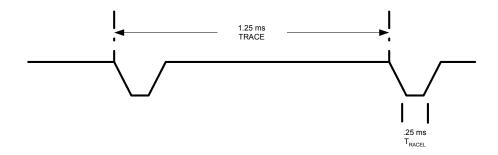

- Host processor must count RAC cycles to determine where the chip is in the erase process, one row per RAC cycle. RAC pulses LOW for 0.25 millisecond at the end of each erased row. The erase of the "next" row begins with the rising edge of RAC. See the <u>Digital Erase</u> <u>RAC</u> timing diagram on page 51.

- 4. When the erase of the last desired row begins, the following STOP command (Command Byte = 80 hex) must be issued. This command must be completely given, including receiving the ACK from the Slave before the RAC pin goes HIGH at the end of the row.

#### nuvoton

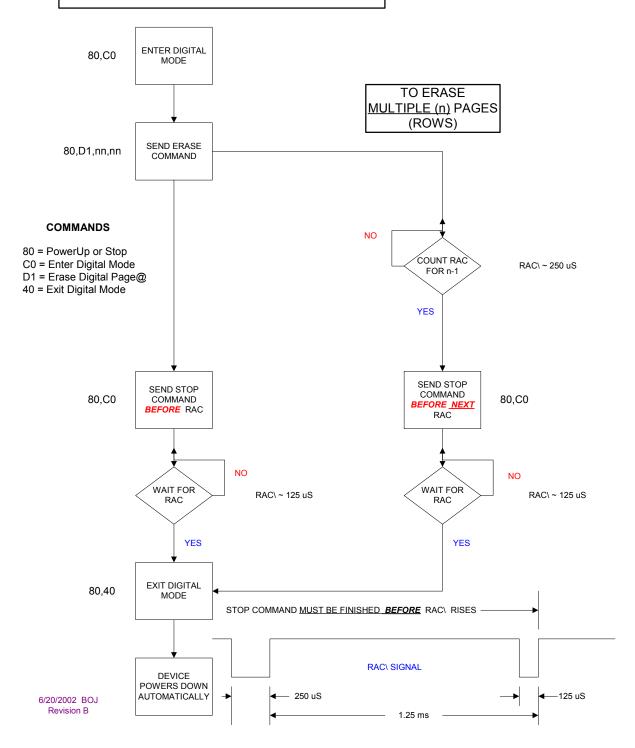

# SUGGESTED FLOW FOR DIGITAL ERASE IN ISD5100-Series

### 6.5.4.2. Write Digital Data

```

Write

=====

I2CStart

SendByte(0x80)

- Write, Slave address zero

WaitACK

WaitSCLHigh

SendByte(0xc0)

- Enter Digital Mode Command

WaitACK

WaitSCLHigh

I2CStop

I2CStart

SendByte(0x80)

- Write, Slave address zero

WaitACK

WaitSCLHigh

SendByte(0xc9)

- Write Digital Data Command

WaitACK

WaitSCLHigh

SendByte(row/256)

- high address byte

WaitACK

WaitSCLHigh

SendByte(row%256)

- low address byte

WaitACK

WaitSCLHigh

repeat until all data is sent

{

SendByte(data) - send data byte

WaitACK()

WaitSCLHigh()

}

I2CStop

```

## nuvoTon

**I2CStart**

SendByte(0x80) - Write, Slave address zero

WaitACK

WaitSCLHigh

SendByte(0x40)

- Exit Digital Mode Command

WaitACK

WaitSCLHigh

**I2CStop**

## nuvoton

### SUGGESTED FLOW FOR DIGITAL WRITE IN ISD5100-Series

COMMANDS

80 = PowerUp or Stop C0 = Enter Digital Mode C9 = Write Digital Page@

40 = Exit Digital Mode

6/24/2002 BOJ Revision N/C

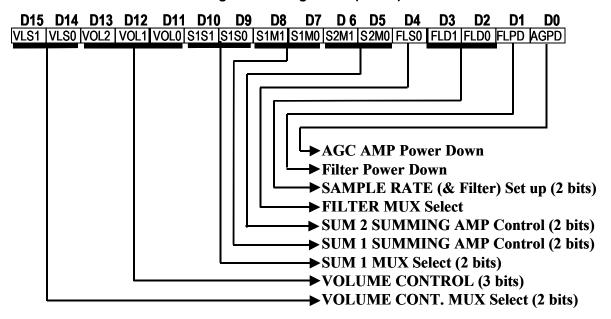

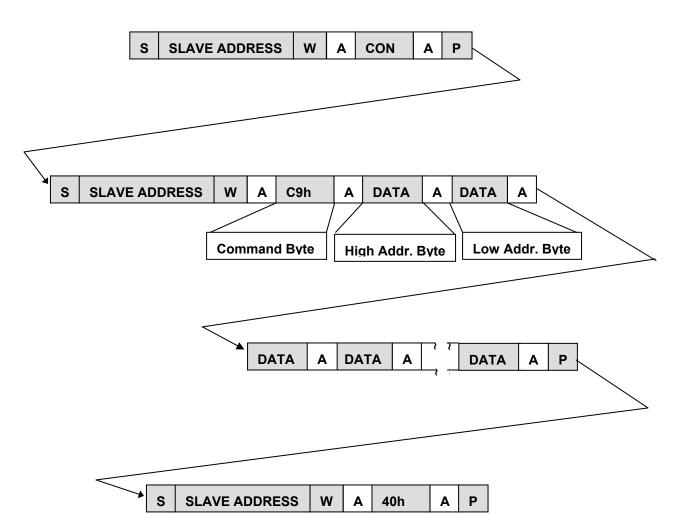

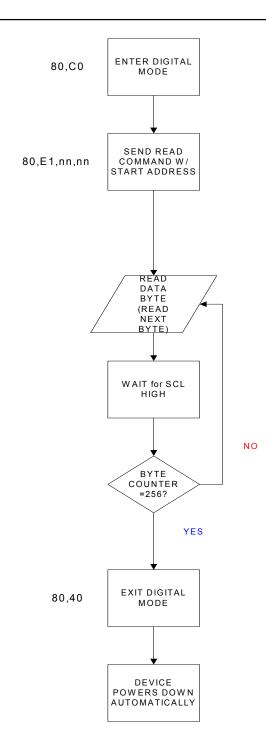

### 6.5.4.3. Read Digital Data

```

Read

=====

I2CStart

SendByte(0x80)

- Write, Slave address zero

WaitACK

WaitSCLHigh

SendByte(0xc0)

- Enter Digital Mode

WaitACK

WaitSCLHigh

I2CStop

I2CStart

SendByte(0x80)

- Write, Slave address zero

WaitACK

WaitSCLHigh

SendByte(0xe1)

- Read Digital Data Command

WaitACK

WaitSCLHigh

SendByte(row/256)

- high address byte

WaitACK

WaitSCLHigh()

SendByte(row%256)

- low address byte

WaitACK

WaitSCLHigh

I2CStart

- Send repeat start command

SendByte(0x81)

- Read, Slave address zero

repeat until all data is read

{

data = ReadByte()

- send clocks to read data byte

SendACK

- send NACK on the last byte

WaitSCLHigh

- The only flow control available

```

#### nuvoton

} I2CStop() **I2CStart** SendByte(0x80) - Write, Slave address zero WaitACK WaitSCLHigh SendByte(0x40) - Exit Digital Mode WaitACK WaitSCLHigh **I2CStop** CON S **SLAVE ADDRESS** W Α Α Ρ W **SLAVE ADDRESS** S **DATA** Α E1h Α **DATA Command Byte** High Addr. Byte Low Addr. Byte **SLAVE ADDRESS** R **DATA DATA DATA** Р **SLAVE ADDRESS** W Ρ 40h Α

## nuvoton

COMMANDS

80 = PowerUp or Stop

C0 = Enter Digital Mode

E1 = Read Digital Page@

40 = Exit Digital Mode

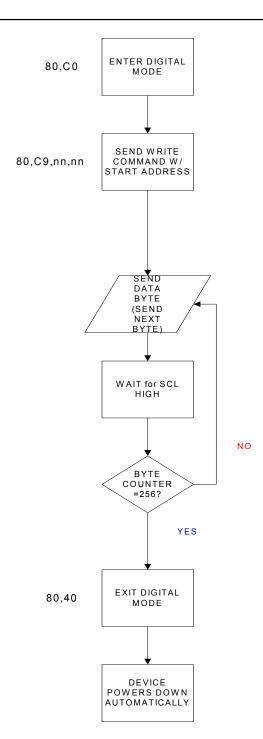

### SUGGESTED FLOW FOR DIGITAL READ IN ISD5100-Series

6/24/2002 BOJ Revision N/C

#### 6.6. PIN DETAILS

#### 6.6.1 Digital I/O Pins

#### SCL (Serial Clock Line)

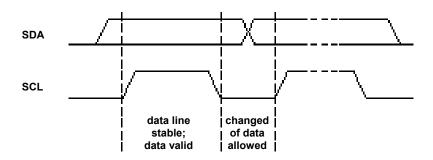

The Serial Clock Line is a bi-directional clock line. It is an open-drain line requiring a pull-up resistor to Vcc. It is driven by the "master" chips in a system and controls the timing of the data exchanged over the Serial Data Line.

#### SDA (Serial Data Line)

The Serial Data Line carries the data between devices on the I<sup>2</sup>C interface. Data must be valid on this line when the SCL is HIGH. State changes can only take place when the SCL is LOW. This is a bi-directional line requiring a pull-up resistor to Vcc.

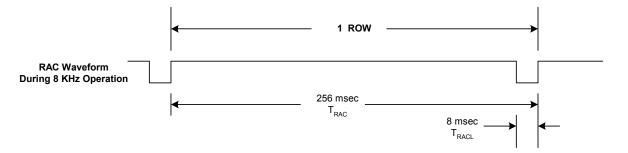

#### **RAC (Row Address Clock)**

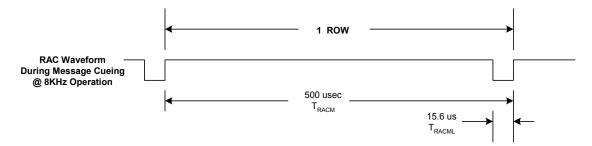

RAC is an open drain output pin that normally marks the end of a row. At the 8 kHz sample frequency, the duration of this period is 256 ms. RAC stays HIGH for 248 ms and stays LOW for the remaining 8 ms before it reaches the end of a row. There are 2048 rows of memory in the ISD5116 devices, 1024 rows in the ISD5108, 512 rows in the ISD5104 and 256 rows in the ISD5102.

The RAC pin remains HIGH for 500  $\mu$ sec and stays LOW for 15.6  $\mu$ sec under the Message Cueing mode. See the <u>Timing Parameters table</u> on page 64 for RAC timing information at other sample rates. When a record command is first initiated, the RAC pin remains HIGH for an extra T<sub>RACML</sub> period, to load sample and hold circuits internal to the device. The RAC pin can be used for message management techniques.

#### RAC Waveform During Digital Erase @ 8kHz Operation

#### INT (Interrupt)

INT is an open drain output pin. The ISD5100 Series interrupt pin goes LOW and stays LOW when an Overflow (OVF) or End of Message (EOM) marker is detected. Each operation that ends in an EOM or OVF generates an interrupt, including the message cueing cycles. The interrupt is cleared by a READ STATUS instruction that will give a status byte out the SDA line.

#### XCLK (External Clock Input)

This is the external clock input. To use internal clock, this pin must be grounded (suggest connecting to  $V_{SSD}$ ). While in internal clock mode, the ISD5100 Series are operated at one of four internal rates selected for its internal oscillator by the Sample Rate Select bits. For precision timing control, external clock signal can be applied through this pin. In the external clock mode, the device can be clocked through the XCLK pin at 4.096 MHz as described in section 7.4.3 on page 32.

Because the anti-aliasing and smoothing filters track the Sample Rate Select bits, one must, for optimum performance, maintain the external clock at 4.096 MHz *AND* set the Sample Rate Configuration bits to one of the four values to properly set the filters to the correct cutoff frequency as described in section 7.4.3 on page 32. The duty cycle on the input clock is not critical, as the clock is immediately divided by two internally.

#### **External Clock Input Table**

| ISD5116<br>Duration<br>(Minutes) | ISD5108<br>Duration<br>(Minutes) | ISD5104<br>Duration<br>(Minutes) | ISD5102<br>Duration<br>(Minutes) | Sample<br>Rate<br>(kHz) | Required<br>Clock<br>(kHz) | FLD1 | FLD0 | Filter<br>Knee<br>(kHz) |

|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|----------------------------|------|------|-------------------------|

| 8.73                             | 4.36                             | 2.18                             | 1.08                             | 8.0                     | 4096                       | 0    | 0    | 3.4                     |

| 10.9                             | 5.45                             | 2.72                             | 1.35                             | 6.4                     | 4096                       | 0    | 1    | 2.7                     |