# **Dual High Speed PECL Comparators**

# ADCMP561/ADCMP562

#### **FEATURES**

Differential PECL compatible outputs

700 ps propagation delay input to output

75 ps propagation delay dispersion

Input common-mode range: -2.0 V to +3.0 V

Robust input protection

Differential latch control

Internal latch pull-up resistors

Power supply rejection greater than 85 dB

700 ps minimum pulse width

1.5 GHz equivalent input rise time bandwidth

Typical output rise/fall time of 500 ps

ESD protection > 4kV HBM, >200V MM

Programmable hysteresis

#### **APPLICATIONS**

Automatic test equipment

High speed instrumentation

Scope and logic analyzer front ends

Window comparators

High speed line receivers

Threshold detection

Peak detection

High speed triggers

Patient diagnostics

Disk drive read channel detection

Hand-held test instruments

Zero-crossing detectors

Line receivers and signal restoration

Clock drivers

### **GENERAL DESCRIPTION**

The ADCMP561/ADCMP562 are high speed comparators fabricated on Analog Devices' proprietary XFCB process. The devices feature a 700 ps propagation delay with less than 75 ps overdrive dispersion. Dispersion, a measure of the difference in propagation delay under differing overdrive conditions, is a particularly important characteristic of comparators. A separate programmable hysteresis pin is available on the ADCMP562.

A differential input stage permits consistent propagation delay with a wide variety of signals in the common-mode range from -2.0 V to +3.0 V. Outputs are complementary digital signals that

### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

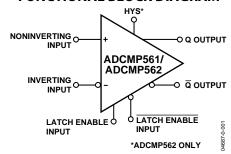

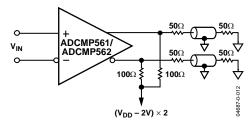

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

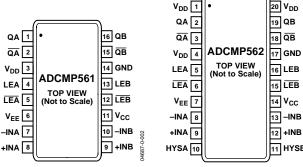

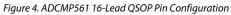

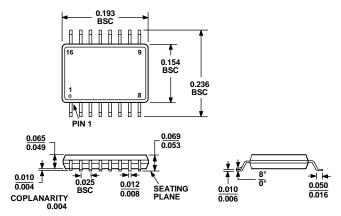

Figure 2. ADCMP561 16-Lead QSOP

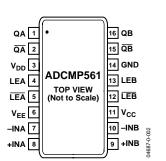

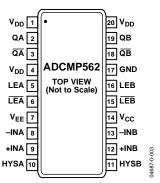

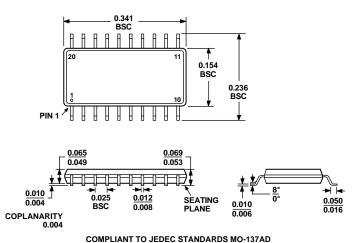

Figure 3. ADCMP562 20-Lead QSOP

are fully compatible with PECL 10 K and 10 KH logic families. The outputs provide sufficient drive current to directly drive transmission lines terminated in 50  $\Omega$  to  $V_{\rm DD}$  – 2 V. A latch input, which is included, permits tracking, track-and-hold, or sample-and-hold modes of operation. The latch input pins contain internal pull-ups that set the latch in tracking mode when left open.

The ADCMP561/ADCMP562 are specified over the industrial temperature range (-40°C to +85°C).

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| Specifications                               | 3 |

|----------------------------------------------|---|

| Absolute Maximum Ratings                     | 5 |

| Thermal Considerations                       | 5 |

| ESD Caution                                  | 5 |

| Pin Configurations and Function Descriptions | 6 |

| Typical Performance Characteristics          | 8 |

| Timing Information10                         | 0 |

| Application Information                      | 1 |

| Clock Timing Recovery11                   |

|-------------------------------------------|

| Optimizing High Speed Performance         |

| Comparator Propagation Delay Dispersion11 |

| Comparator Hysteresis                     |

| Minimum Input Slew Rate Requirement       |

| Typical Application Circuits              |

| Outline Dimensions                        |

| Ordering Guide                            |

### **REVISION HISTORY**

| 7/04—Data Sheet Changed from Rev. 0 to Rev. A |    |

|-----------------------------------------------|----|

| Changes to Specification Table                | 4  |

| Changes to Figure 14                          | 9  |

| Changes to Figure 21                          | 12 |

| Changes to Figure 23                          | 13 |

4/04—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{\text{CC}} = +5.0 \text{ V}, V_{\text{EE}} = -5.2 \text{ V}, V_{\text{DD}} = +3.3 \text{ V}, T_{\text{A}} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } T_{\text{A}} = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.}$

**Table 1. Electrical Characteristics**

| Parameter                                                   | Symbol                                | Conditions                                                       | Min                    | Тур        | Max                                | Unit        |

|-------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------|------------------------|------------|------------------------------------|-------------|

| DC INPUT CHARACTERISTICS                                    |                                       |                                                                  |                        |            |                                    |             |

| Input Voltage Range                                         |                                       |                                                                  | -2.0                   |            | 3.0                                | V           |

| Input Differential Voltage                                  |                                       |                                                                  | -5                     |            | +5                                 | V           |

| Input Offset Voltage                                        | Vos                                   | $V_{CM} = 0 V$                                                   | -10.0                  | ±2.0       | +10.0                              | mV          |

| Input Offset Voltage Channel Matching                       |                                       |                                                                  |                        | ±2.0       |                                    | mV          |

| Offset Voltage Tempco                                       | $\Delta V_{OS}/d_T$                   |                                                                  |                        | 2.0        |                                    | μV/°C       |

| Input Bias Current                                          | I <sub>IN</sub>                       | -IN = -2 V, +IN = +3 V                                           | -10.0                  | ±3         | +10.0                              | μΑ          |

| Input Bias Current Tempco                                   |                                       |                                                                  |                        | 0.5        |                                    | nA/°C       |

| Input Offset Current                                        |                                       |                                                                  |                        | ±1.0       |                                    | μΑ          |

| Input Capacitance                                           | C <sub>IN</sub>                       |                                                                  |                        | 0.75       |                                    | pF          |

| Input Resistance, Differential Mode                         |                                       |                                                                  |                        | 750        |                                    | kΩ          |

| Input Resistance, Common Mode                               |                                       |                                                                  |                        | 1800       |                                    | kΩ          |

| Active Gain                                                 | Av                                    |                                                                  |                        | 63         |                                    | dB          |

| Common-Mode Rejection Ratio                                 | CMRR                                  | $V_{CM} = -2.0 \text{ V to } +3.0 \text{ V}$                     |                        | 80         |                                    | dB          |

| Hysteresis                                                  |                                       | R <sub>HYS</sub> = ∞                                             |                        | ±1.0       |                                    | mV          |

| LATCH ENABLE CHARACTERISTICS                                |                                       |                                                                  |                        |            |                                    |             |

| Latch Enable Voltage Range                                  |                                       |                                                                  | V <sub>DD</sub> – 2.0  |            | $V_{DD}$                           | V           |

| Latch Enable Differential Voltage Range                     |                                       |                                                                  | 0.4                    |            | 2.0                                | V           |

| Latch Enable Input High Current                             |                                       | @ V <sub>DD</sub>                                                | -300                   |            | +300                               | μA          |

| Latch Enable Input Low Current                              |                                       | @ V <sub>DD</sub> -2.0 V                                         | -300                   |            | +300                               | μA          |

| LE Voltage, Open                                            |                                       | Latch inputs not connected                                       | V <sub>DD</sub> - 0.2  | $V_{DD}$   | $V_{DD} + 0.1$                     | V           |

| LE Voltage, Open                                            |                                       | Latch inputs not connected                                       | $V_{DD}/2 - 0.2$       | $V_{DD}/2$ | $V_{DD}/2 + 0.2$                   | V           |

| Latch Setup Time                                            | t <sub>s</sub>                        | $V_{OD} = 250 \text{ mV}$                                        | 1001 - 11              | 250        | 1001 = 1 11=                       | ps          |

| Latch Hold Time                                             | t <sub>H</sub>                        | $V_{OD} = 250 \text{ mV}$                                        |                        | 250        |                                    | ps          |

| Latch-to-Output Delay                                       | t <sub>PLOH</sub> , t <sub>PLOL</sub> | $V_{OD} = 250 \text{ mV}$                                        |                        | 600        |                                    | ps          |

| Latch Minimum Pulse Width                                   | t <sub>PL</sub>                       | $V_{OD} = 250 \text{ mV}$ $V_{OD} = 250 \text{ mV}$              |                        | 500        |                                    | ps          |

| DC OUTPUT CHARACTERISTICS                                   | CFL.                                  | V0D = 230 IIIV                                                   |                        | 300        |                                    | P3          |

| Output Voltage—High Level                                   | V <sub>OH</sub>                       | PECL 50 Ω to V <sub>DD</sub> – 2.0 V                             | V <sub>DD</sub> – 1.15 |            | $V_{DD} - 0.81$                    | V           |

| Output Voltage—Figh Level Output Voltage—Low Level          | Vol                                   | PECL 50 Ω to V <sub>DD</sub> – 2.0 V                             | V <sub>DD</sub> – 1.95 |            | $V_{DD} - 0.51$<br>$V_{DD} - 1.54$ | v           |

| Rise Time                                                   | t <sub>R</sub>                        | 10% to 90%                                                       | V 00 - 1.93            | 550        | V UU — 1.54                        | ps          |

| Fall Time                                                   | t <sub>F</sub>                        | 10% to 90%                                                       |                        | 470        |                                    |             |

| AC PERFORMANCE                                              | LF.                                   | 1070 to 9070                                                     |                        | 470        |                                    | ps          |

| Propagation Delay                                           | <b>+</b>                              | V <sub>OD</sub> = 1 V                                            |                        | 700        |                                    | nc          |

| Propagation Delay                                           | t <sub>PD</sub>                       | $V_{OD} = 1 \text{ V}$<br>$V_{OD} = 20 \text{ mV}$               |                        | 830        |                                    | ps          |

| Dropagation Dolay Tompso                                    | ۸+ /ط                                 | $V_{OD} = 20 \text{ HeV}$<br>$V_{OD} = 1 \text{ V}$              |                        | 0.25       |                                    | ps<br>ps/°C |

| Propagation Delay Tempco                                    | ∆t <sub>PD</sub> /d <sub>T</sub>      | V <sub>OD</sub> = 1 V                                            |                        | 0.25       |                                    | ps/ C       |

| Prop Delay Skew—Rising Transition to Falling Transition     |                                       | V <sub>OD</sub> = 1 V                                            |                        | 50         |                                    | ps          |

| Within Device Propagation Delay Skew—<br>Channel-to-Channel |                                       | V <sub>OD</sub> = 1 V                                            |                        | 50         |                                    | ps          |

| Overdrive Dispersion                                        |                                       | $20 \text{ mV} \leq V_{OD} \leq 100 \text{ mV}$                  |                        | 75         |                                    | ps          |

| Overdrive Dispersion                                        |                                       | 100 mV ≤ V <sub>OD</sub> ≤ 1.5 V                                 |                        | 75         |                                    | ps          |

| Slew Rate Dispersion                                        |                                       | 0.4 V/ns ≤ SR ≤ 1.33 V/ns                                        |                        | 50         |                                    | ps          |

| Pulse Width Dispersion                                      |                                       | 700 ps ≤ PW ≤ 10 ns                                              |                        | 25         |                                    | ps          |

| Duty Cycle Dispersion                                       |                                       | 33 MHz, 1 V/ns, 0.5 V                                            |                        | 15         |                                    | ps          |

| Common-Mode Voltage Dispersion                              |                                       | 1 V swing, $-1.5 \text{ V} \le \text{V}_{CM} \le +2.5 \text{ V}$ |                        | 10         |                                    | ps          |

| Parameter                                         | Symbol              | Conditions                                                  | Min   | Тур  | Max   | Unit |

|---------------------------------------------------|---------------------|-------------------------------------------------------------|-------|------|-------|------|

| AC PERFORMANCE (continued)                        |                     |                                                             |       |      |       |      |

| Equivalent Input Rise Time Bandwidth <sup>1</sup> | $BW_{EQ}$           | 0 V to 1 V swing, 2 V/ns                                    |       | 1500 |       | MHz  |

| Maximum Toggle Rate                               |                     | >50% output swing                                           |       | 800  |       | MHz  |

| Minimum Pulse Width                               | PW <sub>MIN</sub>   | $\Delta t_{PD} < 25 \text{ ps}$                             |       | 700  |       | ps   |

| RMS Random Jitter                                 |                     | V <sub>OD</sub> = 400 mV, 1.3 V/ns, 312 MHz, 50% duty cycle |       | 1.0  |       | ps   |

| Unit-to-Unit Propagation Delay Skew               |                     |                                                             |       | 100  |       | ps   |

| POWER SUPPLY                                      |                     |                                                             |       |      |       |      |

| Positive Supply Current                           | l <sub>vcc</sub>    | @ +5.0 V                                                    | 2     | 3.2  | 5     | mA   |

| Negative Supply Current                           | I <sub>VEE</sub>    | @ -5.2 V                                                    | 10    | 22   | 28    | mA   |

| Logic Supply Current                              | $I_{VDD}$           | @ 3.3 V without load                                        | 6     | 9    | 13    | mA   |

| Logic Supply Current                              |                     | @ 3.3 V with load                                           | 45    | 60   | 70    | mA   |

| Positive Supply Voltage                           | $V_{CC}$            | Dual                                                        | 4.75  | 5.0  | 5.25  | V    |

| Negative Supply Voltage                           | VEE                 | Dual                                                        | -4.96 | -5.2 | -5.45 | V    |

| Logic Supply Voltage                              | $V_{DD}$            | Dual                                                        | 2.5   | 3.3  | 5.0   | V    |

| Power Dissipation                                 | P <sub>D</sub>      | Dual, without load                                          | 130   | 160  | 190   | mW   |

| Power Dissipation                                 |                     | Dual, with load                                             | 180   | 220  | 250   | mW   |

| DC Power Supply Rejection Ratio—Vcc               | PSRR <sub>VCC</sub> |                                                             |       | 85   |       | dB   |

| DC Power Supply Rejection Ratio—V <sub>EE</sub>   | PSRR <sub>VEE</sub> |                                                             |       | 85   |       | dB   |

| DC Power Supply Rejection Ratio—V <sub>DD</sub>   | $PSRR_{VDD}$        |                                                             |       | 85   |       | dB   |

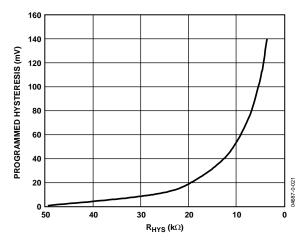

| HYSTERESIS (ADCMP562 Only)                        |                     |                                                             |       |      |       |      |

| Hysteresis                                        |                     | $R_{HYS} = 19.5 \text{ k}\Omega$                            |       | 20   |       | mV   |

|                                                   |                     | $R_{HYS} = 8.0 \text{ k}\Omega$                             |       | 70   |       | mV   |

<sup>&</sup>lt;sup>1</sup> Equivalent input rise time bandwidth assumes a first-order input response and is calculated by the following formula:  $BW_{EQ} = 0.22/\sqrt{(tr_{COMP}^2 - tr_{IN}^2)}$ , where  $tr_{IN}$  is the 20/80 input transition time applied to the comparator and  $tr_{COMP}$  is the effective transition time as digitized by the comparator input.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating           |

|--------------------------------------|------------------|

| Supply Voltages                      |                  |

| Positive Supply Voltage (Vcc to GND) | -0.5 V to +6.0 V |

| Negative Supply Voltage (VEE to GND) | -6.0 V to +0.5 V |

| Logic Supply Voltage (VDD to GND)    | -0.5 V to +6.0 V |

| Ground Voltage Differential          | -0.5 V to +0.5 V |

| Input Voltages                       |                  |

| Input Common-Mode Voltage            | -3.0 V to +4.0 V |

| Differential Input Voltage           | -7.0 V to +7.0 V |

| Input Voltage, Latch Controls        | -0.5 V to +5.5 V |

| Output                               |                  |

| Output Current                       | 30 mA            |

| Temperature                          |                  |

| Operating Temperature, Ambient       | -40°C to +85°C   |

| Operating Temperature, Junction      | 125℃             |

| Storage Temperature Range            | −65°C to +150°C  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL CONSIDERATIONS

The ADCMP561 QSOP 16-lead package option has a  $\theta_{JA}$  (junction-to-ambient thermal resistance) of 104°C/W in still air.

The ADCMP562 QSOP 20-lead package option has a  $\theta_{JA}$  (junction-to-ambient thermal resistance) of 80°C/W in still air.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 5. ADCMP562 20-Lead QSOP Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No.  |          |                 |                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCMP561 | ADCMP562 | Mnemonic        | Function                                                                                                                                                                                                                                                                                                                                                                                        |

| -        | 1        | $V_{\text{DD}}$ | Logic Supply Terminal.                                                                                                                                                                                                                                                                                                                                                                          |

| 1        | 2        | QA              | One of two complementary outputs for Channel A. QA is logic high if the analog voltage at the noninverting input is greater than the analog voltage at the inverting input (provided the comparator is in compare mode). See the description of Pin LEA for more information.                                                                                                                   |

| 2        | 3        | QA              | One of two complementary outputs for Channel A. $\overline{QA}$ is logic low if the analog voltage at the noninverting input is greater than the analog voltage at the inverting input (provided the comparator is in compare mode). See the description of Pin LEA for more information.                                                                                                       |

| 3        | 4        | $V_{DD}$        | Logic Supply Terminal.                                                                                                                                                                                                                                                                                                                                                                          |

| 4        | 5        | LEA             | One of two complementary inputs for Channel A Latch Enable. In compare mode (logic high), the output tracks changes at the input of the comparator. In the latch mode (logic low), the output reflects the input state just prior to the comparator's being placed in the latch mode. LEA must be driven in conjunction with LEA. If left unconnected, the comparator defaults to compare mode. |

| 5        | 6        | ĪĒĀ             | One of two complementary inputs for Channel A Latch Enable. In compare mode (logic low), the output tracks changes at the input of the comparator. In latch mode (logic high), the output reflects the input state just prior to the comparator's being placed in the latch mode. LEA must be driven in conjunction with LEA. If left unconnected, the comparator defaults to compare mode.     |

| 6        | 7        | VEE             | Negative Supply Terminal.                                                                                                                                                                                                                                                                                                                                                                       |

| 7        | 8        | -INA            | Inverting Analog Input of the Differential Input Stage for Channel A. The inverting A input must be driven in conjunction with the noninverting A input.                                                                                                                                                                                                                                        |

| 8        | 9        | +INA            | Noninverting Analog Input of the Differential Input Stage for Channel A. The noninverting A input must be driven in conjunction with the inverting A input.                                                                                                                                                                                                                                     |

|          | 10       | HYSA            | Programmable Hysteresis Input.                                                                                                                                                                                                                                                                                                                                                                  |

|          | 11       | HYSB            | Programmable Hysteresis Input.                                                                                                                                                                                                                                                                                                                                                                  |

| 9        | 12       | +INB            | Noninverting Analog Input of the Differential Input Stage for Channel B. The noninverting B input must be driven in conjunction with the inverting B input.                                                                                                                                                                                                                                     |

| 10       | 13       | -INB            | Inverting Analog Input of the Differential Input Stage for Channel B. The inverting B input must be driven in conjunction with the noninverting B input.                                                                                                                                                                                                                                        |

| 11       | 14       | Vcc             | Positive Supply Terminal.                                                                                                                                                                                                                                                                                                                                                                       |

| 12       | 15       | ĪĒB             | One of two complementary inputs for Channel B Latch Enable. In compare mode (logic low), the output tracks changes at the input of the comparator. In latch mode (logic high), the output reflects the input state just prior to placing the comparator in the latch mode. LEB must be driven in conjunction with LEB. If left unconnected, the comparator defaults to compare mode.            |

| 13       | 16       | LEB             | One of two complementary inputs for Channel B Latch Enable. In compare mode (logic high), the output tracks changes at the input of the comparator. In latch mode (logic low), the output reflects the input state just prior to placing the comparator in the latch mode. LEB must be driven in conjunction with LEB. If left unconnected, the comparator defaults to compare mode.            |

| Pin No.  |          |          |                                                                                                                                                                                                                                                                                           |

|----------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCMP561 | ADCMP562 | Mnemonic | Function                                                                                                                                                                                                                                                                                  |

| 14       | 17       | GND      | Analog Ground.                                                                                                                                                                                                                                                                            |

| 15       | 18       | QB       | One of two complementary outputs for Channel B. $\overline{QB}$ is logic low if the analog voltage at the noninverting input is greater than the analog voltage at the inverting input (provided the comparator is in compare mode). See the description of PIN LEB for more information. |

| 16       | 19       | QB       | One of two complementary outputs for Channel B. QB is logic high if the analog voltage at the noninverting input is greater than the analog voltage at the inverting input (provided the comparator is in compare mode). See the description of Pin LEB for more information.             |

|          | 20       | $V_{DD}$ | Logic Supply Terminal.                                                                                                                                                                                                                                                                    |

### TYPICAL PERFORMANCE CHARACTERISTICS

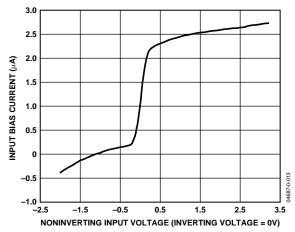

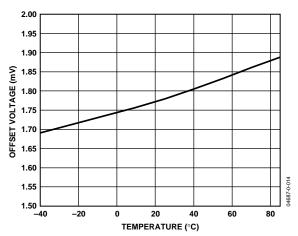

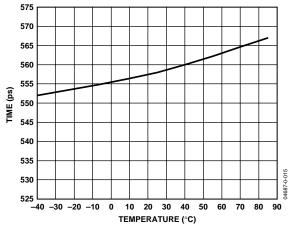

$V_{CC}$  = +5.0 V,  $V_{EE}$  = -5.2 V,  $V_{DD}$  = +3.3 V,  $T_A$  = 25°C, unless otherwise noted.

Figure 6. Input Bias Current vs. Input Voltage

Figure 7. Input Offset Voltage vs. Temperature

Figure 8. Rise Time vs. Temperature

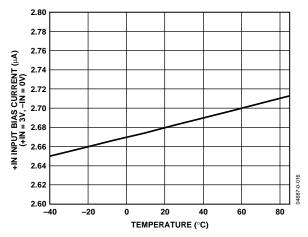

Figure 9. Input Bias Current vs. Temperature

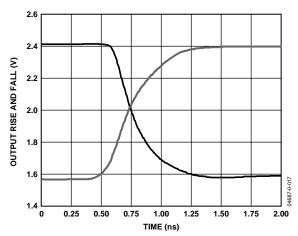

Figure 10. Rise and Fall of Outputs vs. Time

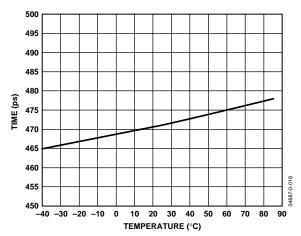

Figure 11. Fall Time vs. Temperature

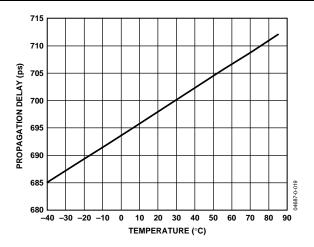

Figure 12. Propagation Delay vs. Temperature

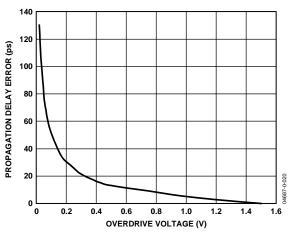

Figure 13. Propagation Delay vs. Overdrive Voltage

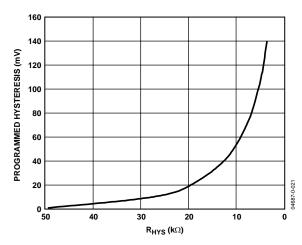

Figure 14. Comparator Hysteresis vs. R<sub>HYS</sub>

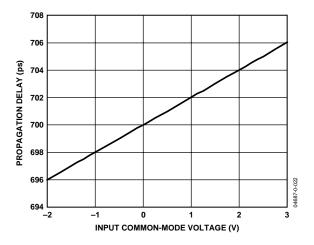

Figure 15. Propagation Delay vs. Common-Mode Voltage

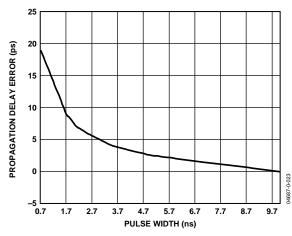

Figure 16. Propagation Delay Error vs. Pulse Width

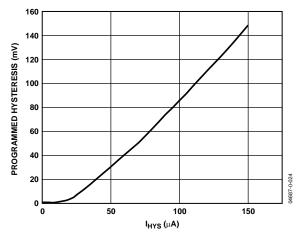

Figure 17. Comparator Hysteresis vs. IHYS

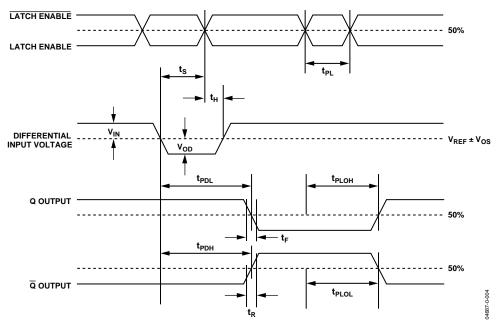

## **TIMING INFORMATION**

Figure 18. System Timing Diagram

Figure 18 shows the compare and latch features of the ADCMP561/ADCMP562. Table 4 describes the terms in the diagram.

**Table 4. Timing Descriptions**

| Symbol                   | Timing                            | Description                                                                                                                                                             |

|--------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>t</b> <sub>PDH</sub>  | Input to Output High Delay        | Propagation delay measured from the time the input signal crosses the reference ( $\pm$ the input offset voltage) to the 50% point of an output low-to-high transition. |

| <b>t</b> <sub>PDL</sub>  | Input to Output Low Delay         | Propagation delay measured from the time the input signal crosses the reference ( $\pm$ the input offset voltage) to the 50% point of an output high-to-low transition. |

| <b>t</b> <sub>PLOH</sub> | Latch Enable to Output High Delay | Propagation delay measured from the 50% point of the latch enable signal low-to-high transition to the 50% point of an output low-to-high transition.                   |

| <b>t</b> <sub>PLOL</sub> | Latch Enable to Output Low Delay  | Propagation delay measured from the 50% point of the latch enable signal low-to-high transition to the 50% point of an output high-to-low transition.                   |

| t <sub>H</sub>           | Minimum Hold Time                 | Minimum time after the negative transition of the latch enable signal that the input signal must remain unchanged to be acquired and held at the outputs.               |

| $t_{\text{PL}}$          | Minimum Latch Enable Pulse Width  | Minimum time the latch enable signal must be high to acquire an input signal change.                                                                                    |

| ts                       | Minimum Setup Time                | Minimum time before the negative transition of the latch enable signal that an input signal change must be present to be acquired and held at the outputs.              |

| $t_{\text{R}}$           | Output Rise Time                  | Amount of time required to transition from a low to a high output as measured at the 20% and 80% points.                                                                |

| <b>t</b> F               | Output Fall Time                  | Amount of time required to transition from a high to a low output as measured at the 20% and 80% points.                                                                |

| $V_{\text{OD}}$          | Voltage Overdrive                 | Difference between the differential input and reference input voltages.                                                                                                 |

### APPLICATION INFORMATION

The ADCMP561/ADCMP562 comparators are very high speed devices. Consequently, high speed design techniques must be employed to achieve the best performance. The most critical aspect of any ADCMP561/ADCMP562 design is the use of a low impedance ground plane. A ground plane, as part of a multilayer board, is recommended for proper high speed performance. Using a continuous conductive plane over the surface of the circuit board can create this, allowing breaks in the plane only for necessary signal paths. The ground plane provides a low inductance ground, eliminating any potential differences at different ground points throughout the circuit board caused by ground bounce. A proper ground plane also minimizes the effects of stray capacitance on the circuit board.

It is also important to provide bypass capacitors for the power supply in a high speed application. A 1  $\mu F$  electrolytic bypass capacitor should be placed within 0.5 inches of each power supply pin to ground. These capacitors reduce any potential voltage ripples from the power supply. In addition, a 10 nF ceramic capacitor should be placed as close as possible from the power supply pins on the ADCMP561/ADCMP562 to ground. These capacitors act as a charge reservoir for the device during high frequency switching.

The LATCH ENABLE input is active low (latched). If the latching function is not used, the LATCH ENABLE input may be left open or may be attached to  $V_{\rm DD}$  ( $V_{\rm DD}$  is a PECL logic high). The complementary input, LATCH ENABLE, may be left open or may be tied to  $V_{\rm DD}-2.0$  V. Leaving the latch inputs unconnected or providing the proper voltages disables the latching function.

Occasionally, one of the two comparator stages within the ADCMP561/ADCMP562 is not used. The inputs of the unused comparator should not be allowed to float. The high internal gain may cause the output to oscillate (possibly affecting the comparator that is being used) unless the output is forced into a fixed state. This is easily accomplished by ensuring that the two inputs are at least one diode drop apart, while also appropriately connecting the LATCH ENABLE and LATCH ENABLE inputs as described previously.

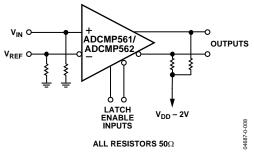

The best performance is achieved with the use of proper PECL terminations. The open emitter outputs of the ADCMP561/ ADCMP562 are designed to be terminated through 50  $\Omega$  resistors to  $V_{\rm DD}-2.0$  V, or any other equivalent PECL termination. If high speed PECL signals must be routed more than a centimeter, microstrip or stripline techniques may be required to ensure proper transition times and prevent output ringing.

#### **CLOCK TIMING RECOVERY**

Comparators are often used in digital systems to recover clock timing signals. High speed square waves transmitted over a distance, even tens of centimeters, can become distorted due to stray capacitance and inductance. Poor layout or improper termination can also cause reflections on the transmission line, further distorting the signal waveform. A high speed comparator can be used to recover the distorted waveform while maintaining a minimum of delay.

#### **OPTIMIZING HIGH SPEED PERFORMANCE**

As with any high speed comparator amplifier, proper design and layout techniques should be used to ensure optimal performance from the ADCMP561/ADCMP562. The performance limits of high speed circuitry can be a result of stray capacitance, improper ground impedance, or other layout issues.

Minimizing resistance from source to the input is an important consideration in maximizing the high speed operation of the ADCMP561/ADCMP562. Source resistance in combination with equivalent input capacitance could cause a lagged response at the input, thus delaying the output. The input capacitance of the ADCMP561/ADCMP562, in combination with stray capacitance from an input pin to ground, could result in several picofarads of equivalent capacitance. A combination of 3 k $\Omega$  source resistance and 5 pF of input capacitance yields a time constant of 15 ns, which is significantly slower than the 750 ps capability of the ADCMP561/ADCMP562. Source impedances should be significantly less than 100  $\Omega$  for best performance.

Sockets should be avoided due to stray capacitance and inductance. If proper high speed techniques are used, the devices should be free from oscillation when the comparator input signal passes through the switching threshold.

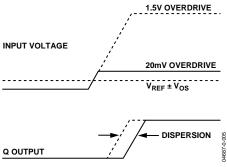

# COMPARATOR PROPAGATION DELAY DISPERSION

The ADCMP561/ADCMP562 have been specifically designed to reduce propagation delay dispersion over an input overdrive range of 100 mV to 1.5 V. Propagation delay overdrive dispersion is the change in propagation delay that results from a change in the degree of overdrive (how far the switching point is exceeded by the input). The overall result is a higher degree of timing accuracy because the ADCMP561/ADCMP562 are far less sensitive to input variations than most comparator designs.

Propagation delay dispersion is a specification that is important in critical timing applications such as ATE, bench instruments, and nuclear instrumentation. Overdrive dispersion is defined as the variation in propagation delay as the input overdrive conditions are changed (Figure 19). For the ADCMP561 and ADCMP562, overdrive dispersion is typically 75 ps as the overdrive is changed from 100 mV to 1.5 V. This specification applies for both positive and negative overdrive because the ADCMP561/ADCMP562 have equal delays for positive and negative going inputs.

Figure 19. Propagation Delay Dispersion

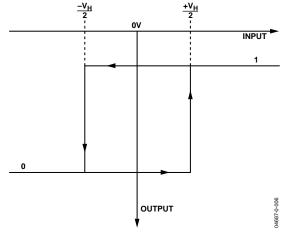

#### **COMPARATOR HYSTERESIS**

The addition of hysteresis to a comparator is often useful in a noisy environment, or where it is not desirable for the comparator to toggle between states when the input signal is at the switching threshold. The transfer function for a comparator with hysteresis is shown in Figure 20. If the input voltage approaches the threshold from the negative direction, the comparator switches from a 0 to a 1 when the input crosses  $+V_{\rm H}/2$ . The new switching threshold becomes  $-V_{\rm H}/2$ . The comparator remains in a 1 state until the threshold  $-V_{\rm H}/2$  is crossed, coming from the positive direction. In this manner, noise centered on 0 V input does not cause the comparator to switch states unless it exceeds the region bounded by  $\pm V_{\rm H}/2$ .

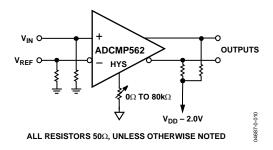

Positive feedback from the output to the input is often used to produce hysteresis in a comparator (Figure 24). The major problem with this approach is that the amount of hysteresis varies with the output logic levels, resulting in a hysteresis that is not symmetrical around zero.

In the ADCMP562, hysteresis is generated through the programmable hysteresis pin. A resistor from the HYS pin to GND creates a current into the part that is used to generate hysteresis. Hysteresis generated in this manner is independent of output swing and is symmetrical around the trip point. The

hysteresis versus resistance curve is shown in Figure 21.

A current source can also be used with the HYS pin. The relationship between the current applied to the HYS pin and the resulting hysteresis is shown in Figure 17.

Figure 20. Comparator Hysteresis Transfer Function

Figure 21. Comparator Hysteresis vs. R<sub>HYS</sub>

#### MINIMUM INPUT SLEW RATE REQUIREMENT

As for all high speed comparators, a minimum slew rate must be met to ensure that the device does not oscillate when the input crosses the threshold. This oscillation is due in part to the high input bandwidth of the comparator and the parasitics of the package. Analog Devices recommends a slew rate of 1 V/ $\mu$ s or faster to ensure a clean output transition. If slew rates less than 1 V/ $\mu$ s are used, hysteresis should be added to reduce the oscillation.

### TYPICAL APPLICATION CIRCUITS

Figure 22. High Speed Sampling Circuits

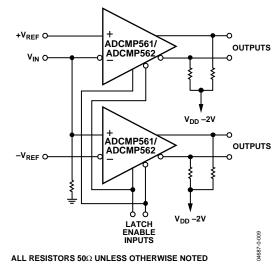

Figure 23. High Speed Window Comparator

Figure 24. Adding Hysteresis Using the HYS Control Pin

Figure 25. How to Interface a PECL Output to an Instrument with a 50  $\Omega$  to Ground Input

### **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MO-137AB

Figure 26. 16-Lead Shrink Small Outline Package [QSOP] (RQ-16) Dimensions shown in inches

Figure 27. 20-Lead Shrink Small Outline Package [QSOP] (RQ-20) Dimensions shown in inches

### **ORDERING GUIDE**

| Model       | Temperature Range | Package Description | Package Option |

|-------------|-------------------|---------------------|----------------|

| ADCMP561BRQ | -40°C to +85°C    | 16-Lead QSOP        | RQ-16          |

| ADCMP562BRQ | -40°C to +85°C    | 20-Lead QSOP        | RQ-20          |

| ADCMP561/ADCMP56 | 2 |

|------------------|---|

|------------------|---|

**NOTES**

| ADCMP561/ADCMP | 562 |

|----------------|-----|

|----------------|-----|

**NOTES**