Data Sheet March 15, 2007 FN6142.4

## 40MHz Rail-to-Rail Video Buffer

The ISL59112 is a single rail-to-rail 6dB video buffer with a 3dB roll-off frequency of 40MHz and a slew rate of 60V/µs. Input signal DC restoration is accomplished with an internal sync tip clamp. Operating from single supplies ranging from +2.5V to +3.6V and sinking an ultra-low 2mA quiescent current, the ISL59112 is ideally suited for low power, battery-operated applications. It also features inputs capable of reaching down to 0.15V below the negative rail. Additionally, an enable high pin shuts the part down in under 20ns.

The ISL59112 is designed to meet the needs for very low power and bandwidth criteria inherent to battery operated communication, instrumentation and modern industrial applications, such as video on demand, cable set-top boxes, DVD players and HDTV. The ISL59112 is offered in a space-saving SC-70 package guaranteed to a 1mm maximum height constraint and specified for operation from -40°C to +85°C temperature range.

# Ordering Information

| PART<br>NUMBER<br>(Note) | PART<br>MARKING | TAPE &<br>REEL | PACKAGE<br>(Pb-Free) | PKG.<br>DWG.# |

|--------------------------|-----------------|----------------|----------------------|---------------|

| ISL59112IEZ-T7           | СРА             | 7" (3k pcs)    | 6 Ld SC-70           | P6.049A       |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **Features**

- 40MHz -3dB bandwidth

- 85V/µs slew rate

- Low supply current = 2mA

- Power-down current less than 1µA

- Supplies from 2.5V to 3.6V

- · Rail-to-rail output

- Input to 0.15V below ground

- · Internal sync tip clamp

- SAG correction reduces coupling capacitor size

- Pb-free plus anneal available (RoHS compliant)

## **Applications**

- Video amplifiers

- · Digital cameras

- · Camera phones

- Portable/handheld products

- · Communications devices

- · Video on demand

- Cable set-top box

- Satellite set-top box

- DVD players

- HDTV

- · Personal video recorders

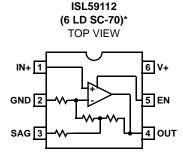

#### Pinout

\*1mm MAXIMUM HEIGHT GUARANTEED

## **Absolute Maximum Ratings** (T<sub>A</sub> = +25°C)

| Supply Voltage from $V_S$ + to $V_S$                | 6V |

|-----------------------------------------------------|----|

| Input Voltage $V_S$ + +0.3V to $V_S$ 0.             | 3V |

| Continuous Output Current 40r                       | nΑ |

| ESD Rating                                          |    |

| Human Body Model (Per MIL-STD-883 Method 3015.7)300 | ٥V |

| Machine Model (Per EIAJ ED-4701 Method C-111)30     | ٥V |

## **Thermal Information**

| Storage Temperature65°C to +125°C                |

|--------------------------------------------------|

| Ambient Operating Temperature40°C to +85°C       |

| Operating Junction Temperature                   |

| Power Dissipation See Curves                     |

| Pb-free reflow profile see link below            |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **Electrical Specifications** $V_S$ + = 3.3V, $V_S$ - = GND, $T_A$ = +25°C, $R_L$ = 150 $\Omega$ to GND, unless otherwise specified

| DESCRIPTION          | PARAMETER                      | CONDITIONS                                                  | MIN  | TYP  | MAX  | UNIT |

|----------------------|--------------------------------|-------------------------------------------------------------|------|------|------|------|

| INPUT CHARAC         | TERISTICS                      | ·                                                           |      |      |      |      |

| V <sub>CC</sub>      | Supply Voltage Range           |                                                             | 2.5  |      | 3.6  | V    |

| I <sub>DD(ON)</sub>  | Quiescent Supply Current       | V <sub>IN</sub> = 500mV, EN = V <sub>DD</sub> , no load     |      | 2    | 2.75 | mA   |

| I <sub>DD(OFF)</sub> | Shutdown Supply Current        | EN = 0V                                                     |      |      | 3    | μΑ   |

| V <sub>OLS</sub>     | Output Level Shift Voltage     | V <sub>IN</sub> = 0V, no load                               | 60   | 130  | 200  | mV   |

| V <sub>CLAMP</sub>   | Input Voltage Clamp            | I <sub>IN</sub> = -1mA                                      | -40  | -15  | +10  | mV   |

| I <sub>CLAMP</sub>   | Clamp Current                  | V <sub>IN</sub> = V <sub>CLAMP</sub> - 100mV                |      | -6   | -3   | mA   |

| I <sub>B</sub>       | Input Bias Current             | V <sub>IN</sub> = 500mV                                     | 2.5  | 5    | 7.5  | μΑ   |

| R <sub>IN</sub>      | Input Resistance               | 0.5V < V <sub>IN</sub> < 1.0V                               | 0.5  | 3    |      | МΩ   |

| A <sub>V</sub>       | Voltage Gain                   | $R_L = 150\Omega$                                           | 5.8  | 6.0  | 6.2  | dB   |

| A <sub>SAG</sub>     | SAG Correction DC Gain to VOUT | SAG open                                                    |      | 2.25 |      | V/V  |

| PSRR                 | DC Power Supply Rejection      | V <sub>DD</sub> = 2.7V to 3.3V                              | 43   | 63   |      | dB   |

| V <sub>OH</sub>      | Output Voltage High Swing      | $V_{IN} = 2V$ , $R_L = 150\Omega$ to GND                    | 2.85 | 3.2  |      | V    |

| I <sub>SC</sub>      | Output Short-Circuit Current   | $V_{IN}$ = 2V, to GND through $10\Omega$                    |      | -94  | -65  | mA   |

|                      |                                | $V_{IN}$ = 100mV, out short to $V_{DD}$ through 10 $\Omega$ | 65   | 115  |      | mA   |

| I <sub>ENABLE</sub>  | Enable Current                 | Enable pin = 0V to 3.6V                                     | -3   | 0    | +3   | μA   |

| V <sub>IL</sub>      | EN Logic Low Threshold         | V <sub>DD</sub> = 2.7V to 3.3V                              |      |      | 0.8  | V    |

| V <sub>IH</sub>      | EN Logic High Threshold        | V <sub>DD</sub> = 2.7V to 3.3V                              | 1.6  |      |      | V    |

| R <sub>OUT</sub>     | Shutdown Output Impedance      | EN = 0V DC                                                  | 3.6  | 4.5  | 5.9  | kΩ   |

|                      |                                | EN = 0V, f = 4.5MHz                                         |      | 3.4  |      | kΩ   |

| AC PERFORMA          | NCE                            | ·                                                           |      |      |      |      |

| BW                   | -3dB Bandwidth                 | $R_L = 150\Omega, C_L = 5pF$                                |      | 40   |      | MHz  |

| BW                   | ±0.1dB Bandwidth               | $R_L = 150\Omega, C_L = 5pF$                                |      | 27   |      | MHz  |

| dG                   | Differential Gain              | NTSC and PAL DC coupled                                     |      | 0.02 |      | %    |

|                      |                                | NTSC and PAL AC coupled                                     |      | 0.02 |      | %    |

| dP                   | Differential Phase             | NTSC and PAL DC coupled                                     |      | 0.4  |      | o    |

|                      |                                | NTSC and PAL AC coupled                                     |      | 0.04 |      | 0    |

| D/DT                 | Group Delay Variation          | f = 100kHz, 5MHz                                            |      | 5.4  |      | ns   |

| SNR                  | Signal To Noise Ratio          | 100% white signal                                           |      | 65   |      | dB   |

| t <sub>ON</sub>      | Enable Time                    | V <sub>IN</sub> = 500mV, V <sub>OUT</sub> to 1%             |      | 570  |      | ns   |

<u>intersil</u>

2

**Electrical Specifications**  $V_S$ + = 3.3V,  $V_S$ - = GND,  $T_A$  = +25 $^{\circ}$ C,  $R_L$  = 150 $\Omega$  to GND, unless otherwise specified (Continued)

| DESCRIPTION    | PARAMETER          | CONDITIONS                                       | MIN | TYP | MAX | UNIT |

|----------------|--------------------|--------------------------------------------------|-----|-----|-----|------|

| toff           | Disable Time       | V <sub>IN</sub> = 500mV, V <sub>OUT</sub> to 1%  |     | 14  |     | ns   |

| SR(Ih)         | Positive Slew Rate | V <sub>IN</sub> = 1V <sub>STEP</sub> , 10% - 90% | 30  | 85  |     | V/µs |

| SR(hl)         | Negative Slew Rate | V <sub>IN</sub> = 1V <sub>STEP</sub>             |     | -80 | -30 | V/µs |

| t <sub>F</sub> | Fall Time          | 1.0V <sub>STEP</sub>                             |     | 9   |     | ns   |

| t <sub>R</sub> | Rise Time          | 1.0V <sub>STEP</sub> , 20% - 80%                 |     | 9   |     | ns   |

# **Typical Performance Curves**

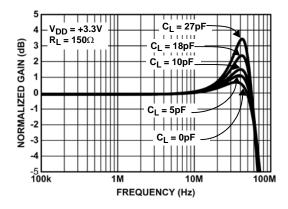

FIGURE 1. FREQUENCY RESPONSE FOR VARIOUS  $C_{\mathsf{LOAD}}$

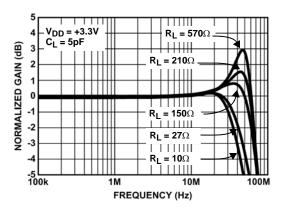

FIGURE 2. FREQUENCY RESPONSE FOR VARIOUS  $R_{\mbox{\scriptsize LOAD}}$

FIGURE 3. FREQUENCY RESPONSE FOR VARIOUS  $V_{OS}$

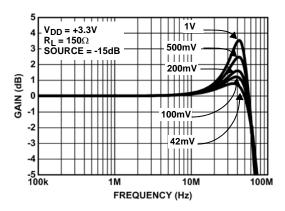

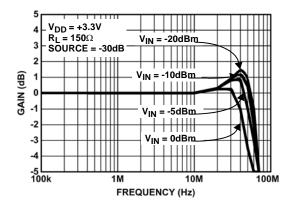

FIGURE 4. FREQUENCY RESPONSE FOR VARIOUS  $V_{\mbox{\scriptsize IN}}$

# Typical Performance Curves (Continued)

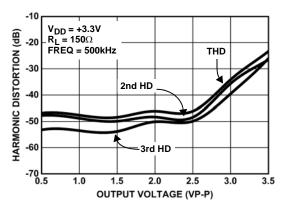

FIGURE 5. HARMONIC DISTORTION vs OUTPUT VOLTAGE

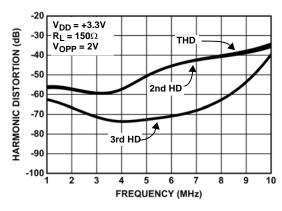

FIGURE 6. HORMONIC DISTORTION vs FREQUENCY

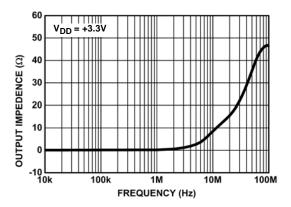

FIGURE 7. OUTPUT IMPEDENCE vs FREQUENCY

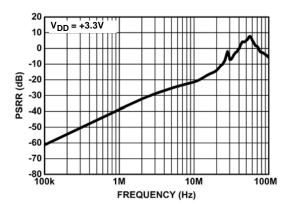

FIGURE 8. PSRR vs FREQUENCY

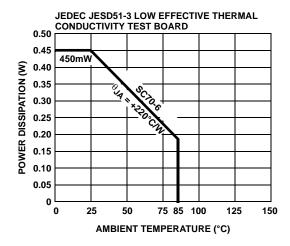

FIGURE 9. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

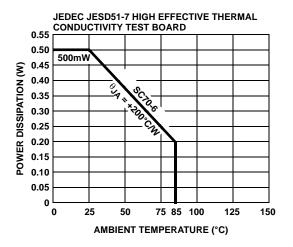

FIGURE 10. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

intersil

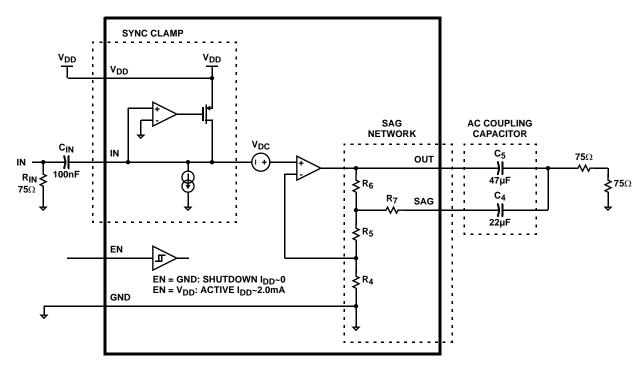

FIGURE 11. BLOCK DIAGRAM

# Application Information

The ISL59112 is a single supply rail-to-rail output buffer achieving a -3dB bandwidth of around 40MHz and slew rate of about 85V/µs while demanding only 2mA of supply current. This part is ideally suited for applications with specific micropower consumption and high bandwidth demands. As described in both the performance characteristics section and the features section, the ISL59112 is designed to be very attractive for portable composite video applications.

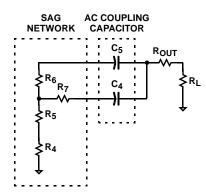

The ISL59112 features a sync clamp and SAG network at the output facilitating reduction of typically large AC coupling capacitors. See Figure 11.

## Internal Sync Clamp

The typical embedded video DAC operates from a ground referenced single supply. This becomes an issue because the lower level of the sync pulse output may be at a 0V reference level to some positive level. The problem is presenting a 0V input to most single supply driven amplifiers will saturate the output stage of the amplifier, resulting in a clipped sync tip and degrading the video image. A larger positive reference may offset the input above its positive range.

The ISL59112 features an internal sync clamp and an offset function to level shift the entire video signal to the best level before it reaches the input of the amplifier stage. These features are also helpful to avoid saturation of the output

stage of the amplifier by setting the signal closer to the best voltage range.

The simplified block diagram of the ISL59112 in Figure 11 is divided into four sections. The first (Section A) is the Sync Clamp. The AC coupled video sync signal is pulled negative by a current source at the input of the comparator amplifier. When the sync tip goes below the comparator threshold, the output comparator is driven negative and the PMOS device turns on clamping sync tip to near ground level.

## AC Output Coupling and the SAG Network

Composite video signals carry viable information at frequencies as low as 30Hz up to 5MHz. When a video system output is AC coupled it is critical that the filter represented by the output coupling capacitor and the surrounding resistance network provide a band pass function with a low pass band low enough to exclude very low frequencies down to DC, and with a high pass band pass sufficiently high to include frequencies at the higher end of the video spectrum.

intersil

FIGURE 12. SAG NETWORK AND AC COUPLING CAPACITORS

Typically, this is accomplished with 220µF coupling capacitor, a large and somewhat costly solution providing a low frequency pole around 5Hz. If the size of this capacitor is even slightly reduced we have found that the accompanying phase shift in the 50Hz to 100Hz frequency range results in field tilt, which results in a degraded video image.

The internal SAG network of the ISL59112 replaces the  $220\mu F$  AC coupling capacitor with a network of two smaller capacitors as shown, in Figure 12. Additionally, the network is designed to place a zero in the ~30Hz range, providing a small amount of peaking to compensate the phase response associated with field tilt.

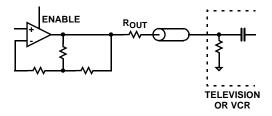

## **DC Output Coupling**

The ISL59112 internal sync clamp makes it possible to DC couple the output to a video load, eliminating the need for any AC coupling capacitor, thereby saving board space and additional expense for capacitors. Additionally, this solution completely eliminates the issue of field tilt in the lower frequency. The trade off is greater demand of supply current. Typical load current for AC coupled is around 3mA compared to typical 6mA used when DC coupling.

FIGURE 13. DC COUPLE

## **Output Drive Capability**

The ISL59112 does not have internal short-circuit protection circuitry. If the output is shorted indefinitely, the power dissipation could easily overheat the die or the current could eventually compromise metal integrity. Maximum reliability is maintained if the output current never exceeds ±40mA. This limit is set by the design of the internal metal interconnect. Note that in transient applications, the part is robust.

Short-circuit protection can be provided externally with a back match resistor in series with the output placed close as possible to the output pin. In video applications this would be a  $75\Omega$  resistor and will provide adequate short-circuit protection to the device. Care should still be taken not to stress the device with a short at the output.

## Power Dissipation

With the high output drive capability of the ISL59112, it is possible to exceed the +125°C absolute maximum junction temperature under certain load current conditions.

Therefore, it is important to calculate the maximum junction temperature for an application to determine if load conditions or package types need to be modified to assure operation of the amplifier in a safe operating area.

The maximum power dissipation allowed in a package is determined according to Equation 1:

$$PD_{MAX} = \frac{T_{JMAX} - T_{AMAX}}{\Theta_{JA}}$$

(EQ. 1)

Where:

T<sub>JMAX</sub> = Maximum junction temperature

T<sub>AMAX</sub> = Maximum ambient temperature

$\Theta_{JA}$  = Thermal resistance of the package

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the load, or

for sourcing:

$$PD_{MAX} = V_S \times I_{SMAX} + (V_S - V_{OUT}i) \times \frac{V_{OUT}i}{R_Li}$$

(EQ. 2)

for sinking:

$$PD_{MAX} = V_{S} \times I_{SMAX} + (V_{OUT}i - V_{S}) \times I_{LOAD}i$$

(EQ. 3)

Where:

$V_S$  = Supply voltage

I<sub>SMAX</sub> = Maximum quiescent supply current

V<sub>OUT</sub> = Maximum output voltage of the application

R<sub>LOAD</sub> = Load resistance tied to ground

I<sub>LOAD</sub> = Load current

By setting the two  $P_{DMAX}$  equations equal to each other, we can solve the output current and  $R_{LOAD}$  to avoid the device overheat.

intersil

# Power Supply Bypassing Printed Circuit Board Layout

As with any modern operational amplifier, a good printed circuit board layout is necessary for optimum performance. Lead lengths should be as short as possible. The power supply pin must be well bypassed to reduce the risk of oscillation. For normal single supply operation, where the V<sub>S</sub>- pin is connected to the ground plane, a single 4.7µF tantalum capacitor in parallel with a 0.1µF ceramic capacitor from V<sub>S</sub>+ to GND will suffice. This same capacitor combination should be placed at each supply pin to ground if split supplies are to be used. In this case, the V<sub>S</sub>- pin becomes the negative supply rail.

## **Printed Circuit Board Layout**

For good AC performance, parasitic capacitance should be kept to minimum. Use of wire wound resistors should be avoided because of their additional series inductance. Use of sockets should also be avoided if possible. Sockets add parasitic inductance and capacitance that can result in compromised performance. Minimizing parasitic capacitance at the amplifier's inverting input pin is very important. The feedback resistor should be placed very close to the inverting input pin. Strip line design techniques are recommended for the signal traces.

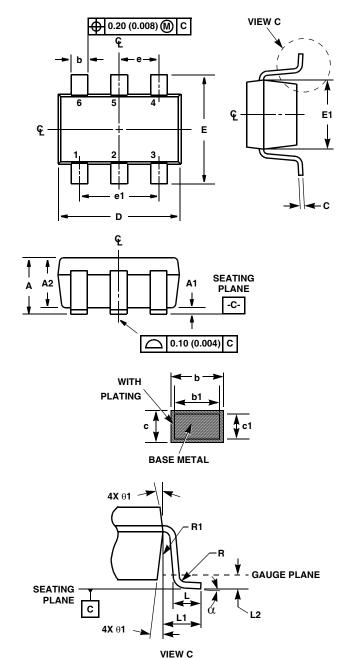

# Small Outline Transistor Plastic Packages (SC70-6)

P6.049A

6 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE

|        | INCHES     |       | MILLIMETERS |          |       |

|--------|------------|-------|-------------|----------|-------|

| SYMBOL | MIN        | MAX   | MIN         | MAX      | NOTES |

| Α      | 0.031      | 0.039 | 0.80        | 1.00     | -     |

| A1     | 0.001      | 0.004 | 0.025       | 0.10     | -     |

| A2     | 0.034      | 0.036 | 0.85        | 0.90     | -     |

| b      | 0.006      | 0.012 | 0.15        | 0.30     | -     |

| b1     | 0.006      | 0.010 | 0.15        | 0.25     | -     |

| С      | 0.004      | 0.008 | 0.10        | 0.20     | 6     |

| c1     | 0.004      | 0.006 | 0.10        | 0.15     | 6     |

| D      | 0.073      | 0.085 | 1.85        | 2.15     | 3     |

| E      | 0.084      | BSC   | 2.1 BSC     |          | -     |

| E1     | 0.045      | 0.053 | 1.15        | 1.35     | 3     |

| е      | 0.0256 Ref |       | 0.65 Ref    |          | -     |

| e1     | 0.0512 Ref |       | 1.30        | Ref      | -     |

| L      | 0.010      | 0.018 | 0.26        | 0.46     | 4     |

| L1     | 0.016 Ref. |       | 0.400       | Ref.     | -     |

| L2     | 0.006 BSC  |       | 0.15        | 0.15 BSC |       |

| N      | 6          |       | 6           |          | 5     |

| R      | 0.004      | -     | 0.10        | -        | -     |

| α      | 0°         | 8°    | 0°          | 8°       | -     |

Rev. 0 7/05

#### NOTES:

- 1. Dimensioning and tolerance per ASME Y14.5M-1994.

- 2. Package conforms to EIAJ SC70 and JEDEC MO203AB.

- Dimensions D and E1 are exclusive of mold flash, protrusions, or gate burrs.

- 4. Footlength L measured at reference to gauge plane.

- 5. "N" is the number of terminal positions.

- 6. These Dimensions apply to the flat section of the lead between 0.08mm and 0.15mm from the lead tip.

- Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

<u>intersil</u>