# LM4681 Boomer® Audio Power Amplifier Series

# 10 Watt Stereo CLASS D Audio Power Amplifier with Stereo Headphone Amplifier and I<sup>2</sup>C/SPI Volume Control

### **General Description**

The LM4681 is a fully integrated single supply, CLASS D audio power amplifier solution. The LM4681 utilizes a proprietary balanced pulse-width modulation technique that lowers output noise and THD and improves PSRR when compared to conventional pulse width modulators.

The LM4681 also features a stereo headphone amplifier that delivers 80mW into a  $32\Omega$  headset with less than 0.5% THD.

The LM4681's I<sup>2</sup>C/SPI (selectable) volume control has a +30dB to -48dB range when speakers are driven and a range of +13dB to -65dB when headphones are connected. All amplifiers are protected by thermal shutdown. Additionally, the high efficiency power amplifiers have output current limit.

With a  $8\Omega$  load, the IC's efficiency for a 6W power level is 85%. The IC features click and pop reduction circuitry that minimizes audible popping during device turn-on and turn-off. The LM4681 is available in a 48-lead LLP package, ideal for portable and desktop computer applications.

# **Key Specifications**

- $P_O$  at THD+N =10%,  $A_V$  = 30dB,  $V_{DD}$  = 14V 10W (typ)

- THD+N at 1kHz at 1W into 8Ω (Power Amp) 0.43% (typ)

- Efficiency at 7W into 8Ω 85% (min)

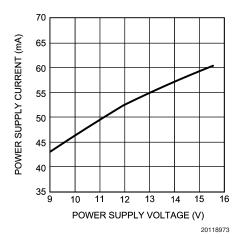

- Total quiescent power supply current 50mA (typ)

- THD+N 1kHz, 20mW, 32Ω (Headphone) 0.02% (typ)

- Single supply range 9.0V to 15.5V

#### **Features**

- Pulse-width modulator.

- I<sup>2</sup>C/SPI (selectable) volume control

- Stereo headphone amplifier.

- "Click and pop" suppression circuitry.

- Micropower shutdown mode.

- 48 lead LLP package (No heatsink required).

### **Applications**

- Flat Panel Displays

- Televisions

- Multimedia Monitors

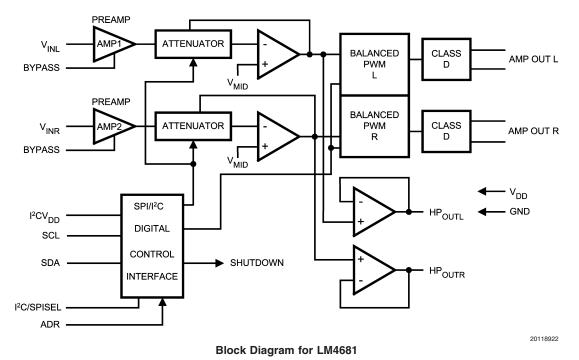

# **Block Diagram**

BOOMER™ is a trademark of National Semiconductor Corporation

© 2006 National Semiconductor Corporation

DS201189

#### **Connection Diagram LLP Package** BYPASS\_A HP\_GND a Z VREF 2 2 2 48 47 37 45 44 40 38 OUT1\_A OUT1\_B 1 36 OUT1\_B 2 35 OUT1\_A OUT1\_B OUT1\_A 34 3 33 $PV_{DD}B$ PV<sub>DD</sub>\_A 32 PGND\_B PGND\_A PGND\_B 31 PGND\_A PGND\_B 30 PGND\_A 29 $PV_{DD}B$ PV<sub>DD</sub>\_A 28 $PV_{DD}A$ $\mathsf{PV}_\mathsf{DD}\!\!-\!\!\mathsf{B}$ OUT2\_B 10 27 OUT2\_A 26 OUT2\_B 11 OUT2\_A 12 25 OUT2\_B OUT2\_A $V_{DD-A}$ GND\_A SDA ADR 2 SCL HPSEL 2 SEL S 2 20118917 **Top View** Order Number LM4681SQ See NS Package Number SQA048AA (LLP Package)

# **Absolute Maximum Ratings** (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage 16V Input Voltage -0.3V to  $V_{DD}$  +0.3V

Power Dissipation (Note 3) Internally Limited ESD Susceptibility(Note 4) 2000V ESD Susceptibility (Note 5) 200V Junction Temperature (Note 6) 150°C

Storage Temperature  $(1000 \text{ G})^{-150 \text{ G}}$   $-65^{\circ}\text{C} \leq T_{A} \leq 150^{\circ}\text{C}$

**LLP** Package

Vapor Phase (60 sec.) 215°C Infrared (15 sec.) 220°C

### Operating Ratings (Notes 1, 2)

Temperature Range

$T_{MIN} \le T_A \le T_{MAX}$   $-40^{\circ}C \le T_A \le +85^{\circ}C$ Supply Voltage  $9V \le V_{DD} \le 15.5V$

Thermal Resistance (LLP Package)

$\theta_{JA}$   $28^{\circ}\text{C/W}$   $\theta_{JC}$   $20^{\circ}\text{C/W}$

Soldering Information

### **Electrical Characteristics** (Notes 1, 2, 7)

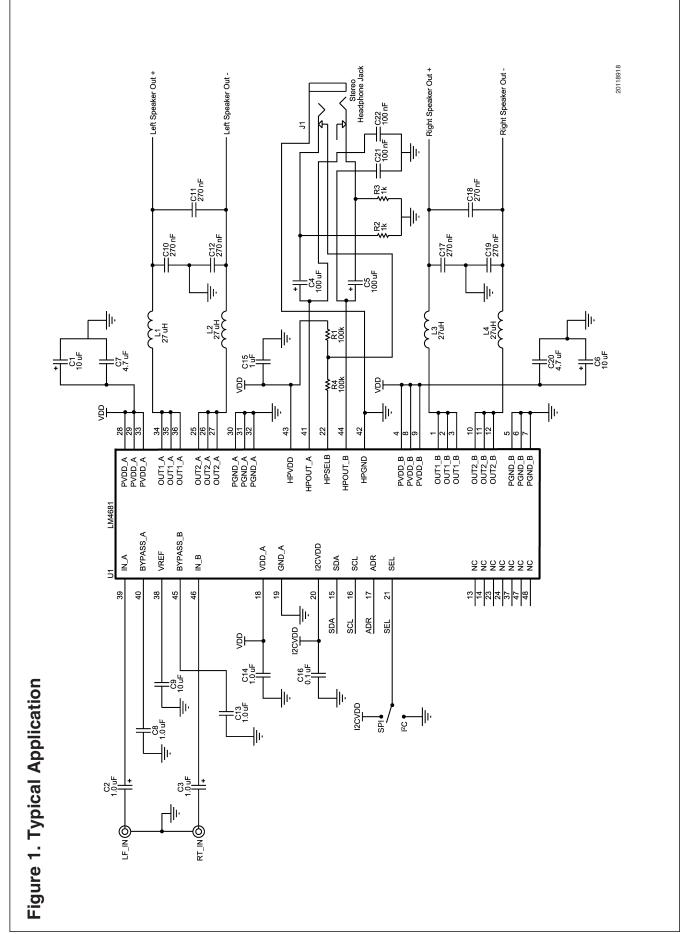

The following specifications apply for  $V_{DD}=12V$ ,  $I^2CV_{DD}=5V$ ,  $R_L=8\Omega$ , LC filter values as shown in Figure 1, unless otherwise specified. Limits apply for  $T_A=25$ °C.

| Symbol                          | Downward or .                                     |                                                                                               | LM4     | LM4681                                   |                    |  |

|---------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------|---------|------------------------------------------|--------------------|--|

|                                 | Parameter                                         | Conditions                                                                                    | Typical | Limit                                    | Units              |  |

| V <sub>DD</sub>                 | Operating Supply Voltage Range                    |                                                                                               | 12      | 15.5<br>9                                | V (max)<br>V (min) |  |

| I <sub>S</sub>                  | Quiescent Power Supply Current,<br>Class D Mode   | V <sub>IN</sub> = 0V <sub>RMS</sub> , V <sub>HPSEL</sub> = 0V                                 | 50      | 70                                       | mA<br>(max)        |  |

| I <sub>S</sub>                  | Quiescent Power Supply Current,<br>Headphone Mode | $V_{IN} = 0V_{RMS}, V_{HPSEL} = V_{DD}$                                                       | 22      | 30                                       | mA<br>(max)        |  |

| I <sub>SD</sub>                 | Quiescent Power Supply Current,<br>Shutdown Mode  | V <sub>SD</sub> = 5V                                                                          | 0.1     |                                          | mA                 |  |

| R <sub>IN</sub>                 | Input Resistance in Both Modes                    |                                                                                               | 8       |                                          | kΩ                 |  |

| I <sup>2</sup> CV <sub>DD</sub> | I <sup>2</sup> C / SPI Logic Supply Voltage       |                                                                                               |         | 5.5<br>3                                 | V (max)<br>V (min) |  |

| V <sub>IH</sub>                 | Minimum High Level Input<br>Voltage               | 12C/CDL Interface mine                                                                        |         | 0.7 x<br>I <sup>2</sup> CV <sub>DD</sub> | V (min)            |  |

| V <sub>IL</sub>                 | Maximum Low Level Input<br>Voltage                | - I <sup>2</sup> C/SPI Interface pins                                                         |         | 0.3 x<br>I <sup>2</sup> CV <sub>DD</sub> | V (max)            |  |

| V <sub>HPIH</sub>               | HP Sense High Input Voltage                       |                                                                                               |         | V <sub>DD</sub> – 1                      | V (min)            |  |

| V <sub>HPIL</sub>               | HP Sense Low Input Voltage                        |                                                                                               |         | V <sub>DD</sub> /2                       | V (max)            |  |

| Power Am                        | plifiers                                          |                                                                                               | •       |                                          |                    |  |

|                                 | Maximum Output Power, Per                         | THD+N $\leq$ 1%, $f_{IN} = 1kHz$                                                              | 6.0     | 5.3                                      | W (min)            |  |

| Po                              | Channel                                           | THD+N $\leq$ 10%, V <sub>DD</sub> = 14V,<br>f <sub>IN</sub> = 1kHz                            | 10      |                                          | W                  |  |

| P <sub>D1</sub>                 | Power Dissipation                                 | P <sub>O</sub> = 6W/Chan, f <sub>IN</sub> = 1kHz                                              | 1.17    |                                          | W                  |  |

| E <sub>FF1</sub>                | Efficiency                                        | P <sub>O</sub> = 6W/Chan, f <sub>IN</sub> = 1kHz                                              | 85      |                                          | %                  |  |

| THD+N                           | Harmonic Distortion + Noise                       | P <sub>O</sub> = 1W/Chan, f <sub>IN</sub> = 1kHz                                              | 0.11    |                                          | %                  |  |

| V <sub>NOISE</sub>              | Output Noise Voltage                              | $R_{SOURCE} = 50\Omega, C_{IN} = 1\mu F,$<br>BW = 8Hz to 22kHz,<br>A-weighted, input referred | 10      |                                          | μV                 |  |

#### Electrical Characteristics (Notes 1, 2, 7) (Continued)

The following specifications apply for  $V_{DD}=12V$ ,  $I^2CV_{DD}=5V$ ,  $R_L=8\Omega$ , LC filter values as shown in Figure 1, unless otherwise specified. Limits apply for  $T_A=25\,^{\circ}C$ .

| Symbol             | Doromotor                                        | Conditions                                                                                                                | LM4681         |       | Units       |  |  |

|--------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------|-------|-------------|--|--|

|                    | Parameter                                        | Conditions                                                                                                                | Typical        | Limit | Units       |  |  |

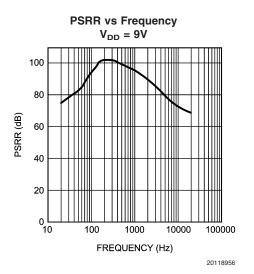

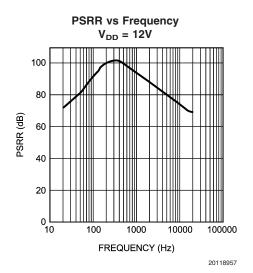

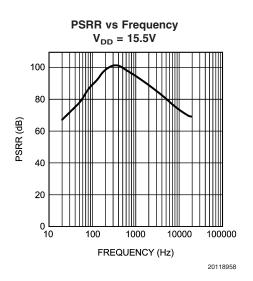

| PSRR               | Power Supply Rejection Ratio                     | $V_{RIPPLE} = 200 \text{mV}_{P-P},$ $C_{BYPASS1} = 10 \mu \text{F},$ input referred $f = 50 \text{Hz}$ $f = 60 \text{Hz}$ | 82<br>84       |       | dB          |  |  |

|                    |                                                  | f = 100Hz<br>f = 120Hz<br>f = 1kHz                                                                                        | 92<br>95<br>95 |       |             |  |  |

| Headphone          | Headphone Amplifiers                             |                                                                                                                           |                |       |             |  |  |

| Po                 | Maximum Power Output Per<br>Channel              | THD+N $\leq$ 1%, R <sub>L</sub> = 32 $\Omega$ , f <sub>IN</sub> = 1kHz                                                    | 94             | 70    | mW<br>(min) |  |  |

| THD+N              | Distortion + Noise                               | $P_O = 20$ mW, $R_L = 32\Omega$ , $f_{IN} = 1$ kHz                                                                        | 0.02           |       | %           |  |  |

| V <sub>NOISE</sub> | Output Noise Voltage, RMS                        | $R_{IN} = 50\Omega$ , $C_{IN} = 1\mu F$ ,<br>$BW = 20Hz$ to $20kHz$ , $R_L = 32\Omega$<br>A-weighted, Input referred      | 22             |       | μV          |  |  |

| PSRR               | Power Supply Rejection Ratio (Referred to Input) | 200mV, 1kHz, $V_{IN} = 0$ , $R_L = 32\Omega$                                                                              | 77             |       | dB          |  |  |

### **Electrical Characteristics for Volume Control** (Notes 1, 2)

The following specifications apply for  $V_{DD}$  = 12V. Limits apply for  $T_A$  = 25°C.

|                    |            |                                    | LM4681   |          | Units     |

|--------------------|------------|------------------------------------|----------|----------|-----------|

| Symbol             | Parameter  | Conditions                         | Typical  | Limit    | (Limits ) |

|                    |            |                                    | (Note 8) | (Note 7) |           |

| C <sub>RANGE</sub> | Gain Range | Digital Code = Full Scale, No Load |          |          |           |

|                    |            | Power Amplifier                    | 30       | 29       | dB (min)  |

|                    |            | Headphone Amplifier                | 13       | 12       | dB (min)  |

|                    |            | Digital Code = +1LSB, No Load      |          |          |           |

|                    |            | Power Amplifier                    | -48      | -46      | dB (min)  |

|                    |            | Headphone Amplifier                | -65      | -63      | dB (min)  |

| A <sub>M</sub>     | Mute Gain  | Digital Code = 0, No Load          |          |          |           |

|                    |            | Power Amplifier                    |          | -74      | dB (max)  |

|                    |            | Headphone Amplifier                | -76      | -74      | dB (max)  |

Note 1: All voltages are measured with respect to the ground pin, unless otherwise specified.

**Note 2:** "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. "Operating Ratings" indicate conditions for which the device is functional, but do not guarantee specific performance limits. "Electrical Characteristics" state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 3: For operating at case temperatures above 25°C, the device must be derated based on a 150°C maximum junction temperature and a thermal resistance of  $\theta_{JA} = 80$ °C/W (junction to ambient).

- Note 4: Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

- Note 5: Machine Model 220pF 240pF discharged through all pins.

- Note 6: The operating junction temperature maximum is 150°C.

- Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

- Note 8: Typicals are measured at  $25^{\circ}\text{C}$  and represent the parametric norm.

# I<sup>2</sup>C/SPI Interface Controls

|                             | B7 | В6 | B5 | B4 | B3 | B2 | B1     | В0       |

|-----------------------------|----|----|----|----|----|----|--------|----------|

| I <sup>2</sup> C<br>Address | 1  | 1  | 0  | 1  | 1  | 0  | ADR    | 0        |

| Mode                        |    |    |    |    |    |    | 0      | 0        |

| Control                     | 0  | Х  | 0  | X  | X  | X  | Mute   | Shutdown |

| Register                    |    |    |    |    |    |    | Active | Active   |

| Volume                      |    |    |    |    |    |    |        |          |

| Control                     |    |    |    |    |    |    |        |          |

| Register                    | 1  | 0  | 0  | V4 | V3 | V2 | V1     | V0       |

| (See                        |    |    |    |    |    |    |        |          |

| Table 4)                    |    |    |    |    |    |    |        |          |

# **Headphone Control**

| HP Sense Pin (HPSEL, pin 22) | Output Stage Configuration |

|------------------------------|----------------------------|

| 0                            | Class D Amps Active        |

| 1 (V <sub>DD</sub> )         | Class D Amps inactive      |

# **Logic Controls**

| Logic Level (SEL, pin 21) | I <sup>2</sup> C/SPI Select |

|---------------------------|-----------------------------|

| 0                         | I <sup>2</sup> C mode       |

| 1                         | SPI mode                    |

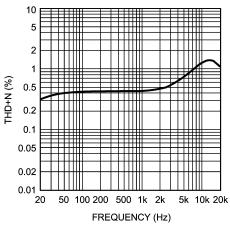

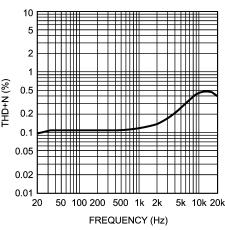

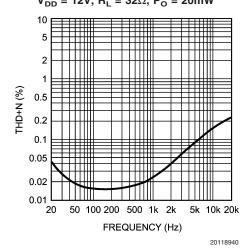

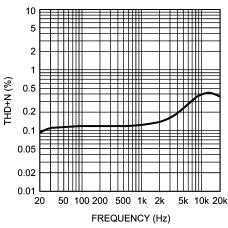

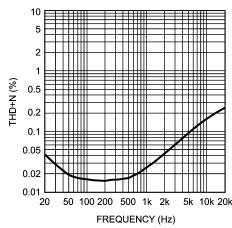

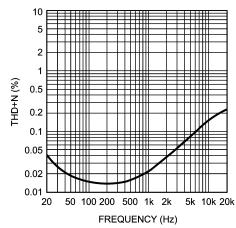

# **Typical Performance Characteristics**

(Volume control at maximum, unless otherwise stated.)

Class D Amplifier THD+N vs Frequency  ${\rm V_{DD}=9V,\,R_L=8\Omega,\,P_O=1W}$

20118936

Class D Amplifier THD+N vs Frequency  $V_{DD}$  = 15.5V,  $R_L$  = 8 $\Omega$ ,  $P_O$  = 1W

20118970

Class AB Headphone Amplifier THD+N vs Frequency  ${\rm V_{DD}=12V,\,R_L=32\Omega,\,P_O=20mW}$

Class D Amplifier THD+N vs Frequency  $\rm V_{DD}$  = 12V,  $\rm R_L$  = 8 $\Omega,\, \rm P_O$  = 1W

20118969

Class AB Headphone Amplifier THD+N vs Frequency  ${\rm V_{DD}=9V,\,R_L=32\Omega,\,P_O=20mW}$

20118939

Class AB Headphone Amplifier THD+N vs Frequency  $V_{DD} = 15.5V, \, R_L = 32 \Omega, \, P_O = 20 mW$

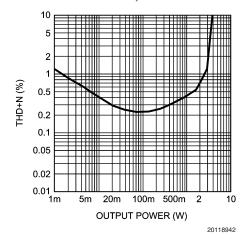

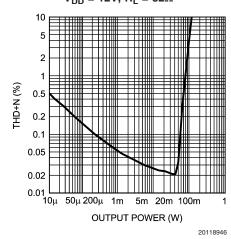

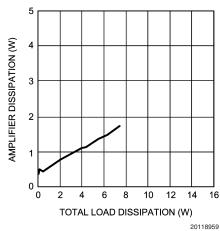

Class D Amplifier THD+N vs Output Power  $V_{DD}=9V,\,R_L=8\Omega$  Both channel driven, both measured

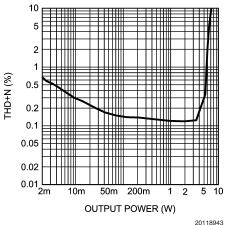

Class D Amplifier THD+N vs Output Power  ${\rm V_{DD}=12V,\ R_L=8\Omega}$  Both channel driven, both measured

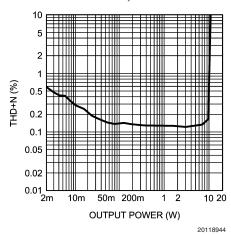

Class D Amplifier THD+N vs Output Power  ${\rm V_{DD}=15.5V,\,R_L=8\Omega}$  Both channel driven, both measured

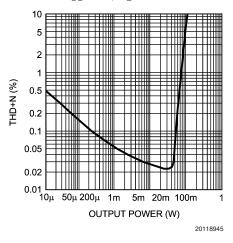

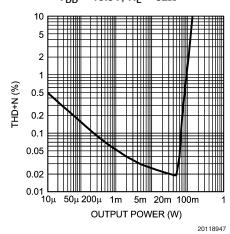

Class AB Headphone Amplifier THD+N vs Output Power  $\mbox{V}_{\mbox{\scriptsize DD}} = \mbox{9V}, \mbox{ R}_{\mbox{\scriptsize L}} = \mbox{32}\Omega$

Class AB Headphone Amplifier THD+N vs Output Power  $\rm V_{DD}$  = 12V,  $\rm R_{L}$  =  $32\Omega$

Class AB Headphone Amplifier THD+N vs Output Power  $\rm V_{DD}$  = 15.5V,  $\rm R_{L}$  = 32 $\!\Omega$

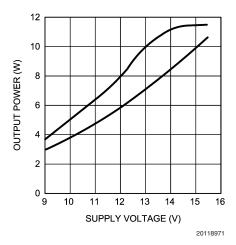

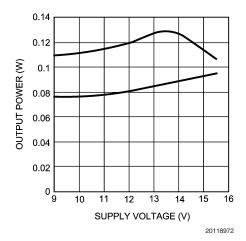

#### Class D Amplifier Output Power vs Supply Voltage

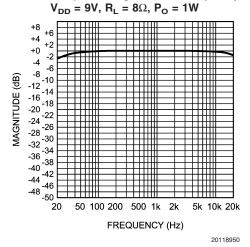

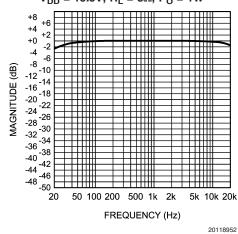

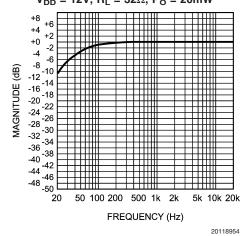

# Class D Amplifier Magnitude vs Frequency

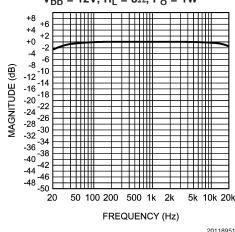

# Class D Amplifier Magnitude vs Frequency $V_{DD}$ = 15.5V, $R_L$ = 8 $\Omega$ , $P_O$ = 1W

# Class AB Headphone Amplifier Output Power vs Supply Voltage

Class D Amplifier Magnitude vs Frequency  $V_{DD}$  = 12V,  $R_L$  = 8 $\Omega$ ,  $P_O$  = 1W

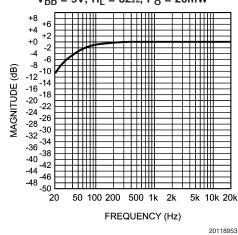

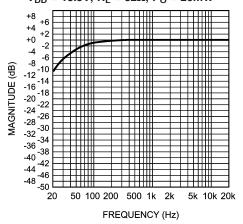

Class AB Headphone Amplifier Magnitude vs Frequency  $V_{DD}$  = 9V,  $R_L$  = 32 $\Omega$ ,  $P_O$  = 20mW

Class AB Headphone Amplifier Magnitude vs Frequency  $V_{DD}$  = 12V,  $R_L$  = 32 $\Omega$ ,  $P_O$  = 20mW

Class AB Headphone Amplifier Magnitude vs Frequency  $V_{DD}$  = 15.5V,  $R_L$  = 32 $\Omega$ ,  $P_O$  = 20mW

20118955

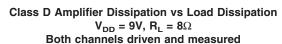

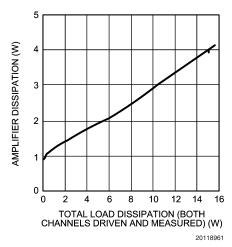

Class D Amplifier Dissipation vs Load Dissipation  $V_{DD}=12V,\,R_L=8\Omega$  Both channels driven and measured

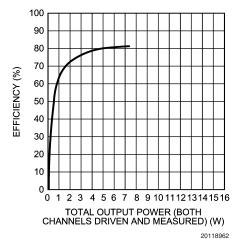

Class D Amplifier Efficiency vs Total Output Power  ${\rm V_{DD}=9V,\,R_L=8\Omega}$  Both channels driven and measured

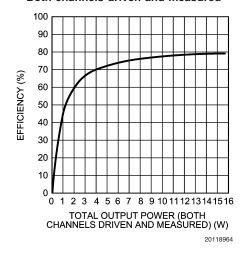

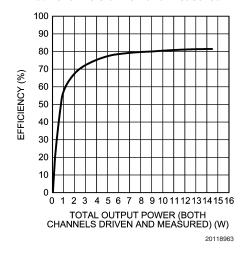

Class D Amplifier Efficiency vs Total Output Power  $V_{DD}=15.5V,\,R_{L}=8\Omega$  Both channels driven and measured

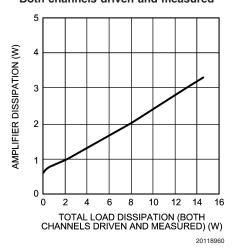

Class D Amplifier Dissipation vs Load Dissipation  $V_{DD}=\text{15.5V},\ R_L=8\Omega$  Both channels driven and measured

Class D Amplifier Efficiency vs Total Output Power  ${\rm V_{DD}=12V,\,R_L=8\Omega}$  Both channels driven and measured

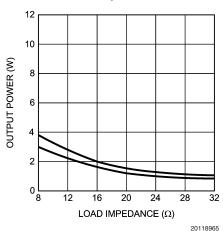

Output Power vs Load Resistance  $V_{DD}=9V, \\$  Upper curve = 10% THD+N, Lower curve = 1% THD+N

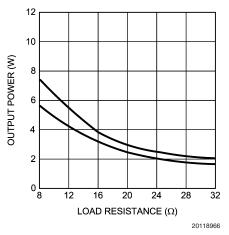

Output Power vs Load Resistance  $V_{DD} = 12V, \\$  Upper curve = 10% THD+N, Lower curve = 1% THD+N

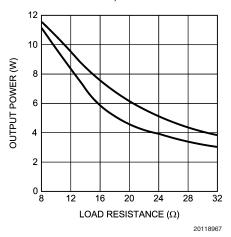

# Output Power vs Load Resistance V<sub>DD</sub> = 15.5V, Upper curve = 10% THD+N, Lower curve = 1% THD+N

#### Power Supply Current vs Power Supply Voltage

#### **General Features**

#### SYSTEM FUNCTIONAL INFORMATION

#### **Modulation Technique**

Unlike typical Class D amplifiers that use single-ended comparators to generate a pulse-width modulated switching waveform and RC timing circuits to set the switching frequency, the LM4681 uses a balanced differential floating modulator. Oscillation is a result of injecting complimentary currents onto the respective plates of a floating, on-die capacitor. The value of the floating capacitor and value of the components in the modulator's feedback network set the nominal switching frequency at 450kHz. Modulation results from imbalances in the injected currents. The amount of current imbalance is directly proportional to the applied input signal's magnitude and frequency.

Using a balanced, floating modulator produces a Class D amplifier that is immune to common mode noise sources such as substrate noise. This noise occurs because of the high frequency, high current switching in the amplifier's output stage. The LM4681 is immune to this type of noise because the modulator, the components that set its switching frequency, and even the load all float with respect to ground.

The balanced modulator's pulse width modulated output drives the gates of the LM4681's H-bridge configured output power MOSFETs. The pulse-train present at the power MOSFETs' output is applied to an LC low pass filter that removes the 450kHz energy component. The filter's output signal, which is applied to the driven load, is an amplified replica of the audio input signal.

#### **Shutdown Function**

The LM4681's digitally controlled shutdown function allows the user to place the amplifier in a shutdown mode while the system power supply remains active. Activating shutdown deactivates the output switching waveform and minimizes the quiescent current. Through the SPI/I<sup>2</sup>C digital interface, the Mode control register's Bit 0 is used to control the LM4681's shutdown function. A logic "0" activates shutdown, whereas a logic "1" returns the amplifier to its operational quiescent state. When the power supply voltage is first applied, the LM4681 is operating in the shutdown mode. For more information on the digital interface, see the section titled "SPI/I<sup>2</sup>C Serial Digital Interface."

#### **Mute Function**

The LM4681's digitally-controlled mute function allows the user to place the amplifier outputs in a muted mode while the amplifier's analog input signals remain active. Activating mute internally removes the analog input signal from the Class D and headphone amplifier inputs. While muted, the amplifier inputs and outputs retain their V<sub>DD</sub>/2 operational bias. Through the SPI/I²C digital interface, the Mode control register's Bit 1 is used to control the LM4681's audio mute function. A logic "0" activates mute, whereas a logic "1" deactivates mute. When the power supply voltage is first applied, the LM4681's headphone and Class D amplifier outputs are muted. More information on the digital interface is found in the section titled "SPI/I²C Serial Digital Interface."

#### Stereo Headphone Amplifier

The LM4681's stereo headphone amplifier operates continuously, even while the Class D amplifiers are active. When using headphones to listen to program material, it is usually

desirable to stop driving external speakers. This is easily achieved by using the active low HPSEL input. As shown in typical application schematic in Figure 1, with no headphones connected to the headphone jack the input voltage applied to the HPSEL pin is a logic low. In this state, the Class D amplifiers are active and able to drive external speakers. When headphones are plugged into the headphone jack, the switch internal to the jack is opened. This changes the voltage applied to the HPSEL pin to a logic high, shutting off the LM4681's Class D amplifiers.

#### **Under Voltage Proctection**

The under voltage protection disables the output driver section of the LM4681 while the supply voltage is below 8V. This condition may occur as power is first applied or during low line conditions, changes in load resistance, or when power supply sag occurs. The under voltage protection ensures that all of the LM4681's power MOSFETs are off. This action eliminates shoot-through current and minimizes output transients during turn-on and turn-off. The under voltage protection gives the digital logic time to stabilize into known states, further minimizing turn output transients.

#### **Power Supply Sequencing**

To ensure best performance, please observe the following power-up sequence. The  $\rm I^2CV_{DD}$  supply voltage should be applied first. Do not send any data to the LM4681's internal registers until the  $\rm V_{DD}$  is applied. This takes advantage of the LM4681's power-on reset, which activates the amplifier's shutdown and mute. Once  $\rm I^2CV_{DD}$  is applied, apply the  $\rm V_{DD}$  supply voltage. Prior to removing the two supply voltages, activate shutdown and mute.

#### **Turn-On Time**

The LM4681 has an internal timer that determines the amplifier's turn-on time. After power is first applied or the part returns from shutdown, the nominal turn-on time is 600ms. This delay allows all externally applied capacitors to charge to a final value of  $V_{\rm DD}/2$ . Further, during turn-on, the outputs are muted. This minimizes output transients that may occur while the part settles into is quiescent operating mode.

#### Output Stage Current Limit and Fault Detection Protection

The output stage MOSFETs are protected against output conditions that could otherwise compromise their operational status. The first stage of protection is output current limiting. When conditions that require high currents to drive a load, the LM4681's current limit circuitry clamps the output current at a nominal value of 2.5A. The output waveform is present, but may be clipped or its amplitude reduced. The same 2.5A nominal current limit also occurs if the amplifier outputs are shorted together or either output is shorted to  $V_{\rm DD}$  or GND.

The second stage of protection is an onboard fault detection circuit that continuously monitors the signal on each output MOSFET's gate and compares it against the respective drain voltage. When a condition is detected that violates a MOSFET's Safe Operating Area (SOA), the drive signal is disconnected from the output MOSFETs' gates. The fault detect circuit maintains this protective condition for approximately 600ms, at which time the drive signal is reconnected. If the fault condition is no longer present, normal operation resumes. If the fault condition remains, however, the drive signal is again disconnected.

### General Features (Continued)

#### **Thermal Protection**

The LM4681 has thermal shutdown circuitry that monitors the die temperature. Once the LM4681 die temperature reaches 170°C, the LM4681 disables the output switching waveform and remains disabled until the die temperature falls below 140°C (typ).

#### Over-Modulation Protection

The LM4681's over-modulation protection is a result of the preamplifier's (AMP1 and AMP2, Figure 1) inability to produce signal magnitudes that equal the power supply voltages. Since the preamplifier's output magnitude will always be less than the supply voltage, the duty cycle of the amplifier's switching output will never reach zero. Peak modulation is limited to a nominal 95%.

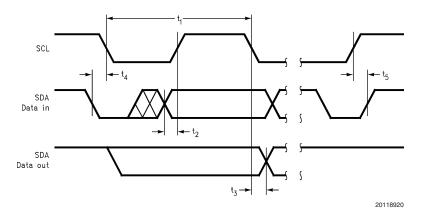

#### I<sup>2</sup>C Compatible Interface

The LM4681 uses a serial bus, which conforms to the  $I^2C$  protocol, to control the chip's functions with two wires: clock (SCL) and data (SDA). The clock line is uni-directional. The data line is bi-directional (open-collector). The maximum clock frequency specified by the  $I^2C$  standard is 400kHz. In this discussion, the master is the controlling microcontroller and the slave is the LM4681.

The  $I^2C$  address for the LM4681 is determined using the ADR pin. The LM4681's two possible  $I^2C$  chip addresses are of the form 110110X<sub>1</sub>0 (binary), where X<sub>1</sub> = 0, if ADR is logic low, and X<sub>1</sub> = 1, if ADR is a logic high. If the  $I^2C$  interface is used to address a number of chips in a system, the LM4681's chip address can be changed to avoid possible address conflicts.

The bus format for the I<sup>2</sup>C interface is shown in Figure 5. The bus format diagram is broken up into six major sections:

The "start" signal is generated by lowering the data signal while the clock signal is high. The start signal will alert all devices attached to the I<sup>2</sup>C bus to check the incoming address against their own address.

The 8-bit chip address is sent next, most significant bit first. The data is latched in on the rising edge of the clock. Each address bit must be stable while the clock level is high.

After the last bit of the address bit is sent, the master releases the data line high (through a pull-up resistor). Then the master sends an acknowledge clock pulse. If the LM4681 has received the address correctly, then it holds the data line low during the clock pulse. If the data line is not held low during the acknowledge clock pulse, then the master should abort the rest of the data transfer to the LM4681.

The 8 bits of data are sent next, most significant bit first. Each data bit should be valid while the clock level is stable high.

After the data byte is sent, the master must check for another acknowledge to see if the LM4681 received the data.

If the master has more data bytes to send to the LM4681, then the master can repeat the previous two steps until all data bytes have been sent.

The "stop" signal ends the transfer. To signal "stop", the data signal goes high while the clock signal is high. The data line should be held high when not in use.

#### **SPI Interface**

The LM4681's serial control interface is compatible with SPI signals and protocols. When using SPI signals, the ADR pin is the input for the SPI ENABLE signal, the SDA pin is the input for the SPI CLOCK signal, and the SDA pin is the SPI DATA input.

#### I<sup>2</sup>C/SPI Interface Power Supply Pin (I<sup>2</sup>C V<sub>DD</sub>)

The LM4681's I²C/SPI interface is powered up through the I²C/SPI V $_{DD}$  pin. The LM4681's I²C/SPI interface operates at a voltage level set by the I²C/SPI V $_{DD}$  pin which can be set independent to that of the main power supply pin V $_{DD}$ . This is ideal whenever logic levels for the I²C/SPI interface are dictated by a microcontroller or microprocessor that is operating at a lower supply voltage than the main battery of a portable system.

#### General Features (Continued)

#### I<sup>2</sup>C Timing Diagrams

FIGURE 1. I<sup>2</sup>C Bus Format

FIGURE 2. I<sup>2</sup>C Timing Diagram

#### **SPI Timing Diagram**

FIGURE 3.

#### **SPI Operational Requirements**

- 1. The maximum clock rate is 5MHz for the CLK pin.

- 2. CLK must remain logic-high for at least 100ns ( $t_{CH}$ ) after the rising edge of CLK, and CLK must remain logic-low for at least 100ns ( $t_{CL}$ ) after the falling edge of CLK.

- 3. Data bits are written to the DATA pin with the most significant bit (MSB) first.

- 4. The serial data bits are sampled at the rising edge of CLK. Any transition on DATA must occur at least 50ns ( $t_{\rm DS}$ ) before

- the rising edge of CLK. Also, any transition on DATA must occur at least 50ns ( $t_{\rm DH}$ ) after the rising edge of CLK and stabilize before the next rising edge of CLK.

- 5. ENABLE should be logic-low only during serial data transmission.

- 6. ENABLE must be logic-low at least 50ns ( $t_{\rm ES}$ ) before the first rising edge of CLK, and ENABLE has to remain logic-low at least 50ns ( $t_{\rm EH}$ ) after the eighth rising edge of CLK.

- 7. If ENABLE remains logic-high for more than 50ns before all 8 bits are transmitted then the data latch will be aborted.

# General Features (Continued)

- 8. If ENABLE is logic-low for more than 8 CLK pulses then only the first 8 data bits will be latched and activated at rising edge of eighth CLK.

- 9. ENABLE must remain logic-high for at least 50ns ( $t_{\rm EL}$ ).

- 10. Coincidental rising or falling edges of CLK and ENABLE are not allowed. If CLK is to be held logic-high after the data

transmission, the falling edge of CLK must occur at least 50ns ( $t_{\rm CS}$ ) before ENABLE transitions to logic-low for the next set of data.

#### **Volume Control**

The internal Stereo Volume Control is set by changing bits 0 through 4 in the SPI interface, as shown in table 3 below.

**TABLE 1. Volume Control Settings**

| Gai        | Gain (dB)          |       |       |       |       |       |

|------------|--------------------|-------|-------|-------|-------|-------|

| HP Outputs | Class D<br>Outputs | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| -64.94     | -48.03             | 0     | 0     | 0     | 0     | 0     |

| -64.94     | -48.03             | 0     | 0     | 0     | 0     | 1     |

| -56.94     | -36.03             | 0     | 0     | 0     | 1     | 0     |

| -47.94     | -31.03             | 0     | 0     | 0     | 1     | 1     |

| -42.94     | -26.03             | 0     | 0     | 1     | 0     | 0     |

| -37.94     | -21.03             | 0     | 0     | 1     | 0     | 1     |

| -33.94     | -17.03             | 0     | 0     | 1     | 1     | 0     |

| -31.94     | -15.03             | 0     | 0     | 1     | 1     | 1     |

| -28.94     | -12.03             | 0     | 1     | 0     | 0     | 0     |

| -25.94     | -9.03              | 0     | 1     | 0     | 0     | 1     |

| -22.94     | -6.03              | 0     | 1     | 0     | 1     | 0     |

| -20.94     | -4.03              | 0     | 1     | 0     | 1     | 1     |

| -18.94     | -2.03              | 0     | 1     | 1     | 0     | 0     |

| -16.94     | -0.03              | 0     | 1     | 1     | 0     | 1     |

| -14.94     | 1.97               | 0     | 1     | 1     | 1     | 0     |

| -12.94     | 3.97               | 0     | 1     | 1     | 1     | 1     |

| -10.94     | 5.97               | 1     | 0     | 0     | 0     | 0     |

| -8.94      | 7.97               | 1     | 0     | 0     | 0     | 1     |

| -6.94      | 9.97               | 1     | 0     | 0     | 1     | 0     |

| -4.94      | 11.97              | 1     | 0     | 0     | 1     | 1     |

| -2.94      | 13.97              | 1     | 0     | 1     | 0     | 0     |

| -0.94      | 15.97              | 1     | 0     | 1     | 0     | 1     |

| 1.06       | 17.97              | 1     | 0     | 1     | 1     | 0     |

| 3.06       | 19.97              | 1     | 0     | 1     | 1     | 1     |

| 6.06       | 22.97              | 1     | 1     | 0     | 0     | 0     |

| 7.07       | 23.97              | 1     | 1     | 0     | 0     | 1     |

| 8.06       | 24.97              | 1     | 1     | 0     | 1     | 0     |

| 9.06       | 25.97              | 1     | 1     | 0     | 1     | 1     |

| 10.06      | 26.97              | 1     | 1     | 1     | 0     | 0     |

| 11.06      | 27.97              | 1     | 1     | 1     | 0     | 1     |

| 12.06      | 28.97              | 1     | 1     | 1     | 1     | 0     |

| 13.06      | 29.97              | 1     | 1     | 1     | 1     | 1     |

### **Application Hints**

#### **SUPPLY BYPASSING**

Correct power supply bypassing has two important goals. The first is to reduce noise on the power supply lines and minimize deleterious effects that the noise may cause to the amplifier's operation. The second is to help stabilize an unregulated power supply and to improve the supply's transient response under heavy current demands. These two goals require different capacitor value ranges. Therefore, various types and values are recommended for supply bypassing. For noise de-coupling, generally small ceramic capacitors (0.01µF to 0.1µF) are recommended. Larger value (1µF to 10µF) tantalum capacitors are needed for the transient current demands. These two capacitors in parallel will do an adequate job of removing most noise from the supply rails and providing the necessary transient current. These capacitors should be placed as close as possible to each IC's supply pin(s) using leads as short as possible.

The LM4681 has two different set of  $V_{DD}$  pins: a set for power  $V_{DD}$  (PV $_{DD}$ ) and a set for signal  $V_{DD}$  (SV $_{DD}$ ). The parallel combination of the low value ceramic (0.1 $\mu$ F) and high value tantalum (10 $\mu$ F) should be used to bypass the PV $_{DD}$  pin. A small value (0.1 $\mu$ F) ceramic or tantalum can be used to bypass the SV $_{DD}$  pin.

#### **OUTPUT STAGE FILTERING**

The LM4681 requires a low pass filter connected between the amplifier's bridge output and the load. Figure 1 shows the recommended LC filter. A minimum value of 27µH is recommended. As shown in Figure 1, using the values of the components connected between the amplifier BTL outputs and the load achieves a 2nd-order lowpass filter response with a -3dB cutoff frequency of 25kHz.

# THD+N MEASUREMENTS AND OUT OF AUDIO BAND NOISE

THD+N (Total Harmonic Distortion plus Noise) is a very important parameter by which all audio amplifiers are measured. Often it is shown as a graph where either the output power or frequency is changed over the operating range. A very important variable in the measurement of THD+N is the bandwidth-limiting filter at the input of the test equipment. Class D amplifiers, by design, switch their output power devices at a much higher frequency than the accepted audio range (20Hz - 20kHz). Alternately switching the output voltage between V<sub>DD</sub> and GND allows the LM4681 to operate at much higher efficiency than that achieved by traditional Class AB amplifiers. Switching the outputs at high frequency also increases the out-of-band noise. Under normal circumstances the output lowpass filter significantly reduces this out-of-band noise. If the low pass filter is not optimized for a given switching frequency, there can be significant increase in out-of-band noise. THD+N measurements can be significantly affected by out-of-band noise, resulting in a higher than expected THD+N measurement. To achieve a more accurate measurement of THD, the test equipment's input bandwidth of the must be limited. Some common upper filter points are 22kHz, 30kHz, and 80kHz. The input filter limits the noise component of the THD+N measurement to a smaller bandwidth resulting in a more real-world THD+N value.

# **Revision History**

| Rev | Date    | Description                                                                                                                               |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 | 2/09/06 | Initial release.                                                                                                                          |

| 1.1 | 2/10/06 | Edited the PSRR Typical values in the Elect. Char table.                                                                                  |

| 1.2 | 3/08/06 | Did few texts (Gen Desc section) clean-up, then re-released D/S to the WEB.                                                               |

| 1.3 | 3/17/06 | Changed the typo under PSRR (Conditions-Vripple from 20mVp-p to 200mVp-p) in the EC Char table, then re-released D/S to the WEB (per KH). |

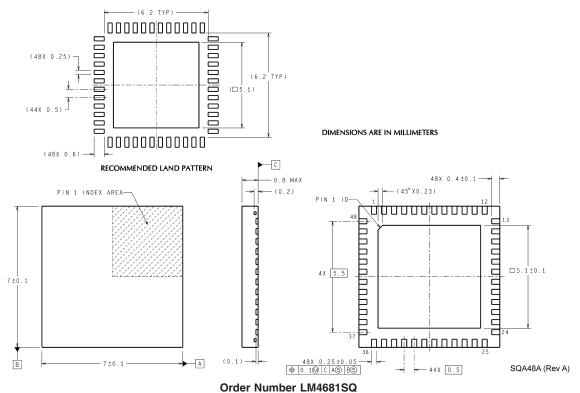

### Physical Dimensions inches (millimeters) unless otherwise noted

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

**NS Package Number SQA048AA**

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560