October 1991

# **TP5088 DTMF Generator for Binary Data**

### **General Description**

This CMOS device provides low cost tone-dialing capability in microprocessor-controlled telephone applications. 4-bit binary data is decoded directly, without the need for conversion to simulated keyboard inputs required by standard DTMF generators. With the TONE ENABLE input low, the oscillator is inhibited and the device is in a low power idle mode. On the low-to-high transition of TONE ENABLE, data is latched into the device and the selected tone pair from the standard DTMF frequencies is generated. An open-drain N-channel transistor provides a MUTE output during tone generation.

### **Features**

- Direct microprocessor interface

- Binary data inputs with latches

- Generates 16 standard tone pairs

- On-chip 3.579545 MHz crystal-controlled oscillator

- Better than 0.64% frequency accuracy

- High group pre-emphasis

- Low harmonic distortion

- MUTE output interfaces to speech network

- Low power idle mode

- 3.5V-8V operation

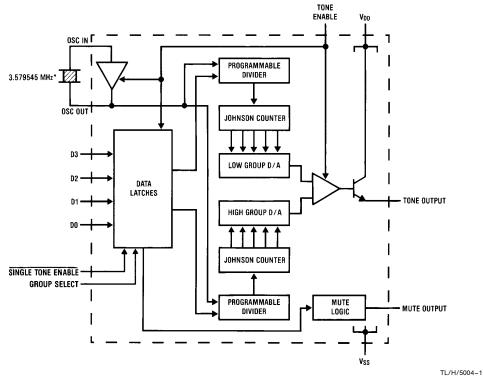

# **Block Diagram**

\*Crystal Specification: Parallel Resonant 3.579545 MHz,  $R_S \le 150\Omega$ , L = 100 mH,  $C_0 = 5$  pF,  $C_1 = 0.02$  pF.

© 1995 National Semiconductor Corporation TL/H/50

RRD-B30M115/Printed in U. S. A.

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>DD</sub>-V<sub>SS</sub>) 12V MUTE Voltage 12V

Maximum Voltage at

Any Other Pin  $V_{DD} + 0.3V$  to  $V_{SS} - 0.3V$

Operating Temperature, T<sub>A</sub>

Storage Temperature

Maximum Power Dissipation

-30°C to +70°C -55°C to +150°C 500 mW

### **Electrical Characteristics**

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{DD}=3.5V$  to 8V,  $T_A=0^{\circ}C$  to  $+70^{\circ}C$  by correlation with 100% electrical testing at  $T_A=25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization.

| Parameter                                                                      | Conditions                                                 | Min                 | Тур        | Max                 | Units          |

|--------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|------------|---------------------|----------------|

| Minimum Supply Voltage, V <sub>DD</sub> (min)                                  | Generating Tones                                           | 3.5                 |            |                     | V              |

| Minimum Supply Voltage for Data Input,<br>TONE ENABLE and MUTE Logic Functions |                                                            | 2                   |            |                     | V              |

| Operating Current<br>Idle<br>Generating Tones                                  | $R_L = \infty$ , D0-D3 Open $V_{DD} = 3.5V$ , Mute Open    |                     | 55<br>1.5  | 350<br>2.5          | μA<br>mA       |

| Input Pull-Up Resistance<br>D0-D3<br>TONE ENABLE                               |                                                            |                     | 100<br>50  |                     | kΩ<br>kΩ       |

| Input Low Level<br>TONE ENABLE, D0-D3                                          |                                                            |                     |            | 0.2 V <sub>DD</sub> | V              |

| Input High Level<br>TONE ENABLE, D0-D3                                         |                                                            | 0.8 V <sub>DD</sub> |            |                     | V              |

| MUTE OUT Sink Current<br>(TONE ENABLE LOW)                                     | $V_{DD} = 3.5V$ $V_{o} = 0.5V$                             | 0.4                 |            |                     | mA             |

| MUTE OUT Leakage Current<br>(TONE ENABLE HIGH)                                 | $V_{DD} = 3.5V$ $V_{o} = V_{DD}$                           |                     | 1          |                     | μΑ             |

| Output Amplitudes<br>Low Group<br>High Group                                   | $R_{L} = 240 \Omega$ $V_{DD} = 3.5V$ $T_{A} = 25^{\circ}C$ | 130<br>180          | 170<br>230 | 220<br>310          | mVrms<br>mVrms |

| Mean Output DC Offset                                                          | $V_{DD} = 3.5V$ $V_{DD} = 8V$                              |                     | 1.2<br>3.6 |                     | V<br>V         |

| High Group Pre-Emphasis                                                        |                                                            | 2.2                 | 2.7        | 3.2                 | dB             |

| Dual Tone/Total Harmonic Distortion Ratio                                      | 1 MHz Bandwidth, $V_{DD}=5V$ $R_L=240\Omega$               | -20                 |            |                     | dB             |

| Start-Up Time (to 90% Amplitude), t <sub>OSC</sub>                             |                                                            |                     | 4          |                     | ms             |

| Data Set-Up Time, t <sub>S</sub> (Figure 2)                                    | $V_{DD} = 5V$                                              | 100                 |            |                     | ns             |

| Data Hold Time, t <sub>H</sub>                                                 | $V_{DD} = 5V$                                              | 280                 |            |                     | ns             |

| Data Duration t <sub>W</sub>                                                   | $V_{DD} = 5V$                                              | 600                 |            |                     | ns             |

Note 1:  $R_L$  is the external load resistor connected from TONE OUT to  $V_{SS}$ .

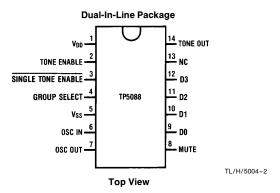

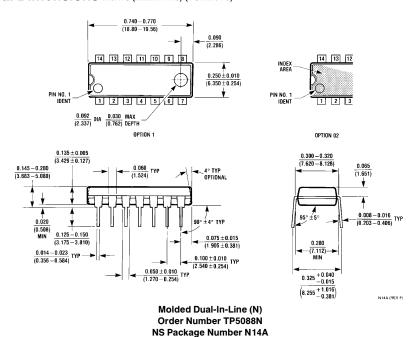

### **Connection Diagram**

Order Number TP5088WM or TP5088N See NS Package M14B or N14A

### **Functional Description**

With the TONE ENABLE pin pulled low, the device is in a low power idle mode, with the oscillator inhibited and the output transistor turned off. Data on inputs D0-D3 is ignored until a rising transition on TONE ENABLE. Data meeting the timing specifications is latched in, the oscillator and output stage are enabled, and tone generation begins. The decoded data sets the high group and low group programmable counters to the appropriate divide ratios. These counters sequence two ratioed-capacitor D/A converters through a series of 28 equal duration steps per sine wave cycle. On-chip regulators ensure good stability of tone amplitudes with variations in supply voltage and temperature. The two tones are summed by a mixer amplifier, with preemphasis applied to the high group tone. The output is an NPN emitter-follower requiring the addition of an external load resistor to VSS.

Table I shows the accuracies of the tone output frequencies and Table II is the Functional Truth Table.

**TABLE I. Output Frequency Accuracy**

| initial in output in equality meaning |                       |                          |                           |  |  |  |  |

|---------------------------------------|-----------------------|--------------------------|---------------------------|--|--|--|--|

| Tone<br>Group                         | Standard<br>DTMF (Hz) | Tone Output<br>Frequency | % Deviation from Standard |  |  |  |  |

| Low                                   | 697                   | 694.8                    | -0.32                     |  |  |  |  |

| Group                                 | 770                   | 770.1                    | +0.02                     |  |  |  |  |

| fL                                    | 852                   | 852.4                    | +0.03                     |  |  |  |  |

|                                       | 941                   | 940.0                    | -0.11                     |  |  |  |  |

| High                                  | 1209                  | 1206.0                   | -0.24                     |  |  |  |  |

| Group                                 | 1336                  | 1331.7                   | -0.32                     |  |  |  |  |

| f <sub>H</sub>                        | 1477                  | 1486.5                   | +0.64                     |  |  |  |  |

|                                       | 1633                  | 1639.0                   | +0.37                     |  |  |  |  |

|                                       |                       |                          |                           |  |  |  |  |

### Pin Descriptions

$\rm \textbf{V}_{DD}$  (Pin 1): This is the positive supply to the device, referenced to  $\rm V_{SS}.$  The collector of the TONE OUT transistor is also connected to this pin.

$\mathbf{V_{SS}}$  (Pin 5): This is the negative voltage supply. All voltages are referenced to this pin.

OSC IN, OSC OUT (Pins 6 and 7): All tone generation timing is derived from the on-chip oscillator circuit. A low-cost

3.579545 MHz A-cut crystal (NTSC TV color-burst) is needed between pins 6 and 7. Load capacitors and a feedback resistor are included on-chip for good start-up and stability. The oscillator is stopped when the TONE ENABLE input is pulled to logic low.

**TONE ENABLE Input (Pin 2):** This input has an internal pull-up resistor. When TONE ENABLE is pulled to logic low, the oscillator is inhibited and the tone generators and output transistor are turned off. A low to high transition on TONE ENABLE latches in data from D0-D3. The oscillator starts, and tone generation continues until TONE ENABLE is pulled low again.

**MUTE (Pin 8):** This output is an open-drain N-channel device that sinks current to  $V_{SS}$  when TONE ENABLE is low and no tones are being generated. The device turns off when TONE ENABLE is high.

**D0, D1, D2, D3 (Pins 9, 10, 11, 12):** These are the inputs for binary-coded data, which is latched in on the rising edge of TONE ENABLE. Data must meet the timing specifications of *Figure 2*. At all other times these inputs are ignored and may be multiplexed with other system functions.

**TONE OUT (Pin 14):** This output is the open emitter of an NPN transistor, the collector of which is connected internally to  $V_{DD}$ . When an external load resistor is connected from TONE OUT to  $V_{SS}$ , the output voltage on this pin is the sum of the high and low group tones superimposed on a DC offset. When not generating tones, this output transistor is turned off to minimize the device idle current.

**GROUP SELECT (Pin 4):** This pin is used to select the high group or low group frequency when the device is in single tone mode. It has an internal pull-up resistor. Leaving this pin open-circuit or pulling it to V<sub>DD</sub> will generate the high group, while pulling to V<sub>SS</sub> will generate the low group frequency at the TONE OUT pin.

| TABLE II. Functional Truth Table |             |    |    |      |           |                     |                     |     |

|----------------------------------|-------------|----|----|------|-----------|---------------------|---------------------|-----|

| Keyboard                         | Data Inputs |    |    | TONE | TONES OUT |                     | MUTE                |     |

| Equivalent                       | D3          | D2 | D1 | D0   | ENABLE    | f <sub>L</sub> (Hz) | f <sub>H</sub> (Hz) |     |

| X                                | х           | Х  | Х  | Х    | 0         | 0V                  | 0V                  | 0V  |

| 1                                | 0           | 0  | 0  | 1    |           | 697                 | 1209                | O/C |

| 2                                | 0           | 0  | 1  | 0    |           | 697                 | 1336                | O/C |

| 3                                | 0           | 0  | 1  | 1    |           | 697                 | 1477                | O/C |

| 4                                | 0           | 1  | 0  | 0    |           | 770                 | 1209                | O/C |

| 5                                | 0           | 1  | 0  | 1    |           | 770                 | 1336                | O/C |

| 6                                | 0           | 1  | 1  | 0    |           | 770                 | 1477                | O/C |

| 7                                | 0           | 1  | 1  | 1    | _         | 852                 | 1209                | O/C |

| 8                                | 1           | 0  | 0  | 0    |           | 852                 | 1336                | O/C |

| 9                                | 1           | 0  | 0  | 1    | _         | 852                 | 1477                | O/C |

| 0                                | 1           | 0  | 1  | 0    | _         | 941                 | 1336                | O/C |

| *                                | 1           | 0  | 1  | 1    | _         | 941                 | 1209                | O/C |

| #                                | 1           | 1  | 0  | 0    | _         | 941                 | 1477                | O/C |

| Α                                | 1           | 1  | 0  | 1    |           | 697                 | 1633                | O/C |

| В                                | 1           | 1  | 1  | 0    |           | 770                 | 1633                | O/C |

| С                                | 1           | 1  | 1  | 1    |           | 852                 | 1633                | O/C |

| D                                | 0           | 0  | 0  | 0    |           | 941                 | 1633                | O/C |

# Timing Diagram Typical Application DATA IN, 03-00 TONE ENABLE TONE OUT TONE OUT TONE OUT TONE OUT TL/H/5004-3 \*Adjust Re for desired tone amplitude. FIGURE 2 TL/H/5004-4

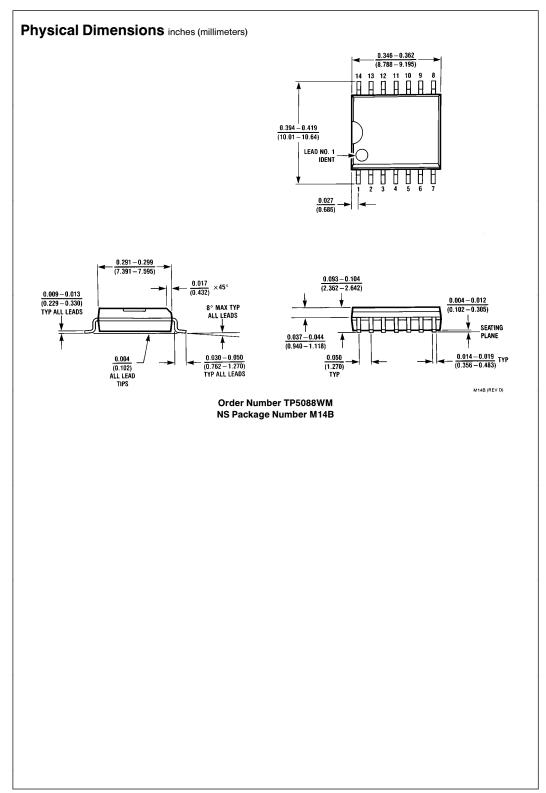

# Physical Dimensions inches (millimeters) (Continued)

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications