# V.32 FCC+ EMBEDDED DIRECT ACCESS ARRANGEMENT

Patented >6000 V isolation

#### **Features**

- Supports up to V.32 modem speeds

- Compliant with 49 PTTs, Proprietary isolation capacitor including FCC, JATE, China, and Korea Line voltage monitor

- Integrated analog front end (AFE) and 2- to 4-wire hybrid

- Integrated ring detector

- Pulse dialing support

**Digital televisions**

#### **Applications**

- V.32 modems

- Set-top boxes Fax machines

ePOS terminals

Multi-function printers

technology

Loop current monitor

8-pin ESOIC package

Caller ID support

Vending machines

interface to integrated DAA module

Lead-free and RoHS-compliant

#### Description

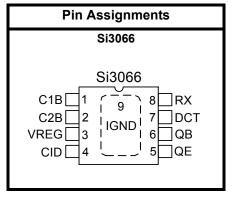

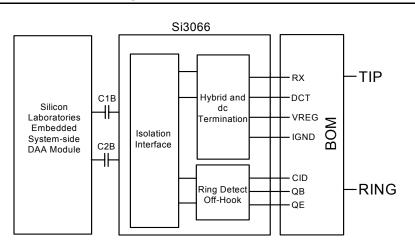

The Si3066 is an integrated direct access arrangement (DAA) for use with an integrated DAA system-side module. It includes a V.32 quality codec, dc termination, ac termination, and an integrated hybrid, eliminating the need for an analog front end (AFE), isolation transformer, relays, optoisolator, and a 2- to 4-wire hybrid. It interfaces directly to the integrated system-side module and features Silicon Laboratories' patented isolation technology. The Si3066 dramatically reduces the board space, component count, and cost required to implement a DAA compliant with the regulatory requirements of 49 different PTTs including FCC, JATE, China, and Korea.

US Patent # 5,870,046 US Patent # 6,061,009 Other Patents Pending

#### **Functional Block Diagram**

# TABLE OF CONTENTS

# <u>Section</u>

## <u>Page</u>

| 1. Electrical Specifications         2. Typical Application Schematic         3. Bill of Materials | .8<br>.9 |

|----------------------------------------------------------------------------------------------------|----------|

| 4. Telephone Line Interface Functional Description                                                 | 10       |

| 4.1. Initialization                                                                                |          |

| 4.2. Isolation Barrier                                                                             |          |

| 4.3. Parallel Handset Detection                                                                    | 10       |

| 4.4. Loop Current Sensing                                                                          | 11       |

| 4.5. Line Voltage Sensing                                                                          | 12       |

| 4.6. Off-Hook                                                                                      | 13       |

| 4.7. DC Termination                                                                                | 13       |

| 4.8. Transhybrid Balance                                                                           | 14       |

| 4.9. Ring Detection                                                                                |          |

| 4.10. Ring Validation                                                                              | 14       |

| 4.11. Ringer Impedance and Threshold                                                               | 15       |

| 4.12. DTMF Dialing                                                                                 | 15       |

| 4.13. Pulse Dialing                                                                                |          |

| 4.14. Receive Overload                                                                             |          |

| 4.15. On-Hook Line Monitor Mode                                                                    | 15       |

| 4.16. Caller ID                                                                                    |          |

| 4.17. Gain Control                                                                                 | 16       |

| 4.18. Sample Rate Converter                                                                        |          |

| 4.19. Power Management                                                                             |          |

| 4.20. Calibration                                                                                  |          |

| 4.21. Revision Identification                                                                      |          |

| 5. Register Summary                                                                                |          |

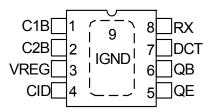

| 6. Pin Descriptions                                                                                |          |

| 7. Ordering Guide                                                                                  |          |

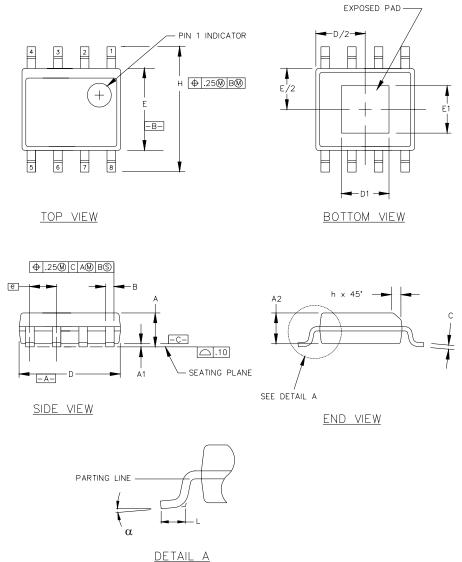

| 8. Package Outline: 8-Pin Exposed Pad SOIC                                                         |          |

| Contact Information                                                                                |          |

|                                                                                                    | -        |

## **1. Electrical Specifications**

#### Table 1. Recommended Operating Conditions

| Parameter <sup>*</sup>                                                                                                                                                                                                                | Symbol         | Test Condition | Min | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-----|-----|-----|------|

| Ambient Temperature                                                                                                                                                                                                                   | T <sub>A</sub> | F-Grade        | 0   | 25  | 70  | °C   |

| *Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.<br>Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated. |                |                |     |     |     |      |

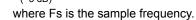

#### Table 2. DAA Loop Characteristics

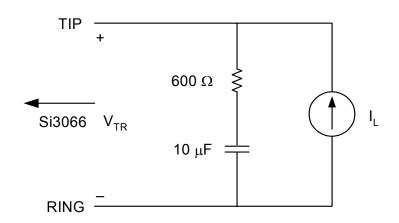

(V<sub>D</sub> = 3.0 to 3.6 V,  $T_A$  = 0 to 70 °C, see Figure 1)

| Parameter                                                                                                                                  | Symbol          | Test Condition                                         | Min | Тур | Max | Unit             |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------|-----|-----|-----|------------------|

| DC Termination Voltage                                                                                                                     | V <sub>TR</sub> | I <sub>L</sub> = 20 mA                                 |     |     | 7.5 | V                |

| DC Termination Voltage                                                                                                                     | V <sub>TR</sub> | I <sub>L</sub> = 120 mA                                | 9   |     |     | V                |

| On-Hook Leakage Current                                                                                                                    | I <sub>LK</sub> | V <sub>TR</sub> = -100 V                               |     |     | 12  | μA               |

| Operating Loop Current                                                                                                                     | I <sub>LP</sub> |                                                        | 15  |     | 120 | mA               |

| DC Ring Current                                                                                                                            |                 | dc current flowing through<br>ring detection circuitry | —   | 1.5 | 3   | μA               |

| Ring Detect Voltage*                                                                                                                       | V <sub>RD</sub> |                                                        | 10  | 15  | 35  | V <sub>rms</sub> |

| Ring Frequency                                                                                                                             | F <sub>R</sub>  |                                                        | 15  |     | 68  | Hz               |

| Ringer Equivalence Number                                                                                                                  | REN             |                                                        | _   |     | 0.2 |                  |

| *Note: The ring signal is guaranteed to not be detected below the minimum. The ring signal is guaranteed to be detected above the maximum. |                 |                                                        |     |     |     |                  |

#### **Table 3. DAA AC Characteristics**

(T<sub>A</sub> = 0 to 70 °C, Fs = 8 kHz)

| Parameter                                         | Symbol            | Test Condition                   | Min | Тур  | Max | Unit              |

|---------------------------------------------------|-------------------|----------------------------------|-----|------|-----|-------------------|

| Sample Rate                                       | Fs                |                                  | 7.2 | —    | 16  | kHz               |

| Receive Frequency Response                        |                   | Low –3 dBFS Corner               | —   | 5    | _   | Hz                |

| Transmit Full Scale Level <sup>1</sup>            | V <sub>FS</sub>   | –1 dBm                           | —   | 0.98 | _   | V <sub>PEAK</sub> |

| Receive Full Scale Level <sup>1,2</sup>           | V <sub>FS</sub>   | –1 dBm                           | —   | 0.98 | —   | VPEAK             |

| Dynamic Range <sup>3,4,5</sup>                    | DR                | IL = 100 mA                      | —   | 70   | _   | dB                |

| Dynamic Range <sup>3,4,5</sup>                    | DR                | I∟ = 20 mA                       | —   | 70   | _   | dB                |

| Transmit Total Harmonic Distortion <sup>5,6</sup> | THD               | I∟ = 20 mA                       | —   | 65   | —   | dB                |

| Receive Total Harmonic Distortion <sup>5,6</sup>  | THD               | I∟ = 20 mA                       | —   | 68   | _   | dB                |

| Dynamic Range (caller ID mode) <sup>7</sup>       | DR <sub>CID</sub> | V <sub>IN</sub> = 1 kHz, –13 dBm | —   | 50   | —   | dB                |

| Caller ID Full Scale Level                        | V <sub>CID</sub>  |                                  | —   | 6    | —   | V <sub>PP</sub>   |

Notes:

1. Measured at TIP and RING with 600  $\Omega$  termination at 1 kHz, as shown in Figure 1.

2. Receive full scale level produces –0.9 dBFS.

3. DR = 20 x log (rms  $V_{FS}$ /rms  $V_{IN}$ )+ 20 x log (rms  $V_{IN}$ /rms noise, excluding harmonics).  $V_{FS}$  is the –1 dBm full-scale level.

- Measurement is 300 to 3400 Hz. Applies to both transmit and receive paths.

V<sub>IN</sub> = 1 kHz, -3 dBFS

THD = 20 x log (rms distortion / rms signal).

DR<sub>CID</sub> = 20 x log (rms V<sub>CID</sub>/rms V<sub>IN</sub>)+ 20 x log (rms V<sub>IN</sub>/rms noise). V<sub>CID</sub> is the 6 V full-scale level.

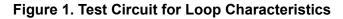

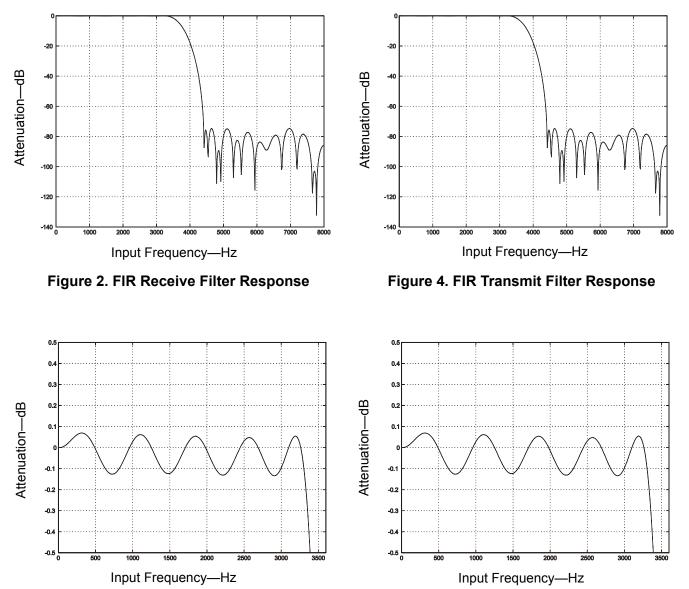

#### Table 4. Digital FIR Filter Characteristics—Transmit and Receive

(Sample Rate = 8 kHz,  $T_A = 0$  to 70 °C)

| Parameter                                                                                      | Symbol                | Min  | Тур | Max | Unit |  |

|------------------------------------------------------------------------------------------------|-----------------------|------|-----|-----|------|--|

| Passband (0.1 dB)                                                                              | F <sub>(0.1 dB)</sub> | 0    | _   | 3.3 | kHz  |  |

| Passband (3 dB)                                                                                | F <sub>(3 dB)</sub>   | 0    | _   | 3.6 | kHz  |  |

| Passband Ripple Peak-to-Peak                                                                   | i                     | -0.1 | _   | 0.1 | dB   |  |

| Stopband                                                                                       |                       | _    | 4.4 |     | kHz  |  |

| Stopband Attenuation                                                                           |                       | -74  | _   |     | dB   |  |

| Group Delay t <sub>gd</sub> — 12/Fs — s                                                        |                       |      |     |     |      |  |

| Note: Typical FIR filter characteristics for Fs = 8000 Hz are shown in Figures 2, 3, 4, and 5. |                       |      |     |     |      |  |

For Figures 2–5, all filter plots apply to a sample rate of Fs = 8 kHz. The filters scale with the sample rate as follows:  $F_{(0.1 \text{ dB})} = 0.4125 \text{ Fs}$  $F_{(-3 \text{ dB})} = 0.45 \text{ Fs}$

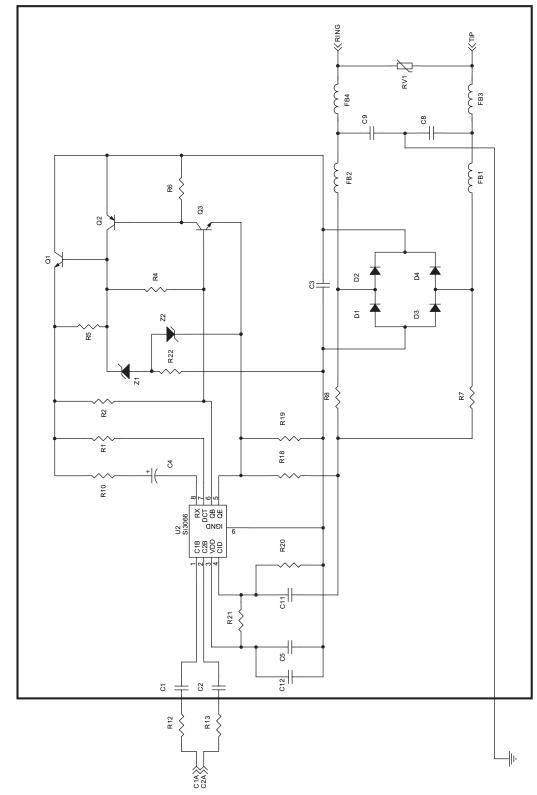

# 2. Typical Application Schematic

No Ground Plane In DAA Section

8

### 3. Bill of Materials

| Component                       | Value                        | Supplier(s)               |

|---------------------------------|------------------------------|---------------------------|

| C1, C2                          | 33 pF, Y2, X7R, ±10%         | Panasonic, Murata, Vishay |

| C3                              | 10 nF, 250 V, X7R, ±20%      | Venkel, SMEC              |

| C4                              | 1.0 μF, 35 V, Elec, ±20%     | Panasonic                 |

| C5                              | 0.1 μF, 16 V, X7R, ±20%      | Venkel, SMEC              |

| C8, C9                          | 680 pF, Y2, X7R, ±10%        | Panasonic, Murata, Vishay |

| C11                             | 220 pF, 50 V, X7R, ±10%      | Venkel, SMEC              |

| C12                             | DNP 0.1 µF, 16 V, X7R, ±20%  | Venkel, SMEC              |

| D1, D2, D3, D4 <sup>1</sup>     | Diode, 400 V, 1N4004         | Central Semiconductor     |

| FB1, FB2, FB3, FB4 <sup>2</sup> | Ferrite Bead, BLM18AG601SN1B | Murata                    |

| Q1, Q3                          | NPN, 300 V, MPSA42           | OnSemi, Fairchild         |

| Q2                              | PNP, 300 V, MPSA92           | OnSemi, Fairchild         |

| RV1                             | Sidactor, 275 V, 100A        | Teccor, Protek, ST Micro  |

| R1 <sup>3</sup>                 | <b>205</b> Ω, 1 W, 1%        | Venkel, SMEC, Panasonic   |

| R2 <sup>4</sup>                 | 243 Ω, 1 W, 1%               | Venkel, SMEC, Panasonic   |

| R4                              | 3.9 kΩ, 1/16 W, 5%           | Venkel, SMEC, Panasonic   |

| R5, R6                          | 100 kΩ, 1/16 W, 5%           | Venkel, SMEC, Panasonic   |

| R7, R8                          | 10 MΩ, 1/16 W, 5%            | Venkel, SMEC, Panasonic   |

| R10                             | 1 kΩ, 1/16 W, 5%             | Venkel, SMEC, Panasonic   |

| R12, R13                        | 56 Ω, 1/16 W, 1%             | Venkel, SMEC, Panasonic   |

| R22                             | DNP 0 Ω, 1/16 W, 5%          | Venkel, SMEC, Panasonic   |

| R18                             | 1.5 MΩ, 1/16 W, 5%           | Venkel, SMEC, Panasonic   |

| R19                             | 180 kΩ, 1/16 W, 5%           | Venkel, SMEC, Panasonic   |

| R20, R21                        | 3 MΩ, 1/16 W, 5%             | Venkel, SMEC, Panasonic   |

| U2                              | Si3066                       | Silicon Laboratories      |

| Z1, Z2                          | Zener Diode, 20 V, 1/2 W     | General Semiconductor     |

Notes:

1. Several diode bridge configurations are acceptable, parts such as a single DF-04S or two CMPD2004S dual diodes may be used (suppliers include General Semiconductor, Diodes Inc., etc.)

**2.** 0  $\Omega$  may be substituted for FB3, FB4 depending on emissions performance.

3. Three 619  $\Omega$  1/4 W 1% in parallel configuration may be substituted for R1.

4. Three 732  $\Omega$  1/4 W 1% in parallel configuration may be substituted for R2.

## 4. Telephone Line Interface Functional Description

Together, the integrated system-side and Si3066 comprise an integrated direct access arrangement (DAA) that provides a programmable line interface to meet the telephone line interface requirements of countries worldwide. The device implements Silicon Laboratories' patented isolation technology, which offers the highest level of integration by replacing an analog front end (AFE), an isolation transformer, relays, opto-isolators, a 2- to 4-wire hybrid, and other circuitry.

The Si3066 can be fully programmed to meet international requirements and is compliant with FCC, JATE, and numerous other country-specific PTT specifications as shown in Table 5. Also, the Si3066 meets the most stringent requirements for out-of-band energy, emissions, immunity, lightning surges, and safety.

#### 4.1. Initialization

The following is an example initialization procedure:

- 1. Select the desired sample rate using the SRC bits (Register 7, bits 3:0).

- 2. Power up the line side by clearing the PDL bit (Register 6, bit 4).

- 3. Enable AOUT (if applicable) by setting ARM[7:0] (Register 20, bits 7:0) and ATM[7:0] (Register 21, bits 7:0) to the desired level.

- 4. Prior to receiving or transmitting data, ensure FDT (Register 12) is set indicating the Si3066 is ready for normal operation.

After the procedure is complete, the DAA is ready for off-hook, on-hook line monitoring, and ring detection.

#### 4.2. Isolation Barrier

The Si3066 achieves an isolation barrier through lowcost, high-voltage capacitors in conjunction with Silicon Laboratories' proprietary signal processing techniques. These techniques eliminate signal degradation from capacitor mismatches, common mode interference, or noise coupling. The C1, C2, C8, and C9 capacitors isolate the system-side device from the Si3066 line-side device. All transmit, receive, control, ring detect, and caller ID data are communicated through this barrier. Y2 class capacitors can be used to achieve surge performance of 6 kV or greater.

The isolated communications link is disabled by default. To enable it, the PDL bit (Register 6, bit 4) must be cleared. No communication between the system-side and Si3066 can occur until this bit is cleared and the FDT bit (Register 12, bit 6) is high.

#### 4.3. Parallel Handset Detection

The Si3066 can detect a parallel handset going offhook. When the DAA is off-hook, the loop current can be monitored via the LCS bits (Register 12, bits 4:0). A significant drop in loop current can signal a parallel handset going off-hook. If a parallel handset causes the LCS bits to read 0s, the DropOut Detect Interrupt bit (Register 4, bit 3) can be checked to verify that a valid line still exists.

For the Si3066 to operate in parallel with another handset, the parallel handset must have a sufficiently high dc termination impedance to support two DAAs off hook on the same line.

# Table 5. Country-Specific PTT Specifications

| Country            |                           |  |  |  |

|--------------------|---------------------------|--|--|--|

| Argentina          | Kyrgyzstan                |  |  |  |

| Armenia            | Масао                     |  |  |  |

| Bahamas            | Mexico                    |  |  |  |

| Bangladesh         | Moldova                   |  |  |  |

| Belarus            | New Zealand <sup>2</sup>  |  |  |  |

| Bermuda            | Paraguay                  |  |  |  |

| Brazil             | Peru                      |  |  |  |

| Brunei             | Puerto Rico               |  |  |  |

| Canada             | Russia                    |  |  |  |

| Caribbean          | Saudi Arabia              |  |  |  |

| Chile              | Singapore                 |  |  |  |

| China              | South Korea <sup>3</sup>  |  |  |  |

| Colombia           | Sri Lanka                 |  |  |  |

| Costa Rica         | Taiwan                    |  |  |  |

| Dominican Republic | Thailand                  |  |  |  |

| Ecuador            | Tunisia                   |  |  |  |

| El Salvador        | UAE                       |  |  |  |

| Georgia            | Ukraine                   |  |  |  |

| Guam               | Uruguay                   |  |  |  |

| Hong Kong          | Uzbekistan                |  |  |  |

| India              | USA                       |  |  |  |

| Indonesia          | Venezuela                 |  |  |  |

| Japan <sup>1</sup> | Vietnam                   |  |  |  |

| Kazakhstan         | Yemen                     |  |  |  |

| Kuwait             |                           |  |  |  |

| Notes:             |                           |  |  |  |

| 1 DCD avaaada 200  | O: diaglaimar required in |  |  |  |

- 1. DCR exceeds 300  $\Omega$ ; disclaimer required in product documentation.

- **2.** 600  $\Omega$  ac termination used; disclaimer required in product documentation.

- **3.** Additional components required to pass ringer impedance specifications.

#### 4.4. Loop Current Sensing

The Si3066 measures loop current when off-hook. The LCS[4:0] bits measure loop current with 3.3 mA/bit resolution. The following functions can be performed with the LCS bits:

- While off-hook, detect if a parallel phone goes on- or off-hook.

- Determine if sufficient loop current is available for proper operation.

- Detect if there is an overload condition.

#### 4.4.1. Loop Current Measurement

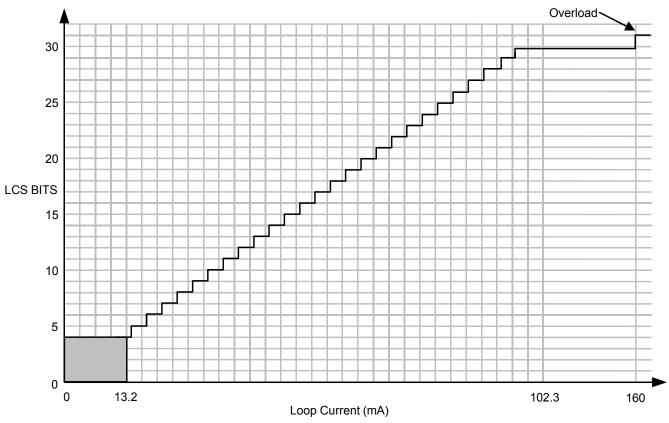

When the DAA is off-hook, the LCS[4:0] bits measure loop current with 3.3 mA/bit resolution. These bits can be used to detect another device going off-hook by monitoring the dc loop current. The transfer function for LCS is shown in Figure 6 and is detailed in Table 6. The LCS bits report loop current down to the minimum operating loop current for the DAA. Below this threshold, the reported value of loop current is unpredictable and may vary between zero and the minimum operating current.

When the LCS bits have reached their maximum value, the Loop Current Sense Overload Interrupt bit fires; however, LCSOI firing does not necessarily guarantee that an overload situation has occurred.

Figure 6. Typical LCS Transfer Function

| LCS[4:0]                                | Condition                                                                                                                       |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                         | Insufficient line current for normal operation. Use the DODI bit (Register 4, bit 3) to determine if a line is still connected. |

| 00100 <sub>b</sub> – 11110 <sub>b</sub> | Normal operation.                                                                                                               |

| 11111 <sub>b</sub>                      | Loop current is excessive (>160 mA).                                                                                            |

Table 6. Loop Current Sense Transfer Function

#### 4.5. Line Voltage Sensing

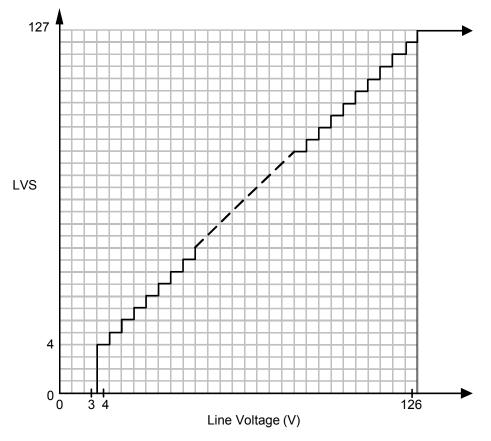

The Si3066 measures line voltage when on-hook. The LVS[6:0] bits (register 29) report line voltage with 1 V/bit resolution (typical). The LVS bits can be used to determine if a line is present and, if so, if it is idle or in use. Since these operations can be performed while on-hook, there is no need to enter the off-hook state and possibly disturb a call in progress to determine the status of the line. The typical LVS transfer function is shown in Figure 7 and detailed in Table 7.

Figure 7. Line Voltage Status Transfer Function

| Table 7. Line | Voltage | Status | Transfer | Function |

|---------------|---------|--------|----------|----------|

|---------------|---------|--------|----------|----------|

| LVS[6:0]                                    | Line Voltage                        |

|---------------------------------------------|-------------------------------------|

| 0000000b                                    | V <sub>LINE</sub> < 3.5 V           |

| 0000100 <sub>b</sub> – 1111110 <sub>b</sub> | 3.5 V ≤ V <sub>LINE</sub> < 126.5 V |

| 1111111 <sub>b</sub>                        | V <sub>LINE</sub> ≥ 126.5 V         |

#### 4.6. Off-Hook

The software generates an off-hook command by setting the OH bit (Register 5, bit 0). This seizes the line for incoming/outgoing calls and can also be used for pulse dialing. When on-hook, negligible dc current flows through the hookswitch. When off-hook, the hookswitch transistor pair, Q1 and Q2, turn on. A termination impedance is applied across TIP and RING and causes dc loop current to flow.

Several events occur internally to the DAA when the OH bit is set. There is a 250 µs latency for the off-hook command to communicate to the line-side device. When the line-side device goes off-hook, an off-hook counter forces a delay before transmission or reception can

occur. After this, an ADC calibration is performed for 256 ms. The ADC calibration can be disabled by setting the ADCC bit (Register 17, bit 5). Refer to Section "4.20. Calibration" on page 16 for more information on automatic calibration. To calculate the total time required to go off-hook and start transmission or reception, the digital filter delay (typically 1.5 ms with the FIR filter) should be included in the calculation.

#### 4.7. DC Termination

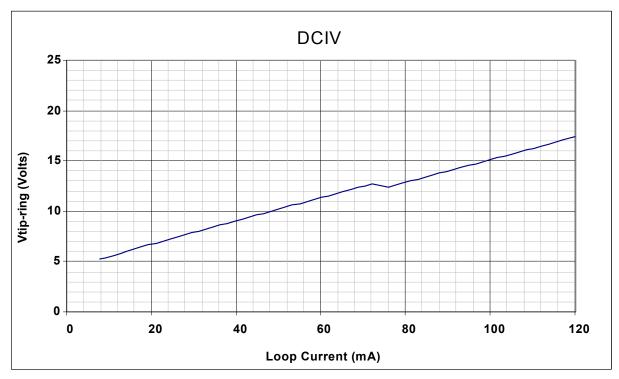

The Si3066 dc I/V characteristics, shown in Figure 8, support a transmit full scale level of -1 dBm at TIP and RING. This meets FCC requirements and the requirements of many other countries.

Figure 8. DC I/V Characteristics

#### 4.8. Transhybrid Balance

The Si3066 contains an on-chip analog hybrid that performs the 2- to 4-wire conversion and near-end echo cancellation.

#### 4.9. Ring Detection

Ring detection can be performed by monitoring the ring detector output or by observing the audio CODEC data. The ring detector output can be monitored with the register bits, RDTN, RDTP, and RDT (Register 5, bits 6, 5, and 2). Software must detect the frequency of the ring signal to distinguish a ring from pulse dialing by telephone equipment connected in parallel.

Alternatively, hardware ring validation can be used. See Section "4.10. Ring Validation".

The ring detector output is controlled by the RFWE bit (Register 18, bit 1). When the RFWE bit is 0 (default mode), only positive ring signals are reported by the ring detector. A positive ring signal is defined as a voltage greater than the ring threshold at the QE pin. Conversely, a negative ring signal is defined as a voltage less than the negative ring threshold. When the RFWE bit is 1, the ring detector reports both positive and negative ring signals.

The RDTP and RDTN behavior is based on the ring voltage. When the signal is above the positive ring threshold, the RDTP bit is set. When the signal is below the negative ring threshold, the RDTN bit is set. When the signal is between these thresholds, neither bit is set. The RDT behavior is also based on the ring voltage. When the RFWE bit is 0, a positive ring signal sets the RDT bit for a period of time. When the RFWE bit is 1, either a positive or negative ring signal sets the RDT bit.

The audio CODEC data also signals ring events when on-hook. If the RFWE bit is 0, the CODEC output is fixed at –32768 when a ring is not present. The CODEC data becomes +32767 upon detection of a positive ring. Negative rings will be ignored and have no effect on the CODEC data while RFWE is 0.

When on-hook with RFWE = 1, the CODEC data is fixed at +1228 when a ring is not present. The CODEC data becomes +32767 upon detection of a positive ring or -32768 upon detection of a negative ring.

The RDT bit acts like a one shot. When a new ring signal is detected, the one shot is reset. If no new ring signals are detected before the one shot counter reaches 0 (5 seconds), the RDT bit returns to 0. The RDT bit is also reset to 0 by an off-hook event.

#### 4.10. Ring Validation

This feature prevents false ring detection by validating the ring parameters. Invalid signals, such as linevoltage changes when a parallel handset goes off-hook, pulse dialing, polarity reversals, and high-voltage line tests, are ignored. Ring validation can be enabled during normal operation and in low-power sleep mode.

The ring validation circuit operates by calculating the time between alternating crossings of positive and negative ring thresholds to validate that the ring frequency is within tolerance. High- and low-frequency tolerances are programmable in the RAS[5:0] and RMX[5:0] fields. The RCC[2:0] bits define the length of time the ring signal must be within tolerance. Once the duration of the ring frequency is validated by the RCC bits, the circuitry stops checking for frequency tolerance and begins checking for the end of the ring signal, which is defined by a lack of additional threshold crossings for a period of time configured by the RTO[3:0] bits. When the ring frequency is first validated, a timer defined by the RDLY[2:0] bits is started. If the RDLY[2:0] timer expires before the ring timeout, the ring is validated, and a valid ring is indicated. If the ring timeout expires before the RDLY[2:0] timer, a valid ring is not indicated.

Ring validation requires five parameters:

- Timeout parameter to place a lower limit on the frequency of the ring signal on the RAS[5:0] bits (Register 24, bits 5:0). The frequency is measured by calculating the time between crossings of positive and negative ring thresholds.

- Minimum count to place an upper limit on the frequency on the RMX[5:0] bits (Register 22, bits [5:0]).

- Time interval over which the ring signal must be the correct frequency on the RCC[2:0] bits (Register 23, bits [2:0]).

- Timeout period that defines when the ring pulse has ended with the most recent ring threshold crossing on the RTO [3:0] bits (Register 23, bits 6:3).

- Delay period between when the ring signal is validated and when a valid ring signal is indicated to help accommodate distinctive ring on the RDLY [2] bit (Register 23, bit 7).

The ring validation enable bit, RNGV (Register 24, bit 7), enables or disables the ring validation feature in normal operating mode and low-power sleep mode. For further details, see "AN72: Ring Detection/Validation with the Si305x DAAs."

14

#### 4.11. Ringer Impedance and Threshold

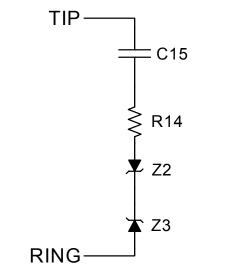

The ring detector in many DAAs is ac-coupled to the line with a large 1  $\mu$ F, 250 V decoupling capacitor. The ring detector on the Si3066 is resistively coupled to the line. The network presents a high ringer impedance to the line of approximately 5 M $\Omega$  to meet the majority of PTT specifications, including FCC. The ringer impedance network shown in Figure 9 is required for compliance with the ringer impedance requirements of South Korea. This network is only required if the application will be deployed in South Korea. The network components are detailed in Table 8.

Figure 9. South Korea Ringer Impedance Network

# Table 8. South Korea Ringer ImpedanceNetwork Components

| ltem | Value         |

|------|---------------|

| C15  | 1 mF, 250 V   |

| R14  | 7.5 kΩ, 1/4 W |

| Z2   | 18 V          |

| Z3   | 18 V          |

#### 4.12. DTMF Dialing

The Si3066 meets all the country requirements for DTMF dialing listed in Table 5 on page 10. Higher DTMF levels can be achieved if the amplitude is increased and the peaks of the DTMF signal are clipped at digital full scale, avoiding wrapping the waveform.

Clipping the signal produces distortion and intermodulation of the signal. Generally, increased distortion between 10 and 20% is acceptable during

DTMF signaling. DTMF levels several dB higher can be achieved with this technique, compared with a digital full-scale peak signal.

#### 4.13. Pulse Dialing

Going off- and on-hook to generate make and break pulses accomplishes pulse dialing. The nominal rate is 10 pulses per second.

#### 4.14. Receive Overload

Certain line events, such as an off-hook event on a parallel phone, a billing tone, or a polarity reversal, can cause a receiver overload. Although the DAA may remain off-hook during such an event, the data received from the line may be corrupted.

If a disturbance on the line causes the loop current to collapse below the minimum operating current, the dropout detect bit, DOD, is set. An interrupt will be generated if the dropout detect interrupt mask bit, DODM, is set.

#### 4.15. On-Hook Line Monitor Mode

The DAA monitors line activity when in on-hook linemonitor mode. This mode detects caller ID data, and no line current is drawn. See Section "4.16. Caller ID" on page 15. This mode is enabled by setting the ONHM bit (Register 5, bit 3). ARX [2:0] (Register 15, bits 2:0) provides gain to the normal receive path of the DAA and functions as a gain bit for the on-hook line monitor.

#### 4.16. Caller ID

The DAA can pass caller ID data from the phone line to a software caller ID decoder.

#### 4.16.1. Type I Caller ID

Type I Caller ID sends the CID data while the phone is on-hook. In systems where the caller ID data is passed on the phone line between the first and second rings, utilize the following method to capture the caller ID data:

- After identifying a ring signal using one of the methods described in Section "4.9. Ring Detection" on page 14, determine when the first ring has completed.

- 2. Assert the ONHM bit (Register 5, bit 3) to enable the caller ID ADC. This low-current ADC, which is powered from the system-side device, digitizes the caller ID data.

- 3. Clear the ONHM bit after the caller ID data is received.

#### 4.16.2. Type II Caller ID

Type II Caller ID sends the CID data while the phone is off-hook and is often referred to as caller ID/call waiting (CID/CW). To receive the CID data while off-hook, use the following procedure:

- 1. The Caller Alert Signal (CAS) tone is sent from the Central Office (CO) and is digitized along with the line data. The software must detect the presence of this tone.

- 2. Since the DAA is the only device on the line and is Type II CID-compliant, the software must mute its upstream data output to avoid propagation of its reply tone and the subsequent CID data. After muting its upstream data output, the software must then return an acknowledgement (ACK) tone to the CO to request the transmission of the CID data.

- 3. The CO then responds with the CID data, and the software unmutes the upstream data output and continues with normal operation.

- 4. The muting of the upstream data path by the software mutes the handset in a telephone application so the user cannot hear the acknowledgement tone and CID data being sent.

The CID data presented to the software could have up to a 10% dc offset. The software caller ID decoder must either use a high-pass or a band-pass filter to accurately retrieve the caller ID data.

#### 4.17. Gain Control

The Si3066 supports multiple receive gain and transmit attenuation settings (Register 15). The receive path supports gains of 0, 3, 6, 9, and 12 dB, as selected with the ARX[2:0] bits. The receive path can be muted with the RXM bit. The transmit path supports attenuations of 0, 3, 6, 9, and 12 dB, as selected with the ATX[2:0] bits. The transmit path can be muted with the TXM bit.

#### 4.18. Sample Rate Converter

The SRC [3:0] bits (Register 7, bits 3:0) are used to select the sample rate. The following sample rates are supported: 7200, 8000, 8229, 8400, 9000, 9600, 10286, 12000, 13714, and 16000 Hz.

#### 4.19. Power Management

The Si3066 supports four basic power management operation modes: normal operation, reset operation, sleep mode, and full powerdown mode. The power management modes are controlled by the PDL and PDN bits (Register 6, bits [4:3]).

Upon powerup or following a reset, the Si3066 is in reset operation. The PDL bit is set, and the PDN bit is cleared. The system-side module is fully operational

except for the isolated capacitor link. No communication between the system side and Si3066 can occur during reset operation. Register bits associated with the Si3066 are not valid in this mode.

The most common mode of operation is normal operation. The PDL and PDN bits are cleared, and the capacitive link is passing information between the system side and the Si3066. A valid sample rate must be programmed before entering this mode.

The Si3066 supports a low-power sleep mode for the wake-up-on-ring feature of many modems. The sample rate must be programmed with a valid non-zero value before enabling sleep mode. The PDN bit must then be set; the PDL <u>bit cleared</u>. To take the DAA out of sleep mode, pulse (RESET) low.

In summary, the powerdown sequence for sleep mode is as follows:

- 1. SRC[3:0] must have a valid non-zero value.

- 2. Set the PDN bit (Register 6, bit 3) and clear the PDL bit (Register 6, bit 4).

The power-up sequence is as follows:

- 1. Reset the DAA by pulsing the  $\overline{\text{RESET}}$  pin.

- 2. Program registers to required settings.

The Si3066 also supports an additional powerdown mode. When the PDN and PDL bits are set, the DAA enters a complete powerdown mode and draws negligible current (deep sleep mode). Normal operation is restored using the same process for taking the DAA out of sleep mode.

#### 4.20. Calibration

The Si3066 initiates an auto-calibration by default when the device goes off-hook or experiences a loss in line power. Calibration removes offsets that are present in the on-chip ADC and could affect the ADC dynamic range. Auto-calibration is initiated after the DAA dc termination stabilizes and takes 273 ms to complete.

#### 4.21. Revision Identification

The revision of the system-side module and line-side (Si3066) can be determined using the REVA[3:0] bits (Register 11, bits 3:0) and REVB[3:0] bits (Register 13, bits 5:2), respectively. Table 9 lists the revision values.

Table 9. Si3066 Revision Levels

| Si3066 Revision | Si3066 REVB[3:0] |

|-----------------|------------------|

| A               | 1000             |

| В               | 1001             |

# 5. Register Summary

| Offset | Name                            | Bit 7   | Bit 6    | Bit 5  | Bit 4  | Bit 3    | Bit 2    | Bit 1    | Bit 0 |

|--------|---------------------------------|---------|----------|--------|--------|----------|----------|----------|-------|

| 1      | Control 1                       | SR      |          | PWM    | M[1:0] | PWME     |          | IDL      |       |

| 2      | Control 2                       |         |          |        | WDTE   | AL       | RDM      | HBE      | RXE   |

| 3      | Interrupt Mask                  | RDTM    |          | FDTM   |        | DODM     | LCSM     |          |       |

| 4      | Interrupt Status                | RDTI    |          | FDTI   |        | DODI     | LCSI     |          |       |

| 5      | DAA Control 1                   |         | RDTN     | RDTP   |        | ONHM     | RDT      |          | OH    |

| 6      | DAA Control 2                   |         |          |        | PDL    | PDN      |          |          |       |

| 7      | Sample Rate Control             |         |          |        |        |          | SRO      | C[3:0]   |       |

| 8      | Reserved                        |         |          |        |        |          |          |          |       |

| 9      | Reserved                        |         |          |        |        |          |          |          |       |

| 10     | DAA Control 3                   |         |          |        |        |          |          |          | DDL   |

| 11     | System-Side Revision            |         | LSIE     | 0[3:0] |        |          | REV      | 'A[3:0]  |       |

| 12     | Line-Side Status                |         | FDT      |        |        |          | LCS[4:0] | ]        |       |

| 13     | Line-Side Revision              |         |          |        | REVE   | 8[3:0]   |          |          |       |

| 14     | Reserved                        |         |          |        |        |          |          |          |       |

| 15     | TX/RX Gain Control              | TXM     | ATX[2:0] |        |        | RXM      |          | ARX[2:0] |       |

| 16     | Reserved                        |         |          |        |        |          |          |          |       |

| 17     | Calibration                     |         |          | ADCC   |        |          |          |          |       |

| 18     | International Control 3         |         |          |        |        |          |          | RFWE     |       |

| 19     | Dropout Detect                  |         |          |        |        |          |          | DOD      |       |

| 20     | Call Progress<br>RX Attenuation |         |          |        | ARM    | [7:0]    |          | ·        |       |

| 21     | Call Progress<br>TX Attenuation |         |          |        | ATM    | [7:0]    |          |          |       |

| 22     | Ring Validation Control 1       | RDLY    | ′[1:0]   |        |        | RMX      | ([5:0]   |          |       |

| 23     | Ring Validation Control 2       | RDLY[2] |          | RTO    | [3:0]  |          |          | RCC[2:0] |       |

| 24     | Ring Validation Control 3       | RNGV    |          |        |        | RAS      | [5:0]    |          |       |

| 25     | Reserved                        |         |          |        |        |          |          |          |       |

| 26     | Reserved                        |         |          |        |        |          |          |          |       |

| 27     | Reserved                        |         |          |        |        |          |          |          |       |

| 28     | Reserved                        |         |          |        |        |          |          |          |       |

| 29     | Line Voltage Status             |         |          | ı      | 1      | LVS[6:0] | _VS[6:0] |          |       |

| 30–59  | Reserved                        |         |          |        |        |          |          |          |       |

| 60     | Line-side ID                    |         |          |        |        |          | LSID4    |          |       |

#### DAA Register 1. Control 1

| Bit  | D7  | D6 | D5        | D4 | D3   | D2 | D1  | D0 |

|------|-----|----|-----------|----|------|----|-----|----|

| Name | SR  |    | PWMM[1:0] |    | PWME |    | IDL |    |

| Туре | R/W |    | R/        | W  | R/W  |    | R/W |    |

Reset settings = 0000\_0x0x

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SR        | Software Reset.0 = Enables DAA for normal operation.1 = Sets all registers to their reset value.Note: Bit clears automatically after being set.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6   | Reserved  | Always write as zero. Reads undefined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5:4 | PWMM[1:0] | <ul> <li>Pulse-Width Modulation Mode.</li> <li>Selects the type of signal on the call progress AOUT pin.</li> <li>00 = PWM output clocked at 16.384 MHz. A local density of 1s and 0s tracks the combined transmit and receive signal.</li> <li>01 = Balanced conventional PWM output signal has high and low portions of the modulated pulse centered on the 32 kHz sample clock.</li> <li>10 = Conventionally PWM output signal returns to 0 at 32 kHz intervals and rises at a time in the 32 kHz period proportional to the instantaneous amplitude.</li> <li>11 = Reserved.</li> </ul> |

| 3   | PWME      | Pulse-Width Modulation Enable.0 = Call progress PWM AOUT disabled.1 = Call progress PWM AOUT enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2   | Reserved  | Read returns zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | IDL       | <ul> <li>Isolation Digital Loopback.</li> <li>0 = Digital loopback across isolation barrier disabled.</li> <li>1 = Enables digital loopback mode across isolation barrier. The line-side device must be enabled and off-hook before setting this mode. This data path includes RX and TX filters. A valid phone line is not necessary for this mode.</li> </ul>                                                                                                                                                                                                                             |

| 0   | Reserved  | Read returns zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### DAA Register 2. Control 2

| Bit  | D7 | D6 | D5 | D4   | D3  | D2  | D1  | D0  |

|------|----|----|----|------|-----|-----|-----|-----|

| Name |    |    |    | WDTE | AL  | RDM | HBE | RXE |

| Туре |    |    |    | R/W  | R/W | R/W | R/W | R/W |

#### Reset settings = xxx0\_0011

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                                                                                                                                                                              |

| 4   | WDTE     | <ul> <li>DAA Watchdog Timer Enable.</li> <li>0 = Watchdog timer disabled.</li> <li>1 = Watchdog timer enabled. When set, this bit is cleared only by a hardware reset. The watchdog timer monitors DAA register writes. If a register write does not occur within a 4.096 second window, the DAA is put into an on-hook state. Only a write of a DAA register restarts the timer.</li> </ul> |

| 3   | AL       | Analog Loopback.<br>0 = Analog loopback mode disabled.<br>1 = Enables external analog loopback mode.                                                                                                                                                                                                                                                                                         |

| 2   | RDM      | Ring Detect Mode.0 = Ring detect on positive threshold.1 = Ring detect on positive and negative threshold.                                                                                                                                                                                                                                                                                   |

| 1   | HBE      | Hybrid Enable.0 = Disconnects hybrid in transmit path.1 = Connects hybrid in transmit path.                                                                                                                                                                                                                                                                                                  |

| 0   | RXE      | Receive Enable.0 = Receive path disabled.1 = Enables receive path.                                                                                                                                                                                                                                                                                                                           |

#### DAA Register 3. Interrupt Mask

| Bit  | D7   | D6 | D5   | D4 | D3   | D2   | D1 | D0 |

|------|------|----|------|----|------|------|----|----|

| Name | RDTM |    | FDTM |    | DODM | LCSM |    |    |

| Туре | R/W  |    | R/W  |    | R/W  | R/W  |    |    |

Reset settings =  $0x0x_00xx$

| Bit | Name     | Function                                                        |

|-----|----------|-----------------------------------------------------------------|

| 7   | RDTM     | Ring Detect Interrupt Mask.                                     |

|     |          | 0 = A ring signal does not cause an interrupt.                  |

|     |          | 1 = A ring signal causes an interrupt.                          |

| 6   | Reserved | Always write this bit to zero. Reads undefined.                 |

| 5   | FDTM     | Frame Detect Interrupt Mask.                                    |

|     |          | 0 = Isolation capacitor frame lock does not cause an interrupt. |

|     |          | 1 = Isolation capacitor frame lock causes an interrupt.         |

| 4   | Reserved | Always write this bit to zero. Reads undefined.                 |

| 3   | DODM     | Drop Out Detect Interrupt Mask.                                 |

|     |          | 0 = A line supply dropout does not cause an interrupt.          |

|     |          | 1 = A line supply dropout causes an interrupt.                  |

| 2   | LCSM     | Loop Current Sense Overload Interrupt Mask.                     |

|     |          | 0 = Loop current sense overload does not cause an interrupt.    |

|     |          | 1 = Loop current sense overload causes an interrupt.            |

| 1:0 | Reserved | Always write this bit to zero. Reads undefined.                 |

#### DAA Register 4. Interrupt Status

| Bit  | D7   | D6 | D5   | D4 | D3   | D2   | D1 | D0 |

|------|------|----|------|----|------|------|----|----|

| Name | RDTI |    | FDTI |    | DODI | LCSI |    |    |

| Туре | R/W  |    | R/W  |    | R/W  | R/W  |    |    |

Reset settings = 0x0x\_00xx

| Bit | Name     | Function                                                                                                                                                                                                                                                                |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RDTI     | Ring Detect Interrupt Status.<br>0 = No ring.                                                                                                                                                                                                                           |

|     |          | 1 = Ring detected. Write 0 to clear.                                                                                                                                                                                                                                    |

| 6   | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                                                         |

| 5   | FDTI     | <ul> <li>Frame Detect Interrupt Status.</li> <li>0 = Frame detect established.</li> <li>1 = Frame detect lost. Write 0 to clear.</li> </ul>                                                                                                                             |

| 4   | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                                                         |

| 3   | DODI     | Drop Out Detect Interrupt Status.<br>0 = Line-side power available.<br>1 = Line-side power unavailable.                                                                                                                                                                 |

| 2   | LCSI     | <ul> <li>Loop Current Sense Overload Interrupt.</li> <li>0 = The LCS bits have not reached max (all ones).</li> <li>1 = The LCS bits have reached max value. If the LCSM bit is set, a hardware interrupt occurs. This bit must be written to 0 to clear it.</li> </ul> |

| 1:0 | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                                                         |

#### DAA Register 5. DAA Control 1

| Bit  | D7 | D6   | D5   | D4 | D3   | D2  | D1 | D0  |

|------|----|------|------|----|------|-----|----|-----|

| Name |    | RDTN | RDTP |    | ONHM | RDT |    | ОН  |

| Туре |    | R    | R    |    | R/W  | R   |    | R/W |

Reset settings = x00x\_00x0

| Bit | Name     | Function                                                                                                                                                                                                                                |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                         |

| 6   | RDTN     | Ring Detect Signal Negative.0 = No ring signal is occurring.1 = A negative ring signal is occurring.                                                                                                                                    |

| 5   | RDTP     | Ring Detect Signal Positive.0 = No ring signal is occurring.1 = A positive ring signal is occurring.                                                                                                                                    |

| 4   | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                         |

| 3   | ONHM     | <ul> <li>On-Hook Line Monitor.</li> <li>0 = Normal on-hook mode.</li> <li>1 = Enables low-power monitoring mode allowing the DAA to receive line activity without going off-hook. This mode is used for caller-ID detection.</li> </ul> |

| 2   | RDT      | Ring Detect.0 = Reset either five seconds after last positive ring is detected or when the system executes an off-hook.1 = Indicates a ring is occurring.                                                                               |

| 1   | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                         |

| 0   | ОН       | Off-Hook.<br>0 = Line-side device on-hook.<br>1 = Causes the line-side device to go off-hook.                                                                                                                                           |

#### DAA Register 6. DAA Control 2

| Bit  | D7 | D6 | D5 | D4  | D3  | D2 | D1 | D0 |

|------|----|----|----|-----|-----|----|----|----|

| Name |    |    |    | PDL | PDN |    |    |    |

| Туре |    |    |    | R/W | R/W |    |    |    |

| Bit | Name     | Function                                                                                                                                                                |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                         |

| 4   | PDL      | <ul> <li>Powerdown Line-Side Chip.</li> <li>0 = Normal operation. Program the clock generator before clearing this bit.</li> <li>1 = Powers down the Si3066.</li> </ul> |

| 3   | PDN      | <ul> <li>Powerdown DAA.</li> <li>0 = Normal operation.</li> <li>1 = Powers down the DAA logic. A DAA soft reset is required to restore normal operation.</li> </ul>     |

| 2:0 | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                         |

#### DAA Register 7. Sample Rate Control

| Bit  | D7 | D6 | D5 | D4 | D3       | D2 | D1 | D0 |  |  |

|------|----|----|----|----|----------|----|----|----|--|--|

| Name |    |    |    |    | SRC[3:0] |    |    |    |  |  |

| Туре |    |    |    |    | R/W      |    |    |    |  |  |

Reset settings = xxxx\_0001

| Bit | Name     | Function                                                                                                                                                                                                                                                        |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                                                 |

| 3:0 | SRC[3:0] | Sample Rate Control.<br>Sets the sampling rate.<br>0000 = 7200 Hz<br>0001 = 8000 Hz<br>0010 = 8229 Hz<br>0011 = 8400 Hz<br>0100 = 9000 Hz<br>0101 = 9600 Hz<br>0110 = 10286 Hz<br>0111 = 12000 Hz<br>1000 = 13714 Hz<br>1001 = 16000 Hz<br>1010-1111 = Reserved |

#### DAA Register 8. Reserved

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|----|----|----|----|----|----|----|----|

| Name |    |    |    |    |    |    |    |    |

| Туре |    |    |    |    |    |    |    |    |

| Bit | Name     | Function                                        |

|-----|----------|-------------------------------------------------|

| 7:0 | Reserved | Always write this bit to zero. Reads undefined. |

#### DAA Register 9. Reserved

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|----|----|----|----|----|----|----|----|

| Name |    |    |    |    |    |    |    |    |

| Туре |    | •  |    |    |    |    |    |    |

Reset settings = xxxx\_xxxx

| Bit | Name     | Function                                        |

|-----|----------|-------------------------------------------------|

| 7:0 | Reserved | Always write this bit to zero. Reads undefined. |

#### DAA Register 10. DAA Control 3

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

|------|----|----|----|----|----|----|----|-----|

| Name |    |    |    |    |    |    |    | DDL |

| Туре |    |    |    |    |    |    |    | R/W |

#### Reset settings = xxxx\_xx0

| Bit | Name     | Function                                                                                                                                                                        |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                 |

| 0   | DDL      | <ul> <li>Digital Data Loopback.</li> <li>0 = Normal Operation.</li> <li>1 = Loopback transmit to receive before the filters. Output data is identical to input data.</li> </ul> |

#### DAA Register 11. System-Side Revision

| Bit  | D7 | D6   | D5             | D4 | D3        | D2 | D1 | D0 |  |

|------|----|------|----------------|----|-----------|----|----|----|--|

| Name |    | LSIE | <b>D</b> [3:0] |    | REVA[3:0] |    |    |    |  |

| Туре |    | F    | ۲              |    |           | F  | २  |    |  |

| Bit | Name      | Function                                                                                   |

|-----|-----------|--------------------------------------------------------------------------------------------|

| 7:4 | LSID[3:0] | Line-Side ID.<br>1011 = Si3066                                                             |

| 3:0 | REVA[3:0] | System-Side Revision.<br>Four bit value indicating the revision of the system-side device. |

#### DAA Register 12. Line-Side Status

| Bit  | D7 | D6  | D5 | D4       | D3 | D2 | D1 | D0 |  |

|------|----|-----|----|----------|----|----|----|----|--|

| Name |    | FDT |    | LCS[4:0] |    |    |    |    |  |

| Туре |    | R   |    | R        |    |    |    |    |  |

Reset settings = xxxx\_xxxx

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                       |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved | Read returns zero.                                                                                                                                                                                                                                                                                                                                                             |

| 6   | FDT      | <ul> <li>Frame Detect.</li> <li>0 = Indicates isolation capacitor link has not established frame lock.</li> <li>1 = Indicates isolation capacitor link frame lock is established.</li> </ul>                                                                                                                                                                                   |

| 5   | Reserved | Always write this bit to zero. Reads undefined.                                                                                                                                                                                                                                                                                                                                |

| 4:0 | LCS[4:0] | Loop Current Sense.<br>Five-bit value returning the loop current in 3.3 mA/bit resolution when the DAA is in an off-<br>hook state.<br>00000–00011 = Indicates the loop current is less than required for normal operation.<br>00100 = Indicates minimum loop current for normal operation.<br>00101 = 11110 = Normal operation<br>11111 = Indicates loop current is > 160 mA. |

#### DAA Register 13. Line-Side Revision

| Bit  | D7 | D6 | D5        | D4 | D3 | D2 | D1 | D0 |  |

|------|----|----|-----------|----|----|----|----|----|--|

| Name |    |    | REVB[3:0] |    |    |    |    |    |  |

| Туре |    |    |           | F  | २  |    |    |    |  |

| Bit | Name      | Function                                                                                                                    |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Reserved  | Always write this bit to zero. Reads undefined.                                                                             |

| 5:2 | REVB[3:0] | Line-Side Revision.<br>Four-bit value indicating the revision of the Si3066 device.<br>1000 = Revision A; 1001 = Revision B |

| 1:0 | Reserved  | Always write this bit to zero. Reads undefined.                                                                             |

#### DAA Register 14. Reserved

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|----|----|----|----|----|----|----|----|

| Name |    |    |    |    |    |    |    |    |

| Туре |    |    |    |    |    |    |    |    |

Reset settings = xxxx\_xxxx

| Bit | Name     | Function                                        |

|-----|----------|-------------------------------------------------|

| 7:0 | Reserved | Always write this bit to zero. Reads undefined. |

#### DAA Register 15. TX/RX Gain Control

| Bit  | D7  | D6       | D5  | D4 | D3  | D2 | D1       | D0 |

|------|-----|----------|-----|----|-----|----|----------|----|

| Name | TXM | ATX[2:0] |     |    | RXM |    | ARX[2:0] |    |

| Туре | R/W |          | R/W |    |     |    | R/W      |    |

#### Reset settings = 0000\_0000

| Bit | Name     | Function                          |

|-----|----------|-----------------------------------|

| 7   | TXM      | Transmit Mute.                    |

|     |          | 0 = Transmit signal is not muted. |

|     |          | 1 = Mutes the transmit signal.    |

| 6:4 | ATX[2:0] | Analog Transmit Attenuation.      |

|     |          | 000 = 0 dB attenuation            |

|     |          | 001 = 3 dB attenuation            |

|     |          | 010 = 6 dB attenuation            |

|     |          | 011 = 9 dB attenuation            |

|     |          | 1xx = 12 dB attenuation           |

| 3   | RXM      | Receive Mute.                     |

|     |          | 0 = Receive signal is not muted.  |

|     |          | 1 = Mutes the receive signal.     |

| 2:0 | ARX[2:0] | Analog Receive Gain.              |

|     |          | 000 = 0 dB gain                   |

|     |          | 001 = 3 dB gain                   |

|     |          | 010 = 6 dB gain                   |

|     |          | 011 = 9 dB gain                   |

|     |          | 1xx = 12 dB gain                  |

#### DAA Register 16. Reserved

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|----|----|----|----|----|----|----|----|

| Name |    |    |    |    |    |    |    |    |

| Туре |    |    |    |    |    |    |    |    |

Reset settings = xxx1\_xxxx

| Bit | Name     | Function                                        |

|-----|----------|-------------------------------------------------|

| 7:0 | Reserved | Always write this bit to zero. Reads undefined. |

#### DAA Register 17. Calibration

| Bit  | D7 | D6 | D5   | D4 | D3 | D2 | D1 | D0 |

|------|----|----|------|----|----|----|----|----|

| Name |    |    | ADCC |    |    |    |    |    |

| Туре |    |    | R/W  |    |    |    |    |    |

| Bit | Name     | Function                                        |

|-----|----------|-------------------------------------------------|

| 7:6 | Reserved | Always write this bit to zero. Reads undefined. |

| 5   | ADCC     | ADC Calibration.<br>1 = Calibration disabled.   |

| 4:0 | Reserved | Always write this bit to zero. Reads undefined. |

#### DAA Register 18. International Control 3

| Bit  | D7 | D6 | D5 | D4 | D3 | D2 | D1   | D0 |

|------|----|----|----|----|----|----|------|----|

| Name |    |    |    |    |    |    | RFWE |    |

| Туре |    |    |    | •  |    |    | R/W  |    |

Reset Settings = xxxx\_xx0x

| Bit | Name     |                               |                                                                                                                                                                                                                                                                                                                                                                               | Function                |  |  |  |  |  |

|-----|----------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|--|

| 7:2 | Reserved | Always writ                   | Always write this bit to zero. Reads undefined.                                                                                                                                                                                                                                                                                                                               |                         |  |  |  |  |  |

| 1   | RFWE     | Ring Dete                     | ing Detector Full-Wave Rectifier Enable.                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |  |  |

|     |          | this bit con<br>tion circuit, | hen RNGV is disabled, this bit controls the ring detector mode. When RNGV is enabled,<br>s bit configures the RDT bit to either follow the ringing signal detected by the ring valida-<br>n circuit, or to follow an unqualified ring detect one-shot signal initiated by a ring-threshold<br>ossing and terminated by a fixed counter timeout of approximately five seconds. |                         |  |  |  |  |  |

|     |          | RNGV                          | RFWE                                                                                                                                                                                                                                                                                                                                                                          | RDT bit                 |  |  |  |  |  |

|     |          | 0                             | 0                                                                                                                                                                                                                                                                                                                                                                             | Half-Wave               |  |  |  |  |  |

|     |          | 0                             | 1                                                                                                                                                                                                                                                                                                                                                                             | Full-Wave               |  |  |  |  |  |

|     |          | 1                             | 0                                                                                                                                                                                                                                                                                                                                                                             | Validated Ring Envelope |  |  |  |  |  |

|     |          | 1                             | 1     1     Ring Threshold Crossing One-Shot                                                                                                                                                                                                                                                                                                                                  |                         |  |  |  |  |  |