#### **General Description**

The MAX4929E low-frequency 2:1 switch is ideal for HDMI™/DVI™ switching applications. The device features a voltage clamp function to protect low-voltage systems at the output. The MAX4929E operates with a single 5V supply or dual or triple supplies. The MAX4929E provides clamping and voltage translation without additional components. All external inputs/outputs are electrostatic-discharge (ESD)-protected to ±6kV Human Body Model (HBM).

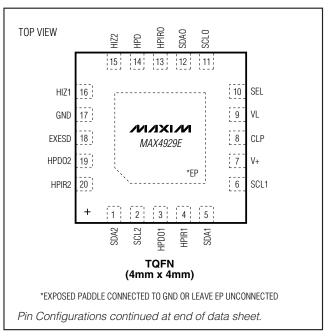

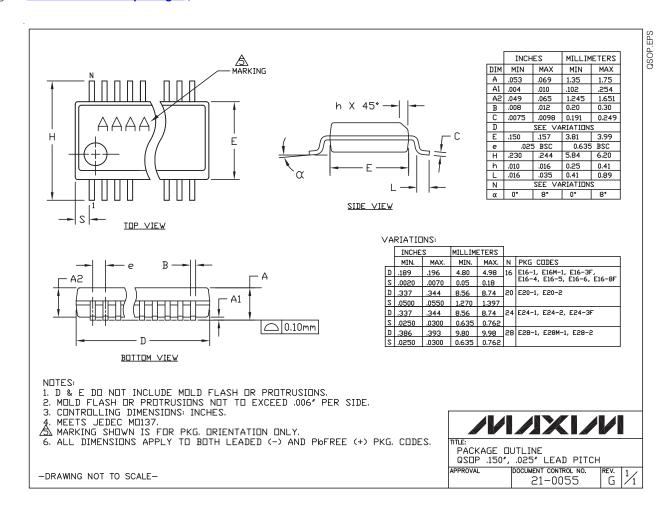

The MAX4929E is available in 20-pin QSOP and 20-pin, 4mm x 4mm, TQFN packages. The device is specified for the extended -40°C to +85°C operating temperature range.

#### **Applications**

**HD** Television Receivers

**HD Monitors**

High-Resolution Computer Monitors

HDMI is a trademark of HDMI Licensing, LLC. DVI is a trademark of Digital Display Working Group (DDWG).

# **Features**

- **♦ DDC Switches** Low 20pF (typ) Capacitance

- ♦ Protects EDID (Extended Display Identification Data) EPROM or MCU from Excess Voltage

- ♦ Hot-Plug Detect Signal **Translates MCU Voltage to TTL Levels**

- ♦ Two Devices Can Be Used to Form a 4:1 Switch No Added Active Components Needed

- ♦ ±6kV ESD Protection HBM on All External I/Os

- ♦ Available in Lead-Free, 20-Pin TQFN or 20-Pin QSOP **Packages**

#### **Ordering Information**

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |  |

|--------------|----------------|-----------------|-------------|--|

| MAX4929EEEP+ | -40°C to +85°C | 20 QSOP         | E20-1       |  |

| MAX4929EETP+ | -40°C to +85°C | 20 TQFN-EP*     | T2044-3     |  |

<sup>+</sup>Denotes a lead-free package

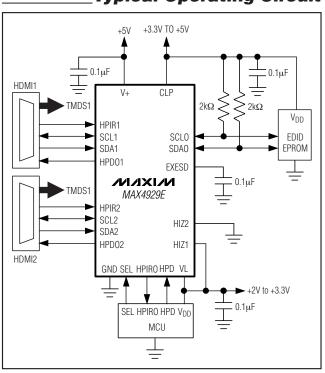

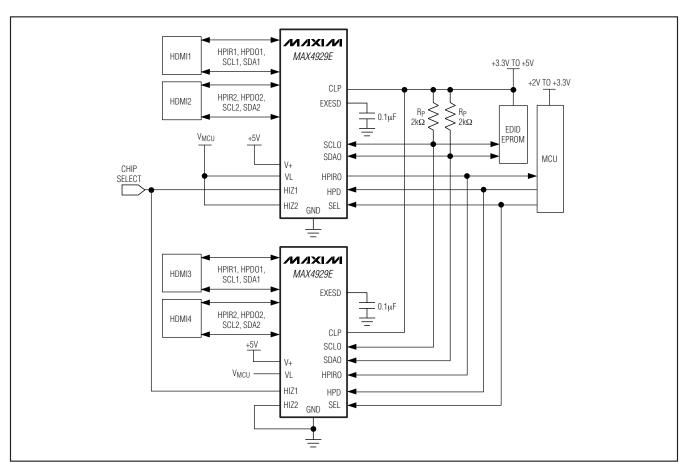

### **Typical Operating Circuit**

### Pin Configurations

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

<sup>\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unless otherwise     | noted.)     |

|-------------------------------------------------------|-------------|

| V+                                                    | 0.3V to +6V |

| All Pins (except GND)                                 | 0.3V to +6V |

| Continuous Current into Any I/O Terminal              | 25mA        |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |             |

| 20-Pin QSOP (derate 9.1mW/°C above +70°C).            | 727mW       |

| 20-Pin TQFN (derate 16.9mW/°C above +70°C)            | 1356mW      |

| Operating Temperature Range  | 40°C to +85°C  |

|------------------------------|----------------|

| Storage Temperature Range    | 65°C to +150°C |

|                              | +150°C         |

| Lead Temperature (soldering, | 10s)+300°C     |

|                              |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V+ = +5V \pm 10\%, CLP = VL = +3.3V \pm 10\%, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                            | SYMBOL                                             | CONDITIONS                                                                                                          | MIN | TYP  | MAX | UNITS |

|--------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| POWER SUPPLY                         | •                                                  |                                                                                                                     |     |      |     | •     |

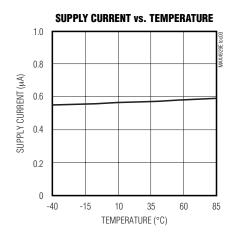

| V+ Supply Current                    | l+                                                 | V+ = 5.5V, VL = CLP = 3.6V                                                                                          |     | 3    | 8   | μΑ    |

| V+ Supply Current                    | I+                                                 | V+ = 0V, VL = CLP = 0V, V <sub>HPIR</sub> = +5.5V                                                                   |     |      | 200 | μΑ    |

| VL Supply Current                    | I <sub>V</sub> L                                   | V+ = 5.5V, $VL = CLP = 3.6V$                                                                                        |     |      | 1   | μΑ    |

| CLP Supply Current                   | ICLP                                               | V+ = 5.5V, $VL = CLP = 3.6V$                                                                                        |     |      | 1   | μΑ    |

| ANALOG SWITCH                        |                                                    |                                                                                                                     |     |      |     |       |

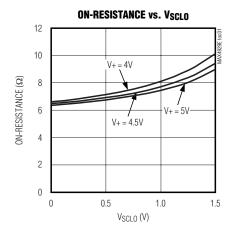

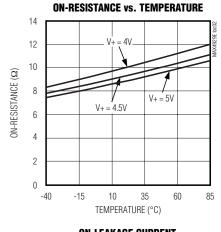

| On-Resistance                        | RON(SCL_),<br>RON(SDA_)                            | V+ = 4.5V, CLP = 3V, V <sub>SCL</sub> or V <sub>SDA</sub> = 0 to 1.5V; I <sub>SCL</sub> or I <sub>SDA</sub> = ±10mA |     | 10   | 25  | Ω     |

| On-Resistance Match Between Channels | ΔR <sub>ON</sub>                                   | $V+=4.5V$ , $CLP=3V$ , $V_{SCL}$ or $V_{SDA}=0$ to 1.5V; $I_{SCL}$ or $I_{SDA}=\pm 10$ mA                           |     | 2    | 8   | Ω     |

| On-Resistance Flatness               | R <sub>FLAT</sub>                                  | $V+=4.5V$ , $CLP=3V$ , $V_{SCL}$ or $V_{SDA}=0$ to 1.5V; $I_{SCL}$ or $I_{SDA}=\pm 10$ mA                           |     |      | 13  | Ω     |

| Off-Leakage Current                  | ISCL_(OFF),<br>ISDA_(OFF)                          | V+ = 5.5V, V <sub>SCL</sub> or V <sub>SDA</sub> = 0V, 5.5V;<br>HIZ1 = HIZ2 = 0V or VL (Note 1)                      | -5  |      | +5  | μΑ    |

| On-Leakage Current                   | I <sub>SCL_(ON)</sub> ,<br>I <sub>SDA_(ON)</sub>   | V+ = 5.5V, V <sub>SCL</sub> or V <sub>SDA</sub> = 0V, 5.5V<br>(Note 1)                                              | -5  |      | +5  | μΑ    |

| Output Clamped Voltage               | Vovc(sclo),<br>Vovc(sdao)                          | $V+ = 5V$ , CLP = 3.3V, VL = 5V, R <sub>P</sub> = 1k $\Omega$ (Note 2)                                              |     | 3.3  |     | V     |

| SWITCH DYNAMIC CHARACTE              | RISTICS                                            |                                                                                                                     |     |      |     |       |

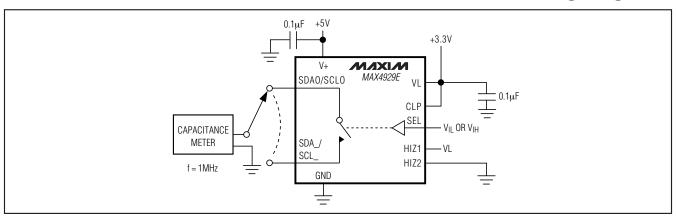

| SCL_, SDA_ Off-Capacitance           | C <sub>SCL_(OFF)</sub> ,<br>C <sub>SDA_(OFF)</sub> | V+ = 5V, T <sub>A</sub> = +25°C, Figure 1                                                                           |     | 20   |     | рF    |

| SCL_, SDA_ On-Capacitance            | C <sub>SCL_(ON)</sub> ,<br>C <sub>SDA_(ON)</sub>   | V+ = 5V, T <sub>A</sub> = +25°C, Figure 1                                                                           |     | 30   |     | рF    |

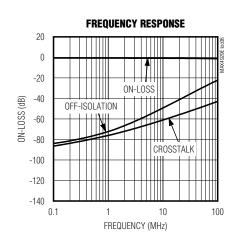

| Bandwidth                            | BW                                                 | $R_S = R_L = 50\Omega$ , $C_L = 10pF$                                                                               |     | 40   |     | MHz   |

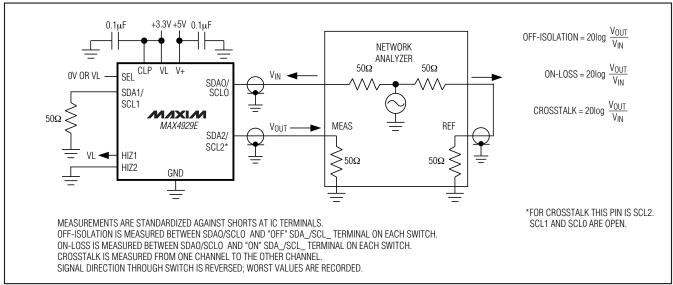

| Crosstalk                            | V <sub>CT</sub>                                    | $R_S = R_L = 50\Omega$ , $f = 1MHz$ , Figure 2 (Note 3)                                                             |     | -75  |     | dB    |

| Off-Isolation                        | V <sub>ISO</sub>                                   | $R_S = R_L = 50\Omega$ , $f = 1MHz$ , Figure 2 (Note 4)                                                             |     | -70  |     | dB    |

| LOGIC INPUT (HPIR1, HPIR2)           |                                                    |                                                                                                                     |     |      |     |       |

| Input Logic-Low Voltage              | V <sub>IL</sub>                                    | V+ = 4.5V                                                                                                           |     |      | 0.8 | V     |

| Input Logic-High Voltage             | VIH                                                | V+ = 5.5V                                                                                                           | 3.8 |      |     | V     |

| Input Logic Leakage                  | I <sub>INL</sub>                                   |                                                                                                                     |     | 0.01 | 1   | μΑ    |

2 \_\_\_\_\_\_*MAXIM*

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = +5V \pm 10\%, CLP = VL = +3.3V \pm 10\%, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                       | SYMBOL            | CONDITIONS                                                                      | MIN | TYP  | MAX | UNITS |

|---------------------------------|-------------------|---------------------------------------------------------------------------------|-----|------|-----|-------|

| LOGIC INPUT (SEL, HPD, HIZ1,    | HIZ2)             |                                                                                 | •   |      |     |       |

| Input Logic-Low Voltage         | V <sub>IL</sub>   | V+ = 4.5V, $VL = CLP = 3V$                                                      |     |      | 0.8 | V     |

| Input Logic-High Voltage        | V <sub>IH</sub>   | V+ = 5.5V, $VL = CLP = 3.6V$                                                    | 2.0 |      |     | V     |

| Hysteresis                      | V <sub>HYST</sub> | $3V \le VL = CLP \le 3.6V$                                                      |     | 150  |     | mV    |

| Input Logic-Leakage Current     | linl              |                                                                                 |     | 0.01 | 1   | μΑ    |

| LOGIC OUTPUT (HPDO1, HPDO       | 2, HPIRO)         |                                                                                 |     |      |     |       |

| HPDO_Output Logic-Low Voltage   | Vol(HPDO_)        | $V+ = 4.5V$ , $VL = CLP = 3.0V$ , $I_{SINK} = 4mA$                              |     |      | 0.5 | V     |

| HPDO_Output Logic-High Voltage  | VOH(HPDO_)        | V+ = 4.5V, VL = CLP = 3.0V, ISOURCE = 4mA                                       | 4.0 |      |     | V     |

| HPIRO Output Logic-Low Voltage  | Vol(HPIRO)        | $V+ = 4.5V$ , $VL = CLP = 3.0V$ , $I_{SINK} = 2mA$                              |     |      | 0.5 | V     |

| HPIRO Output Logic-High Voltage | Voh(HPIRO)        | V+ = 4.5V, VL = CLP = 3.0V, ISOURCE = 2mA                                       | 2.5 |      |     | V     |

| Output-Logic Leakage Current    | lo                | HIZ1 = HIZ2 = 0V or VL                                                          |     |      | 1   | μΑ    |

| TIMING CHARACTERISTICS          |                   |                                                                                 |     |      |     |       |

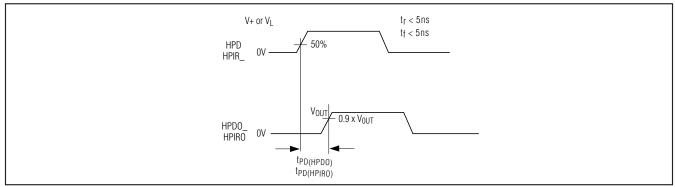

|                                 | tPD(HPDO_)        | $V+ = 4.5V$ , $VL = CLP = 3.0V$ , $C_L = 15pF$ , $SEL = 0V$ or $VL$ (Figure 3)  |     | 33   |     | ns    |

| Logic Delay                     | tPD(HPIRO)        | V+ = 4.5V, VL = CLP = 3.0V, C <sub>L</sub> = 15pF,<br>SEL = 0V or VL (Figure 3) |     |      | 33  |       |

| ESD PROTECTION                  |                   |                                                                                 |     |      |     |       |

| ESD Protection, Human Body      |                   | HPIR1, HPIR2, HPDO1, HPDO2, SCL1,<br>SCL2, SDA1, SDA2 (Note 5)                  |     | ±6   |     | 14)/  |

| Model                           |                   | HPIRO, HPD, SEL, SCLO, SDAO, HIZ1,<br>HIZ2 (Note 6)                             |     | ±2   |     | kV    |

| EXESD Leakage Current           |                   |                                                                                 |     | 1.0  |     | μΑ    |

Note 1: Leakage measured at SCLO or SDAO with SCL\_ and SDA\_ open.

**Note 2:** Pullup resistor of RP =  $1k\Omega$  at SCLO and SDAO. These resistors are necessary for the clamp/translation to operate correctly.

Note 3: Crosstalk is measured between any two analog inputs, crosstalk = 20log(V<sub>OUT</sub> / V<sub>IN</sub>).

**Note 4:** Off-isolation = 20log10 (V<sub>SCLO</sub> / V<sub>SCL</sub>), V<sub>SCLO</sub> = output, V<sub>SCL</sub> = input to off switch.

Note 5: Referenced to GND.

Note 6: Any combination of pin to any other pin.

#### **Test Circuits/Timing Diagrams**

Figure 1. Channel Off-/On-Capacitance

Figure 2. On-Loss, Off-Isolation, and Crosstalk

Figure 3. Logic Delay Timing

4 \_\_\_\_\_\_*NIXIN*

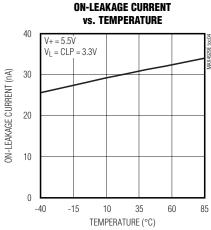

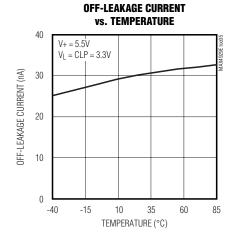

### Typical Operating Characteristics

(V+ = 5V, VL = 3.3V, CLP = 3.3V,  $T_A$  = +25°C, unless otherwise noted.)

### Pin Description

| PIN NAME |      |       | FUNCTION                                                                                                                                                                                   |

|----------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QSOP     | TQFN | NAME  | FUNCTION                                                                                                                                                                                   |

| 1        | 19   | HPDO2 | Hot-Plug Detect Output 2. Translate logic level of HPD to V+ compatible (see Table 2).                                                                                                     |

| 2        | 20   | HPIR2 | Hot-Plug Interrupt Request 2                                                                                                                                                               |

| 3        | 1    | SDA2  | Serial Data Input. SDA Mux Input 2.                                                                                                                                                        |

| 4        | 2    | SCL2  | Serial Clock Input. SCL Mux Input 2.                                                                                                                                                       |

| 5        | 3    | HPDO1 | Hot-Plug Detect Output 1. Translate logic level of HPD to V+ compatible (see Table 2).                                                                                                     |

| 6        | 4    | HPIR1 | Hot-Plug Interrupt Request 1                                                                                                                                                               |

| 7        | 5    | SDA1  | Serial Data Input. SDA Mux Input 1.                                                                                                                                                        |

| 8        | 6    | SCL1  | Serial Clock Input. SCL Mux Input 1.                                                                                                                                                       |

| 9        | 7    | V+    | Positive Supply Voltage. Bypass V+ to GND with a 0.1µF or greater ceramic capacitor.                                                                                                       |

| 10       | 8    | CLP   | Clamp-Voltage Reference. Clamp the maximum voltage of SCLO and SDAO. Bypass CLP to GND with a 0.1µF or greater ceramic capacitor (see Figure 6 and the <i>Typical Operating Circuit</i> ). |

| 11       | 9    | VL    | Logic Supply for HIZ_, SEL, HPD, HPIRO. Bypass VL to GND with a 0.1µF or greater ceramic capacitor. VL should have the same voltage level as any MCU interface.                            |

| 12       | 10   | SEL   | Select Input. Logic input for Mux connection (see Table 1).                                                                                                                                |

| 13       | 11   | SCLO  | SCL Mux Output. Connect SCLO to EDID EPROM.                                                                                                                                                |

| 14       | 12   | SDAO  | SDA Mux Output. Connect SDAO to EDID EPROM.                                                                                                                                                |

| 15       | 13   | HPIRO | Hot-Plug Interrupt Request Output. Translate logic level of HPIR_ to VL compatible (see Table 3).                                                                                          |

| 16       | 14   | HPD   | Hot-Plug Detect Input. Logic level on HPD is compatible with MCU.                                                                                                                          |

| 17       | 15   | HIZ2  | Enable Input 2 (see Table 4).                                                                                                                                                              |

| 18       | 16   | HIZ1  | Enable Input 1 (see Table 4).                                                                                                                                                              |

| 19       | 17   | GND   | Ground                                                                                                                                                                                     |

| 20       | 18   | EXESD | External ESD Discharge. Connect 0.1µF capacitor from EXESD to GND.                                                                                                                         |

| _        | EP   | EP    | Exposed Paddle. Connect EP to GND or leave EP unconnected.                                                                                                                                 |

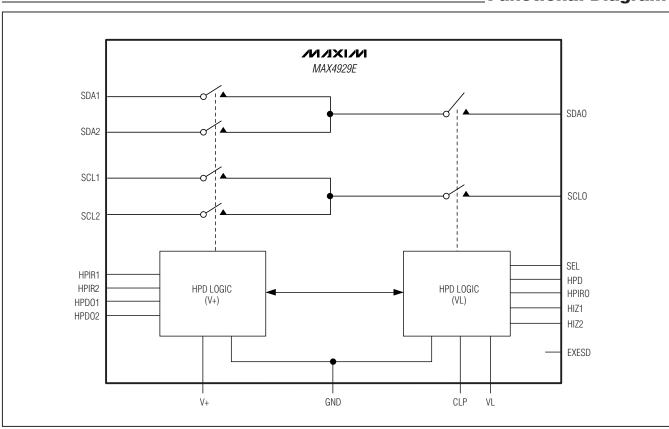

#### **Functional Diagram**

### **Detailed Description**

The MAX4929E low-frequency 2:1 switch is ideal for the low-frequency portion of HDMI/DVI switching applications. The device features three independent voltage inputs that allow the user to match any voltage level encountered in switching without additional components. The V+ range is from 4.5V to 5.5V to match the HDMI/DVI 5V requirements. CLP is set to match the EDID EPROM from 3.3V to 5.5V. VL is connected to the same supply as the system MCU. All pins going to the HDMI/DVI connectors are ESD-protected to ±6kV Human Body Model (HBM).

The MAX4929E has two enable inputs. The enable function allows the device to operate in normal mode or go into a high-Z state. It is possible to control two MAX4929Es with a single control bit, creating a 4:1 equivalent switch using a minimum of external components (see Figure 6).

Supply or signals sequencing are not required for the MAX4929E. Supply voltages V+, VL, and CLP can be

applied in any order. Signals can be applied in any order as well.

#### **Analog Switch**

The MAX4929E features a voltage clamp function for the two 2:1 switch. Inputs to SCL\_/SDA\_ are V+ level compatible. Maximum output voltages of SCLO/SDAO are clamped to CLP. For optimum performance connect the EDID EPROM supply voltage to CLP (see Figure 6). For proper operation of the voltage clamp, connect SCLO/SDAO to CLP through the pullup resistors. For maximum output range, connect CLP to V+. The output of the switch is connected to the EDID EPROM, voltages from 3V to 5.5V are expected.

#### **Logic Inputs**

VL is the supply to input logic HIZ\_, SEL, and HPD. Connect VL to the same supply as the system MCU for compatibility.

V+ is the supply to the input logic of the HPIR1 and HPIR2 inputs.

# Table 1. Inputs Selection for 2:1 Mux Truth Table

|     | INPUTS |      | SWITCH CONNECTIONS         |  |  |  |  |

|-----|--------|------|----------------------------|--|--|--|--|

| SEL | HIZ1   | HIZ2 | SWITCH CONNECTIONS         |  |  |  |  |

| 0   | 0      | 1    | SDAO to SDA1, SCLO to SCL1 |  |  |  |  |

| 0   | 1      | 0    | SDAO to SDA1, SCLO to SCL1 |  |  |  |  |

| 1   | 0      | 1    | SDAO to SDA2, SCLO to SCL2 |  |  |  |  |

| 1   | 1      | 0    | SDAO to SDA2, SCLO to SCL2 |  |  |  |  |

| Х   | 0      | 0    | High Impedance             |  |  |  |  |

| Х   | 1      | 1    | High Impedance             |  |  |  |  |

#### **Table 2. HPD Output Channel Selection**

|     | INP | UTS    | OUTPUTS |                   |                   |  |  |

|-----|-----|--------|---------|-------------------|-------------------|--|--|

| SEL | HPD | HIZ1   | HIZ2    | HPDO1             | HPDO2             |  |  |

| X   | 0   | 0<br>1 | 1 0     | 0                 | 0                 |  |  |

| 0   | 1   | 0      | 1<br>0  | 1                 | 0                 |  |  |

| 1   | 1   | 0      | 1<br>0  | 0                 | 1                 |  |  |

| Х   | Х   | 1      | 1       | High<br>Impedance | High<br>Impedance |  |  |

| Х   | Х   | 0      | 0       | High<br>Impedance | High<br>Impedance |  |  |

#### **Table 3. HPIRO Output Channel Selection**

|     |       | INPUTS |        |        | OUTPUT            |

|-----|-------|--------|--------|--------|-------------------|

| SEL | HPIR1 | HPIR2  | HIZ1   | HIZ2   | HPIRO             |

| X   | 0     | 0      | 0<br>1 | 1<br>0 | 0                 |

| X   | 1     | 1      | 0<br>1 | 1<br>0 | 1                 |

| 0   | 0     | X      | 0<br>1 | 1<br>0 | 0                 |

| 0   | 1     | Х      | 0<br>1 | 1<br>0 | 1                 |

| 1   | X     | 0      | 0<br>1 | 1<br>0 | 0                 |

| 1   | Х     | 1      | 0<br>1 | 1<br>0 | 1                 |

| Χ   | X     | Х      | 0      | 0      | High<br>Impedance |

| X   | X     | Х      | 1      | 1      | High<br>Impedance |

#### **Table 4. Mode of Operation**

| INP  | UTS  | OUTPUTS                                                                    |

|------|------|----------------------------------------------------------------------------|

| HIZ1 | HIZ2 | MODE OF OPERATION                                                          |

| 0    | 0    | High Impedance: SDAO, SDA1, SDA2,<br>SCLO, SCL1, SCL2, HPDO1, HPDO2, HPIRO |

| 0    | 1    | Normal Operation                                                           |

| 1    | 0    | Normal Operation                                                           |

| 1    | 1    | High Impedance: SDAO, SDA1, SDA2, SCLO, SCL1, SCL2, HPDO1, HPDO2, HPIRO    |

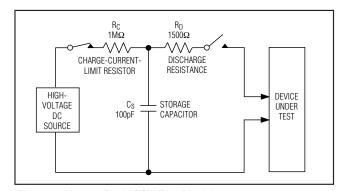

Figure 4. Human Body ESD Test Model

#### **Logic Outputs**

The HPDO\_ signals are 5V TTL-compatible, per HDMI/ DVI specifications. HPIRO is VL compatible.

#### **ESD Protection**

As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against ESD encountered during handling and assembly. Additionally, the MAX4929E is protected to  $\pm 6kV$  (HBM) on SCL1, SCL2, SDA1, SDA2, HPDO1, HPDO2, HPIR1, and HPIR2 by the HBM.

#### Human Body Model

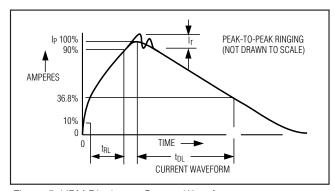

Several ESD testing standards exist for measuring the robustness against ESD events. The ESD protection of the MAX4929E is characterized with the HBM method. Figure 4 shows the model used to simulate an ESD event resulting from contact with the human body. The model consists of a 100pF storage capacitor that is charged to a high voltage, then discharged through a 1.5k $\Omega$  resistor. Figure 5 shows the current waveform when the storage capacitor is discharged into a lower impedance.

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report documenting test setup, methodology, and results.

Figure 5. HBM Discharge Current Waveform

### **Applications Information**

#### **Power-Supply Bypassing and Sequencing**

There is no power-supply sequencing required. Power can be applied to V+, CLP, or VL in any order. Bypass

V+, VL, and CLP to GND using  $0.1\mu F$  or larger ceramic capacitors as close to the device as possible.

#### **Hot Plug**

The MAX4929E is designed for HDMI/DVI switching. The MAX4929E permits hot-plugging to any inputs/outputs regardless of the power status of the device. A plug can be inserted, and thus connected to the MAX4929E whether the device is powered up or not. Therefore, sequencing of power supplies is not required; V+, CLP, and VL can be applied in any order.

# **Configure Two Devices to Form 4:1 Switch** Two MAX4929Es can be connected together to form a 4:1 switch (see Figure 6).

#### **Exposed Paddle**

The MAX4929EETP+ provides an EP to improve thermal performance in the TQFN package. Connect the EP to GND or leave EP unconnected.

Figure 6. Two MAX4929Es Connected to Form a 4:1 Translating Switch

/N/IXI/N \_\_\_\_\_

#### Pin Configurations (continued) TOP VIEW 20 EXESD HPIR2 2 19 GND SDA2 3 18 HIZ1 MIXIM SCL2 4 MAX4929E 17 HIZ2 HPD01 5 16 HPD HPIR1 6 15 HPIRO SDA1 7 14 SDA0 SCL1 8 13 SCLO 12 SEL V+ 9 11 VL CLP 10 QSOP

\_\_\_\_\_Chip Information

PROCESS: BICMOS

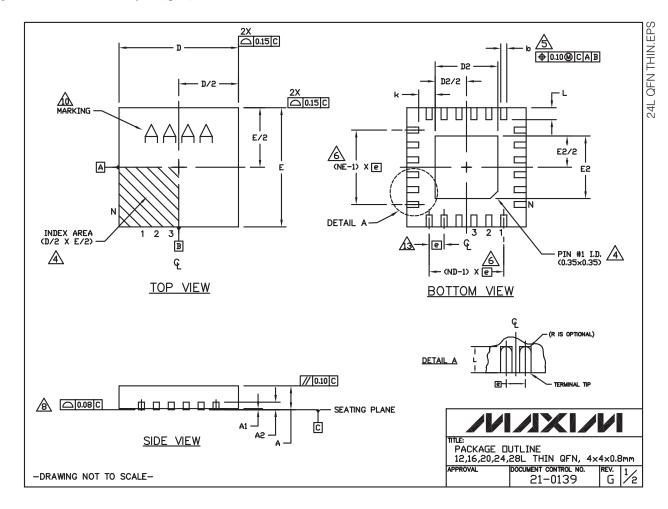

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

|               | COMMON DIMENSIONS |         |      |      |        |      |           |       |           |        |           |          |         |      |      |

|---------------|-------------------|---------|------|------|--------|------|-----------|-------|-----------|--------|-----------|----------|---------|------|------|

| PKG           | 12                | ⊇L 4×   | 4    | 16   | L 4×   | 4    | 20        | L 4×  | 4         | 24     | 4L 4×     | 4        | 28L 4×4 |      |      |

| REF.          | MIN.              | NDM.    | MAX. | MIN. | NDM.   | MAX. | MIN.      | NOM.  | MAX.      | MIN.   | NDM.      | MAX.     | MIN.    | NDM. | MAX. |

| Α             | 0.70              | 0.75    | 0.80 | 0.70 | 0.75   | 0.80 | 0.70      | 0.75  | 0.80      | 0.70   | 0.75      | 0.80     | 0.70    | 0.75 | 0.80 |

| A1            | 0.0               | 0.02    | 0.05 | 0.0  | 0.02   | 0.05 | 0.0       | 0.02  | 0.05      | 0.0    | 0.02      | 0.05     | 0.0     | 0.02 | 0.05 |

| A2            | 0                 | .20 RE  | F    | 0    | .20 RE | F    | 0.20 REF  |       | 0         | 20 RE  | F         | 0.20 REF |         |      |      |

| b             | 0.25              | 0.30    | 0.35 | 0.25 | 0.30   | 0.35 | 0.20      | 0.25  | 0.30      | 0.18   | 0.23      | 0.30     | 0.15    | 0.20 | 0.25 |

| D             | 3.90              | 4.00    | 4.10 | 3.90 | 4.00   | 4.10 | 3.90      | 4.00  | 4.10      | 3.90   | 4.00      | 4.10     | 3.90    | 4.00 | 4.10 |

| E             | 3.90              | 4.00    | 4.10 | 3.90 | 4.00   | 4.10 | 3.90      | 4.00  | 4.10      | 3.90   | 4.00      | 4.10     | 3.90    | 4.00 | 4.10 |

| е             | (                 | 0.80 BS | C.   | 0    | .65 BS | C.   | 0.50 BSC. |       | 0.50 BSC. |        | 0.40 BSC. |          |         |      |      |

| k             | 0.25              | -       | -    | 0.25 | -      | -    | 0.25      | -     | -         | 0.25   | -         | -        | 0.25    | -    | 1    |

| L             | 0.45              | 0.55    | 0.65 | 0.45 | 0.55   | 0.65 | 0.45      | 0.55  | 0.65      | 0.30   | 0.40      | 0.50     | 0.30    | 0.40 | 0.50 |

| N             |                   | 12      |      |      | 16     |      | 20        |       | 24        |        |           | 28       |         |      |      |

| ND            |                   | 3       |      |      | 4      |      |           | 5     |           |        | 6         |          |         | 7    |      |

| NE            |                   | 3       |      |      | 4      |      | 5         |       | 6         |        | 7         |          |         |      |      |

| Jedec<br>Var. |                   | WGGB    |      |      | WGGC   |      | ,         | wGGD- | ı         | VGGD-2 |           |          | VGGE    |      |      |

| EXPOSED PAD VARIATIONS |      |      |      |      |      |      |  |  |  |  |

|------------------------|------|------|------|------|------|------|--|--|--|--|

| PKG.                   |      | D2   |      |      | E2   |      |  |  |  |  |

| CODES                  | MIN. | NDM. | MAX. | MIN. | NDM. | MAX. |  |  |  |  |

| T1244-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T1244-4                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T1644-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T1644-4                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T2044-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T2044-3                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T2444-2                | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |

| T2444-3                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |

| T2444-4                | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |

| T2844-1                | 2.50 | 2.60 | 2.70 | 2.50 | 2.60 | 2.70 |  |  |  |  |

#### NOTES

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25mm AND 0.30mm FROM TERMINAL TIP.

ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

- 9. DRAWING CONFORMS TO JEDEC MD220, EXCEPT FOR T2444

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. COPLANARITY SHALL NOT EXCEED 0.08mm.

- 12. WARPAGE SHALL NOT EXCEED 0.00mm.

12. WARPAGE SHALL NOT EXCEED 0.10mm.

13. LEAD CENTERINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION 'e', ±0.05.

- 14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 15. ALL DIMENSIONS ARE THE SAME FOR LEADED (-) & PIOFREE (+) PACKAGE CODES.

PACKAGE DUTLINE 12,16,20,24,28L THIN QFN, 4×4×0.8mm ŒV. 21-0139

-DRAWING NOT TO SCALE-

#### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

\_ 13

© 2007 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.