### **General Description**

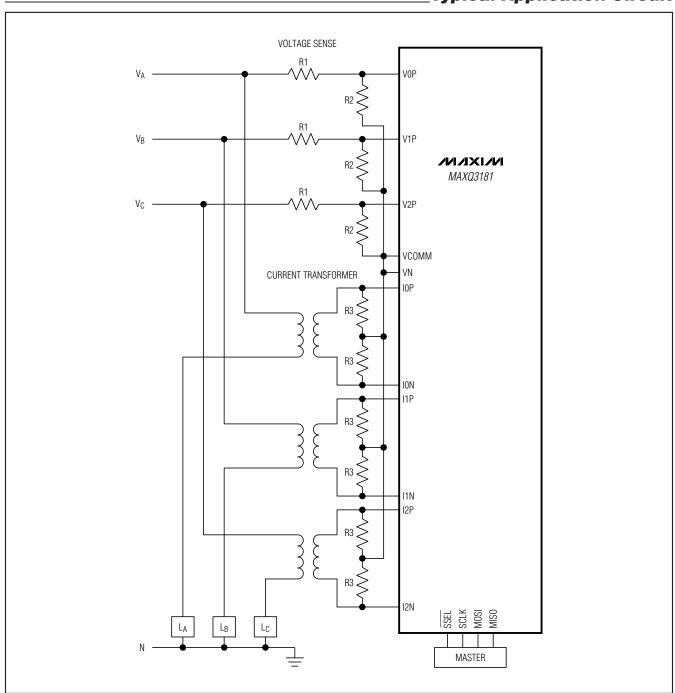

The MAXQ3181 is a dedicated electricity measurement front-end that collects and calculates polyphase voltage, current, active power and energy, and many other metering parameters of a polyphase load. The computed results can be retrieved by an external master through the on-chip serial peripheral interface (SPI™) bus. This bus is also used by the external master to configure the operation of the MAXQ3181 and monitor the status of operations.

The MAXQ3181 performs voltage and current measurements using an integrated ADC that can measure up to seven external differential signal pairs. An eighth differential signal pair is used to measure the die temperature. An internal amplifier automatically adjusts the current channel gain to compensate for low-current channel-signal levels.

### **Applications**

3-Phase Active Energy Electricity Meters

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAXQ3181-RAN+ | -40°C to +85°C | 28 TSSOP    |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Pin Configuration and Typical Application Circuit appear at end of data sheet.

#### **Features**

- ♦ Compatible with 3-Phase/3-Wire, 3-Phase/4-Wire, and Other 3-Phase Services

- ♦ 0.1% Active Power and Energy Linearity Error

- ♦ 0.5% Apparent Power and Energy Linearity Error

- ♦ 0.5% Linearity Errors for RMS Voltage and RMS Current

- Neutral Line Current Measurement

- **♦** Line Frequency (Hz)

- **♦ Power Factors**

- ♦ Phase Sequence Indication

- ♦ Phase Voltage Absence Detection

- ♦ Programmable Pulse Width

- ♦ Programmable No-Load Current Threshold

- **♦ Programmable Meter Constant**

- **♦** Programmable Thresholds for Undervoltage and Overvoltage Detection

- ♦ Programmable Threshold for Overcurrent Detection

- ♦ Amp-Hours in Absence of Voltage Signals

- ♦ On-Chip Digital Temperature Sensor

- ♦ Precision Internal Voltage Reference 2.048V (30ppm/°C typical), Also Supports An External Voltage Reference

- ◆ Active Power and Energy of Each Phase and Combined 3-Phase (kWh), Positive and Negative

- ♦ Apparent Power and Energy of Each Phase and **Combined 3-Phase**

- **♦** Supports Software Meter Calibration

- ♦ Up to 3-Point Multipoint Calibration to **Compensate for Transducer Nonlinearity**

- ♦ Power-Fail Detection

- ♦ Bidirectional Reset Input/Output

- ♦ SPI-Compatible Serial Interface with Interrupt Request (IRQ) Output

- ♦ Single 3.3V Supply, Low Power (35mW typical)

MAXQ is a registered trademark of Maxim Integrated Products, Inc. SPI is a trademark of Motorola. Inc.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: www.maxim-ic.com/errata.

Maxim Integrated Products 1

| TABLE OF CONTENTS                           |    |

|---------------------------------------------|----|

| Absolute Maximum Ratings                    | .8 |

| Metering Specifications                     | .8 |

| Electrical Characteristics                  | .8 |

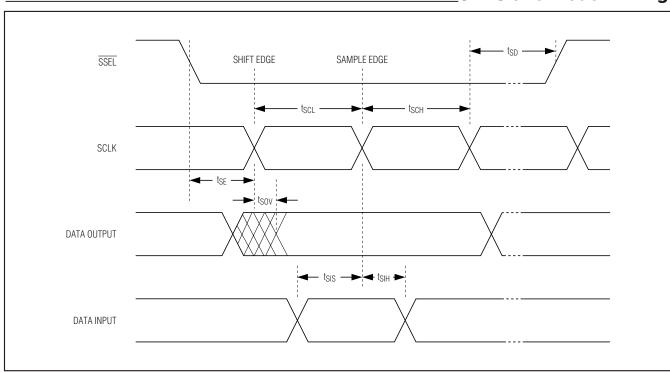

| SPI Slave Mode Timing                       | 0  |

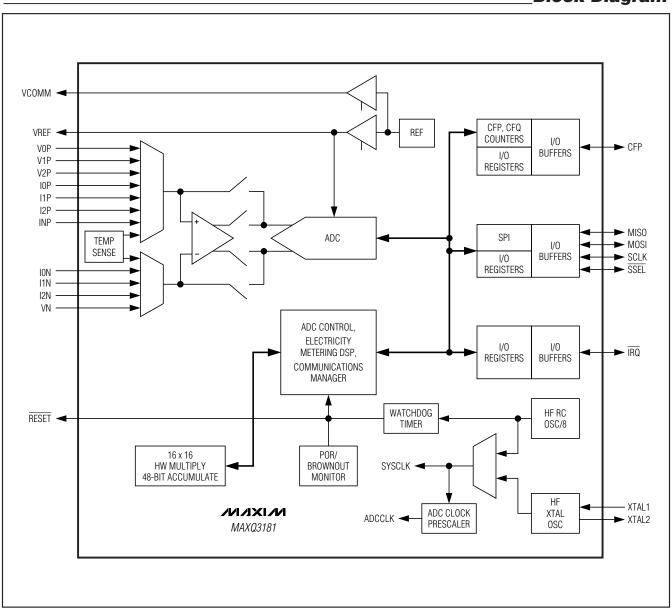

| Block Diagram                               | 1  |

| Pin Description                             | 2  |

| Detailed Description                        | 3  |

| Analog Front-End1                           | 3  |

| Digital Signal Processor                    | 3  |

| Precision Pulse Generators                  | 3  |

| SPI Peripheral                              | 3  |

| Operating Modes1                            | 3  |

| Run Mode                                    | 3  |

| Stop Mode1                                  | 3  |

| Reset Sources                               | 4  |

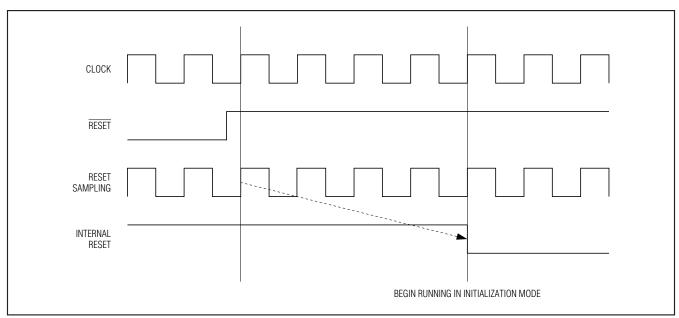

| External Reset                              | 4  |

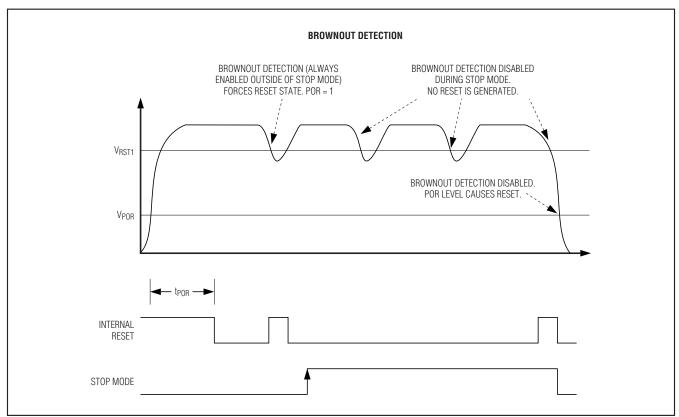

| Power-On Reset                              | 5  |

| Watchdog Reset                              | 5  |

| Software Reset                              | 5  |

| Power-Supply Monitoring                     | 6  |

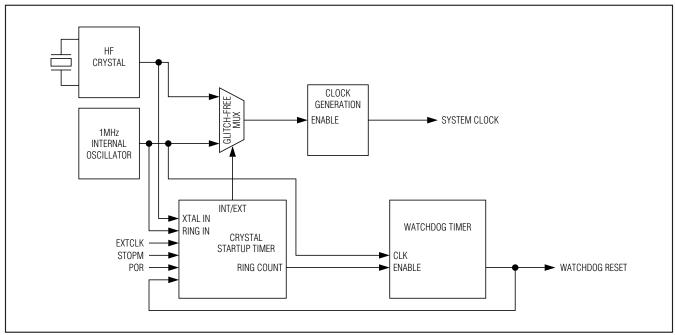

| Clock Sources                               | 6  |

| External High-Frequency Crystal             |    |

| External High-Frequency Clock               | 7  |

| Internal RC Oscillator1                     |    |

| Master Communications                       |    |

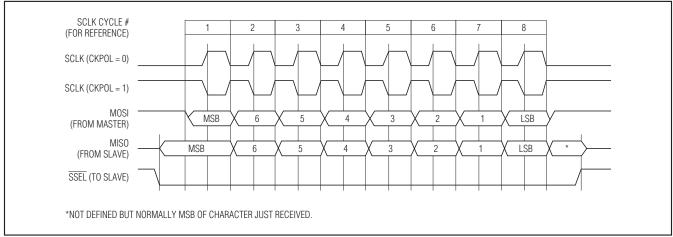

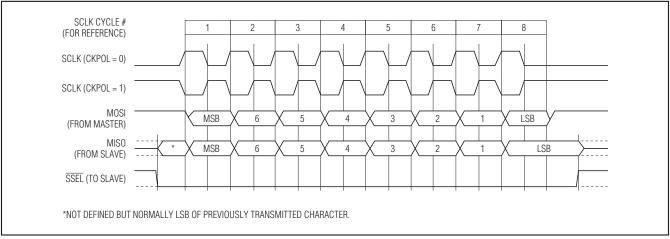

| SPI Communications Rate and Format1         |    |

| SPI Communications Protocol                 |    |

| Host Software Design                        |    |

| Register Set                                | 2  |

| RAM-Based Registers                         | 26 |

| General Operating Registers                 | 26 |

| Global Status Register (STATUS) (0x000)     |    |

| Operating Mode Register 0 (OPMODE0) (0x001) |    |

| Operating Mode Register 1 (OPMODE1) (0x002) |    |

| Operating Mode Register 2 (OPMODE2) (0x003) | 29 |

| TABLE OF CONTENTS (continued)                                                                  |    |

|------------------------------------------------------------------------------------------------|----|

| Global Interrupt Registers                                                                     | 31 |

| Interrupt Request Flag Register (IRQ_FLAG) (0x004)                                             | 31 |

| Interrupt Mask Register (IRQ_MASK) (0x006)                                                     | 32 |

| Meter Pulse Configuration                                                                      | 33 |

| Pulse Configuration—CFP Output (PLSCFG1) (0x01E)                                               | 33 |

| CFP Pulse Width (PLS1_WD) (0x020)                                                              | 33 |

| CFP Pulse Threshold (THR1) (0x022)                                                             | 34 |

| Calibration Registers                                                                          | 34 |

| Current Gain, Phase X = A/B/C/N (X.I_GAIN) (A: 0x130, B: 0x21C, C: 0x308, N: 0x12E)            | 34 |

| Voltage Gain, Phase X = A/B/C (X.V_GAIN) (A: 0x132, B: 0x21E, C: 0x30A)                        | 35 |

| Energy Gain, Phase X = A/B/C (X.E_GAIN) (A: 0x134, B: 0x220, C: 0x30C)                         | 35 |

| Phase-Angle Compensation, High Range, Phase X = A/B/C (X.PA0) (A: 0x13E, B: 0x22A, C: 0x316)   | 35 |

| Phase-Angle Compensation, Medium Range, Phase X = A/B/C (X.PA1) (A: 0x140, B: 0x22C, C: 0x318) | 36 |

| Phase-Angle Compensation, Low Range, Phase X = A/B/C (X.PA2) (A: 0x142, B: 0x22E, C: 0x31A)    | 36 |

| Limit Registers                                                                                | 36 |

| Overcurrent Level (OCLVL) (0x044)                                                              | 36 |

| Overvoltage Level (OVLVL) (0x046)                                                              | 37 |

| Undervoltage Level (UVLVL) (0x048)                                                             | 37 |

| No-Load Level (NOLOAD) (0x04A)                                                                 | 37 |

| Phase Status Registers                                                                         | 38 |

| Interrupt Flags, Phase X = A/B/C (X.FLAGS) (A: 0x144, B: 0x230, C: 0x31C)                      | 38 |

| Interrupt Mask, Phase $X = A/B/C$ (X.MASK) (A: 0x145, B: 0x231, C: 0x31D)                      | 39 |

| Energy Overflow Flags, Phase $X = A/B/C$ (X.EOVER) (A: 0x146, B: 0x232, C: 0x31E)              | 39 |

| Measurements                                                                                   | 40 |

| Line Frequency (LINEFR) (0x062)                                                                | 40 |

| Power Factor, Phase X = A/B/C (X.PF) (A: 0x1C6, B: 0x2B2, C: 0x39E)                            | 40 |

| RMS Voltage, Phase X = A/B/C (X.VRMS) (A: 0x1C8, B: 0x2B4, C: 0x3A0)                           | 40 |

| RMS Current, Phase X = A/B/C (X.IRMS) (A: 0x1CC, B: 0x2B8, C: 0x3A4)                           |    |

| Energy, Real Positive, Phase $X = A/B/C$ (X.EAPOS) (A: 0x1E8, B: 0x2D4, C: 0x3C0)              | 41 |

| Energy, Real Negative, Phase X = A/B/C (X.EANEG) (A: 0x1EC, B: 0x2D8, C: 0x3C4)                | 42 |

| Energy, Apparent, Phase $X = A/B/C$ (X.ES) (A: 0x1F8, B: 0x2E4, C: 0x3D0)                      |    |

| Virtual Register Conversion Coefficients                                                       |    |

| Voltage Units Conversion Coefficient (VOLT_CC) (0x014)                                         |    |

| Current Units Conversion Coefficient (AMP_CC) (0x016)                                          |    |

| Power Units Conversion Coefficient (PWR_CC) (0x018)                                            |    |

| Energy Units Conversion Coefficient (ENR_CC) (0x01A)                                           | 45 |

|                                                                                                |    |

| TABLE OF CONTENTS (continued)                                                       |      |

|-------------------------------------------------------------------------------------|------|

| Virtual Registers                                                                   | 46   |

| Power                                                                               | 46   |

| Real Power, Phase X = A/B/C/T (PWRP.X) (A: 0x801, B: 0x802, C: 0x804, T: 0x807)     | 46   |

| Apparent Power, Phase X = A/B/C/T (PWRS.X) (A: 0x821, B: 0x822, C: 0x824, T: 0x827) | 46   |

| Voltage and Current                                                                 | 47   |

| RMS Volts, Phase X = A/B/C (V.X) (A: 0x831, B: 0x832, C: 0x834)                     | 47   |

| RMS Amps, Phase X = A/B/C/N (I.X) (A: 0x841, B: 0x842, C: 0x844, N: 0x840)          | 47   |

| Power Factor                                                                        | 47   |

| Power Factor (PF.T) (0x867)                                                         | 47   |

| Energy                                                                              | 48   |

| Real Energy, Phase A/B/C/T (ENRP.X) (A: 0x8C1, B: 0x8C2, C: 0x8C4, T: 0x8C7)        | 48   |

| Apparent Energy, Phase A/B/C/T (ENRS.X) (A: 0x871, B: 0x872, C: 0x874, T: 0x877)    | 48   |

| Theory of Operation                                                                 | 49   |

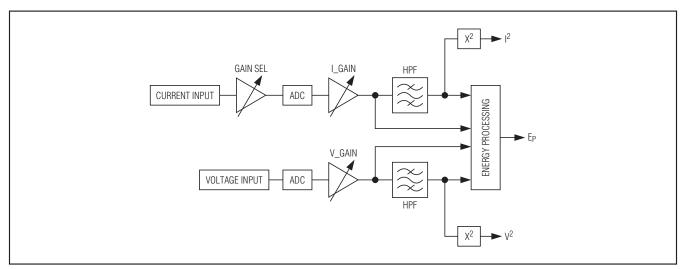

| Analog Front-End Operation                                                          | 49   |

| Digital Signal Processing (DSP) Terminology                                         | 49   |

| Digital Processing                                                                  | 49   |

| Per Sample Operations                                                               | 50   |

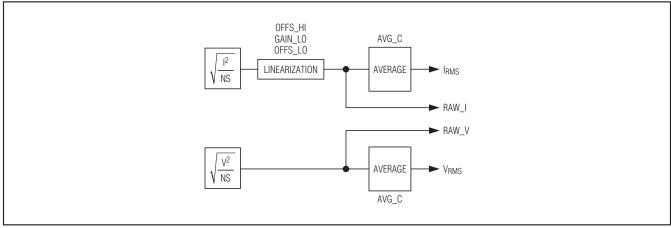

| Per DSP Cycle Operations                                                            | 50   |

| Energy Accumulation                                                                 | 52   |

| No-Zero-Crossing Detection                                                          | 52   |

| Phase Sequence Status                                                               | 52   |

| Power Calculation (Active and Apparent)                                             | 53   |

| Energy Accumulation Start Delay                                                     | 53   |

| No-Load Feature                                                                     | 53   |

| On Demand Calculations                                                              | 53   |

| RMS Volts, RMS Amps                                                                 | 53   |

| Power                                                                               | 54   |

| Power Factor                                                                        | 54   |

| Line Frequency                                                                      | 54   |

| Energy                                                                              | 54   |

| Meter Pulse                                                                         |      |

| Generating Pulses                                                                   |      |

| Meter Constant                                                                      | 55   |

| Interrupts                                                                          | 55   |

| Overvoltage and Overcurrent Detection                                               | 56   |

| Meter Units to Real Units Conversion                                                | 56   |

| Units Conversion Examples                                                           | 58   |

| 4 M/X                                                                               | (I/M |

| TABLE OF CONTENTS (continued)                                                           |    |

|-----------------------------------------------------------------------------------------|----|

| Calibration Procedure                                                                   | 58 |

| Calibration Overview                                                                    | 58 |

| Calibrating Voltage                                                                     | 59 |

| Calibrating Current                                                                     | 59 |

| Calibrating Phase Offset                                                                | 60 |

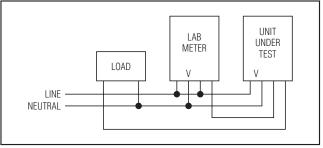

| Interfacing the MAXQ3181 to External Hardware                                           | 60 |

| Connections to the Power Source                                                         | 6  |

| Sensor Selection                                                                        | 6  |

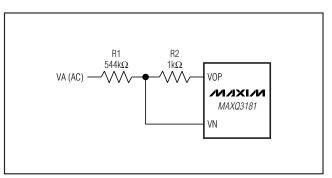

| Voltage Sensors                                                                         | 6  |

| Voltage-Divider                                                                         | 6  |

| Voltage Transformer                                                                     | 6  |

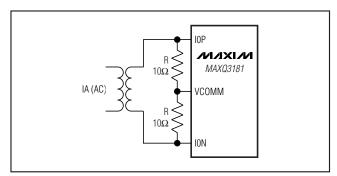

| Current Sensors                                                                         | 62 |

| Current Shunt                                                                           | 62 |

| Current Transformer                                                                     | 62 |

| Advanced Operation                                                                      | 62 |

| Modifying the ADC Operation                                                             | 62 |

| Fine-Tuning the DSP Controls                                                            | 62 |

| Fine-Tuning the Line Frequency Measurement                                              | 62 |

| Low-Power Measurement Mode (LOWPM)                                                      | 63 |

| Temperature                                                                             | 63 |

| Advanced Calibrations                                                                   | 63 |

| Calibrating Current Offset                                                              | 63 |

| Calibrating Linearity                                                                   | 63 |

| Calibrating Power/Energy Gain                                                           | 64 |

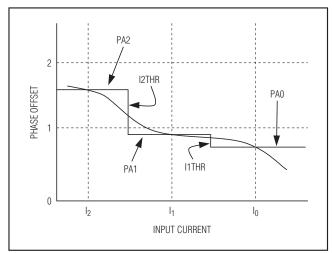

| Multipoint Phase Offset Calibration                                                     |    |

| Advanced Register Configurations                                                        | 65 |

| Analog Scan Configuration Registers                                                     | 65 |

| Time Slot Assignment—Current Channel X = A/B/C (SCAN_IX) (A: 0x008, B: 0x00C, C: 0x00A) | 65 |

| Time Slot Assignment—Voltage Channel X = A/B/C (SCAN_VX) (A: 0x009, B: 0x00D, C: 0x00B) | 66 |

| Time Slot Assignment—Neutral Current Channel (SCAN_IN) (0x00E)                          |    |

| Time Slot Assignment—Temperature Channel (SCAN_TE) (0x00F)                              |    |

| Neutral Current                                                                         |    |

| Auxiliary Channel Configuration (AUX_CFG) (0x010)                                       |    |

| DSP System Configuration                                                                |    |

| System Clock Frequency (SYS_KHZ) (0x012)                                                |    |

| Cycle Count (CYCNT) (0x01C)                                                             |    |

| Number of Scan Frames per DSP Cycle (NS) (0x040)                                        |    |

|                                                                                         |    |

| TABLE OF CONTENTS (continued)                                                                         |             |

|-------------------------------------------------------------------------------------------------------|-------------|

| Filter Coefficients                                                                                   | 71          |

| Line Cycle Noise Rejection Filter (REJ_NS) (0x02C)                                                    | 71          |

| Line Cycle Averaging Filter (AVG_NS) (0x02E)                                                          | 71          |

| Meter Measurement Averaging Filter (AVG_C) (0x030)                                                    | 72          |

| Meter Measurement Highpass Filter (HPF_C) (0x032)                                                     | 72          |

| Zero-Cross Lowpass Filter (ZC_LPF) (0x05A)                                                            | 72          |

| Hardware Mirror Registers                                                                             | 73          |

| ADC Configuration (R_ACFG) (0x04C)                                                                    | 73          |

| ADC Conversion Rate (R_ADCRATE) (0x04E)                                                               | 73          |

| ADC Settling Time (R_ADCACQ) (0x050)                                                                  | 74          |

| SPI Configuration (R_SPICF) (0x052)                                                                   | 74          |

| Timeouts                                                                                              | 75          |

| Zero-Crossing Timeout (NZX_TIMO) (0x054)                                                              | 75          |

| Communications Timeout (COM_TIMO) (0x056)                                                             | 75          |

| Energy Accumulation Timeout (ACC_TIMO) (0x058)                                                        | 75          |

| Phase-Angle Compensation                                                                              | 76          |

| Phase Offset Current Threshold 1 (I1THR) (0x05C)                                                      | 76          |

| Phase Offset Current Threshold 2 (I2THR) (0x05E)                                                      | 76          |

| Miscellaneous Gain                                                                                    | 76          |

| Neutral Current Gain (N.I_GAIN) (0x12E)                                                               | 76          |

| Linearity Compensation                                                                                | 77          |

| Linearity Offset, High Range, Phase $X = A/B/C$ (X.OFFS_HI) (A: 0x138, B: 0x224, C: 0x310)            |             |

| Linearity Gain Coefficient, Low Range, Phase $X = A/B/C$ (X.GAIN_LO) (A: 0x13A, B: 0x226, C: 0x312) . | 77          |

| Linearity Offset, Low Range, Phase $X = A/B/C$ (X.OFFS_LO) (A: 0x13C, B: 0x228, C: 0x314)             |             |

| Measurements—RAM Registers                                                                            |             |

| On-Demand RMS Result (N.IRMS) (0x11C)                                                                 |             |

| Energy Accumulated in the Last DSP Cycle                                                              |             |

| Real Energy, Phase X = A/B/C (X.ACT) (A: 0x1D0, B: 0x2BC, C: 0x3A8)                                   |             |

| Apparent Energy, Phase X = A/B/C (X.APP) (A: 0x1D8, B: 0x2C4, C: 0x3B0)                               |             |

| Checksum (CHKSUM) (0x060)                                                                             |             |

| Neutral Current                                                                                       |             |

| RMS Current, Neutral (I.N) (0x840)                                                                    |             |

| Special Commands                                                                                      |             |

| Applications Information                                                                              |             |

| Grounds and Bypassing                                                                                 |             |

| Specific Design Considerations for MAXQ3181-Based Systems                                             |             |

| Additional Documentation                                                                              | 82          |

| 6                                                                                                     | <b> </b> // |

| TABLE OF CONTENTS (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Package Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| TABLE OF CONTENTS (continued)  Technical Support Package Information Pin Configuration Pip Continue Pip Content Cont |  |

| Typical Application Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

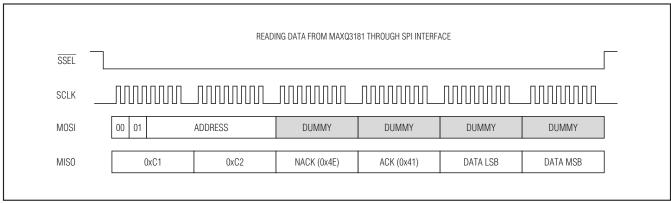

| Figure 5. Read SPI Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

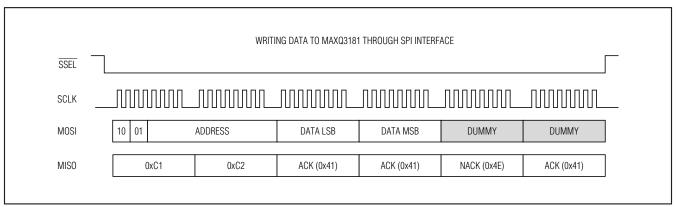

| Figure 6. Write SPI Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

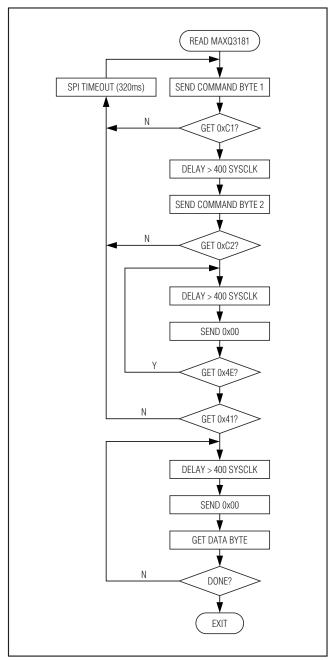

| Figure 7. Flowchart for Reading from MAXQ3181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Figure 8. Flowchart for Writing to MAXQ3181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Figure 9. Per Sample Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Figure 10. Computation of RMS Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

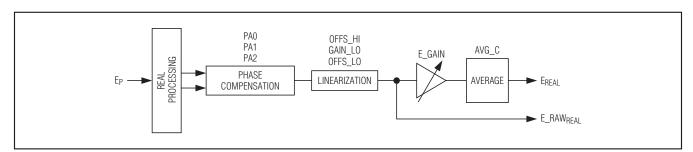

| Figure 11. Phase Compensation for Energy Calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

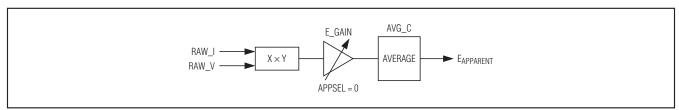

| Figure 12. Apparent Energy Calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Figure 16. Phase Offset vs. Input Current Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Table 1. Command Format for SPI Register Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Table 2. Command Format for SPI Register Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |