Data Sheet, V 1.3, Jun. 2006

# CIC751 Companion IC

## Microcontrollers

Never stop thinking

Edition 2006-06 Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2006. All Rights Reserved.

#### Attention please!

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Data Sheet, V 1.3, Jun. 2006

# CIC751 Companion IC

## Microcontrollers

Never stop thinking

| Revision | ENTIAL<br>History:                                           | 2006-06                                      | V 1.3    |  |  |  |

|----------|--------------------------------------------------------------|----------------------------------------------|----------|--|--|--|

| Previous | Version:                                                     | None.                                        |          |  |  |  |

| Page     | Subjects                                                     | (major changes since last revision)          |          |  |  |  |

| 25       | chapter 4.4.4. Power Sequencing was reworked for version 1.2 |                                              |          |  |  |  |

| 25       | chapter 4                                                    | .4.4. Power Sequencing was reworked for vers | sion 1.3 |  |  |  |

| 33       | table 4-13                                                   | B updated for version 1.3                    |          |  |  |  |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

## **Table of Contents**

## **Table of Contents**

| 1                                          | Summary of Features                                                       |

|--------------------------------------------|---------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                     | General Device Information4Introduction4Pin Configuration and Definition4 |

| <b>3</b><br>3.1<br>3.1.1<br>3.1.2<br>3.1.3 | Functional Description10Detailed Features10ADC11MLI12SSC12                |

| <b>4</b><br>4.1                            | Electrical Parameters                                                     |

| 4.1<br>4.2                                 | DC Parameters                                                             |

| 4.3                                        | Analog/Digital Converter Parameters                                       |

| 4.4                                        | AC Characteristics                                                        |

| 4.4.1                                      | Definition of Internal Timing                                             |

| 4.4.1.1                                    | Prescaler Mode 21                                                         |

| 4.4.1.2                                    | Phase Locked Loop (PLL) 21                                                |

| 4.4.2                                      | Testing Waveforms of the digital input/output signals 23                  |

| 4.4.3                                      | Output Rise and Fall Times 24                                             |

| 4.4.4                                      | Power Sequencing                                                          |

| 4.4.5                                      | Timing Parameters 27                                                      |

| 4.4.5.1                                    | Micro Link Interface (MLI) Timing 27                                      |

| 4.4.6                                      | Synchronous Serial Channel (SSC) Slave Mode Timing                        |

| 4.5                                        | Package and Reliability 32                                                |

| 4.5.1                                      | Packaging                                                                 |

| 4.5.2                                      | Package Outlines                                                          |

| 4.5.3                                      | Quality Declarations                                                      |

**Table of Contents**

#### **Summary of Features**

## **1** Summary of Features

This section provides a high-level description of the features on the CIC751.

- 5 V Analog to Digital Converter

- 16 analog input channels

- Internal low power oscillator

- Slave (SPI) SSC interface operating on 5 V or 3.3 V

- MLI Interface operating on 5 V or 3.3 V

- Maximum system frequency of 40 MHz

- Low-power design

- Single power supply concept design (for pad and core supply)

- Separated ADC supply

- Input and output pins with 3.3 V and 5.0 V

- Flexible clocking concept

- Crossbar bus architecture

#### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery.

For the available ordering codes for the CIC751 please refer to the "**Product Catalog Microcontrollers**", which summarizes all available microcontroller variants.

#### **General Device Information**

## 2 General Device Information

## 2.1 Introduction

The CIC751 is a companion IC for the Infineon AUDO-NG family of 32-bit microcontrollers. The major function of the CIC751 is to provide the AUDO-NG 32-bit microcontrollers with the capability of a 5 V Analog to Digital Converter (ADC). The interconnection of the CIC751 and the microcontroller is accomplished via either the Micro Link Interface (MLI) or the Synchronous Serial Interface (SSC). Internal operations of the CIC751 are supported by the very flexible on-chip DMA controller.

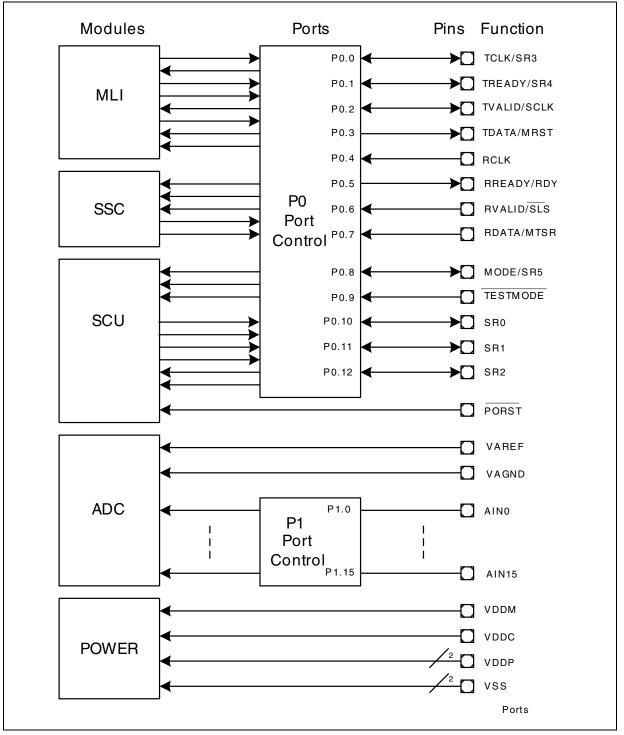

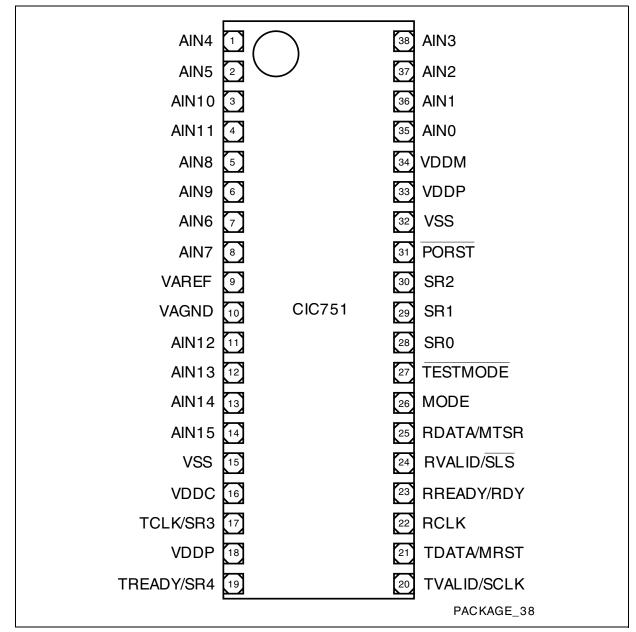

## 2.2 Pin Configuration and Definition

The pins of the CIC751 are described in detail in **Table 2-1**, including all their alternate functions.

| Symbol | Pin/Port   | I/O | Function                                                                           |

|--------|------------|-----|------------------------------------------------------------------------------------|

| AIN0   | 35<br>P1.0 | I   | Analog Input 0 <sup>1)</sup><br>For this pin a Multiplexer Test Mode is available. |

| AIN1   | 36<br>P1.1 | I   | Analog Input 1 <sup>1)</sup>                                                       |

| AIN2   | 37<br>P1.2 | I   | Analog Input 2 <sup>1)</sup>                                                       |

| AIN3   | 38<br>P1.3 | I   | Analog Input 3 <sup>1)</sup>                                                       |

| AIN4   | 1<br>P1.4  | I   | Analog Input 4 <sup>1)</sup>                                                       |

| AIN5   | 2<br>P1.5  | I   | Analog Input 5 <sup>1)</sup>                                                       |

| AIN6   | 7<br>P1.6  | I   | Analog Input 6 <sup>1)</sup>                                                       |

| AIN7   | 8<br>P1.7  | I   | Analog Input 7 <sup>1)</sup>                                                       |

| AIN8   | 5<br>P1.8  | I   | Analog Input 8 <sup>1)</sup>                                                       |

| AIN9   | 6<br>P1.9  | I   | Analog Input 9 <sup>1)</sup>                                                       |

#### Table 2-1Pin Definitions and Functions

Data Sheet

## **General Device Information**

| Table 2-1         Pin Definitions and Functions (cont'd)           |             |     |                                                                                                 |  |  |  |  |

|--------------------------------------------------------------------|-------------|-----|-------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                                                             | Pin/Port    | I/O | Function                                                                                        |  |  |  |  |

| AIN10                                                              | 3<br>P1.10  | I   | Analog Input 10 <sup>1)</sup>                                                                   |  |  |  |  |

| AIN11                                                              | 4<br>P1.11  | I   | Analog Input 11 <sup>1)</sup>                                                                   |  |  |  |  |

| AIN12                                                              | 11<br>P1.12 | 1   | Analog Input 12 <sup>1)</sup>                                                                   |  |  |  |  |

| AIN13                                                              | 12<br>P1.13 | 1   | Analog Input 13 <sup>1)</sup>                                                                   |  |  |  |  |

| AIN14                                                              | 13<br>P1.14 | I   | Analog Input 14 <sup>1)</sup>                                                                   |  |  |  |  |

| AIN15                                                              | 14<br>P1.15 | 1   | Analog Input 15 <sup>1)</sup>                                                                   |  |  |  |  |

| VAREF                                                              | 9           | I   | Analog Reference Voltage                                                                        |  |  |  |  |

| VAGND                                                              | 10          | I   | Analog Ground                                                                                   |  |  |  |  |

| TCLK/SR3                                                           | 17<br>P0.0  | I/O | MODE = 0:<br>MLI Transmit Channel Clock Output<br>MODE = 1:<br>Event output line 3              |  |  |  |  |

| TREADY/SR4                                                         | 19<br>P0.1  | I/O | MODE = 0:<br>MLI Transmit Channel Ready Input<br>MODE = 1:<br>Event request output line 4       |  |  |  |  |

| TVALID/SCLK20<br>P0.2I/O<br>MODE = 0:<br>MLI Transmit<br>MODE = 1: |             | I/O | MLI Transmit Channel Valid Output                                                               |  |  |  |  |

| TDATA/MRST                                                         | 21<br>P0.3  | I/O | MODE = 0:<br>MLI Transmit Channel Data Output<br>MODE = 1:<br>SPI Master Receive Slave Transmit |  |  |  |  |

| RCLK                                                               | 22<br>P0.4  | I/O | MODE = 0:<br>MLI Receive Channel Clock Input<br>MODE = 1:<br>GPIO                               |  |  |  |  |

Downloaded from Elcodis.com electronic components distributor

#### \_\_\_\_\_

## **CIC751**

## CONFIDENTIAL

## **General Device Information**

| Table 2-1     Pin Definitions and Functions (cont'd) |                                                                                               |                        |                                                                                                                                                                                          |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                                               | Pin/Port                                                                                      | I/O                    | Function                                                                                                                                                                                 |  |  |  |

| RREADY/RDY                                           | 23 I/O<br>P0.5                                                                                |                        | MODE = 0:<br>MLI Receive Channel Ready Output<br>MODE = 1:<br>SSC Ready Signal                                                                                                           |  |  |  |

| RVALID/SLS                                           | 24<br>P0.6                                                                                    | I/O                    | MODE = 0:<br>MLI Receive Channel Valid Input<br>MODE = 1:<br>SSC Select Slave                                                                                                            |  |  |  |

| RDATA/MTSR                                           | MODE = 0:<br>MLI Receive Channel Data Input<br>MODE = 1:<br>SPI Master Transmit Slave Receive |                        |                                                                                                                                                                                          |  |  |  |

| MODE <sup>2)</sup>                                   | 26<br>P0.8                                                                                    | I/O                    | Interface Selection<br>Pin MODE selects whether the on-chip MLI or<br>SSC are used to access the CIC751 device.<br>0: On-chip MLI<br>1: On-chip SSC<br>Event request output line 5 (SR5) |  |  |  |

| TESTMODE <sup>3)</sup>                               | 27<br>P0.9                                                                                    | I/O                    | Test Mode Selection <sup>4)</sup><br>0: Reserved; do no use<br>1: Normal Mode                                                                                                            |  |  |  |

| SR0                                                  | 28<br>P0.10                                                                                   | I/O                    | Event request output line 0                                                                                                                                                              |  |  |  |

| SR1                                                  | 29<br>P0.11                                                                                   | I/O                    | External Trigger                                                                                                                                                                         |  |  |  |

| SR2                                                  | 30<br>P0.12                                                                                   | I/O                    | External Trigger                                                                                                                                                                         |  |  |  |

| PORST                                                | 31                                                                                            |                        | Power-on Reset <sup>5)</sup>                                                                                                                                                             |  |  |  |

| V <sub>DDM</sub>                                     | 34                                                                                            | +5 V                   | Power Supply, supply for ADC module                                                                                                                                                      |  |  |  |

| V <sub>DDP</sub>                                     | 18, 33                                                                                        | +3.3 V<br>or<br>+5.0 V | Power Supply, supply for I/O pads                                                                                                                                                        |  |  |  |

| V <sub>DDC</sub>                                     | 16                                                                                            | +2.5 V                 | Power Supply, supply for digital module cores <sup>6)</sup>                                                                                                                              |  |  |  |

| V <sub>ss</sub>                                      | 15, 32                                                                                        | 0 V                    | Ground                                                                                                                                                                                   |  |  |  |

#### Table 2-1 Pin Definitions and Functions (cont'd)

#### **General Device Information**

- 1) In addition to the analog input function of pin P1.x, a digital input stage is available. This input stage is activated while STCU\_SYSCON.P1DIDIS = 0.

- 2) The initial logic state on pin MODE is latched while the PORST input is active. A weak pull-up can be disabled if used as the SR5 pin.

- 3) The initial logic state on pin TESTMODE is latched while the PORST input is active.

- 4) The meaning of 0 and 1 is only valid while this pin is latched. Thereafter it can be used as GPIO pin.

- 5) This pin has no internal pulls. If required an external pull has to be provided.

- 6) An external capacitance of 220 nF is required for this pin.

Figure 2-1 shows the pin-out for a 38-pin package

#### **General Device Information**

Figure 2-1 Pins for P/PG-TSSOP-38 Package

#### **General Device Information**

Figure 2-2 Pin Numbering for P/PG-TSSOP-38 Package

#### **Functional Description**

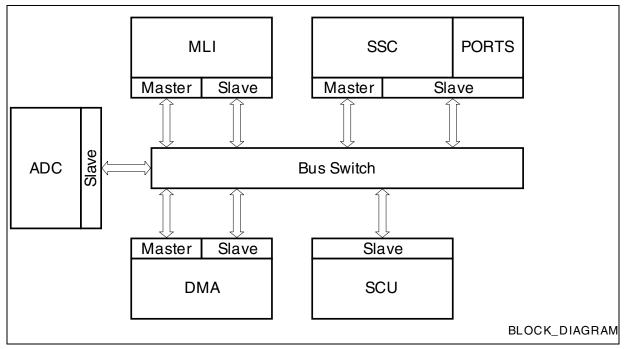

## **3** Functional Description

**Figure 3-1** provides the block diagram of the CIC751 companion chip. This design allows access to the ADC by the host CPU without sacrificing any of the features of the ADC. This can be achieved because all registers of the ADC are mapped to the on-chip bus. This bus can be accessed via one of the two serial interfaces. Selection of the interface is made via pin MODE, which can be directly connected to the supply voltage or via pull-up/down resistors.

The bus domain is completely separated from the address domain on the CPU chip. The addresses of all modules on the companion chip are 32-bit addresses. Transactions between the CPU and the SSC are executed with the SSC transmission protocol; transactions between the MLI and the CPU use the MLI transmission protocol.

Each transaction via any of the two serial interfaces is defined by address, data, data width, and type of frame. The address from which data is read or written to, is related to the address domain. The data width may be 8, 16 or 32 bits for the MLI and 16 bits for the SSC. The ADC and the MLI may send request triggers to the DMA Controller.

Figure 3-1 CIC751 Block Diagram

## 3.1 Detailed Features

The following sections provide detailed information about each of the on-chip modules.

**CIC751**

CONFIDENTIAL

## **Functional Description**

## 3.1.1 ADC

The CIC751 provides an Analog/Digital Converter with 8-bit or 10-bit resolution and a sample & hold circuit on-chip. An input multiplexer selects between up to 16 analog input channels either via software (Fixed Channel Modes) or automatically (Auto Scan Modes).

To fulfill most requirements of embedded control applications, the ADC supports the following conversion modes:

- Standard Conversions

- Fixed Channel Single Conversion

produces just one result from the selected channel

- Fixed Channel Continuous Conversion repeatedly converts the selected channel

- Auto Scan Single Conversion

produces one result from each of a selected group of channels

- Auto Scan Continuous Conversion repeatedly converts the selected group of channels

- Wait for Read Mode start a conversion automatically when the previous result was read

- Channel Injection Mode

can insert the conversion of a specific channel into a group conversion (auto scan)

The key features of the ADC are:

- Use of Successive Approximation Method

- Integrated sample and hold functionality

- Analog Input Voltage Range from 0V to 5V

- 16 Analog Input Channels

- 16 ADC result registers

- Resolution:

<u>8-Bit or 10-Bit in Compatibili</u>

- 8-Bit or 10-Bit in Compatibility Mode

- Minimum Conversion Time: 2.55 µs @ 10-Bit

Total Uppediveted Error (TUE): 11 CB @ 2 Bit

- Total Unadjusted Error (TUE): $\pm$ 1 LSB @ 8-Bit,  $\pm$  2 LSB @ 10-Bit

- Support of several Conversion Modes

Fixed Channel Single Conversion

Fixed Channel Continuous Conversion

Auto Scan Single Conversion

Auto Scan Continuous Conversion

Wait for Result Read and Start Next Conversion

Channel Injection during Group Conversion

- Programmable Conversion and Sample Timing Scheme

- Automatic Self-Calibration to changing temperatures or process variations

#### **Functional Description**

#### 3.1.2 MLI

The Micro Link Interface (MLI) is a fast synchronous serial interface that makes it possible to exchange data between microcontrollers or other devices.

The key features of the MLI are:

- Synchronous serial communication between an MLI transmitter and an MLI receiver

- Different system clock speeds are supported in the MLI transmitter and MLI receiver due to full handshake protocol (4 lines between a transmitter and a receiver)

- Fully transparent read/write access is supported (= remote programming)

- Complete address range of target device (Remote Controller) is available

- Specific frame protocol to transfer commands, addresses, and data

- Error detection by parity bit

- 32-bit, 16-bit, or 8-bit data transfers are supported

- Programmable baud rate:  $f_{MLI}/2$  (max.:  $f_{MLI} = f_{SYS}$ )

- Multiple receiving devices are supported

## 3.1.3 SSC

The SSC supports full-duplex and half-duplex serial synchronous communication up to 10 Mbit/s (@ 40 MHz module clock). The serial clock signal is received from an external master (Slave Mode). Data width, shift direction, clock polarity, and phase are programmable. This allows communication with SPI-compatible devices. Transmission and reception of data is double-buffered. A shift clock generator provides the SSC with a separate serial clock signal.

This section describes only the use of the SSC module as a slave because the CIC751 always operates as a slave to a host.

## Features

- Slave Mode operation

- Full-duplex or half-duplex operation

- Automatic pad control possible

- Flexible data format

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: Idle low or idle high state for the shift clock

- Programmable clock/data phase: Data shift with leading or trailing edge of the shift clock

- Internal Master Function

- Access to the all addresses

- Automatic address handling

- Automatic data handling

Data Sheet

#### **Electrical Parameters**

## 4 Electrical Parameters

The Electrical Specifications comprise parameters to ensure the product's lifetime (Absolute Maximum Parameters) as well as parameters to describe the product's operating conditions.

## 4.1 General Parameters

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

Note: Table 4-2 and Table 4-3 are valid for port 0 only.

| Parameter                                                          | Symbol           |      | Values |                           | Unit | Note /             |

|--------------------------------------------------------------------|------------------|------|--------|---------------------------|------|--------------------|

|                                                                    |                  | Min. | Тур.   | Max.                      |      | Test Condit<br>ion |

| Storage temperature                                                | T <sub>ST</sub>  | -65  | -      | 150                       | °C   | -                  |

| Voltage on $V_{DDC}$ pins with respect to ground ( $V_{SS}$ )      | V <sub>DDC</sub> | -0.5 | -      | 3.25                      | V    | -                  |

| Voltage on $V_{DDP}$ pins with respect to ground ( $V_{SS}$ )      | V <sub>DDP</sub> | -0.5 | -      | 6.2                       | V    | -                  |

| Voltage on any pin with respect to ground (V <sub>SS</sub> )       | V <sub>IN</sub>  | -0.5 | -      | V <sub>DDP</sub> +<br>0.5 | V    | _                  |

| Input current on any pin during overload condition                 | -                | -10  | -      | 10                        | mA   | _                  |

| Absolute sum of all input<br>currents during overload<br>condition | -                | -    | -      | 100                       | mA   | -                  |

| Junction temperature                                               | TJ               | -40  | -      | 150                       | °C   | under bias         |

#### Table 4-1 Absolute Maximum Ratings

## **Operating Conditions**

The following operating conditions must not be exceeded to ensure correct operation of the CIC751. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

#### **Electrical Parameters**

**CIC751**

#### Table 4-2 Operating Condition Parameters

| Parameter                                              | Symbol             |                | Value | Unit                   | Note /             |                                                   |

|--------------------------------------------------------|--------------------|----------------|-------|------------------------|--------------------|---------------------------------------------------|

|                                                        |                    | Min. Typ. Max. |       |                        | Test Condit<br>ion |                                                   |

| System frequency                                       | f <sub>sys</sub>   | -              | -     | 40                     | MHz                | -                                                 |

| RCOSC output frequency                                 | f <sub>RCOSC</sub> | 8              | 9     | 10                     | MHz                | over all conditions                               |

| Digital supply voltage for the core                    | V <sub>DDC</sub>   | 2.25           | -     | 2.75                   | V                  | Active<br>Mode, $f_{SYS} = f_{SYSmax}^{1}$        |

| Digital supply voltage for IO pads for 5 V Mode        | V <sub>DDP</sub>   | 4.5            | 5.0   | 5.5                    | V                  | Active<br>Mode <sup>2)3)</sup>                    |

| Digital supply voltage for IO pads for 3.3 V Mode      | V <sub>DDP</sub>   | 3.13           | 3.3   | 3.47                   | V                  | Active<br>Mode <sup>4)5)</sup>                    |

| Supply Voltage Difference<br>for IO pads in 5.0 V Mode | $\Delta V_{DD}$    | -0.5           | -     | -                      | V                  | V <sub>DDP</sub> - V <sub>DDC</sub> <sup>6)</sup> |

| Digital ground voltage                                 | V <sub>SS</sub>    | 0              | -     | -                      | V                  | Reference voltage                                 |

| Overload current                                       | I <sub>OV</sub>    | -5             | -     | 5                      | mA                 | Per IO pin <sup>7)8)</sup>                        |

|                                                        |                    | -2             | _     | 5                      | mA                 | Per analog<br>input pin <sup>7)8)</sup>           |

| Overload current coupling                              | K <sub>OVA</sub>   | -              | -     | 1.0 × 10 <sup>-4</sup> | -                  | l <sub>ov</sub> > 0                               |

| factor for analog inputs <sup>9)</sup>                 |                    | _              | -     | 1.5 × 10 <sup>-3</sup> | -                  | l <sub>ov</sub> < 0                               |

| Overload current coupling                              | K <sub>OVD</sub>   | -              | -     | 5.0 × 10 <sup>-3</sup> | -                  | l <sub>ov</sub> > 0                               |

| factor for digital I/O pins <sup>9)</sup>              |                    | _              | —     | 1.0 × 10 <sup>-2</sup> | _                  | l <sub>ov</sub> < 0                               |

| Absolute sum of overload currents                      | $\Sigma   _{OV} $  | _              | -     | 50                     | mA                 | 8)                                                |

| External Load<br>Capacitance                           | CL                 | -              | -     | 50                     | pF                 |                                                   |

1)  $f_{SYSmax} = 40 \text{ MHz}$

2) External circuitry must guarantee low-level at the PORST pin at least until both power supply voltages have reached the operating range.

- 3) The specified voltage range is allowed for operation. The range limits may be reached under extreme operating conditions. However, specified parameters, such as leakage currents, refer to the standard operating voltage range of  $V_{DDP} = 4.5 \text{ V}$  to 5.5 V.

- 4) External circuitry must guarantee low-level at the PORST pin at least until both power supply voltages have reached the operating range.

#### **Electrical Parameters**

- 5) The specified voltage range is allowed for operation. The range limits may be reached under extreme operating conditions. However, specified parameters, such as leakage currents, refer to the standard operating voltage range of V<sub>DDP</sub> = 4.5 V to 5.5 V.

- 6) This limitation must be fulfilled under all operating conditions including power-ramp-up and power-ramp-down.

- 7) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range: V<sub>OV</sub> > V<sub>DDP</sub> + 0.5 V (I<sub>OV</sub> > 0) or V<sub>OV</sub> < V<sub>SS</sub> 0.5 V (I<sub>OV</sub> < 0). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltages must remain within the specified limits. Proper operation is not guaranteed if overload conditions occur on functional pins.

- 8) Not subject to production test verified by design/characterization.

- 9) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it.

The total current through a pin is  $|I_{TOT}| = |I_{OZ}| + (|I_{OV}| \times K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

## 4.2 DC Parameters

The following chapter describes the DC parameters of the device.

| Parameter                                    | Symbol           |                               | Values |                        |    | Note /                                                                              |

|----------------------------------------------|------------------|-------------------------------|--------|------------------------|----|-------------------------------------------------------------------------------------|

|                                              |                  | Min.                          | Тур.   | Max.                   |    | Test Condition                                                                      |

| Input low voltage<br>TTL                     | V <sub>IL</sub>  | -                             | -      | $0.3 	imes V_{DDP}$    | V  | 2)                                                                                  |

| Input low voltage<br>(Special Threshold)     | V <sub>ILS</sub> | -                             | -      | $0.45 \times V_{DDP}$  | V  | 3)                                                                                  |

| Input high voltage<br>TTL                    | V <sub>IH</sub>  | $0.7 \times V_{DDP}$          | -      | -                      | V  | 2)                                                                                  |

| Input high voltage<br>(Special Threshold)    | V <sub>IHS</sub> | 0.8×V <sub>DDP</sub><br>- 0.2 | -      | V <sub>DDP</sub> + 0.5 | V  | 3)                                                                                  |

| Input Hysteresis<br>(Special Threshold)      | HYS              | $0.02 \times V_{DDP}$         | -      | -                      | V  | $V_{DDP}$ in [V], Series resistance = 0 $\Omega^{3}$                                |

| Output low voltage                           | V <sub>OL</sub>  | -                             | -      | 1.0                    | V  | $I_{OL} = 8 \text{ mA}^{4)}$                                                        |

|                                              |                  | _                             | -      | 0.45                   | V  | $I_{OL} = 2.5 \text{ mA}^{4(5)}$                                                    |

| Output high voltage <sup>6)</sup>            | V <sub>OH</sub>  | V <sub>DDP</sub> - 1.0        | -      | _                      | V  | I <sub>OH</sub> = - 8 mA <sup>4)</sup>                                              |

|                                              |                  | V <sub>DDP</sub> -<br>0.45    | -      | -                      | V  | $I_{OH} = -2.5 \text{ mA}^{(4)5)}$                                                  |

| Input leakage current (Port 1) <sup>7)</sup> | I <sub>OZ1</sub> | -                             | _      | ±300                   | nA | $\begin{array}{l} 0 \ V < V_{IN} < V_{DDM}, \\ T_A \leq 125 \ ^\circ C \end{array}$ |

Table 4-3

DC Characteristics (Operating Conditions apply)<sup>1)</sup>

#### **Electrical Parameters**

| Parameter                                                | Symbol                           | Symbol Values |      |                               |    | Note /                                                                                                   |  |

|----------------------------------------------------------|----------------------------------|---------------|------|-------------------------------|----|----------------------------------------------------------------------------------------------------------|--|

|                                                          |                                  | Min.          | Тур. | Max.                          |    | Test Condition                                                                                           |  |

| Leakage current of<br>pin VAREF<br>(Idle Mode)           | I <sub>VAREFIM</sub>             | -             | -    | ±800                          | nA | $\begin{array}{l} 0 \ V < V_{\rm IN} < V_{\rm DDP}, \\ T_{\rm A} \leq 125 \ ^{\circ}{\rm C} \end{array}$ |  |

| Leakage current of<br>pin VAREF<br>(Active Mode)         | I <sub>VAREFAM</sub>             | -             | -    | ±20 +<br>I <sub>VAREFIM</sub> | μA | $\begin{array}{l} 0 \ V < V_{\rm IN} < V_{\rm DDP}, \\ T_{\rm A} \leq 125 \ ^{\circ}{\rm C} \end{array}$ |  |

| Input leakage current<br>(Port 0) <sup>7)</sup>          | I <sub>OZ2</sub>                 | -             | -    | ±500                          | nA | 0.45 V < V <sub>IN</sub> <<br>V <sub>DDP</sub>                                                           |  |

| Configuration pull-up                                    | I <sub>CPUH</sub> 9)             | _             | _    | -5                            | μA | $V_{IN} = V_{IHmin}$                                                                                     |  |

| current <sup>8)</sup>                                    | I <sub>CPUL</sub> <sup>10)</sup> | -100          | -    | -                             | μA | $V_{IN} = V_{ILmax}$                                                                                     |  |

| Level active hold current                                | I <sub>LHA</sub> <sup>11)</sup>  | -100          | -    | -                             | μA | V <sub>OUT</sub> = 0.45 V                                                                                |  |

| Pin capacitance <sup>12)</sup><br>digital inputs/outputs | C <sub>IO</sub>                  | -             | -    | 10                            | pF | -                                                                                                        |  |

Keeping signal levels within the limits specified in this table, ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current I<sub>OV</sub>.

2) This parameter is tested for PORST

3) This parameter is tested for P0.

The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 4-4, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

5) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are guaranteed.

6) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- 7) An additional error current  $(I_{INJ})$  will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- 8) This specification is valid during Reset for configuration on PORT0.

- 9) The maximum current may be drawn while the respective signal line remains inactive.

- 10) The minimum current must be drawn to drive the respective signal line active.

- 11) The minimum current must be drawn to drive the respective signal line active.

12) Only one point on the curve is tested in production. The rest of the curve is verified by design/characterization.

#### **Electrical Parameters**

| Port Output Driver            | Maximum Output Current                                    | Nominal Output Current                      |  |  |  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------|---------------------------------------------|--|--|--|--|--|--|--|

| Mode                          | (I <sub>OLmax</sub> , -I <sub>OHmax</sub> ) <sup>1)</sup> | (I <sub>OLnom</sub> , -I <sub>OHnom</sub> ) |  |  |  |  |  |  |  |

| Strong driver <sup>2)3)</sup> | 8 mA                                                      | 2.5 mA                                      |  |  |  |  |  |  |  |

| Strong driver <sup>4)5)</sup> | 10 mA                                                     | 2.5 mA                                      |  |  |  |  |  |  |  |

| Medium driver <sup>6)</sup>   | 4.0 mA                                                    | 1.0 mA                                      |  |  |  |  |  |  |  |

| Weak driver <sup>6)</sup>     | 0.5 mA                                                    | 0.1 mA                                      |  |  |  |  |  |  |  |

#### Table 4-4 Current Limits for Port Output Drivers

An output current above II<sub>OXnom</sub>I may be drawn from up to three pins at the same time. For any group of 16 neighboring port output pins the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

2) For 3.3 V operation.

- 3) The strong driver is used for all pins beside pin 35 (AIN0)

- 4) For 5.0 V operation.

- 5) The strong driver is used for all pins beside pin 35 (AIN0)

- 6) The medium / weak driver is only used for pin 35 (AIN0)

| Parameter                                                       | Symbol Val       |      |      | alues Unit |    | Note /                           |

|-----------------------------------------------------------------|------------------|------|------|------------|----|----------------------------------|

|                                                                 |                  | Min. | Тур. | Max.       |    | Test Condition                   |

| Power supply current<br>(active) with all<br>peripherals active | I <sub>DDC</sub> | -    | _    | 30         | mA | at 40 MHz<br>system<br>frequency |

| Power supply current<br>(active) with all<br>peripherals active | I <sub>DDC</sub> | _    | _    | 18         | mA | at 20 MHz<br>system<br>frequency |

| Pad I/O current                                                 | I <sub>DDP</sub> | -    | 4    | _          | mA |                                  |

| V <sub>DDM</sub> supply current                                 | I <sub>DDM</sub> | —    | -    | 5          | mA |                                  |

#### Table 4-5Power Consumption CIC751

## 4.3 Analog/Digital Converter Parameters

The parameters of the ADC module are described below.

Downloaded from Elcodis.com electronic components distributor

## **Electrical Parameters**

| Parameter                                         | Symbol             | Values                                                                        |           |                           | Unit            | Note /           |  |

|---------------------------------------------------|--------------------|-------------------------------------------------------------------------------|-----------|---------------------------|-----------------|------------------|--|

|                                                   |                    | Min.                                                                          | Typ. Max. |                           |                 | Test Condition   |  |

| Analog supply voltage                             | V <sub>DDM</sub>   | 4.5                                                                           | 5.0       | 5.5                       | V               | 1)               |  |

| Analog reference supply                           | V <sub>AREF</sub>  | 4.5                                                                           | _         | V <sub>DDM</sub><br>+ 0.1 | V               | 2)               |  |

| Analog reference ground                           | V <sub>AGND</sub>  | V <sub>SS</sub> - 0.1                                                         | -         | V <sub>SS</sub> +<br>0.1  | V               | -                |  |

| Analog input voltage range                        | V <sub>AIN</sub>   | V <sub>AGND</sub>                                                             | -         | V <sub>AREF</sub>         | V               | 3)               |  |

| Basic clock frequency                             | $f_{\rm BC}$       | 0.5                                                                           | _         | 20                        | MHz             | 4)               |  |

| Conversion time for 10-bit result <sup>5)</sup>   | t <sub>C10P</sub>  | $52 \times t_{BC} + t_{S} + 6 \times t_{SYS}$                                 | -         | -                         | -               | Post-calibr. on  |  |

|                                                   | t <sub>C10</sub>   | $\begin{array}{c} 40 \times t_{BC} + t_{S} \\ + 6 \times t_{SYS} \end{array}$ | -         | -                         | -               | Post-calibr. off |  |

| Conversion time for<br>8-bit result <sup>5)</sup> | t <sub>C8P</sub>   | $\begin{array}{c} 44 \times t_{BC} + t_{S} \\ + 6 \times t_{SYS} \end{array}$ | -         | -                         | -               | Post-calibr. on  |  |

|                                                   | t <sub>C8</sub>    | $\begin{array}{c} 32 \times t_{BC} + t_{S} \\ + 6 \times t_{SYS} \end{array}$ | -         | -                         | -               | Post-calibr. off |  |

| Calibration time after reset                      | t <sub>CAL</sub>   | 484                                                                           | -         | 11,696                    | t <sub>BC</sub> | 6)               |  |

| Total unadjusted error                            | TUE                | -                                                                             | _         | ±2                        | LSB             | 2)               |  |

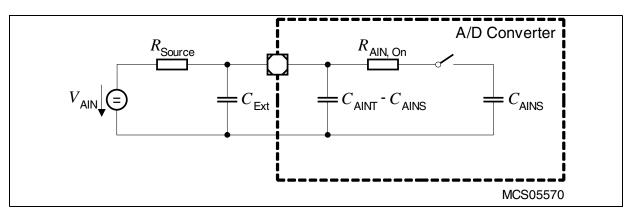

| Total capacitance of an analog input              | C <sub>AINT</sub>  | -                                                                             | -         | 15                        | pF              | 7)               |  |

| Switched capacitance of an analog input           | C <sub>AINS</sub>  | _                                                                             | -         | 10                        | pF              | 7)               |  |

| Resistance of the analog input path               | R <sub>AIN</sub>   | -                                                                             | -         | 2                         | kΩ              | 7)               |  |

| Total capacitance<br>of the reference input       | C <sub>AREFT</sub> | -                                                                             | -         | 20                        | pF              | 7)               |  |

| Switched capacitance of the reference input       | C <sub>AREFS</sub> | -                                                                             | _         | 15                        | pF              | 7)               |  |

| Resistance of the reference input path            | R <sub>AREF</sub>  | -                                                                             | -         | 1                         | kΩ              | 7)               |  |

#### **Electrical Parameters**

CIC751

- The specified voltage range is allowed for operation. The range limits may be reached under extreme operating conditions. However, specified parameters, such as leakage currents, refer to the standard operating voltage range of V<sub>DDM</sub> = 4.5 V to 5.5 V.

- 2) TUE is tested at  $V_{AREF} = V_{DDP} + 0.1 V$ ,  $V_{AGND} = 0 V$ . It is verified by design for all other voltages within the defined voltage range.

If the analog reference supply voltage drops below 4.5 V (i.e.  $V_{AREF} \ge 4.0$  V) or exceeds the power supply voltage by up to 0.2 V (i.e.  $V_{AREF} = V_{DDP} + 0.2$  V) the maximum TUE is increased to ±3 LSB. This range is not subject to production test.

The specified TUE is guaranteed only, if the absolute sum of input overload currents on Port 1 pins (see  $I_{OV}$  specification) does not exceed 10 mA, and if  $V_{AREF}$  and  $V_{AGND}$  remain stable during the respective period of time. During the reset calibration sequence the maximum TUE may be ±4 LSB.

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 4) The limit values for  $f_{BC}$  must not be exceeded when selecting the peripheral frequency and the ADCTC setting.

- 5) This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time to load the result register with the conversion result (t<sub>SYS</sub> = 1/f<sub>SYS</sub>). Values for the basic clock t<sub>BC</sub> depend on programming and can be taken from Table 4-7. When the post-calibration is switched off, the conversion time is reduced by 12 x t<sub>BC</sub>.

- 6) The actual duration of the reset calibration depends on the noise on the reference signal. Conversions executed during the reset calibration increase the calibration time. The TUE for those conversions may be increased.

- 7) Not subject to production test verified by design/characterization.

The given parameter values cover the complete operating range. Under relaxed operating conditions (temperature, supply voltage) reduced values can be used for calculations. At room temperature and nominal supply voltage the following typical values can be used:

$C_{AINTtyp} = 12 \text{ pF}, C_{AINStyp} = 7 \text{ pF}, R_{AINtyp} = 1.5 \text{ k}\Omega, C_{AREFTtyp} = 15 \text{ pF}, C_{AREFStyp} = 13 \text{ pF}, R_{AREFtyp} = 0.7 \text{ k}\Omega.$

Figure 4-1 Equivalent Circuitry for Analog Inputs

Sample time and conversion time of the CIC751's A/D Converter are programmable. In compatibility mode, the above timing can be calculated using **Table 4-7**. The limit values for  $f_{BC}$  must not be exceeded when selecting ADCTC.

#### **Electrical Parameters**

| ADCON.15 14<br>(ADCTC) | A/D Converter Basic Clock $f_{\rm BC}$ | ADCON.13 12<br>(ADSTC) | Sample Time        |

|------------------------|----------------------------------------|------------------------|--------------------|

| 00                     | <i>f</i> <sub>SYS</sub> / 4            | 00                     | $t_{BC} \times 8$  |

| 01                     | f <sub>SYS</sub> / 2                   | 01                     | $t_{BC} \times 16$ |

| 10                     | f <sub>SYS</sub> / 16                  | 10                     | $t_{BC} \times 32$ |

| 11                     | f <sub>SYS</sub> / 8                   | 11                     | $t_{BC} \times 64$ |

#### Table 4-7 A/D Converter Computation Table<sup>1)</sup>

1) These selections are available in compatibility mode. An improved mechanism to control the ADC input clock can be selected.

#### **Converter Timing Example**

| Assumptions:      | $f_{\rm SYS}$     | = 40 MHz (i.e. t <sub>SYS</sub> = 25 ns), ADCTC = '01', ADSTC = '00'                   |

|-------------------|-------------------|----------------------------------------------------------------------------------------|

| Basic clock       | $f_{\rm BC}$      | = $f_{SYS}$ / 2 = 20 MHz, i.e.<br>t <sub>BC</sub> = 50 ns                              |

| Sample time       | t <sub>s</sub>    | = t <sub>BC</sub> × 8 = 400 ns                                                         |

| Conversion 10-bi  | t:                |                                                                                        |

| With post-calibr. | t <sub>C10P</sub> | = $52 \times t_{BC} + t_{S} + 6 \times t_{SYS}$ = (2600 + 400 + 150) ns = 3.15 µs      |

| Post-calibr. off  | t <sub>C10</sub>  | = $40 \times t_{BC} + t_{S} + 6 \times t_{SYS}$ = (2000 + 400 + 150) ns = 2.55 $\mu$ s |

| Conversion 8-bit: |                   |                                                                                        |

| With post-calibr. | t <sub>C8P</sub>  | = $44 \times t_{BC} + t_{S} + 6 \times t_{SYS}$ = (2200 + 400 + 150) ns = 2.75 $\mu$ s |

| Post-calibr. off  | t <sub>C8</sub>   | = $32 \times t_{BC} + t_{S} + 6 \times t_{SYS}$ = (1600 + 400 + 150) ns = 2.15 µs      |

#### **Electrical Parameters**

## 4.4 AC Characteristics

The internal operation and consequently the timings of the CIC751 are based on the internal system clock  $\rm f_{SYS}.$

## 4.4.1 Definition of Internal Timing

The system clock signal  $f_{\rm SYS}$  can be generated from the oscillator clock signal  $f_{\rm OSC}$  or from the clock applied to the RCLK pin via different mechanisms. The duration of system clock periods and their variation (and also the derived external timing) depend on the used mechanism to generate  $f_{\rm SYS}$ . This influence must be regarded when calculating the timings for the CIC751.

The used mechanism to generate the system clock is selected by register PLLCON.

## 4.4.1.1 Prescaler Mode

When Prescaler Mode is configured (SCU\_PLLCON.PLLCTRL =  $01_B$ ) the system clock is derived from the internal oscillator through the P- and K-dividers:

$f_{SYS} = f_{OSC} / ((SCU_PLLCON.PDIV+1) \times (SCU_PLLCON.KDIV+1)).$

If both divider factors are selected as '1' (SCU\_PLLCON.PDIV = SCU\_PLLCON.KDIV = '0') the frequency of  $f_{SYS}$  directly follows the frequency of  $f_{OSC}$  so the high and low time of  $f_{SYS}$  is defined by the duty cycle of the input clock  $f_{OSC}$ .

The lowest system clock frequency is achieved by selecting the maximum values for both divider factors:

$f_{\text{SYS}} = f_{\text{OSC}} / ((3+1) \times (14+1)) = f_{\text{OSC}} / 60.$

## 4.4.1.2 Phase Locked Loop (PLL)

When PLL operation is configured (SCU\_PLLCON.PLLCTRL = 11<sub>B</sub>) the on-chip phase locked loop is enabled and provides the system clock. The PLL multiplies the input frequency by the factor F ( $f_{SYS} = f_{OSC} \times F$ ) which results from the input divider, the multiplication factor, and the output divider (F = SCU\_PLLCON.NDIV+1 / (SCU\_PLLCON.PDIV+1 × SCU\_PLLCON.KDIV+1)). The PLL circuit synchronizes the system clock to the input clock. This synchronization is done smoothly, i.e. the system clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{SYS}$  is constantly adjusted so it is locked to  $f_{OSC}$ . The slight variation causes a jitter of  $f_{SYS}$  which also affects the duration of individual TCMs.

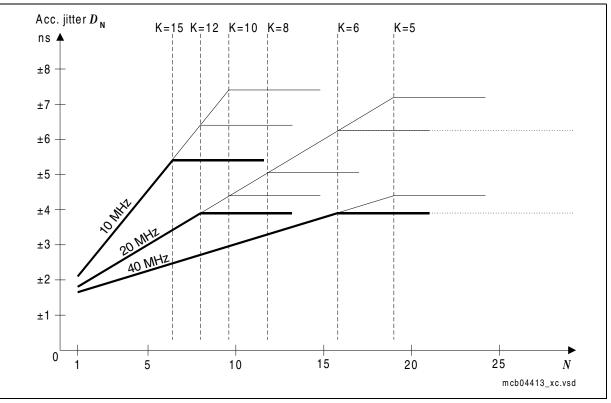

The actual minimum value for TCM depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency so it corresponds to the applied input frequency the relative deviation for periods of more than one TCM is lower than for one single TCM (see formula and Figure 4-2).

infineon

CONFIDENTIAL

#### **Electrical Parameters**

This is especially important for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective time frame. The VCO output clock is divided by the output prescaler (K = SCU\_PLLCON.KDIV+1) to generate the system clock signal  $f_{SYS}$ . Therefore, the number of VCO cycles can be represented as K × *N*, where *N* is the number of consecutive  $f_{SYS}$  cycles (TCM).

For a period of  $N_N \times \text{TCM}$  the accumulated PLL jitter is defined by the deviation D:  $D_N [ns] = \pm (1.5 + 6.32 \times N / f_{SYS}); f_{SYS}$  in [MHz], N = number of consecutive TCMs. So, for a period of 3 TCMs @ 20 MHz and K = 12:  $D_3 = \pm (1.5 + 6.32 \times 3 / 20) = 2.448$  ns. This formula is applicable for K × N < 95. For longer periods the K×N=95 value can be used. This steady value can be approximated by:  $D_{Nmax} [ns] = \pm (1.5 + 600 / (K \times f_{SYS})).$

Figure 4-2 Approximated Accumulated PLL Jitter

Note: The bold lines indicate the minimum accumulated jitter which can be achieved by selecting the maximum possible output prescaler factor K.

Different frequency bands can be selected for the VCO, so the operation of the PLL can be adjusted to a wide range of input and output frequencies:

Downloaded from Elcodis.com electronic components distributor

#### **Electrical Parameters**

| PLLCON.PLLVB | VCO Frequency Range | Base Frequency Range |

|--------------|---------------------|----------------------|

| 00           | 100 150 MHz         | 20 80 MHz            |

| 01           | 150 200 MHz         | 40 130 MHz           |

| 10           | 200 250 MHz         | 60 180 MHz           |

| 11           | Reserved            |                      |

#### Table 4-8 VCO Bands for PLL Operation<sup>1)</sup>

1) Not subject to production test - verified by design/characterization.

## 4.4.2 Testing Waveforms of the digital input/output signals

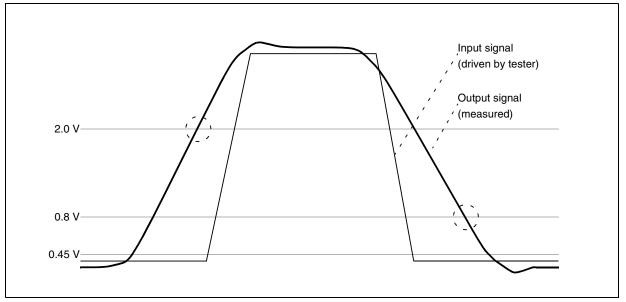

The relation between a real and the ideal digital waveform, together with the characteristically measurement levels is shown below.

#### Figure 4-3 Input Output Waveforms

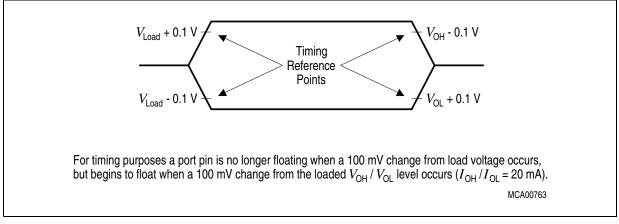

The figure below shows the transition between an actively driven digital output level and three-state (input state).

**CIC751**

#### **Electrical Parameters**

## Figure 4-4 Float Waveforms

## 4.4.3 Output Rise and Fall Times

The Output Rise/Fall time of a GPIO is  $t_r = t_f = 14$ ns, at  $C_L = 50$ pF.

#### **Electrical Parameters**

## 4.4.4 Power Sequencing

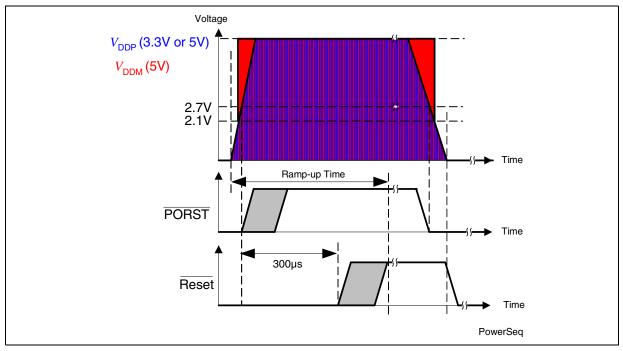

The CIC751 device needs two power supply voltages: digital ports power supply voltage  $V_{DDP}$ , analog supply voltage  $V_{DDM}$ . The digital core supply voltage  $V_{DDC}$  is derived from  $V_{DDP}$  by embedded voltage regulator of the CIC751. The following section defines the time and voltage constraints and relations between these two power supplies that have to be satisfied at power up and power down of the device.

**Figure 4-5** describes the requirements that the external power supplies  $V_{DDP}$ , and  $V_{DDM}$  must satisfy in order to provide the correct operation of the device.

The following rules should be applied in order to guarantee a stable power-up behavior:

- The active PORST should not be released before V<sub>DDP</sub> reached 2.7 V

- At any time it is not allowed that  $V_{DDM} > V_{DDP}$  if  $V_{DDP} < 2.1$  V.

The second rule can be violated (without operation lifetime reduction) if instead the following conditions are not violated:

- The external resistor on the Analog Inputs AIN0 to AIN15 has to be equal or greater than 2 K $\Omega$

- The accumulated time the second rule is violated is less than 4 % of the total product operation lifetime.

Figure 4-5 Power-up Sequence

## **Electrical Parameters**

## Table 4-9Ramp-up Times

| Case                           | Time        |

|--------------------------------|-------------|

| Ramp-up after a power-on event | max. 500 μs |

| Ramp-up after a reset event    | max. 450 μs |

Downloaded from Elcodis.com electronic components distributor

**CIC751**

## CONFIDENTIAL

#### 4.4.5 Timing Parameters

Peripheral timing parameters are not subject to production test. They are verified by design/characterization.

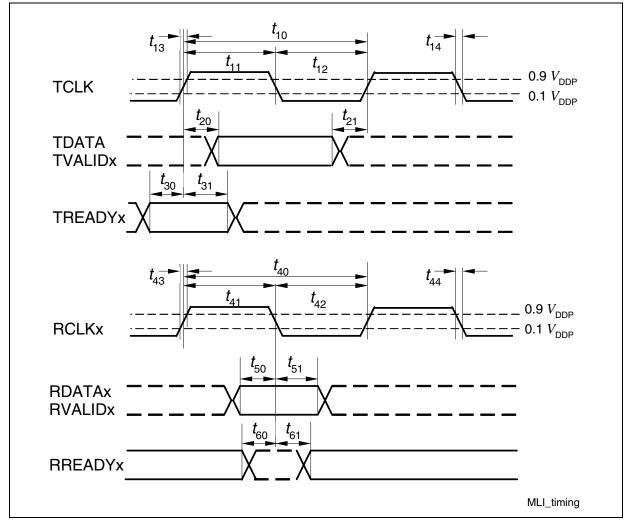

## 4.4.5.1 Micro Link Interface (MLI) Timing

The timing of the MLI handshake signals refer to the system clock frequency  $f_{SYS}$ . This frequency is the base for the generation of the MLI baud rate  $f_{TCLK}$ .

| Parameter                                            | Symbol          |                           | Values | Unit | Note /          |                                            |

|------------------------------------------------------|-----------------|---------------------------|--------|------|-----------------|--------------------------------------------|

|                                                      |                 | Min.                      | Тур.   | Max. |                 | Test Con dition                            |

| TCLK clock period                                    | t <sub>10</sub> | 2 * t <sub>SYS</sub>      | -      | -    | ns              | t <sub>SYS</sub> =<br>1 / f <sub>SYS</sub> |

| TCLK high period                                     | t <sub>11</sub> | 20%                       | 50%    | 80%  | t <sub>10</sub> |                                            |

| TCLK low period                                      | t <sub>12</sub> | 20%                       | 50%    | 80%  | t <sub>10</sub> |                                            |

| TCLK rise time                                       | t <sub>13</sub> | -                         | -      | 35%  | t <sub>10</sub> |                                            |

| TCLK fall time                                       | t <sub>14</sub> | -                         | -      | 35%  | t <sub>10</sub> |                                            |

| TDATA and TVALID setup time to TCLK raising edge     | t <sub>20</sub> | -                         | -      | 10%  | t <sub>10</sub> |                                            |

| TDATA and TVALID hold time to TCLK raising edge      | t <sub>21</sub> | -                         | -      | 10%  | t <sub>10</sub> |                                            |

| TREADY setup time to TCLK raising edge <sup>1)</sup> | t <sub>30</sub> | 10%                       | -      | -    | t <sub>10</sub> |                                            |

| TREADY hold time to TCLK raising edge <sup>2)</sup>  | t <sub>31</sub> | 10%                       | -      | -    | t <sub>10</sub> |                                            |

| RCLK clock period                                    | t <sub>40</sub> | < 2 *<br>t <sub>SYS</sub> | -      | -    | ns              | t <sub>SYS</sub> =<br>1 / f <sub>SYS</sub> |

| RCLK high period                                     | t <sub>41</sub> | 20%                       | 50%    | 80%  | t <sub>40</sub> |                                            |

| RCLK low period                                      | t <sub>42</sub> | 20%                       | 50%    | 80%  | t <sub>40</sub> |                                            |

| RCLK rise time                                       | t <sub>43</sub> | -                         | -      | 35%  | t <sub>40</sub> |                                            |

| RCLK fall time                                       | t <sub>44</sub> | _                         | -      | 35%  | t <sub>40</sub> |                                            |

| RDATA and RVALID setup time to RCLK falling edge     | t <sub>50</sub> | 10%                       | -      | -    | t <sub>40</sub> |                                            |

#### Table 4-10 MLI Timing ( $V_{SS} = 0 V; f_{MLI} \le 40 MHz$ $V_{DDP} = 3.13 \text{ to } 3.47 V; T_A = -40 \degree C \text{ to } +125 \degree C; C_I = 50 \text{ pF}$ )

Data Sheet

#### **Electrical Parameters**

# Table 4-10MLI Timing ( $V_{SS} = 0 V$ ; $f_{MLI} <= 40 MHz$ $V_{DDP} = 3.13$ to 3.47 V; $T_A = -40 °C$ to +125 °C; $C_L = 50 pF$ )

| Parameter                                            | Symbol          | , v  | Values | Unit | Note /          |                    |

|------------------------------------------------------|-----------------|------|--------|------|-----------------|--------------------|

|                                                      |                 | Min. | Тур.   | Max. |                 | Test Con<br>dition |

| RDATA and RVALID hold time to RCLK falling edge      | t <sub>51</sub> | 10%  | -      | -    | t <sub>40</sub> |                    |

| RREADY setup time to RCLK falling edge <sup>3)</sup> | t <sub>60</sub> | 50%  | -      | -    | t <sub>40</sub> |                    |

| RREADY hold time to RCLK falling edge <sup>4)</sup>  | t <sub>61</sub> | -    | -      | 50%  | t <sub>40</sub> |                    |

1) Referring to the TCLK edge when TVALID becomes 0 and the TCLK edge when the ready delay time elapses.

2) Referring to the TCLK edge when TVALID becomes 0 and the TCLK edge when the ready delay time elapses.

3) Referring to the former value at the RCLK edge when RVALID changes.

4) Referring to the new value at the RCLK edge when RVALID changes.

**CIC751**

## **Electrical Parameters**

Figure 4-6 MLI Timing

#### **Electrical Parameters**

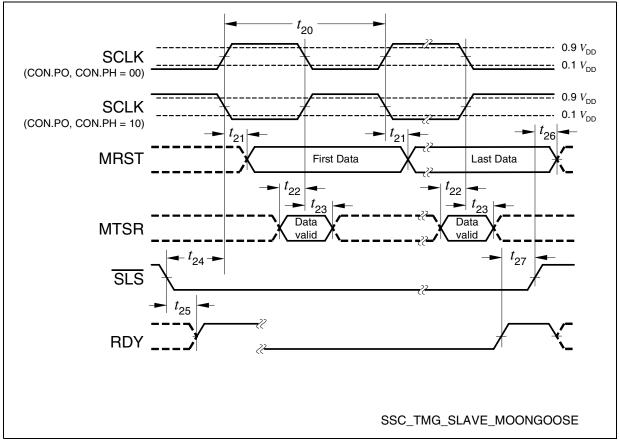

#### 4.4.6 Synchronous Serial Channel (SSC) Slave Mode Timing

The timing of the Synchronous Serial Channel in slave mode is defined below.

## Table 4-11SSC Timing (VSS = 0 V; $f_{SSC} \le 40$ MHzVDDP = 3.13 to 3.47 V (Class A); TA = -40 °C to +125 °C; CL = 50 pF)

| Parameter                                                                                                                 | Sy                           | V                | alues | Unit |    |                    |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|-------|------|----|--------------------|

|                                                                                                                           | mb<br>ol                     | Min.             | Тур.  | Max. |    | Test Co<br>ndition |

| SCLK clock period                                                                                                         | <i>t</i> <sub>20</sub><br>CC | T <sub>SSC</sub> |       | -    | ns |                    |

| MRST delay from SCLK<br>Rising/Falling Edge<br>from SCLK RE (CON.PO,CON.PH = 00)<br>from SCLK FE (CON.PO,CON.PH = 10)     | t <sub>21</sub><br>CC        | 4                |       | 12   | ns |                    |

| MRST hold from SLS Rising Edge                                                                                            | <i>t</i> <sub>26</sub><br>CC | -                |       | 14   | ns |                    |

| MTSR setup to SCLK<br>Rising/Falling Edge<br>to SCLK RE (CON.PO,CON.PH = 00)<br>to SCLK FE (CON.PO,CON.PH = 10)           | <i>t</i> <sub>22</sub><br>SR | 0                |       | _    | ns |                    |

| MTSR hold from SCLK<br>Rising/Falling Edge<br>from SCLK RE (CON.PO,CON.PH = 00)<br>from SCLK FE (CON.PO,CON.PH = 10)      | <i>t</i> <sub>23</sub><br>SR | $2 + T_{SSC}$    |       | _    | ns |                    |

| SLSI lead delay from SCLK<br>Rising/Falling Edge<br>from SCLK RE (CON.PO,CON.PH = 00)<br>from SCLK FE (CON.PO,CON.PH =10) | <i>t</i> <sub>24</sub><br>SR | 6                |       | _    | ns | 1)                 |

| RDY lead delay to SLS RE                                                                                                  | <i>t</i> <sub>25</sub><br>CC | 13               |       | 15   | ns |                    |

| SLS hold from RDY RE                                                                                                      | <i>t</i> <sub>27</sub><br>SR | 4                |       | -    | ns |                    |

1) This is only valid if SSC move engine is idle (RDY = 1).

**Electrical Parameters**

Figure 4-7 SSC Slave Mode Timing

#### **Electrical Parameters**

## 4.5 Package and Reliability

This chapter defines the parameters related to the Package and Reliability of the device.

## 4.5.1 Packaging

The parameters of the package of the CIC751 are defined below.

| Table 4-12 | Package Parameters | (P/PG-TSSOP-38) |

|------------|--------------------|-----------------|

|------------|--------------------|-----------------|

| Parameter          | Symbol            | Limit Values |      | Limit Values |              | Limit Values |  | Unit | Notes |

|--------------------|-------------------|--------------|------|--------------|--------------|--------------|--|------|-------|

|                    |                   | Min.         | Max. |              |              |              |  |      |       |

| Power dissipation  | P <sub>DISS</sub> | —            | tbd. | W            | -            |              |  |      |       |

| Thermal resistance | R <sub>THJA</sub> | _            | 59   | K/W          | Chip-Ambient |              |  |      |       |

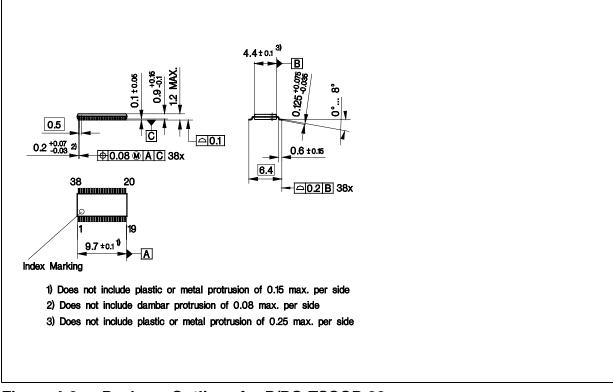

## 4.5.2 Package Outlines

The physical characteristics of the package are described below.

Figure 4-8 Package Outlines for P/PG-TSSOP-38

#### **Electrical Parameters**

#### 4.5.3 Quality Declarations

The following chapter defines some quality parameters of CIC751.

| Table 4-13 | <b>Quality Parameters</b> |

|------------|---------------------------|

|------------|---------------------------|

| Parameter                                                            | Symbol           | Limit Values |                     | Unit  | Notes                                                                                                                 |

|----------------------------------------------------------------------|------------------|--------------|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------|

|                                                                      |                  | Min.         | Max.                |       |                                                                                                                       |

| Operation Lifetime                                                   | t <sub>OP</sub>  | -            | 18000               | hours | at average weighted<br>junction temperature<br>$T_J = 116^{\circ}C$ (ambient<br>temperature<br>$T_A = 102^{\circ}C$ ) |

|                                                                      |                  | _            | 24000 <sup>1)</sup> | hours | at average weighted<br>junction temperature<br>$T_J = 106^{\circ}C$ (ambient<br>temperature<br>$T_A = 92^{\circ}C$ )  |

| Life Expectancy                                                      | t <sub>B</sub>   | 20           | -                   | years |                                                                                                                       |

| ESD susceptibility<br>according to Human<br>Body Model (HBM)         | V <sub>HBM</sub> | -            | 2000                | V     | Conforming to<br>EIA/JESD22-A114-B                                                                                    |

| ESD susceptibility<br>according to<br>Socketed Device<br>Model (SDM) | V <sub>SDM</sub> | -            | 500                 | V     | Conforming to ESDA<br>Std DS5.3-1993                                                                                  |

| Moisture Sensitivity<br>Level (MSL)                                  | -                | -            | 3                   | -     | Conforming to Jedec<br>J-STD-020C for<br>240°C                                                                        |

1) One example of a detailed temperature profile is: 1200 hours at  $T_J = 140 \text{ °C} (T_A = 125 \text{ °C})$ 3600 hours at  $T_J = 115 \text{ °C} (T_A = 100 \text{ °C})$ 7200 hours at  $T_J = 100 \text{ °C} (T_A = 85 \text{ °C})$ 12000 hours at  $T_J = 90 \text{ °C} (T_A = 75 \text{ °C})$

Note: Information about soldering can be found on the "package" information page under: http://www.infineon.com/products.

www.infineon.com

Published by Infineon Technologies AG