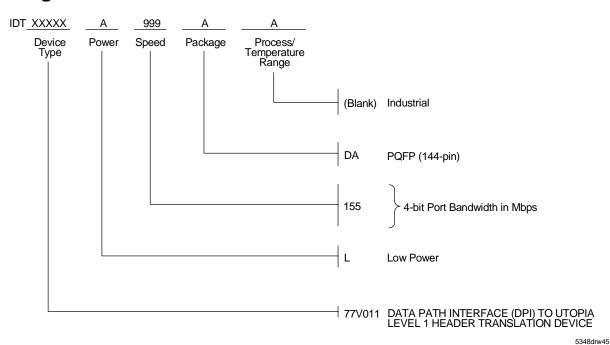

Data Path Interface (DPI) to Utopia Level 2 Translation Device IDT77V011

#### Features

- Single chip interface between multiple UTOPIA PHYs and a single Data Path Interface (DPI).

- Ideal for xDSL DSLAM and 25Mbps switching applications.

- Supports ATM Forum UTOPIA Level 2 interface in both 8-bit and 16-bit modes.

- \* Supports UTOPIA Level 2 Cell Level Handshake.

- \* Supports up to 31 PHYs on the UTOPIA Level 2 interface.

- Supports either 4-bit or 8-bit DPI interface.

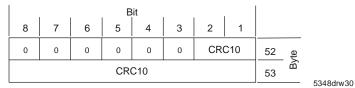

- Supports cell sizes from 52 to 56 bytes on the DPI interface.

- Supports DPI operation up to 50MHz.

- Either Utility Bus or Parallel Manager Management interface for configuring and reading status of PHY registers.

- In-Stream<sup>™</sup> (In-band) programming for configuration of device and management interface communications.

- TAG Routing for flexibility in routing cells.

- Single +3.3V ± 0.3V power supply required.

- Inputs are +5.0V tolerant.

### **Description**

**Block Diagram**

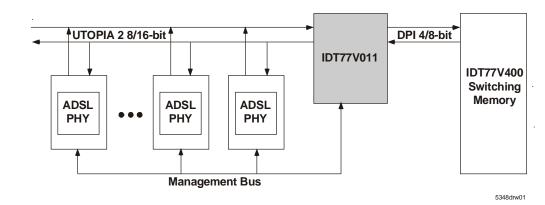

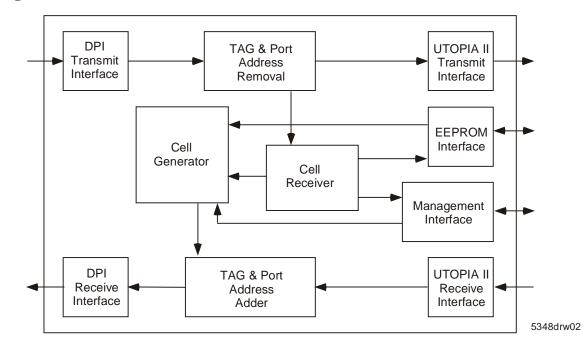

The IDT77V011provides the interface translation between a 4 or 8-bit Data Path Interface (DPI) and an 8 or 16-bit UTOPIA Level 2 interface. DPI offers a reduced device pin count and gives the IDT77V400 Switching Memory a high degree of port configuration flexibility.

By providing a smooth translation to the UTOPIA Level 2 multi-PHY interface, the IDT77V011 offers the opportunity to connect up to 31 PHY ports to a single 155Mbps port of the IDT77V400 Switching Memory.

The IDT77V011 can also provide both transmit and receive TAG Routing, with each direction being individually programmed. In the receive direction up to four bytes can be added to the cell. In the transmit direction up to four bytes can be removed from the cell. This makes the IDT77V011, when combined with the IDT77V400, an ideal component for DSLAM and 25Mbps applications where the user would like to implement OC-3 bandwidth of a single IDT77V400 port to a number of lower bandwidth ports.

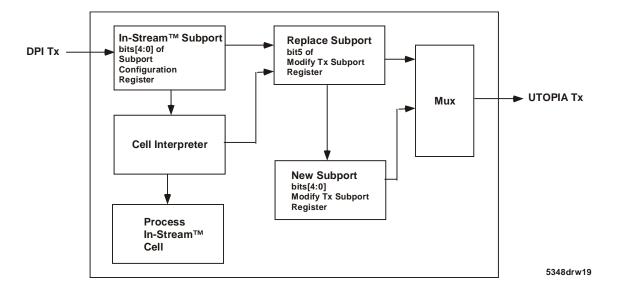

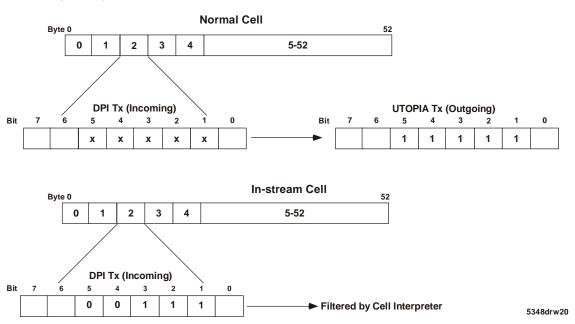

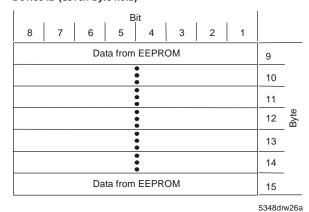

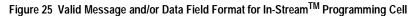

The 77V011 utilizes In-Stream<sup>™</sup> programming for its device configuration options. The cells are received on the DPI transmit interface, identified and sent to the internal cell interpreter for decoding and execution. In-Stream<sup>™</sup> programming cells are transmitted based on a round-robin scheduler, which provides equal priority for each of the subports and the cell generator. This methodology is also used to communicate and configure the PHYs that are connected to the IDT77V011.

Other features include an EEPROM that holds information for initialization and Discovery/Identify cells, and a Management interface to access the PHY devices.

Figure 1 Typical IDT77011 ADSL DSLAM Application with the IDTV400 Switching Memory

# **Block Diagram**

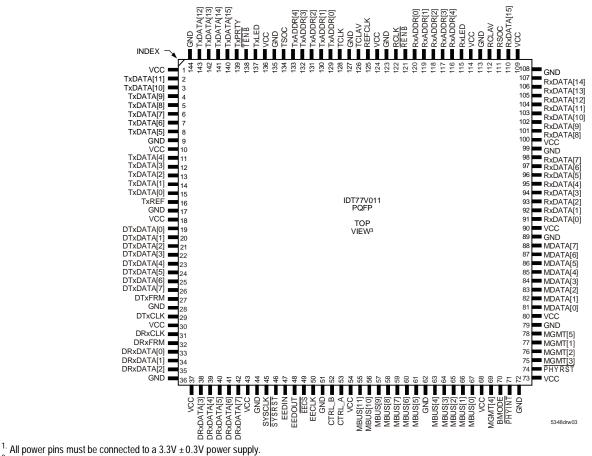

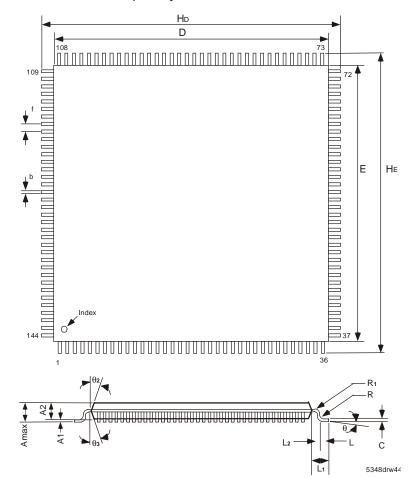

## **Pin Configuration**

<sup>2</sup> All GND pins must be connected to ground supply.

<sup>3.</sup> This text does not indicate orientation of the actual part-marking.

# **Pin Description Table**

| Pin Name    | Pin<br>Number | Input/<br>Output | Mode   | Description                                                                                                           |  |

|-------------|---------------|------------------|--------|-----------------------------------------------------------------------------------------------------------------------|--|

| DTxDATA [0] | 19            | 1                | Normal | 4-bit or 8-bit input data bus used to transfer data from a DPI device. When in 4-bit mode use DTxDATA [3:0]           |  |

| DTxDATA [1] | 20            | I                | Normal | 4-bit or 8-bit input data bus used to transfer data from a DPI device. When in 4-bit mode use DTxDATA [3:0]           |  |

| DTxDATA [2] | 21            | I                | Normal | 4-bit or 8-bit input data bus used to transfer data from a DPI device. When in 4-bit mode use DTxDA                   |  |

| DTxDATA [3] | 22            | I                | Normal | 4-bit or 8-bit input data bus used to transfer data from a DPI device. When in 4-bit mode use DTxDATA [3:0]           |  |

| DTxDATA [4] | 23            | I                | Normal | 4-bit or 8-bit input data bus used to transfer data from a DPI device. When in 4-bit mode use DTxDATA [3:0]           |  |

| DTxDATA [5] | 24            | I                | Normal | 4-bit or 8-bit input data bus used to transfer data from a DPI device. When in 4-bit mode use DTxDATA [3:0]           |  |

| DTxDATA [6] | 25            | I                | Normal | 4-bit or 8-bit input data bus used to transfer data from a DPI device. When in 4-bit mode use DTxDATA [3:0]           |  |

| DTxDATA [7] | 26            | I                | Normal | 4-bit or 8-bit input data bus used to transfer data from a DPI device. When in 4-bit mode use DTxDATA [3:0]           |  |

| DTxFRM      | 27            | I                | Normal | DPI Transmit Start of Frame Marker.                                                                                   |  |

| DTxCLK      | 29            | 0                | Normal | Transmit DPI Clock.                                                                                                   |  |

| DRxDATA [0] | 33            | 0                | Normal | 4-bit or 8-bit output data bus used to transfer data to a DPI device. When in 4-bit mode use DRxDATA [3:0].           |  |

| DRxDATA [1] | 34            | 0                | Normal | 4-bit or 8-bit output data bus used to transfer data to a DPI device. When in 4-bit mode use DRxDATA [3:0].           |  |

| DRxDATA [2] | 35            | 0                | Normal | 4-bit or 8-bit output data bus used to transfer data to a DPI device. When in 4-bit mode use DRxDATA [3:0].           |  |

| DRxDATA [3] | 38            | 0                | Normal | 4-bit or 8-bit output data bus used to transfer data to a DPI device. When in 4-bit mode use DRxDATA [3:0].           |  |

| DRxDATA [4] | 39            | 0                | Normal | 4-bit or 8-bit output data bus used to transfer data to a DPI device. When in 4-bit mode use DRxDATA [3:0].           |  |

| DRxDATA [5] | 40            | 0                | Normal | 4-bit or 8-bit output data bus used to transfer data to a DPI device. When in 4-bit mode use DRxDATA [3:0].           |  |

| DRxDATA [6] | 41            | 0                | Normal | 4-bit or 8-bit output data bus used to transfer data to a DPI device. When in 4-bit mode use DRxDATA [3:0].           |  |

| DRxDATA [7] | 42            | 0                | Normal | 4-bit or 8-bit output data bus used to transfer data to a DPI device. When in 4-bit mode use DRxDATA [3:0].           |  |

| DRxFRM      | 32            | 0                | Normal | DPI Receive Start of Frame Marker.                                                                                    |  |

| DRxCLK      | 31            | I/O              | Normal | Receive DPI Clock.                                                                                                    |  |

| RxDATA [0]  | 91            | I                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [1]  | 92            | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [2]  | 93            | I                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [3]  | 94            | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [4]  | 95            | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [5]  | 96            | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [6]  | 97            | I                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [7]  | 98            | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [8]  | 101           | I                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| RxDATA [9]  | 102           | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |

| Pin Name    | Pin<br>Number | Input/<br>Output | Mode   | Description                                                                                                           |  |  |  |

|-------------|---------------|------------------|--------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| RxDATA [10] | 103           | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |  |  |

| RxDATA [11] | 104           | 1                | Normal | B-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode us RxDATA [7:0].  |  |  |  |

| RxDATA [12] | 105           | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |  |  |

| RxDATA [13] | 106           | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |  |  |

| RxDATA [14] | 107           | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |  |  |

| RxDATA [15] | 110           | 1                | Normal | 8-bit or 16-bit UTOPIA 2 input data bus used to transfer data from a PHY device. When in 8-bit mode use RxDATA [7:0]. |  |  |  |

| RSOC        | 111           | 1                | Normal | UTOPIA 2 Receive Start of Cell marker.                                                                                |  |  |  |

| RCLAV       | 112           | 1                | Normal | UTOPIA 2 Receive Cell Available.                                                                                      |  |  |  |

| RENB        | 121           | 0                | Normal | UTOPIA 2 Receive Enable.                                                                                              |  |  |  |

| RxADDR [0]  | 120           | 0                | Normal | UTOPIA 2 Receive Address Bus.                                                                                         |  |  |  |

| RxADDR [1]  | 119           | 0                | Normal | UTOPIA 2 Receive Address Bus.                                                                                         |  |  |  |

| RxADDR [2]  | 118           | 0                | Normal | UTOPIA 2 Receive Address Bus.                                                                                         |  |  |  |

| RxADDR [3]  | 117           | 0                | Normal | UTOPIA 2 Receive Address Bus.                                                                                         |  |  |  |

| RxADDR [4]  | 116           | 0                | Normal | UTOPIA 2 Receive Address Bus.                                                                                         |  |  |  |

| RxLED       | 115           | 0                | Normal | UTOPIA 2 Receive LED.                                                                                                 |  |  |  |

| RCLK        | 122           | 0                | Normal | UTOPIA 2 Receive Clock.                                                                                               |  |  |  |

| TxDATA [0]  | 15            | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [1]  | 14            | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [2]  | 13            | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [3]  | 12            | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [4]  | 11            | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [5]  | 8             | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [6]  | 7             | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [7]  | 6             | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [8]  | 5             | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [9]  | 4             | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| TxDATA [10] | 3             | 0                | Normal | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].  |  |  |  |

| Pin Name                                         | Pin<br>Number | Input/<br>Output                     | Mode                                                                               | Description                                                                                                                                                                                                                       |  |  |  |

|--------------------------------------------------|---------------|--------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TxDATA [11]                                      | 2             | 0                                    | Normal                                                                             | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].                                                                                                              |  |  |  |

| TxDATA [12]                                      | 143           | 0                                    | Normal                                                                             | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].                                                                                                              |  |  |  |

| TxDATA [13]                                      | 142           | 0                                    | Normal                                                                             | B-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode us<br>xDATA [7:0].                                                                                                             |  |  |  |

| TxDATA [14]                                      | 141           | 0                                    | Normal                                                                             | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].                                                                                                              |  |  |  |

| TxDATA [15]                                      | 140           | 0                                    | Normal                                                                             | 8-bit or 16-bit UTOPIA 2 output data bus used to transfer data to a PHY device. When in 8-bit mode use TxDATA [7:0].                                                                                                              |  |  |  |

| TSOC                                             | 134           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit Start of Cell marker.                                                                                                                                                                                           |  |  |  |

| TCLAV                                            | 126           | I                                    | Normal                                                                             | UTOPIA 2 Transmit Cell Available.                                                                                                                                                                                                 |  |  |  |

| TENB                                             | 138           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit Enable.                                                                                                                                                                                                         |  |  |  |

| TxADDR[0]                                        | 129           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit Address Bus [LSB].                                                                                                                                                                                              |  |  |  |

|                                                  |               | I                                    | Reset                                                                              | Subport Byte Location. Indicates what byte the Tx and Rx Subport Address is located in [LSB].                                                                                                                                     |  |  |  |

| TxADDR[1]                                        | 130           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit Address Bus [LSB+1].                                                                                                                                                                                            |  |  |  |

|                                                  |               | I                                    | Reset                                                                              | Subport Byte Location. Indicates what byte the Tx and Rx Subport Address is located in [LSB+1].                                                                                                                                   |  |  |  |

| TxADDR[2]                                        | 131           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit Address Bus [LSB+2].                                                                                                                                                                                            |  |  |  |

|                                                  |               | I                                    | Reset                                                                              | Subport Byte Location. Indicates what byte the Tx and Rx Subport Address is located in [MSB].                                                                                                                                     |  |  |  |

| TxADDR[3]                                        | 132           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit Address Bus [LSB+3].                                                                                                                                                                                            |  |  |  |

|                                                  |               | I                                    | Reset                                                                              | Initialize from EEPROM. Selects whether five bytes of EEPROM are to be written to In-Stream <sup>™</sup> Cell Header and In-Stream <sup>™</sup> Subport. "0" do not write five byte value, "1" write five byte value from EEPROM. |  |  |  |

| TxADDR[4]                                        | 133           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit Address Bus [MSB].                                                                                                                                                                                              |  |  |  |

| TxLED                                            | 137           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit LED.                                                                                                                                                                                                            |  |  |  |

| TCLK                                             | 128           | 0                                    | Normal                                                                             | UTOPIA 2 Transmit Clock.                                                                                                                                                                                                          |  |  |  |

| TxPRTY                                           | 139           | 0                                    | Normal                                                                             | Parity for DTxDATA [15:0].                                                                                                                                                                                                        |  |  |  |

| REFCLK                                           | 125           | 1                                    | Normal                                                                             | 8 KHz reference clock used to generate TxREF.                                                                                                                                                                                     |  |  |  |

| TxREF                                            | 16            | 0                                    | Normal                                                                             | 8KHz reference clock used by PHY.                                                                                                                                                                                                 |  |  |  |

| EECLK                                            | 50            | 0                                    | Normal                                                                             | EEPROM Clock.                                                                                                                                                                                                                     |  |  |  |

| EECS                                             | 49            | 0                                    | Normal                                                                             | EEPROM Chip Select.                                                                                                                                                                                                               |  |  |  |

| EEDIN                                            | 47            | 1                                    | Normal                                                                             | Serial Input from the EEPROM.                                                                                                                                                                                                     |  |  |  |

| EEDOUT                                           | 48            | 0                                    | Normal                                                                             | Serial Output to the EEPROM.                                                                                                                                                                                                      |  |  |  |

| BMODE                                            | 70            | 1                                    | Normal                                                                             | Bus Mode. Selects Motorola or Intel bus mode. "0" selects Motorola, "1" selects Intel.                                                                                                                                            |  |  |  |

| MBUS[0]                                          | 67            | 0                                    | UTOPIA 2                                                                           | Address Bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                                                                                                        |  |  |  |

| Utility Bus Utility bus PHY chip select (CS[1]). |               | Utility bus PHY chip select (CS[1]). |                                                                                    |                                                                                                                                                                                                                                   |  |  |  |

|                                                  |               | 1                                    | Reset TxSIZE[0] - Number of bytes to remove from cell in transmit direction (LSB). |                                                                                                                                                                                                                                   |  |  |  |

| MBUS[1]                                          | 66            | 0                                    | UTOPIA 2                                                                           | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                                                                                                        |  |  |  |

|                                                  |               |                                      | Utility Bus Utility bus PHY chip select (CS[2]).                                   |                                                                                                                                                                                                                                   |  |  |  |

|                                                  |               | 1                                    | Reset                                                                              | TxSIZE[1] - number of bytes to remove from cell in transmit direction (LSB + 1).                                                                                                                                                  |  |  |  |

| Pin Name   | Pin<br>Number | Input/<br>Output | Mode        | Description                                                                                                                                         |  |  |  |

|------------|---------------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MBUS[2] 65 |               | 0                | UTOPIA 2    | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                          |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[3]).                                                                                                                |  |  |  |

|            |               | I                | Reset       | TxSIZE[2] - number of bytes to remove from cell in transmit direction (MSB).                                                                        |  |  |  |

| MBUS[3]    | BUS[3] 64 O   |                  |             | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                          |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[4]).                                                                                                                |  |  |  |

|            |               | I                | Reset       | TxLOC - Location of Tx TAG in cell. "0" TAG located at beginning of cell, "1" TAG located at end of cell.                                           |  |  |  |

| MBUS[4]    | 63            | 0                | UTOPIA 2    | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                          |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[5]).                                                                                                                |  |  |  |

|            |               | I                | Reset       | TxHEC - Add HEC placeholder. "0" do not add placeholder, "1" add placeholder.                                                                       |  |  |  |

| MBUS[5]    | 61            | 0                | UTOPIA 2    | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                          |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[6]).                                                                                                                |  |  |  |

|            |               | I                | Reset       | RxSIZE[0] - Number of bytes to add to cell in the receive direction (LSB).                                                                          |  |  |  |

| MBUS[6]    | 60            | 0                | UTOPIA 2    | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                          |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[7]).                                                                                                                |  |  |  |

|            |               | I                | Reset       | RxSIZE[1] - Number of bytes to add to cell in the receive direction (LSB + 1).                                                                      |  |  |  |

| MBUS[7]    | 59            | 0                | UTOPIA 2    | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                          |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[8]).                                                                                                                |  |  |  |

|            |               | I                | Reset       | RxSIZE[2] - Number of bytes to add to cell in the receive direction (MSB).                                                                          |  |  |  |

| MBUS[8]    | 58            | 0                | UTOPIA 2    | 2 Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                        |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[9]).                                                                                                                |  |  |  |

|            |               | I                | Reset       | RxLOC - Location of TAG in cell in the receive direction. RxLOC = "0" TAG located at beginning of cell,<br>TxLOC = "1" TAG located at end of cell.  |  |  |  |

| MBUS[9]    | 57            | 0                | UTOPIA 2    | Address bus (LSB+9).                                                                                                                                |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[10]).                                                                                                               |  |  |  |

|            |               | I                | Reset       | RxHEC - Remove HEC from cell. "0" do not remove HEC, "1" remove HEC.                                                                                |  |  |  |

| MBUS[10]   | 56            | 0                | UTOPIA 2    | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                          |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[11]).                                                                                                               |  |  |  |

|            |               | I                | Reset       | DPI Bus Size. Indicates whether DPI transmit and receive bus is 4-bits or 8-bits wide. "0" 4-bit DPI bus, "1" 8-bit DPI bus.                        |  |  |  |

| MBUS[11]   | 55            | 0                | UTOPIA 2    | Address bus. Upper 64 bytes used for 32 address pointers describing PHY's.                                                                          |  |  |  |

|            |               |                  | Utility Bus | Utility bus PHY chip select (CS[12]).                                                                                                               |  |  |  |

|            |               | I                | Reset       | UTOPIA Bus Size. Indicates whether the UTOPIA transmit and receive data bus is 8-bits or 16-bits wide. "0' 8-bit UTOPIA bus, "1" 16-bit UTOPIA bus. |  |  |  |

| MDATA[0]   | 81            | I/O              | UTOPIA 2    | Management interface data bus [LSB].                                                                                                                |  |  |  |

|            |               |                  | Utility Bus | Utility Bus address and data bus [LSB].                                                                                                             |  |  |  |

| MDATA[1]   | 82            | I/O              | UTOPIA 2    | Management interface data bus [LSB+1].                                                                                                              |  |  |  |

|            |               |                  | Utility Bus | Utility Bus address and data bus [LSB+1].                                                                                                           |  |  |  |

| MDATA[2]   | 83            | I/O              | UTOPIA 2    | Management interface data bus [LSB+2].                                                                                                              |  |  |  |

|            |               |                  | Utility Bus | Utility Bus address and data bus [LSB+2].                                                                                                           |  |  |  |

| Pin Name | Pin<br>Number                                                           | Input/<br>Output | Mode        | Description                                                                                                               |

|----------|-------------------------------------------------------------------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|

| MDATA[3] | 84                                                                      | I/O              | UTOPIA 2    | Management interface data bus [LSB+3].                                                                                    |

|          |                                                                         |                  | Utility Bus | Utility Bus address and data bus [LSB+3].                                                                                 |

| MDATA[4] | 85                                                                      | I/O              | UTOPIA 2    | Management interface data bus [LSB+4].                                                                                    |

|          |                                                                         |                  | Utility Bus | Utility Bus address and data bus [LSB+4].                                                                                 |

| MDATA[5] | 86                                                                      | I/O              | UTOPIA 2    | Management interface data bus [LSB+5].                                                                                    |

|          |                                                                         |                  | Utility Bus | Utility Bus address and data bus [LSB+5].                                                                                 |

| MDATA[6] | 87                                                                      | I/O              | UTOPIA 2    | Management interface data bus [LSB+6].                                                                                    |

|          |                                                                         |                  | Utility Bus | Utility Bus address and data bus [LSB+6].                                                                                 |

| MDATA[7] | 88                                                                      | I/O              | UTOPIA 2    | Management interface data bus [MSB].                                                                                      |

|          |                                                                         |                  | Utility Bus | Utility Bus address and data bus [MSB].                                                                                   |

| MGMT[1]  | 77                                                                      | 0                | UTOPIA 2    | Validates Read or Write operation on Management interface (SEL).                                                          |

|          |                                                                         |                  | Utility Bus | Utility bus PHY Chip Select (CS[0]).                                                                                      |

| MGMT[2]  | 76                                                                      | 0                | UTOPIA II   | Management interface Read or Data Strobe (RD/DS).                                                                         |

|          |                                                                         |                  | Utility Bus | Utility bus read (RD).                                                                                                    |

|          |                                                                         | 1                | Reset       | MMODE - Selects what type of management mode interface to use. "0" selects Utility Bus style, "1" selects UTOPIA 2 style. |

| MGMT[3]  | 75                                                                      | 0                | UTOPIA 2    | Management interface Write or Read/Write (WR/RW).                                                                         |

|          |                                                                         |                  | Utility Bus | Utility bus Write (WR).                                                                                                   |

|          |                                                                         | I                | Reset       | MGMT[3] - Selects clock direction for DRxCLK. "0" DRxCLK is an output, "1" DRxCLK is an input.                            |

| MGMT[4]  | 69                                                                      | I                | UTOPIA 2    | Management interface Ready or Data Acknowledge (RDY/DTACK).                                                               |

|          |                                                                         |                  | Utility Bus | No functionality.                                                                                                         |

| MGMT[5]  | 78                                                                      | 0                | UTOPIA II   | No functionality.                                                                                                         |

|          |                                                                         |                  | Utility Bus | Utility Bus Address Latch Enable (ALE).                                                                                   |

| PHYRST   | 74                                                                      | 0                | Normal      | PHY Reset. Resets the PHY device attached to the 77V011.                                                                  |

| PHYINT   | 71                                                                      | I                | Normal      | PHY Interrupt. Phy layer interrupt with open drain active low output.                                                     |

| SYSRST   | 46                                                                      | I                | Normal      | System Reset. Resets the 77V011 and the PHY device(s) attached to it.                                                     |

| SYSCLK   | 45                                                                      | 1                | Normal      | System Clock.                                                                                                             |

| CTRL_A   | 53                                                                      | 0                | Normal      | Control A for system engineering usage. This signal is Low after reset.                                                   |

| CTRL_B   | 52                                                                      | 0                | Normal      | Control B for system engineering usage. This signal is Low after reset.                                                   |

| Vcc      | 1,10,18,30,<br>37,43,54,68,<br>73,80,90,100,<br>109,114,124,<br>136     | Power            | Normal      | 3.3V Power supply pins.                                                                                                   |

| GND      | 9,17,28,36,<br>44,51,62,72,<br>79,89,99,108,<br>113,123,127,<br>135,144 | Ground           | Normal      | Ground pins.                                                                                                              |

# **Absolute Maximum Ratings**

| Symbol | Parameter                   | Min     | Мах  | Unit |

|--------|-----------------------------|---------|------|------|

| Vcc    | 3.3V Digital Supply Voltage | GND-0.3 | 3.6  | V    |

| VIN    | Digital Input Voltage       | GND-0.3 | 5.50 | V    |

| Vout   | Digital Output Voltage      | GND-0.3 | VCC  | V    |

| GND    | Digital Ground Voltage      | 0       | 0    | V    |

| Ιουτ   | Output Current              | —       | 12.0 | mA   |

| Tstg   | Storage Temperature         | -55     | 140  | C°   |

# **Recommended Operating Conditions**

| Symbol | Parameter                        | Min | Max  | Unit |

|--------|----------------------------------|-----|------|------|

| Vcc    | 3.3V Digital Supply Voltage      | 3.0 | 3.6  | V    |

| Vin    | TTL Input Voltage                | GND | 5.50 | V    |

| Та     | Industrial Operating Temperature | -40 | +85  | °C   |

| titr   | Input TTL rise time              | _   | 2    | ns   |

| titf   | Input TTL fall time              | _   | 2    | ns   |

| Vih    | TTL Input High Voltage           | 2.0 | —    | V    |

| VIL    | TTL Input Low Voltage            | —   | 0.8  | V    |

# **DC Electrical Characteristics**

| Symbol | Parameter               | Condition                   | Min | Max | Unit |

|--------|-------------------------|-----------------------------|-----|-----|------|

| lu     | Input Leakage Current   | VCC = 3.3V, VIN = 0V to VCC | 10  | 10  | μA   |

| Ilo    | Output Leakage Current  | VOUT = 0V to VCC            | 10  | 10  | μA   |

| Voн    | TTL Output High Voltage | High Voltage Iон = -4mA     |     | -   | V    |

| Vol    | TTL Output Low Voltage  | IOL = +4mA                  | -   | 0.4 | V    |

| lcc    | Power Supply Current    | 155.52 Mbps                 | —   | 110 | mA   |

# Capacitance

| Symbol | Parameter                  | er Condition            |   | Тур | Max | Unit |

|--------|----------------------------|-------------------------|---|-----|-----|------|

| Cin    | Input Capacitance          | All Inputs              | — | 4   | 1   | pF   |

| Соит   | Output Capacitance         | All Outputs             | - | 6   | _   | pF   |

| CBID   | Bi-Directional Capacitance | All Bi-directional Pins | - | 10  | _   | pF   |

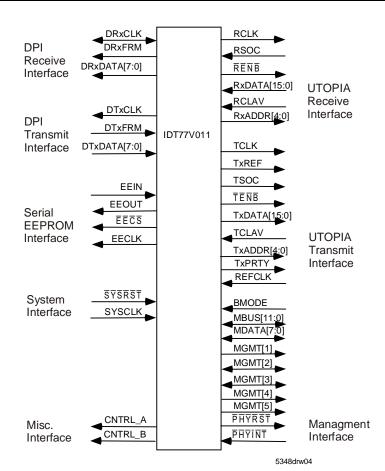

#### **Device Interface**

The 77V011 uses a UTOPIA level 2 interface to receive and transmit ATM cells to and from the PHY device. It is a master UTOPIA interface and can operate with either an 8-bit or 16-bit data bus. Cell level handshake is used to transfer cells over the UTOPIA interface, byte level handshake is not supported.

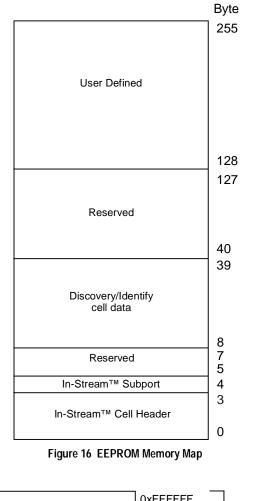

The Data Path Interface (DPI) can be used with a 4-bit or 8-bit data bus. The DPI receive interface can be programmed to operate with the clock as an input or output to accommodate either the IDT SWITCHStAR or a normal mode DPI device. The EEPROM holds information for initialization and Discovery/Identify cells. The EEPROM is an optional device and does not need to be implemented.

The Management interface contains the control pins used to access the internal PHY registers during normal operation, and to program the pin configurable registers at reset.

The Misc. Interface contains two output test pins that can be controlled through the registers.

Figure 2 77V011 Interfaces

| Clock Domain     | DPI and UTOPIA 2 Bus Widths |                              |                             |                              |  |  |  |  |

|------------------|-----------------------------|------------------------------|-----------------------------|------------------------------|--|--|--|--|

|                  | 4-bit DPI<br>8-bit UTOPIA 2 | 4-bit DPI<br>16-bit UTOPIA 2 | 8-bit DPI<br>8-bit UTOPIA 2 | 8-bit DPI<br>16-bit UTOPIA 2 |  |  |  |  |

| DRxCLK<br>DTxCLK | SYSCLK                      | SYSCLK                       | SYSCLK                      | SYSCLK                       |  |  |  |  |

| RCLK<br>TCLK     | SYSCLK/2                    | SYSCLK/4                     | SYSCLK                      | SYSCLK/2                     |  |  |  |  |

Table 1 Clock Relationship and Frequency

#### **Clock Relationships**

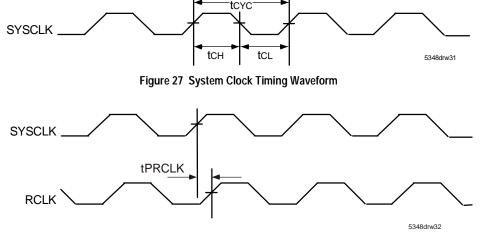

All clocks within the 77V011 are derived from the System Clock (SYSCLK). The frequency at which each output clock operates is dependent on the SYSCLK frequency and on the width of the DPI and UTOPIA 2 interfaces. See Clock Relationship Table for the relationship between SYSCLK and the output clocks.

When DRxCLK is configured as an input it is totally asynchronous to SYSCLK. The DRxCLK clock domain within the 77V011 will run at the same frequency as the DRxCLK pin.

### UTOPIA 2 Receive Interface Operation

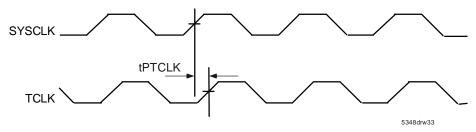

The 77V011 offers a fully compliant UTOPIA Level 2 receive interface, as specified by the UTOPIA Level 2 specification. The interface is a UTOPIA master and will operate with either an 8-bit or 16-bit Input Data Bus (RxDATA[15:0]). UTOPIA cell level handshake is used to receive ATM cells from the PHY device. The other signals associated with this interface are Receive Start of Cell (RSOC), Receive Enable (RENB), Receive Cell Available (RCLAV), Receive Clock (RCLK), Receive Address Bus (RxADDR[4:0]) and Receive LED (RxLED).

The RxADDR[4:0] bus is fully UTOPIA Level 2 compliant and operates according to the MPHY Cell-Level Handshake with one RCLAV, as described in the UTOPIA Level 2 specification.

RCLK is a continuous clock, whose relationship to SYSCLK is defined in the Clock Relationship and Frequency Table.

RxLED indicates if there is activity on the RxDATA[15:0] bus. This signal asserts high when a cell is transferred over the bus and will stay high for 2<sup>22</sup> RCLK cycles. AT 40MHz this is approximately 0.1seconds.

UTOPIA transmit and receive bus size is selected at reset with the MBUS[11] signal. Setting MBUS[11] to a zero will select a 8-bit bus, while setting MBUS[11] to a one will select a 16-bit bus. The value of MBUS[11], at reset, is stored in the UTOPIA 2 Size bit of the Mode Select register. See the UTOPIA 2 Receive Register Table for register description.

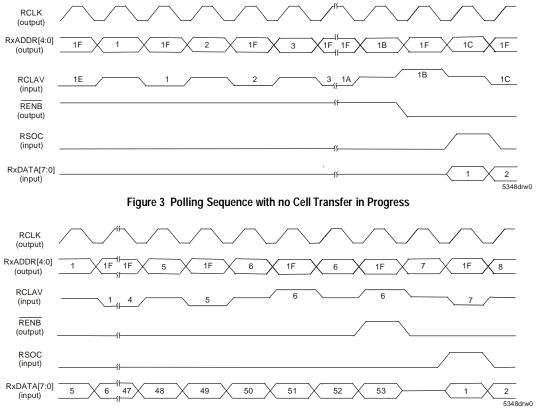

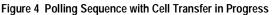

Polling on the UTOPIA 2 receive bus is done in a round robin fashion. The Max Subports field of the Configuration 2 register determines the upper boundary of the polled addresses. The default value of the Max Subports field is 0x1E, which is also the maximum valid PHY address. The user should not program a value of 0x1F, as this is defined as a Null PHY port by the UTOPIA 2 specification.

When there is no cell transfer in progress, no PHY port is selected, the polling sequence is to output the Null PHY subport address (0x1F) on one RCLK cycle and then output a valid PHY subport address on the next RCLK cycle. This sequence is repeated starting at PHY port address 0x00 and ending at the value specified in Max Subports field. The 77v011 will wrap back to address 0x00 once it has polled the Max Subports address. A PHY device is selected when a PHY responds to its subport address by asserting RCLAV high. RENB will assert on the same RCLK cycle that RCLAV is asserted, assuming there is no valid cell transfer in progress. The 77V011 will resume polling starting with the

next sequential subport address once the cell transfer to a selected PHY port begins.

When a PHY port responds with a high RCLAV during a cell transfer the 77V011 will continue to place the responding PHY subport address on the RxADDR[4:0] bus until the current cell transfer has ended and the responding PHY is given control of the bus. For example, if PHY 0x03 responds by asserting RCLAV while PHY 0x08 is still transferring a cell, then the 77V011 will continue to place PHY subport address 0x03 on the RxADDR[4:0] bus. This will continue until PHY 0x08 has finished its cell transfer and PHY 0x03 is given control of the receive bus. Polling will then resume with PHY subport address 0x04.

A variance in the polling state machine may occur when DRxCLK is an input to the 77V011 and the frequency of DRxCLK is low enough to cause the UTOPIA receive bus to interrupt the cell transfer. The interruption will be indicated by RENB de-asserting high during the cell transfer. Data transfer will resume, where it left off, when RENB reasserts low. In order to resume the current cell transfer the same PHY subport address is placed on the RxADDR[4:0] bus one RCLK cycle before RENB is re-asserted low. Each time a cell transfer is interrupted the polling sequence is interrupted in this manner, which may happen frequently if DRxCLK is much slower than SYSCLK. For example if PHY port 0x03 is given control of the bus to transfer a cell. Once PHY port 0x03 takes control of the bus the 77V011 begins its polling sequence starting with PHY port 0x04. In the middle of the cell transfer data is halted by RENB de-asserting high, due to the DPI interface. At this time data transfer is halted while 77V011 is polling PHY port 0x08. After some period of time the DPI interface starts to transfer the remainder of the cell. The 77V011 puts the PHY subport address 0x03 on the RxADDR[4:0] bus and then asserts RENB low on the next RCLK cycle. Data transfer resumes where it had left off and the 77V011 starts polling the PHY ports starting at PHY subport address 0x09.

In 8-bit UTOPIA mode there is a maximum one clock cycle delay between back to back cells when a TAG is not being used, and a maximum seven clock cycle delay when a four byte TAG is used. In 16bit mode there is a maximum one clock cycle delay between back to back cells when a TAG is not being used, and a maximum five clock cycle delay when a four byte TAG is used.

## UTOPIA 2 Transmit Interface Operation

The 77V011 offers a fully compliant UTOPIA Level 2 transmit interface, as specified by the UTOPIA Level 2 specification. This is a master UTOPIA interface that uses UTOPIA cell level handshake to transmit ATM cells to the PHY device. It will operate with either a 8-bit or 16-bit Output Data Bus (TxDATA[15:0]). Other signals associated with this interface are Transmit Start of Cell (TSOC), Transmit Enable (TENB), Transmit Clock (TCLK), Transmit Cell Available (TCLAV), Transmit Reference Clock (TxREF), Reference Clock (REFCLK), Transmit Parity (TxPRTY), Transmit Address Bus (TxADDR[4:0]) and Transmit LED (TxLED).

TCLK is a continuous clock, whose relationship is defined in the Clock Relationship and Frequency Table.

TxREF is a 8KHz reference clock output generated from REFCLK.

REFCLK is a 8KHz reference clock input used to generate the TxREF clock signal.

TxLED indicates if there is activity on the transmit UTOPIA 2 bus. This signal asserts high when a cell is transferred over the bus, and will stay high for  $2^{22}$  TCLK cycles. AT 40MHz this is approximately 0.1 seconds.

TxPRTY is a parity bit for TxDATA[15:0] bus.

The TxADDR[4:0] bus is fully UTOPIA Level 2 compliant and follows the MPHY Cell-Level Handshake with one TCLAV as described in the UTOPIA Level 2 specification.

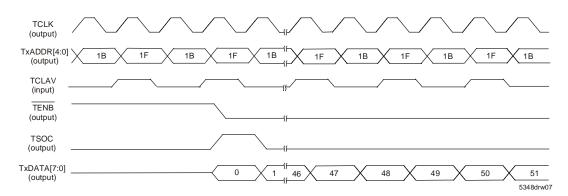

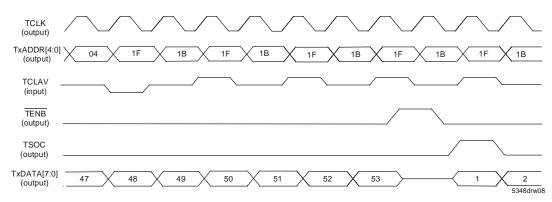

When a cell is transferred on the transmit DPI interface the subport address is analyzed and extracted by the 77V011. The subport address is then interleaved with the Null PHY subport address (0x1F) and output on the TxADDR[4:0] bus to query the corresponding PHY port. Upon detecting a high TCLAV the 77V011 will assert TENB low, TSOC and the first valid byte/word of data. The current PHY subport address will be output on the TxADDR[4:0] bus until another cell enters the 77V011 on the transmit DPI interface. When a cell is detected on the transmit DPI interface and a cell transfer is in progress on the transmit UTOPIA 2 interface, the subport is extracted and output on the TxADDR[4:0] bus, interleaved with the Null PHY subport address, to query the new PHY port. Once the current cell transfer on the transmit UTOPIA 2 interface is complete and the new PHY port has responded, the new cell will be transferred on the transmit UTOPIA 2 interface.

With an 8-bit UTOPIA bus there is a maximum one clock cycle delay between back to back cells when switching is being done without a TAG, and there is a maximum five clock cycle delay if a four byte TAG is being used. There is a maximum three clock cycle delay between back to back cells in 16-bit UTOPIA mode without a TAG, and a maximum five clock cycle delay if a four byte TAG is being used.

There are several registers associated with the UTOPIA 2 Transmit Interface. In-Stream<sup>™</sup> programming cells are used to program the registers, which are described in the UTOPIA 2 Transmit Register Table.

| Register<br>Name | Register<br>Address | Bit<br># | Bit Name      | Value<br>Range | Default<br>Value | Description                                                                                                                                                                |

|------------------|---------------------|----------|---------------|----------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode Select      | 8006                | 2        | UTOPIA 2 Size | 0 - 1          | Defined by pin   | Selects the size of the UTOPIA 2 transmit and receive data bus.<br>"0" 8-bit UTOPIA 2 transmit and receive data bus, "1" 16-bit<br>UTOPIA 2 transmit and receive data bus. |

Table 2 UTOPIA 2 Receive Register Table

11 of 43

Figure 5 Single Cell Transfer with no Cell Transfer in Progress

Figure 6 Back-to-Back Cell Transfer on transmit UTOPIA 2 Bus

| Register<br>Name | Register<br>Address | Bit<br># | Bit<br>Name     | Value<br>Range | Default<br>Value | Description                                                                                                                                                                                                                                                       |

|------------------|---------------------|----------|-----------------|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration 1  | 8001                | 0        | Drop Tx Cell    | 0 - 1          | 0                | Drop a cell with an invalid subport address. "0" do not drop the cell, "1" drop the cell.                                                                                                                                                                         |

| Configuration 2  | 8002                | [1:0]    | Stall Tx        | 0x2            | 0x0              | Selects whether or not to stall the pipeline if the PHY trans-<br>mit FIFO is full. "0" drop cell, "1" stall pipeline indefinitely, "2"<br>stall pipeline for Stall Cycles.                                                                                       |

|                  |                     | [6:2]    | Max Subports    | 0x00 - 0x1E    | 0x1E             | Indicates the maximum subport address value for the PHY(s) connected to the transmit UTOPIA 2 interface.                                                                                                                                                          |

| Configuration 3  | 8003                | [7:0]    | Stall Tx Cycles | 0x00 - 0xFF    | 0xFF             | Number of TCLK cycles the interface has to stall the pipe-<br>line when the PHY transmit FIFO is full. This field is valid<br>only if the Stall Tx for Stall Cycles option is selected.                                                                           |

| Status           | 8009                | 2        | Tx Cell Dropped | 0 - 1          | 0                | Indicates if any cells have been dropped at the transmit<br>UTOPIA 2 interface. This is a status indicator for the Stall Tx<br>bit of the Configuration 2 register. "0" no cells have been<br>dropped, "1" a cell was dropped because the PHY did not<br>respond. |

Table 3 UTOPIA 2 Receive Register Table

#### **DPI Interface**

The Data Path Interface (DPI) is a synchronous bus interface designed to transfer ATM cells between two devices. The 77V011 DPI interface will support either a 4-bit wide data bus (DPI-4) or an 8-bit wide data bus (DPI-8). There are separate transmit and receive interfaces, with all signals being sampled on the rising edge of their respective clock.

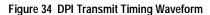

## **DPI Receive Interface**

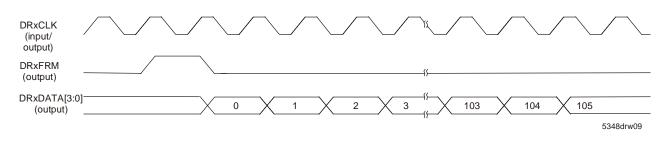

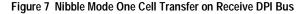

The DPI Receive Interface is used to transfer cells from the 77V011 to the IDT SWITCHStAR or other DPI device. It supports either a 4-bit or 8-bit Output Data Bus (DRxDATA[7:0]) and follows the standard DPI timing characteristics as described in the DPI specification. Other signals associated with this interface are DPI Receive Start of Frame (DRxFRM), and DPI Receive Clock (DRxCLK).

DRxCLK operates at a frequency less than or equal to SYSCLK. Depending on the DPI mode selected this clock will be either an input or an output. In Normal Mode DRxCLK is an input to the 77V011, and its frequency must be less than or equal to SYSCLK. In Switch Mode DRxCLK is a continuous clock generated by the 77V011, with its frequency being equal to SYSCLK. There is no flow control in Switch mode, as it is assumed that the IDT SWITCHStAR will be able to accept all incoming cells (non-blocking). Programming the clock direction is done at reset.

The DPI mode is selected with the MGMT[3] signal at reset, with the condition of MGMT[3] being stored in the DPI Mode bit of the Mode Select register. Setting MGMT[3] ="0" selects Switch Mode (output), while setting MGMT[3] ="1" selects Normal Mode (input).

The DPI bus size is selected with the MBUS[10] pin at reset, with the condition of MBUS[10] being stored in the DPI Size bit of the Mode

Select register. Setting MBUS[10] ="0" selects a 4-bit data bus, while setting MBUS[10] ="1" selects an 8-bit data bus.

DRxFRM is the start of frame marker. This signal is one DRxCLK cycle long and is asserted high one DRxCLK cycle before the first nibble/byte of valid data.

## **DPI Transmit Interface**

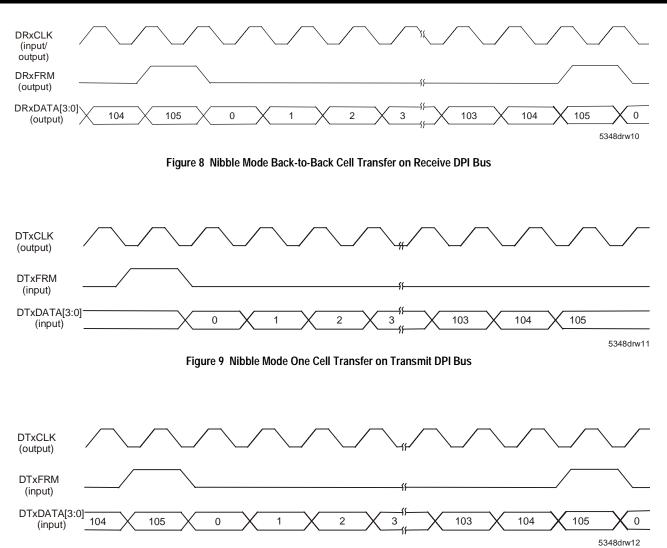

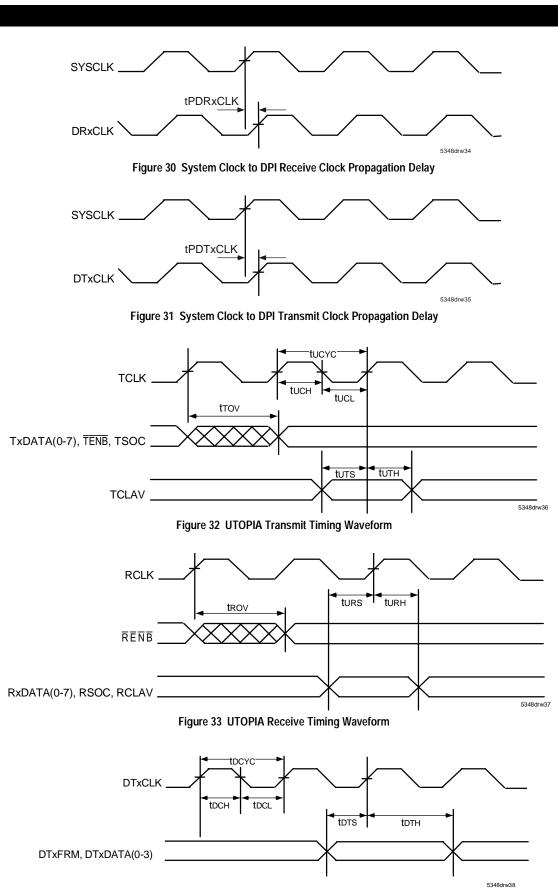

The DPI Transmit Interface is used to transfer cells from the IDT SWITCHStAR or other DPI device to the 77V011. It supports either a 4bit or 8-bit Input Data Bus (DTxDATA[7:0]) and follows the standard DPI timing characteristics as described in the DPI specification. Other signals associated with this interface are DPI Transmit Start of Frame (DTxFRM) and DPI Transmit Clock (DTxCLK).

DTxCLK operates at a frequency equal to SYSCLK. DTxCLK can be stopped to control data flow to the PHY device.

DTxFRM is the start of frame marker. This signal is one DTxCLK cycle long and is asserted high one DTxCLK cycle before the first valid nibble/byte of data.

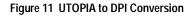

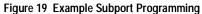

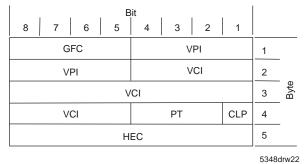

## **UTOPIA to DPI Conversion**

Byte swapping must be performed to convert the 8 or 16-bit transmit and receive of the UTOPIA interface to the 4 or 8-bit transmit and receive of the DPI interface.

In 4-bit DPI mode cell formatting is big endian, or upper nibble first, while in 8-bit DPI mode cell formatting is done little endian to match the IDT 77V400 Switching Memory. The UTOPIA to DPI Conversion Table illustrates how the 77V011 performs cell formatting in 4 and 8-bit DPI mode.

| Register<br>Name | Register<br>Address | Bit<br># | Bit<br>Name | Value<br>Range | Default<br>Value | Description                                                                                                                 |

|------------------|---------------------|----------|-------------|----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Mode Select      | 8006                | 0        | DPI Size    | 0 - 1          | Defined by pin   | Selects the size of DPI data bus. "0" 4-bit DPI transmit and receive data bus, "1" 8-bit DPI transmit and receive data bus. |

|                  |                     | 1        | DPI Mode    | 0 - 1          | Defined by pin   | Selects DRxCLK direction. "0" switch mode (output), "1" nor-<br>mal mode (input).                                           |

Table 4 UTOPIA 2 Receive Register Table

Downloaded from Elcodis.com electronic components distributor

13 of 43

Figure 10 Nibble Mode Back-to-Back Cell Transfer on Transmit DPI Bus

| 8-bit UTOPIA |            |  |  |  |  |  |  |

|--------------|------------|--|--|--|--|--|--|

| bit 7        | bit 0      |  |  |  |  |  |  |

| GFC          | VPI[7:4]   |  |  |  |  |  |  |

| VPI[3:0]     | VPI[15:12] |  |  |  |  |  |  |

| VPI[11:4]    |            |  |  |  |  |  |  |

| 4-bit DPI |          |  |       |  |  |  |  |  |

|-----------|----------|--|-------|--|--|--|--|--|

| bit 3     |          |  | bit 0 |  |  |  |  |  |

| GFC       |          |  |       |  |  |  |  |  |

| VPI[7:4]  |          |  |       |  |  |  |  |  |

|           | VPI[3:0] |  |       |  |  |  |  |  |

| 8-bit UTOPIA |            |  |  |  |  |  |  |

|--------------|------------|--|--|--|--|--|--|

| bit 7        | bit 0      |  |  |  |  |  |  |

| GFC          | VPI[7:4]   |  |  |  |  |  |  |

| VPI[3:0]     | VPI[15:12] |  |  |  |  |  |  |

| VPI[11:4]    |            |  |  |  |  |  |  |

| 8-bit DPI |            |  |  |  |  |  |  |

|-----------|------------|--|--|--|--|--|--|

| bit 7     | bit 0      |  |  |  |  |  |  |

| GFC       | VPI[7:4]   |  |  |  |  |  |  |

| VPI[3:0]  | VPI[15:12] |  |  |  |  |  |  |

| VPI[11:8] | VPI[7:4]   |  |  |  |  |  |  |

Downloaded from Elcodis.com electronic components distributor

## Programming Pin Configurable Registers at Reset

Pull-up or pull-down resistors must be connected to MBUS[11:0], MGMT[3:2] and TxADDR[3:0] signals, on the PCB, to select desired register values. The SYSRST signal must be asserted for at least one <u>SYSCLK</u> cycle to load the desired values. On the rising edge of SYSRST the 77V011 will begin loading the register values, which takes an additional 16 SYSCLK cycles. During this 16 clock cycle period all outputs will be tri-stated.

## Programming Pin Configurable Registers after Reset

The 77V011 has the option to change the Read only pin configurable registers to Read/Write registers. Writing a one to the Override Pin Configuration bit of the Pin Controls register will change the pin configurable registers from Read only to Read/Write. This allows the 77V011 configuration parameters to be changed during normal operation. See Pin Configuration Table for register description.

## **Reset Options**

The System Reset (SYSRST) pin or an In-Stream<sup>™</sup> cell carrying the Reset command (Message Type ID 0x3) will reset the 77V011 and the PHY devices. The SYSRST pin must be asserted low for a minimum of

100ns, while the In-Stream<sup>™</sup> (internal) reset command will keep the 77V011 in reset for 35 SYSCLK cycles.

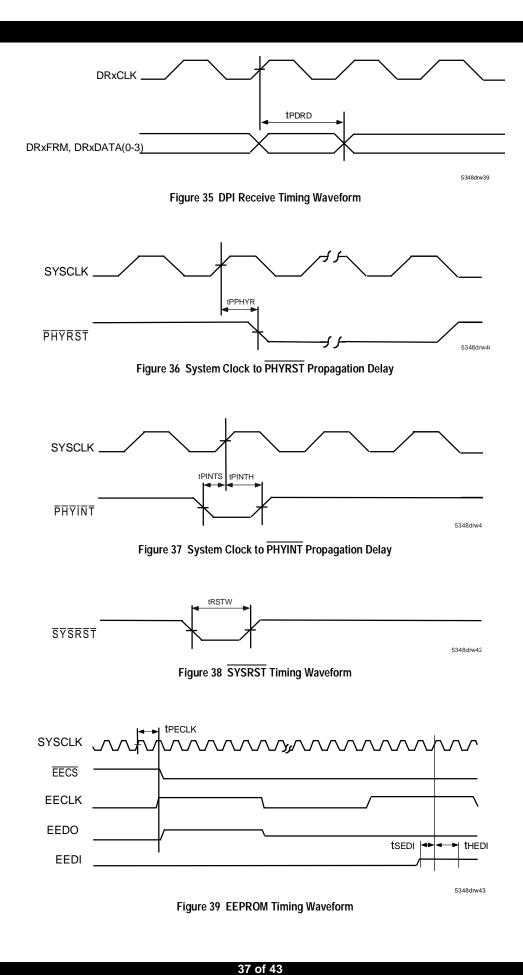

The 77V011 will remain in reset for 16 SYSCLK cycles after the deassertion of SYSRST, or the internal reset in the case of a Reset command. All outputs will be tri-stated starting two SYSCLK cycles after the assertion of SYSRST or the internal reset, and will stay tri-stated for 24 SYSCLK cycles after the deassertion of SYSRST or internal reset. The PHYRST pin will then assert low resetting the PHY devices for eight additional SYSCLK cycles. After the eight clock cycle period PHYRST pin will deassert high. Eight clock cycles may not be long enough to properly reset some PHY devices. In this case a pull down resistor should be connected to the PHYRST pin. This will allow the PHYRST pin to be asserted as soon as it is tri-stated, which will Lenten the time that the PHYRST pin is a logical zero.

The PHY can be reset at any time by writing a one to the PHY Reset bit of the Reset register. Writing a one will force the external PHYRST pin low for 16 SYSCLK cycles. This register bit will return to zero once the reset command is completed. This method will only reset the PHY device connected to the PHYRST pin.

# **Bandwidth and Clock Speeds**

The 77V011 can run at a maximum SYSCLK speed of 50MHz. The DPI clocks must run at 40MHz, or greater, to achieve 155.52Mbps data rate with overhead. The Clock Speed vs. Bandwidth Table lists some of the possible data rates and the clock frequencies required to achieve them.

| Pin Name    | Function @ Reset      | Options                                                                                                                                                                               | Register                                                     |

|-------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| MBUS[2:0]   | Tx TAG Size           | Number of bytes to remove from the cell. Valid values are from zero to four bytes.                                                                                                    | Tx TAG [2:0]                                                 |

| MBUS[3]     | Tx TAG Location       | Location of the transmit TAG. "0" transmit TAG located at the beginning of the cell, "1" transmit TAG located at the end of the cell.                                                 | Tx TAG [4]                                                   |

| MBUS[4]     | Tx Add HEC            | Add a HEC placeholder to the cell. "0" do not add HEC placeholder, "1" add HEC placeholder                                                                                            | . Tx TAG [3]                                                 |

| MBUS[7:5]   | Rx TAG Size           | Number of bytes to add to the cell. Valid values are from zero to four bytes.                                                                                                         | Rx TAG [2:0]                                                 |

| MBUS[8]     | Rx TAG Location       | Location of the receive TAG. "0" receive TAG located at the beginning of the cell, "1" receive TAG located at the end of the cell.                                                    | Rx TAG [4]                                                   |

| MBUS[9]     | Rx HEC                | Remove HEC byte from cell. "0" do not remove HEC byte, "1" remove HEC byte.                                                                                                           | Rx TAG [3]                                                   |

| MBUS[10]    | DPI Size              | DPI bus size. "0" 4-bit transmit and receive data bus, "1" 8-bit transmit and receive data bus.                                                                                       | Mode Select [0]                                              |

| MBUS[11]    | UTOPIA 2 Size         | UTOPIA 2 bus size. "0" 8-bit transmit and receive data bus, "1" 16-bit transmit and receive data bus.                                                                                 | Mode Select [2]                                              |

| MGMT[2]     | MMODE                 | Management mode. "0" Utility Bus style, "1" UTOPIA 2 style.                                                                                                                           | Mode Select [3]                                              |

| MGMT[3]     | DPI Mode              | DRxCLK direction. "0" switch mode (output), "1" normal mode (input).                                                                                                                  | Mode Select [1]                                              |

| TxADDR[2:0] | Subport Byte Location | Transmit and receive subport address location. Indicates what byte of the header the transmit and receive subport addresses are located in. Valid values are zero to three.           | Tx Subport Position<br>[2:0] and Rx Subpor<br>Position [2:0] |

| TxADDR[3]   | Init from EEPROM      | Five byte write from EEPROM to In-Stream <sup>™</sup> Cell Header and In-Stream <sup>™</sup> Subport registers at reset. "0" do not write five byte value, "1" write five byte value. | Mode Select [4]                                              |

Table 5 Reset Configuration Pins

| Register<br>Name | Register<br>Address | Bit # | Bit Name                         | Range<br>Values | Default<br>Values | Description                                                                                                                                                                  |

|------------------|---------------------|-------|----------------------------------|-----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Controls     | 801A                | 0     | Override<br>Pin<br>Configuration | 0 - 1           | 0                 | Enables writing to pin configurable registers during normal operation. "0" pin configurable registers are read only, "1" pin configurable registers are read/write registers |

Table 6 Pin Configuration Table

|                                          | Device to be Reset |               |  |

|------------------------------------------|--------------------|---------------|--|

|                                          | 77V011             | PHY<br>Device |  |

| Software Reset (In-Stream <sup>™</sup> ) | Х                  | Х             |  |

| SYSRST (external pin)                    | Х                  | Х             |  |

| PHYRST (register bit)                    |                    | Х             |  |

Table 7 Reset Table

|                 |                  | DTxCLK &        | UTOPIA TCLK & |               | Calculated Bandwidth of UTOPIA              | Interface (cell rate in Mbps)                     |

|-----------------|------------------|-----------------|---------------|---------------|---------------------------------------------|---------------------------------------------------|

| SYSCLK<br>(MHz) | DPI Bus<br>Width | DRxCLK<br>(MHz) | Bus<br>Width  | RCLK<br>(MHz) | 53 byte cell (normal<br>cell, no TAG added) | 56 byte cell (four bytes of<br>TAG added w/o HEC) |

| 32              | 4                | 32              | 8             | 16            | 125.6                                       | 113.8                                             |

| 40              | 4                | 40              | 8             | 20            | 157                                         | 142.2                                             |

| 50              | 4                | 50              | 8             | 25            | 196.3                                       | 177.8                                             |

| 16              | 8                | 16              | 8             | 16            | 125.6                                       | 113.8                                             |

| 25              | 8                | 25              | 8             | 25            | 196.3                                       | 177.8                                             |

| 33              | 8                | 33              | 8             | 33            | 259.1                                       | 234.7                                             |

| 32              | 8                | 32              | 16            | 16            | 242.3                                       | 235                                               |

| 50              | 8                | 50              | 16            | 25            | 378.6                                       | 367.2                                             |

Table 8 Clock Speed verses Bandwidth Table

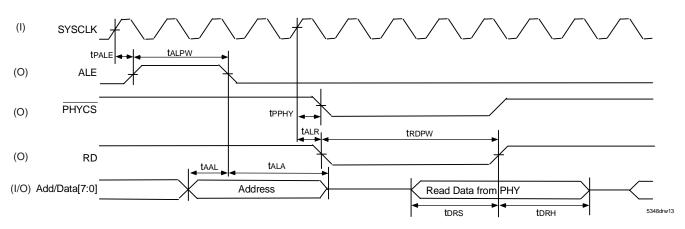

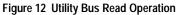

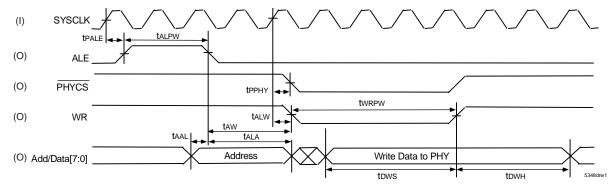

#### Management Interface

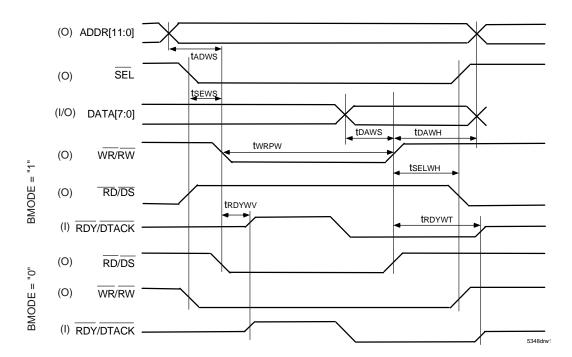

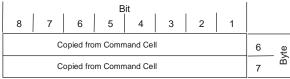

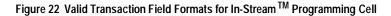

The Management interface is a multi-function interface used to read and write to the PHY registers during normal operation, and to configure the pin configurable registers during reset.