### **Z**86017/**Z**16017

### **PCMCIA Interface Solution**

**Reference Manual**

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact

#### **ZiLOG Worldwide Headquarters**

532 Race Street San Jose, CA 95126-3432 Telephone: 408.558.8500

Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

#### **Document Disclaimer**

© 2002 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

iii

## Preface

Thank you for your interest in Zilog's PCMCIA interface solution. This Reference Manual describes the programming and operation of the Z86017 and Z16017 PCMCIA adapter chips.

This Reference Manual is organized in the following way:

#### • PCMCIA Interface Overview

This chapter is an introductory section that provides an overview of the architecture of the device.

#### Addressing Modes

This chapter describes the addressing modes supported by the Z86017/Z16017 architecture to ensure PCMCIA compatibility.

#### • Programming Internal Registers

This chapter describes the serial interface modes.

### Configuration Registers

This chapter describes the functions of the Z86017/Z16017 internal registers.

### Appendix A

This appendix gives an overview of the Z86017/Z16017 multifunction pins.

### Appendix B

This appendix provides Absolute Maximum Ratings, DC Electrical Characteristics, and Timing Specifications related to the Z86017/Z1601.

### Appendix C

This appendix provides various Z86017/Z16017 timing diagrams.

Preface RM001103-0202

### Appendix D

This appendix provides part numbers and ordering information.

### Appendix E

This appendix provides a description of the Z8601700ZCO PCMCIA Interface Development Kit.

RM001103-0202 Preface

V

# Table of Contents

| Preface | e                                                                                                              | iii |

|---------|----------------------------------------------------------------------------------------------------------------|-----|

| PCMCI   | IA Interface Overview                                                                                          |     |

|         | Features                                                                                                       |     |

|         | Pin Description                                                                                                |     |

|         | Pin Identification                                                                                             |     |

|         | Pin Functions PCMCIA Signals Peripheral or ATA/IDE Signals Serial Interface Signals Peripheral Control Signals |     |

| Address | ssing Modes                                                                                                    | 27  |

| Progran | mming Internal Registers                                                                                       | 35  |

|         | Introduction                                                                                                   |     |

|         | EEPROM Register                                                                                                |     |

|         | Word-to-Byte Operation                                                                                         |     |

| Configu | uration Registers                                                                                              | 83  |

|         | Introduction                                                                                                   |     |

|         | Configuration Registers                                                                                        |     |

| Append  | dix A: Multifunction Pins                                                                                      |     |

RM001103-0202 Table of Contents

vi

|            | Overview of Multifunction Pins           | 91  |

|------------|------------------------------------------|-----|

| Appendix B | 3: Electrical Characteristics and Timing | 97  |

|            | internal attribute memory timing         | 100 |

|            | 017 Device Slew Delay                    | 112 |

| Appendix C | C: Timing Examples                       | 117 |

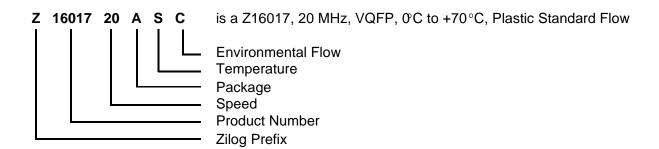

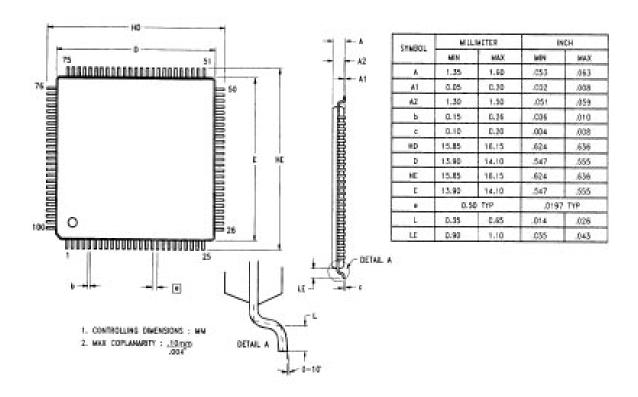

| Appendix D | D: Packaging and Ordering Information    | 121 |

|            | 20 Mhz PCMCIA Adapter Chips              | 121 |

|            | Package                                  |     |

|            | Temperature                              | 121 |

|            | Speed                                    | 121 |

|            | Environmental                            | 121 |

|            | Package Dimensions                       | 122 |

| Appendix E | E: PCMCIA Interface Development Kit      | 123 |

|            | General Description                      | 123 |

|            | Z86017 Specifications                    | 123 |

|            | Power Requirements:                      |     |

|            | Dimensions                               | 123 |

|            | Kit Contents                             | 124 |

|            | Evaluation Board                         |     |

|            | ZPCMCIA0ZDP PCMCIA Extender Card         | 124 |

RM001103-0202 Table of Contents

vii

# List of Figures

| PCMCIA Interface Ove    | erview                                                          | 1    |

|-------------------------|-----------------------------------------------------------------|------|

| Figure 1.               | ZX6017 Functional Block Diagram                                 | 3    |

| Figure 2.               | Serial Port Master Mode Control                                 | 5    |

| Figure 3.               | Serial Port Slave Mode Control                                  | 7    |

| Figure 4.               | EEPROM Programming Through the PCMCIA Interface                 | 8    |

| Figure 5.               | Connection Block Diagram                                        | 9    |

| Figure 6.               | Serial Interface Diagram                                        | 10   |

| Figure 7.               | Attribute and Configuration Memory Diagram                      | 11   |

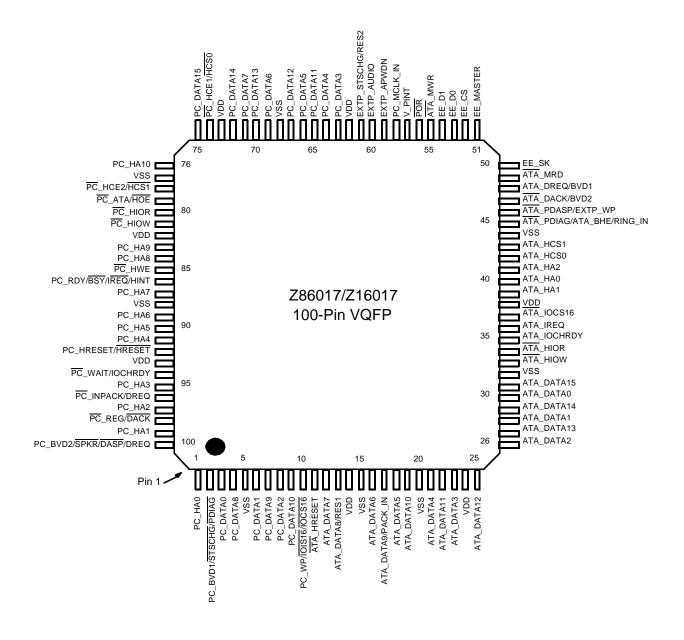

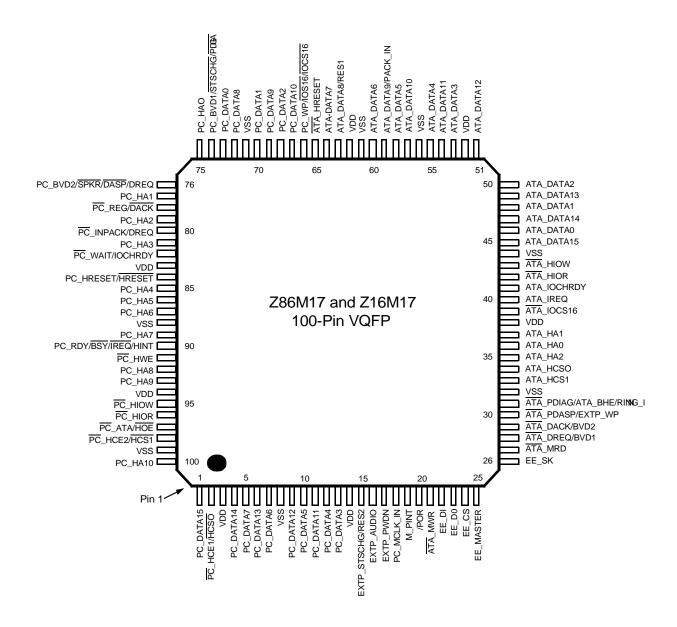

| Figure 8.               | ZX6017 100-Pin VQFP Pin Configuration                           | 12   |

| Figure 9.               | Z86M17 and Z16M17 (Mirror Image) 100-Pin VQFP Pin Configuration | 13   |

| Addressing Modes        |                                                                 | . 27 |

| Programming Internal    | Registers                                                       | . 35 |

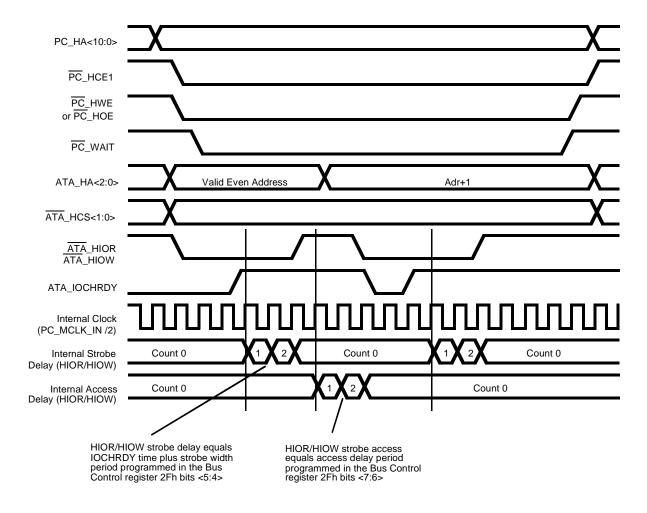

| Figure 10.              | Word-to-Byte Timing                                             | 79   |

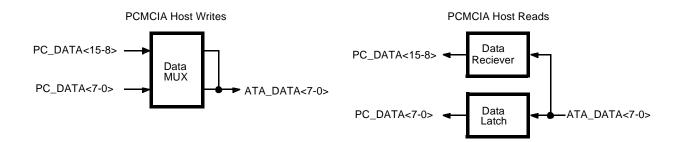

|                         | Word-to-Byte Mode Data Path                                     |      |

| Configuration Registers | s 83                                                            |      |

| Appendix A: Multifunc   | tion Pins                                                       | 91   |

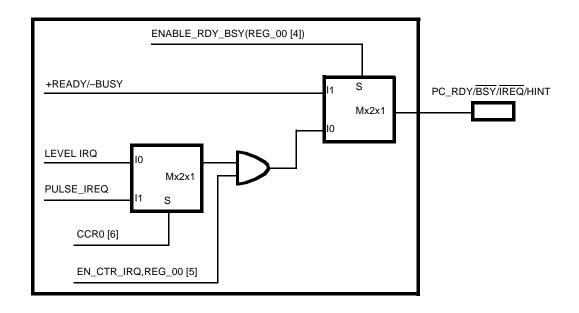

| Figure 12.              | Z16017BA PC_RDY/BSY/IREQ/HINT Pin                               | 91   |

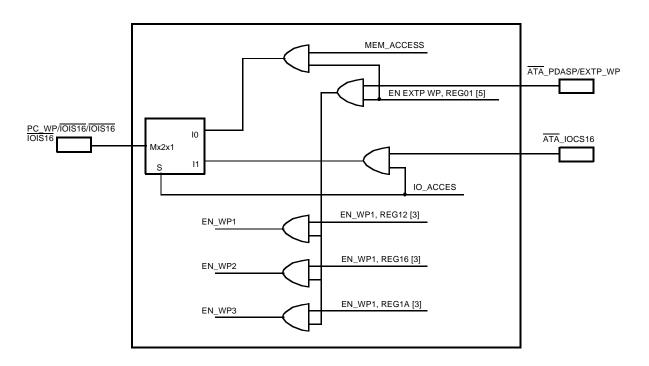

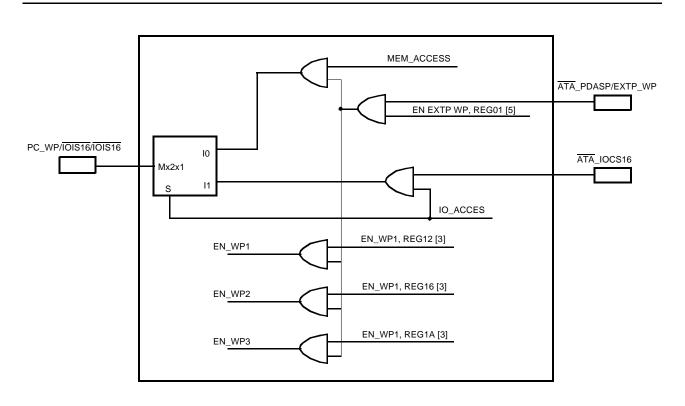

| Figure 13.              | Z86017BA PC_WP/IOIS16/IOIS16 Pin                                | 92   |

| Figure 14.              | Z16017BA PC_WP/IOIS16/IOIS16 Pin                                | 93   |

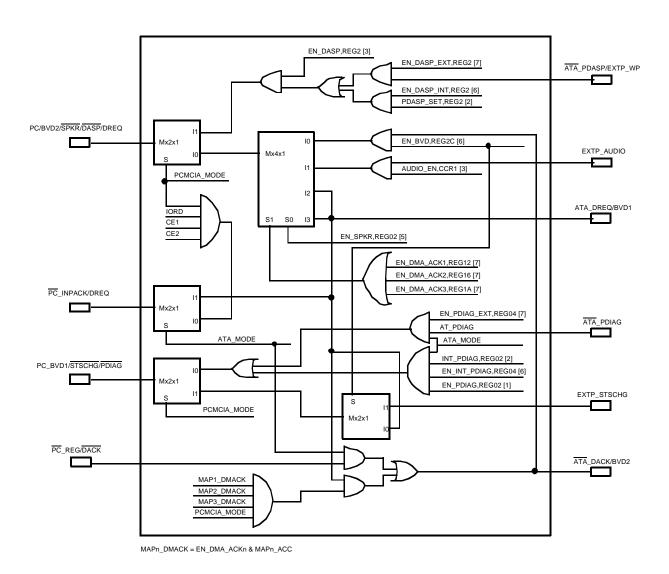

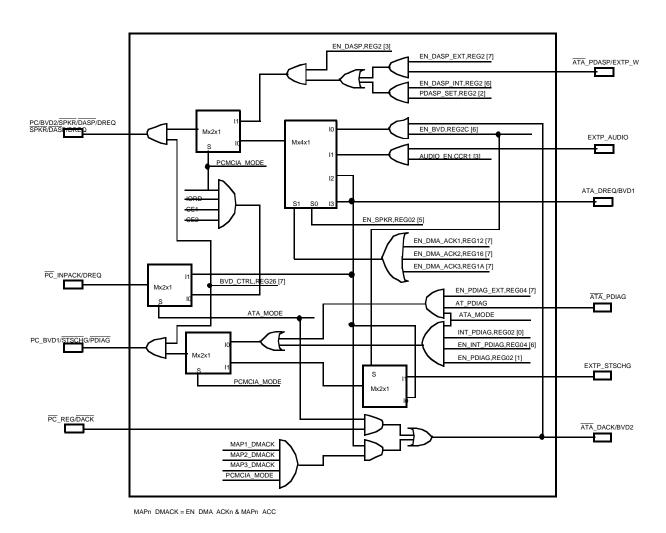

| Figure 15.              | Z86017BA (Overview of Internal Structure)                       | 94   |

RM001103-0202 List of Figures

| Figure 16.             | Z16017BA (Overview of Internal Structure) 95                                         |

|------------------------|--------------------------------------------------------------------------------------|

| Appendix B: Electrical | Characteristics and Timing97                                                         |

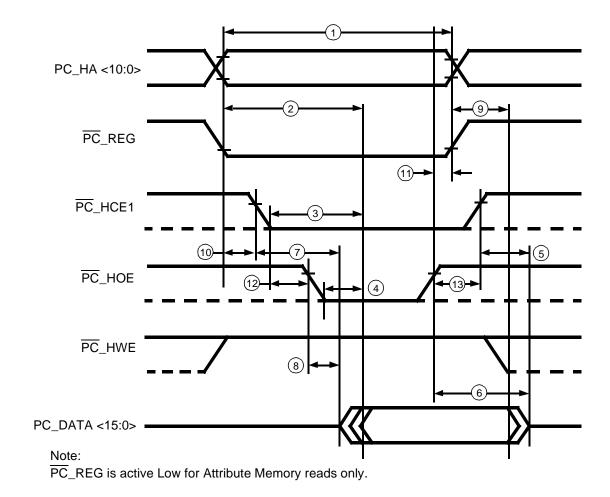

| Figure 17.             | PCMCIA Read Memory Timing, No Wait States 101                                        |

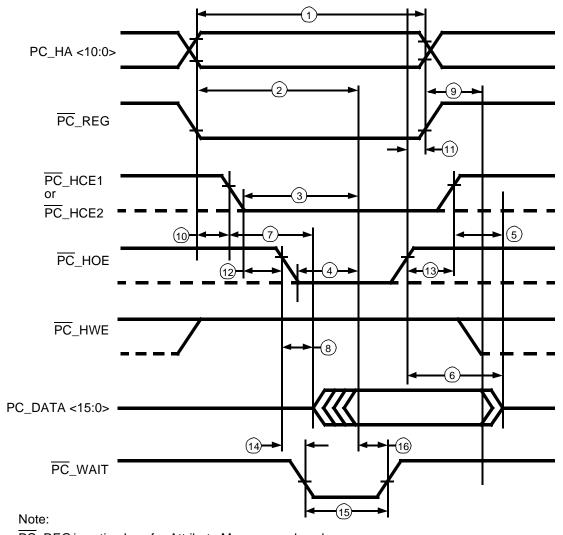

| Figure 18.             | PCMCIA Read Memory Timing, Wait State Enabled 102                                    |

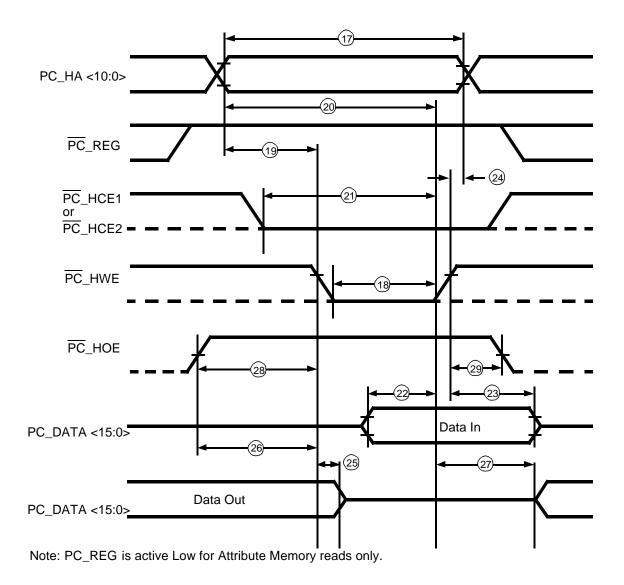

| Figure 19.             | PCMCIA Write Memory Timing, No Wait States 105                                       |

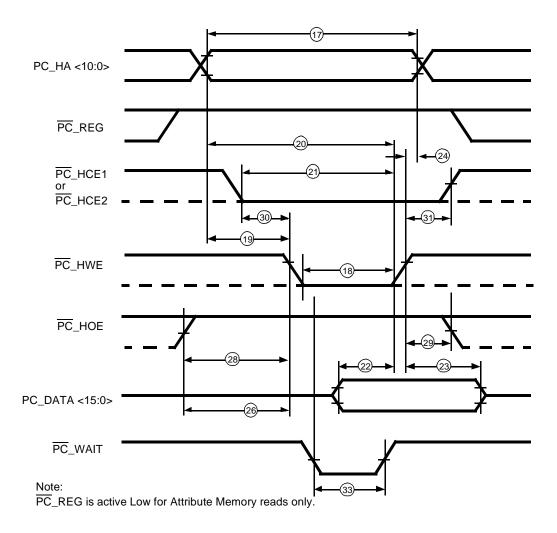

| Figure 20.             | PCMCIA Write Memory Timing, Wait State Enabled 106                                   |

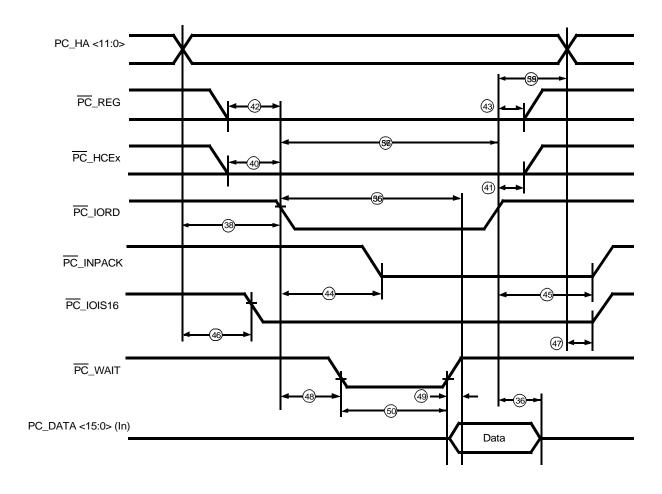

| Figure 21.             | I/O Read Timing                                                                      |

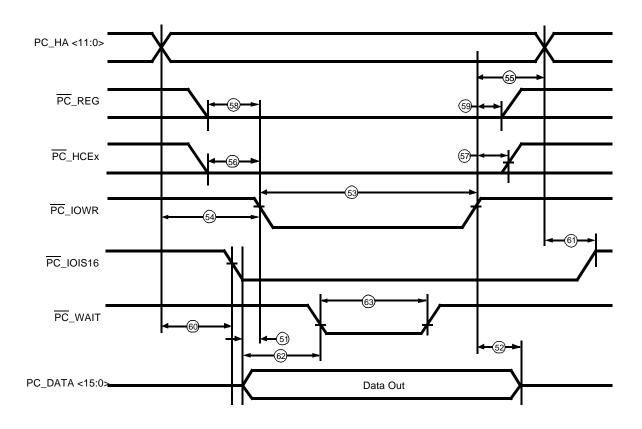

| Figure 22.             | I/O Write Timing                                                                     |

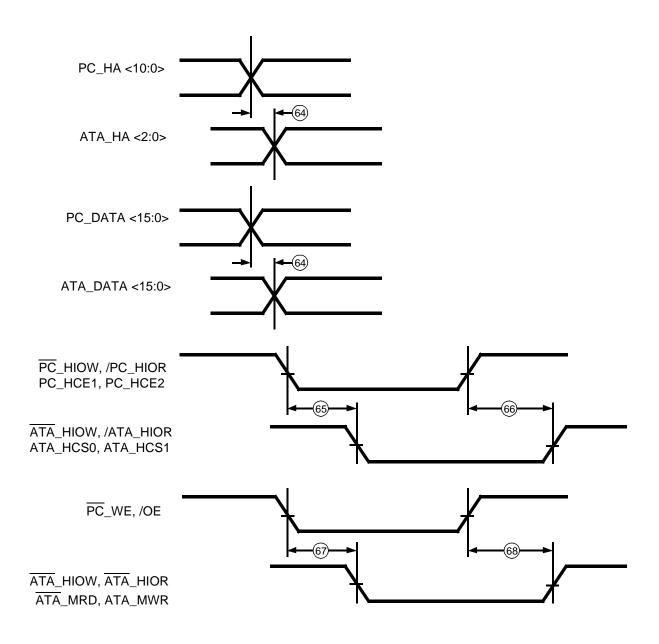

| Figure 23.             | Skew Timing Between PCMCIA and ATA/IDE or Peripheral Bus                             |

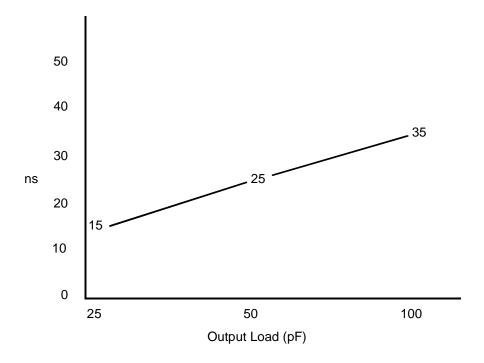

| Figure 24.             | 017 Slew Delay Derating Curve (Typical) 112                                          |

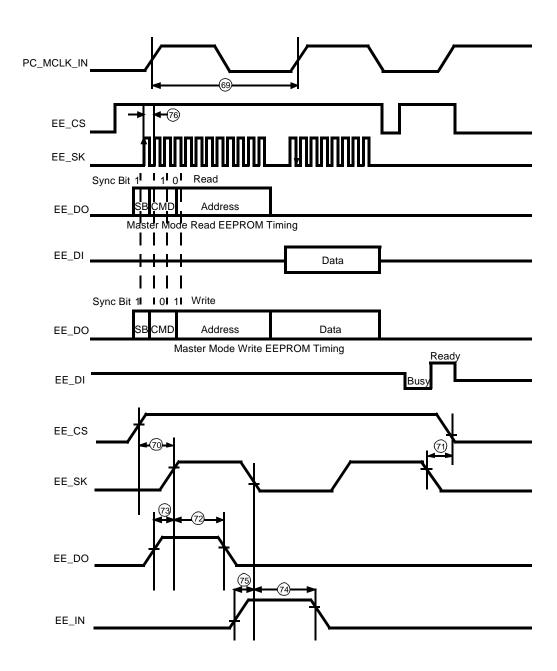

| Figure 25.             | FMaster Mode Read EEPROM Timing                                                      |

| Figure 26.             | Slave Interface Timing (Read)                                                        |

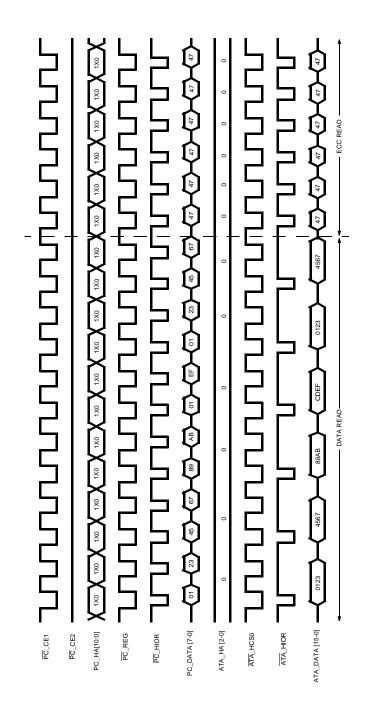

| Appendix C: Timing Ex  | xamples117                                                                           |

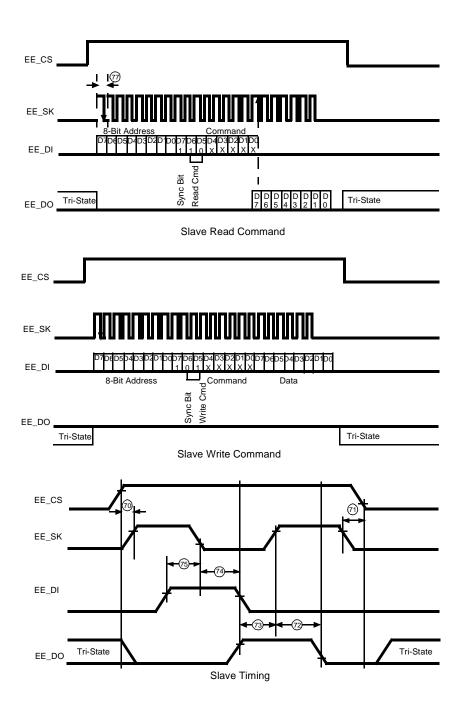

| Figure 27.             | Z16017BA Reset Timing PCMCIA Mode                                                    |

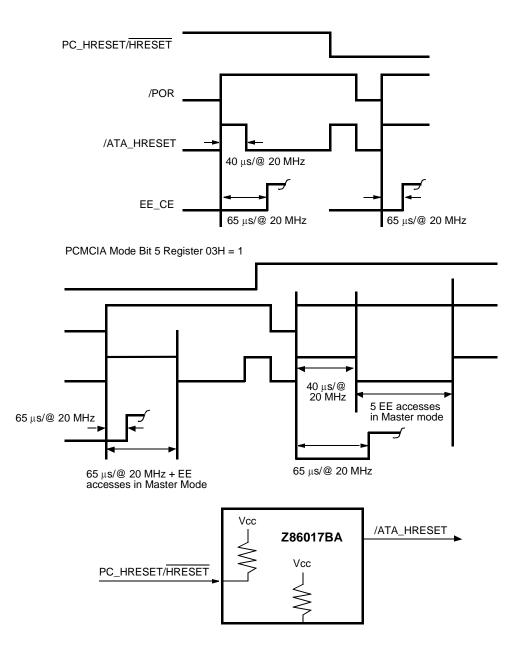

| Figure 28.             | PCMCIA ATA/IDE 16-Bit I/O Write (Register 24 = 01, Internal IOIS 16 is selected) 118 |

| Figure 29.             | PCMCIA ATA / IDE 8-Bit Long Read (Reading 512-byte data plus 6-byte ECC)             |

| Appendix D: Packaging  | and Ordering Information                                                             |

| Figure 30.             | Example Package Name                                                                 |

| Figure 31.             | 100-Lead VQFP Package Diagram                                                        |

| Appendix E: PCMCIA     | Interface Development Kit                                                            |

RM001103-0202 List of Figures

ix

## List of Tables

#### **PCMCIA Interface Overview 1**

Table 2. Power Connections 2

Table 3. 100-Pin VQFP Pin Identification 14

#### **Addressing Modes 27**

| Table 4. ZX6017 Addressing Modes | 2 |

|----------------------------------|---|

|----------------------------------|---|

Table 5. Programming PCMCIA\_ATA ZX6017 Configuration Registers 29

Table 6. PCMCIA Common Memory Mode 31

Table 7. PCMCIA I/O Mode 31

Table 8. PCMCIA\_ATA Memory Mapped Access 32

Table 9. PCMCIA ATA I/O Mapped Access 33

### **Programming Internal Registers 35**

| Table 10. | ZX6017 | Card | Configura | ition Re | gisters ( | 35 |

|-----------|--------|------|-----------|----------|-----------|----|

|           |        |      |           |          |           |    |

Table 11. Interface Configuration Register: Address 00h 38

Table 12. Master Clock 40

Table 13. Interrupt Enable Register: Address 01h 41

Table 14. Interface Configuration Register 1: Address 02h 43

Table 15. PCMCIA PDIAG Pin Functions 44

Table 16. PCMCIA DASP Pin Functions 45

Table 17. Host Chip Select Designations 46

Table 18. Audio Pin Configurations 46

Table 19. Interface Configuration Register 2: Address 03h 47

Table 20. Interface Configuration Register 3: Address 04h 48

RM001103-0202 List of Tables

Table 37.

| Table 22. | Reset Conditions 49                               |

|-----------|---------------------------------------------------|

| Table 23. | PCMCIA CCR Base Address Register: Address 05h 50  |

| Table 24. | CCR Location Examples, Register 5 51              |

| Table 25. | PCMCIA Interrupt Status Register: Address 06h 52  |

| Table 26. | PCMCIA Exception Status Register: Address 07h 53  |

| Table 27. | ATA Sample Mode Bit 54                            |

| Table 28. | Attribute Memory Address Register: Address 08h 54 |

| Table 29. | Attribute Memory Data Register: Address 09h 55    |

| Table 30. | Window 1 Control Register: Address 10h 56         |

| Table 31. | Window 1 Start Address LSB: Address 11h 57        |

| Table 32. | Window 1 Start/Range Address MSB: Address 12h 57  |

| Table 33. | Window 1 Range Address LSB: Address 13h 58        |

| Table 34. | Window 2 Control Register: Address 14h 58         |

| Table 35. | Window 2 Start Address LSB: Address 15h 59        |

| Table 36. | Window 2 Start/Range Address MSB: Address 16h 60  |

Table 21. ATA Register Selection Designations 49

Table 38. Window 3 Control Register: Address 18h 61

Table 39. Window 3 Start Address LSB: Address 19h 62

Table 40. Window 3 Start/Range Address MSB: Address 1Ah 62

Table 41. Window 3 Range Address LSB: Address 1Bh 63

Table 42. EEPROM Valid flag Byte Register: Address 1Eh 63

Table 43. EEPROM Address/Status CCR5 Back Door: Address 20h 63

Window 2 Range Address LSB: Address 17h 60

Table 44. EEPROM Data CCR6 Back Door: Address 21h 64

EEPROM Command CCR7 Back Door: Address 22h 64 Table 45.

Table 46. Revision Control Register: Address 23h 65

Table 47. Revision Number Register: Address 24h 65

Table 48. Bus Control 1 Register: Address 26h 66

List of Tables RM001103-0202

κi

| Table 50.             | 16-Bit_Control 69                                             |

|-----------------------|---------------------------------------------------------------|

| Table 51.             | 8-Bit _CTRL 69                                                |

| Table 52.             | ATA/IDE Dual Drive Control 70                                 |

| Table 53.             | Power Management Timer Count Value: Address 2Ah 71            |

| Table 54.             | Power Management control Register: Address 2Bh 72             |

| Table 55.             | Interface Configuration Register 4: Address 2Ch 73            |

| Table 56.             | Power Management Clock Select 74                              |

| Table 57.             | Configuration Index Compare Register 1: Address 2Dh 75        |

| Table 58.             | Configuration Index Compare Register 2: Address 2Eh 75        |

| Table 59.             | Bus Control Register: Address 2Fh 77                          |

| Table 60.             | Strobe Width and Access Delay 78                              |

| Table 61.             | PCMICA Host Read and Write Address Examples, 81               |

| Configuration Registe | rs 83                                                         |

| Table 62.             | PCMCIA Address xx0h to xx8h, Configuration Register Decode 83 |

| Table 63.             | ZiLOG EEPROM Programming Extensions 84                        |

| Table 64.             | PCMCIA Configuration Option Register CCR0: Address 0Ah        |

PCMCIA Card Status Register CCR1: Address 0Bh 85

PCMCIA I/O Event Indication CCR4: Address 1Fh 88

PCMCIA Pin Replacement Register CCR2: Address 0Ch 86

PCMCIA socket and Copy Register CCR3: Address 0Dh 87

IOIS16 Address Control Register: Address 27h 68

### **Appendix A: Multifunction Pins 91**

Table 65.

Table 66. Table 67.

Table 68.

Table 49.

### **Appendix B: Electrical Characteristics and Timing 97**

84

Table 69. Absolute Maximum Ratings 97

List of Tables RM001103-0202

| Table 70. | DC Electrical Characteristics 98                             |

|-----------|--------------------------------------------------------------|

| Table 71. | Internal Attribute Memory Timing 100                         |

| Table 72. | PCMCIA Memory Write Timing 103                               |

| Table 73. | I/O Read Timing Specification 107                            |

| Table 74. | I/O Write Timing Specification 109                           |

| Table 75. | Skew Timing Between PCMCIA And ATA/IDE or Peripheral Bus 110 |

| Table 76. | Serial Interface Timing 113                                  |

**Appendix C: Timing Examples 117**

**Appendix D: Packaging and Ordering Information 121**

**Appendix E: PCMCIA Interface Development Kit 123**

RM001103-0202 List of Tables

## PCMCIA Interface Overview

#### **FEATURES**

**Table 1. Device Features**

| Device              | RAM (Bytes) | Speed | Package      |

|---------------------|-------------|-------|--------------|

| Z86017              | 256         | 20    | 100-Pin VQFP |

| Z86M17 <sup>1</sup> | 256         | 20    | 100-Pin VQFP |

| Z16017              | 256         | 20    | 100-Pin VQFP |

| Z16M17 <sup>1</sup> | 256         | 20    | 100-Pin VQFP |

#### NOTES:

1.Mirror Image Bond-Out Options

- PCMCIA Configuration Registers

- Sequencer for programming attribute memory using EEPROM content, MASTER mode

- Serial Peripheral Interface (SPI) circuitry allows control through the local microprocessor, SLAVE mode

- PCMCIA to I/O peripheral

- PCMCIA to ATA/IDE translation

- ATA/IDE to ATA/IDE mapping, PASSHROUGH mode

- Operates from a 3.0V to 5.5V power supply

- Conforms to PCMCIA standards

- Low power dissipation

- Mirror image bond-out option (Z86M17/Z16M17)

- On-chip generation of IOIS16 in I/O mode (Z16017)

### **General Description**

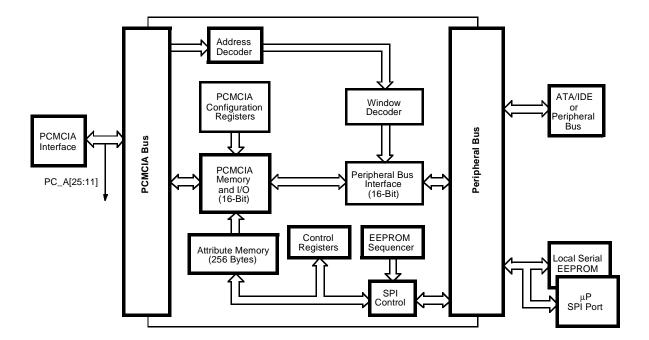

The Z86017/Z16017 (ZX6017) are general-purpose PCMCIA adapter chips used on the card side of the interface. For increased versatility, "mirror image" bond-out versions, the Z86M17 and Z16M17, are also available. These chips are easily configured to allow access to all types of memory or I/O-mapping peripherals, such as Ethernet controllers, Universal Asynchronous Receiver/Transmitters (UART), modems, rotating disk memory, and so on. The ZX6017 can be used in a standalone configuration without the use of a local processor when all necessary data for Attribute Memory, Card Configuration Registers (CCR), Memory/I/O maps, and so on, are being provided by a local serial EEPROM. The serial EEPROM is read automatically using an internal EEPROM sequencer. The ZX6017 can also be configured by a local microprocessor, when one is being used on the card.

Throughout this document, references to the ZX6017 device applies equally to the Z86017 and Z16017, unless otherwise specified.

**Note:** All Signals with an overline ( $\overline{\phantom{a}}$ ) are active Low, that is,  $B/\overline{W}$  (WORD is active Low);  $\overline{B}/W$  (BYTE is active Low, only).

Power connections follow conventional descriptions below:

**Table 2. Power Connections**

| Connection | Circuit         | Device      |

|------------|-----------------|-------------|

| Power      | V <sub>CC</sub> | $V_{ m DD}$ |

| Ground     | GND             | $V_{SS}$    |

The ZX6017 can be programmed by one of two ways: an external 256 byte serial EEPROM can be connected to the serial port interface, or a microprocessor can be connected to this port to provide a higher level of control. Figure 1 depicts the functional block diagram for the ZX6017.

Figure 1. ZX6017 Functional Block Diagram

#### Power-On Reset

The ZX6017 defaults to the Memory Only interface as outlined in the PCMCIA specification upon deassertion of Power-On Reset /POR). The hardware sets Busy on the PC\_RDY/BSY pin and then addresses the EE\_MASTER pin. If the EE\_MASTER pin is unconnected or pulled High, the ZX6017 serial interface defaults to the Master mode and an external EEPROM is required. If this pin is pulled Low, the SLAVE mode is selected and an external microprocessor is required to configure the ZX6017 through the serial interface pins.

Next, the hardware addresses the  $\overline{PC}$ \_ATA/ $\overline{HOE}$  pin. If the  $\overline{PC}$ \_ATA/ $\overline{HOE}$  pin is held Low for 40 clocks (PC\_MCLK\_IN) after POR deassertion, the ZX6017 is enabled for ATA/IDE to ATA/IDE PASSTHROUGH mode. The PASSTHROUGH mode is for systems that use the physical PCMCIA 68-pin connector but do not support PCMCIA protocol. If this pin is held High ( $\overline{PC}$ \_ATA/ $\overline{HOE}$ ), the device is placed into the PCMCIA mode. The override bits in register 00H determine what mode(s) the user can support.

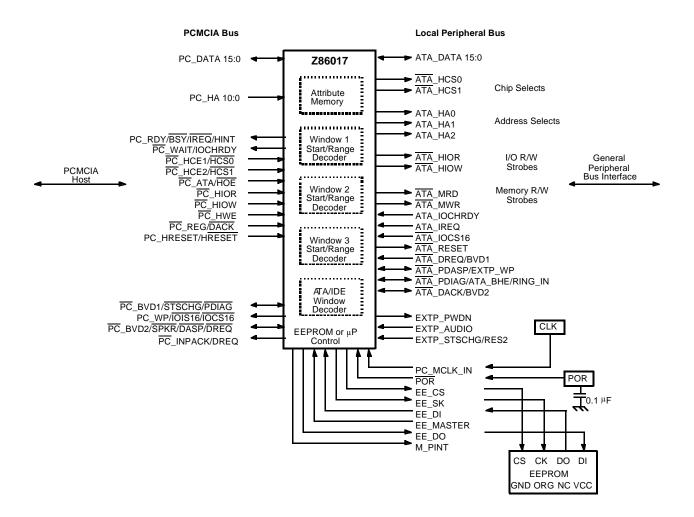

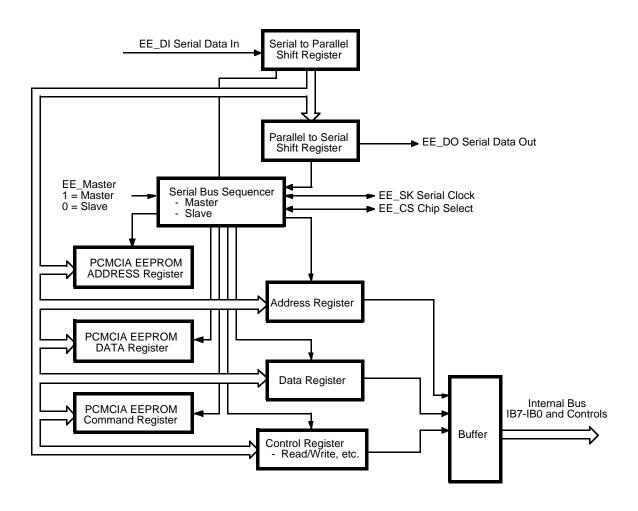

### **Serial Port Operation (Master) Mode**

After the ZX6017 determines that an external EEPROM is present (see Figure 2), the Ready/Busy pin on the PCMCIA interface is set to Busy. The ZX6017 internal sequencer starts up and reads EEPROM address 1eh. If EEPROM address 1Eh is loaded with a 1Ch then the EEPROM's data is considered to be valid. After that, the internal sequencer resets its address counter back to zero. Data from EEPROM's addresses [00-2F] is read out and put into the on-board registers of the ZX6017. The EEPROM sequencer then reads EEPROM addresses 30h to FFh and each byte is moved into the ZX6017 on-board attribute memory addresses 00-CFh. After loading the registers and attribute memory, the sequencer completes by clearing the Ready/Busy pin on the PCMCIA interface indicating 1 "Ready." If EEPROM address 1Eh does not contain 1Ch, then the sequencer stops. The PCMCIA Ready/Busy pin stays in the Busy state, the on-board registers of the ZX6017 remain in their default state, and attribute memory data is unknown. The user can program the off-board EEPROM through the PCMCIA interface by means of three special registers and ignore Busy.

Figure 2. Serial Port Master Mode Control

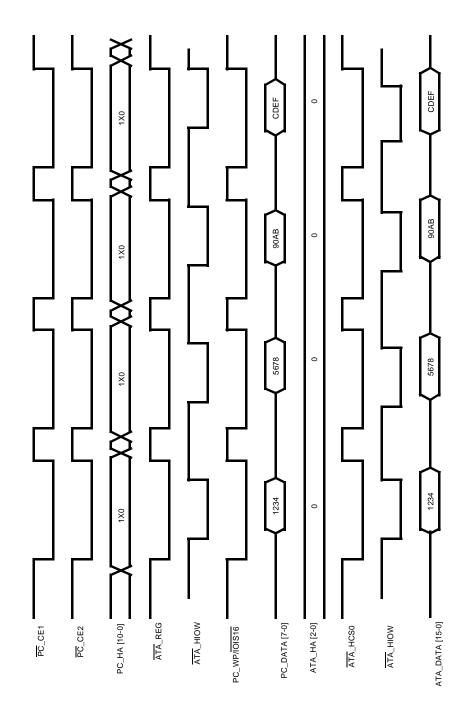

### Serial Port Operation (SLAVE) Mode

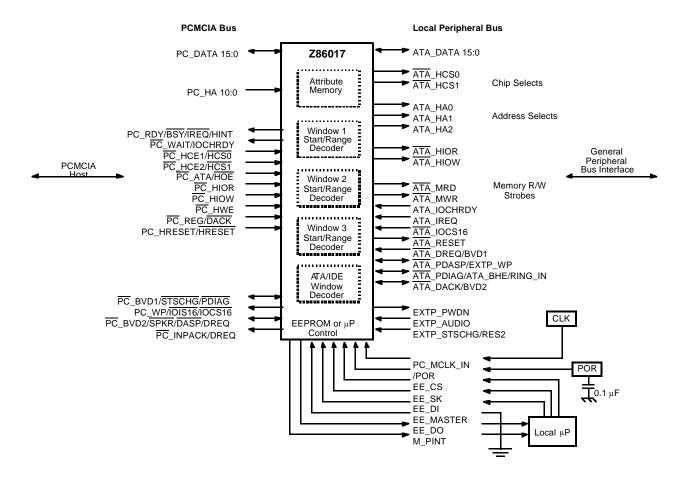

When the ZX6017 is placed in serial port SLAVE mode (EE\_Master signal grounded on POR), the EEPROM sequencer is disabled and the user must provide external hardware (microprocessor) with serial interface to program CCRs and attribute memory. Additionally, if the

POR signal is deasserted, the user must provide a clock source on the PC\_MCLK\_IN pin in the range of 1-20MHz.

The external hardware can program the on-board registers and the attribute memory by selecting the ZX6017 and pulling the EE\_CS pin High. The external hardware must set up the data to be sent to the ZX6017 on the EE\_DI pin and strobe the EE\_SK pin. The first byte of data is the address selected by the user, the second byte is the command byte and the third byte is the data. The external hardware must provide 24 clocks in order to read or write to a location in the ZX6017 (see Figure 26, Slave Interface Timing, in Appendix B).

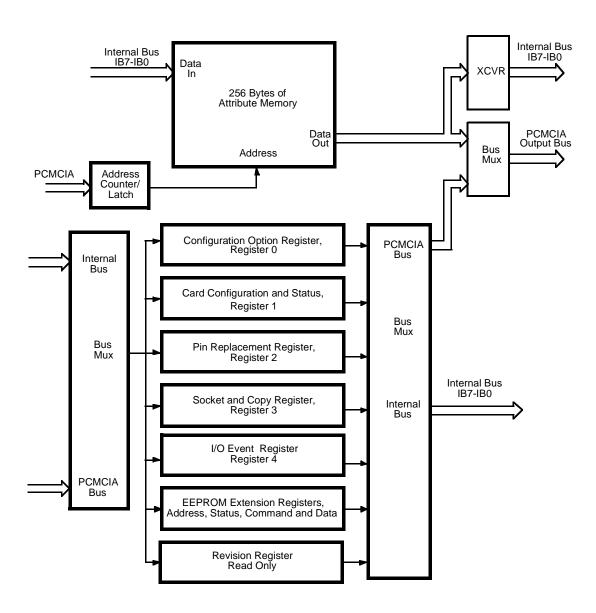

To program the on-board attribute memory, the user must first write to it. Accomplish this programming by writing the address location of the attribute memory to be written (or read) in the attribute RAM data address register at location 08h. When this step has been accomplished, the user then writes (or reads) the attribute RAM data register 09h with the data to be read or written at that location.

**Note:** The attribute RAM address register auto-increments after reading or writing to the attribute RAM data register.

Figure 3 demonstrates programming the ZX6017 in SLAVE Mode. The external user's hardware writes to register 00 and selects the clock divide by and the override mode (if needed). The READY/BUSY pin remains set to 0 to indicate BUSY, and a local μP interrupt polarity is selected.

The user programs registers 01-05, followed by registers 0Ah-2Fh. The user writes to the attribute memory by setting the address in the address register 08h and in the loop on data register 09h with the user's attribute memory data. The user completes the operation by writing back to register 00 to clear the READY/READY status.

Figure 3. Serial Port Slave Mode Control

# **EEPROM Programming Through the PCMCIA Interface**

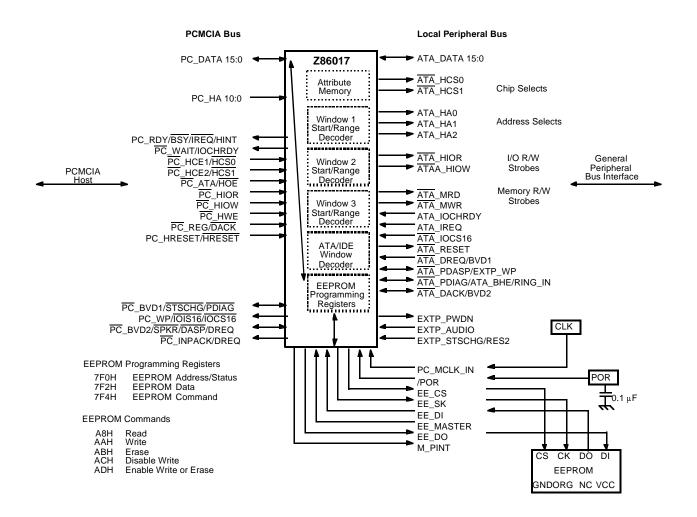

The ZX6017 can program the serial EEPROM through the PCMCIA interface. EEPROM programming is accomplished by means of three special registers that are accessed identically to the CCR registers as defined by the PCMCIA specification (Figure 4). These registers are fixed at addresses 7F0, 7F2, and 7F4. The host software reads and writes each byte of the EEPROM through these registers and configures the

ZX6017 device. After the host writes new values to the EEPROM through these registers, the new values are loaded into the ZX6017 at Power-On Reset (POR).

Note: The values written to register 05h offset the CCR registers and the three special EEPROM programming registers on the next POR.

Figure 4. EEPROM Programming Through the PCMCIA Interface

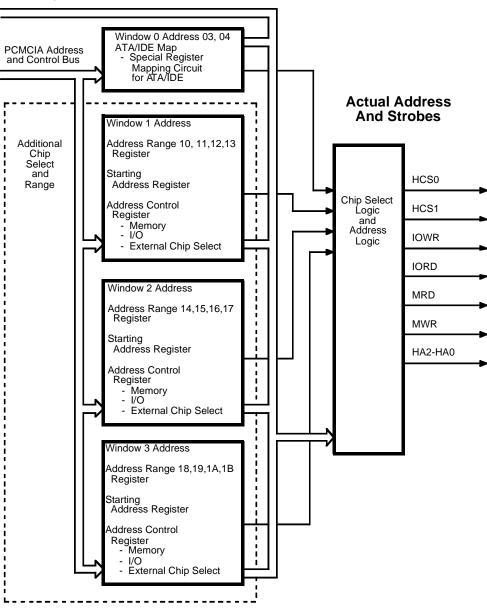

#### **Address Mapping Circuit**

Internal Bus, IB7-IB0 and Controls

Figure 5. Connection Block Diagram

Figure 6. Serial Interface Diagram

Figure 7. Attribute and Configuration Memory Diagram

#### PIN DESCRIPTION

Figure 8. ZX6017 100-Pin VQFP Pin Configuration

Figure 9. Z86M17 and Z16M17 (Mirror Image) 100-Pin VQFP Pin Configuration

### PIN IDENTIFICATION

Table 3. 100-Pin VQFP Pin Identification

| ZX6017 | M17 | Name                 | Description                                    |

|--------|-----|----------------------|------------------------------------------------|

| 1      | 75  | PC_HA0               | PCMCIA Address, Bit 0                          |

| 2      | 74  | PC_BVD1/STSCHG/PDIAG | Battery Voltage Detect 1, Status Change, PDiag |

| 3      | 73  | PC_DATA0             | PCMCIA Data, Bit 0                             |

| 4      | 72  | PC_DATA8             | PCMCIA Data, Bit 8                             |

| 5      | 71  | V <sub>SS</sub>      | Ground                                         |

| 6      | 70  | PC_DATA1             | PCMCIA Data, Bit 1                             |

| 7      | 69  | PC_DATA9             | PCMCIA Data, Bit 9                             |

| 8      | 68  | PC_DATA2             | PCMCIA Data, Bit 2                             |

| 9      | 67  | PC_DATA10            | PCMCIA Data, Bit 10                            |

| 10     | 66  | PC_WP/IOIS16/IOCS16  | Write Protect PCMCIA I/O Is 16-Bit Transfers   |

| 11     | 65  | ATA_HRESET           | AT Host RESET                                  |

| 12     | 64  | ATA_DATA7            | AT Host Data, Bit 7                            |

| 13     | 63  | ATA_DATA8/RES1       | AT Host Data, Bit 8, Reserved Input 1          |

| 14     | 62  | $V_{\mathrm{DD}}$    | Supply Voltage                                 |

| 15     | 61  | V <sub>SS</sub>      | Ground                                         |

| 16     | 60  | ATA_DATA6            | AT Host Data, Bit 6                            |

| 17     | 59  | ATA_DATA9/PACK_IN    | AT Host Data, Bit 9, PACK_IN                   |

| 18     | 58  | ATA_DATA5            | AT Host Data, Bit 5                            |

| 19     | 57  | ATA_DATA10           | AT Host Data, Bit 10                           |

| 20     | 56  | V <sub>SS</sub>      | Ground                                         |

| 21     | 55  | ATA_DATA4            | AT Host Data, Bit 4                            |

RM001103-0202

**PCMCIA Interface Overview**

Table 3. 100-Pin VQFP Pin Identification (Continued)

| ZX6017 | M17 | Name            | Description                 |

|--------|-----|-----------------|-----------------------------|

| 22     | 54  | ATA_DATA11      | AT Host Data, Bit 11        |

| 23     | 53  | ATA_DATA3       | AT Host Data, Bit 3         |

| 24     | 52  | V <sub>DD</sub> | Supply Voltage              |

| 25     | 51  | ATA_DATA12      | AT Host Data, Bit 12        |

| 26     | 50  | ATA_DATA2       | AT Host Data, Bit 2         |

| 27     | 49  | ATA_DATA13      | AT Host Data, Bit 13        |

| 28     | 48  | ATA_DATA1       | AT Host Data, Bit 1         |

| 29     | 47  | ATA_DATA14      | AT Host Data, Bit 14        |

| 30     | 46  | ATA_DATA0       | AT Host Data, Bit 0         |

| 31     | 45  | ATA_DATA15      | AT Host Data, Bit 15        |

| 32     | 44  | V <sub>SS</sub> | Ground                      |

| 33     | 43  | ATA_HIOW        | AT Host I/O Write Strobe    |

| 34     | 42  | ATA_HIOR        | AT Host I/O Read Strobe     |

| 35     | 41  | ATA_IOCHRDY     | AT Host I/O Channel Ready   |

| 36     | 40  | ATA_IREQ        | AT Host Interrupt Request   |

| 37     | 39  | ATA_IOCS16      | AT Host I/O Is 16 Bits Wide |

| 38     | 38  | V <sub>DD</sub> | Supply Voltage              |

| 39     | 37  | ATA_HA1         | AT Host Address, Bit 1      |

| 40     | 36  | ATA_HA0         | AT Host Address, Bit 0      |

| 41     | 35  | ATA_HA2         | AT Host Address, Bit 2      |

| 42     | 34  | ATA_HCS0        | AT Host Chip Select 0       |

| 43     | 33  | ATA_HCS1        | AT Host Chip Select 1       |

**PCMCIA Interface Overview**

Table 3. 100-Pin VQFP Pin Identification (Continued)

| ZX6017 | M17 | Name                          | Description                                      |

|--------|-----|-------------------------------|--------------------------------------------------|

| 44     | 32  | $V_{SS}$                      | Ground                                           |

| 45     | 31  | ATA_PDIAG/ATA_BHE/<br>Ring_IN | PDIAG I/O, Byte High Enable, RING_IN             |

| 46     | 30  | ATA_PDASP/EXTP_WP             | PDASP I/O or Write Protect In                    |

| 47     | 29  | ATA_DACK/BVD2                 | AT Host DMA Acknowledge, Battery Voltage Input 2 |

| 48     | 28  | ATA_DREQ/BVD1                 | AT Host DMA Request, Battery Voltage Input 1     |

| 49     | 27  | ATA_MRD                       | AT Host Memory Read Strobe                       |

| 50     | 26  | EE_SK                         | EEPROM Data Clock                                |

| 51     | 25  | EE_MASTER                     | EEPROM Is Master                                 |

| 52     | 24  | EE_CS                         | EEPROM Data Chip Select                          |

| 53     | 23  | EE_DO                         | EEPROM Data Out                                  |

| 54     | 22  | EE_DI                         | EEPROM Data In                                   |

| 55     | 21  | ATA_MWR                       | AT Host Memory Write Strobe                      |

| 56     | 20  | POR                           | Power-On Reset                                   |

| 57     | 19  | M_PINT                        | Local Processor Interrupt                        |

| 58     | 18  | PC_MCLK_IN                    | Master Clock In                                  |

| 59     | 17  | EXTP_PWDN                     | Power Down Output                                |

| 60     | 16  | EXTP_AUDIO                    | Audio Input                                      |

| 61     | 15  | EXTP_STSCHG/RES2              | Status Change Input, Reserved Input 2            |

| 62     | 14  | $V_{\mathrm{DD}}$             | Supply Voltage                                   |

| 63     | 13  | PC_DATA3                      | PCMCIA Data, Bit 3                               |

| 64     | 12  | PC_DATA4                      | PCMCIA Data, Bit 4                               |

Table 3. 100-Pin VQFP Pin Identification (Continued)

| ZX6017 | M17 | Name                 | Description                            |

|--------|-----|----------------------|----------------------------------------|

| 65     | 11  | PC_DATA11            | PCMCIA Data, Bit 11                    |

| 66     | 10  | PC_DATA5             | PCMCIA Data, Bit 5                     |

| 67     | 9   | PC_DATA12            | PCMCIA Data, Bit 12                    |

| 68     | 8   | V <sub>SS</sub>      | Ground                                 |

| 69     | 7   | PC_DATA6             | PCMCIA Data, Bit 6                     |

| 70     | 6   | PC_DATA13            | PCMCIA Data, Bit 13                    |

| 71     | 5   | PC_DATA7             | PCMCIA Data, Bit 7                     |

| 72     | 4   | PC_DATA14            | PCMCIA Data, Bit 14                    |

| 73     | 3   | V <sub>DD</sub>      | Supply Voltage                         |

| 74     | 2   | PC_HCE1/HCS0         | PCMCIA Card Enable 1 ATA Chip Select 0 |

| 75     | 1   | PC_DATA15            | PCMCIA Data, Bit 15                    |

| 76     | 100 | PC_HA10              | PCMCIA Address, Bit 10                 |

| 77     | 99  | V <sub>SS</sub>      | Ground                                 |

| 78     | 98  | PC_HCE2/HCS1         | PCMCIA Card Enable 2 ATA Chip Select 1 |

| 79     | 97  | PC_ATA/HOE           | Mode Select/PCMCIA Output Enable       |

| 80     | 96  | PC_HIOR              | PCMCIA I/O Read Strobe                 |

| 81     | 95  | PC_HIOW              | PCMCIA I/O Write Strobe                |

| 82     | 94  | $V_{\mathrm{DD}}$    | Supply Voltage                         |

| 83     | 93  | PC_HA9               | PCMCIA Address, Bit 9                  |

| 84     | 92  | PC_HA8               | PCMCIA Address, Bit 8                  |

| 85     | 91  | PC_HWE               | PCMCIA Write Enable                    |

| 86     | 90  | PC_RDY/BSY/IREQ/HINT | PCMCIA Ready/Busy, Interrupt Request   |

**PCMCIA Interface Overview**

Table 3. 100-Pin VQFP Pin Identification (Continued)

| ZX6017 | M17 | Name                       | Description                                                    |

|--------|-----|----------------------------|----------------------------------------------------------------|

| 87     | 89  | PC_HA7                     | PCMCIA Address, Bit 7                                          |

| 88     | 88  | V <sub>SS</sub>            | Ground                                                         |

| 89     | 87  | PC_HA6                     | PCMCIA Address, Bit 6                                          |

| 90     | 86  | PC_HA5                     | PCMCIA Address, Bit 5                                          |

| 91     | 85  | PC_HA4                     | PCMCIA Address, Bit 4                                          |

| 92     | 84  | PC_HRESET/HRESET           | PCMCIA Reset                                                   |

| 93     | 83  | $V_{\mathrm{DD}}$          | Supply Voltage                                                 |

| 94     | 82  | PC_WAIT/IOCHRDY            | PCMCIA Wait, /IOCHRDY                                          |

| 95     | 81  | PC_HA3                     | PCMCIA Address, Bit 3                                          |

| 96     | 80  | PC_INPACK/DREQ             | PCMCIA Input Acknowledge, DREQ                                 |

| 97     | 79  | PC_HA2                     | PCMCIA Address, Bit 2                                          |

| 98     | 78  | PC_REG/DACK                | PCMCIA Register Signal, DACK                                   |

| 99     | 77  | PC_HA1                     | PCMCIA Address, Bit 1                                          |

| 100    | 76  | PC_BVD2/SPKR/DASP/<br>DREQ | PCMCIA Battery Voltage Detect 2, Speaker<br>Output, DASP, DREQ |

19

#### **PIN FUNCTIONS**

### **PCMCIA Signals**

PC\_DATA<15:0> (I/O, Tristate, 8 mA)

PCMCIA Mode: 16-bit host Data bus.

ATA/IDE Mode: 16-bit host Data bus.

• PC\_HA<10:3> (*Input*)

PCMCIA Mode: Host Address lines: 10,9,8,7,6,5,4,3.

ATA/IDE Mode: Not used.

• PC\_HA<2:0> *I(nput)*

PCMCIA Mode: Host Address lines: 2,1,0. ATA/IDE Mode: Host Address lines: 2,1,0.

• PC\_HCE1/HCS0 (Input, 100K Pull-Up)

PCMCIA Mode: This signal is Card Enable 1 (active Low).

ATA/IDE Mode: Host Chip Select 0 (active Low).

• PC\_HCE2/HCS1 (Input, 100K Pull-Up)

PCMCIA Mode: This signal is Card Enable 2 (active Low).

ATA/IDE Mode: Host Chip Select 1 (active Low).

• PC\_REG/DACK (Input, 100K Pull-Up)

PCMCIA Mode: (/REG), Register bit is asserted when the host

selects I/O or Attribute Memory.

ATA/IDE Mode: Data acknowledge (/DACK) defined in ATA. Issued

during DMA data transfers on the data bus.

•  $\overline{PC}_ATA/\overline{HOE}$  (Input, 100K Pull-Up)

PCMCIA Mode: Memory Output Enable Strobe.

ATA/IDE Mode: When pulled Low on Power-On Reset, this signal indicates ATA/IDE mode.

• PC\_HWE (Input, 100K Pull-Up)

PCMCIA Mode: Memory Write Enable Strobe.

ATA/IDE Mode: Not used.

• PC\_HIOR (Input, 100K Pull-Up)

PCMCIA Mode: In PCMCIA I/O mode, this is the Input/Output Read Strobe.

ATA/IDE Mode: Input/Output Read Strobe.

• PC\_HIOW (Input, 100K Pull-Up)

PCMCIA Mode: In PCMCIA I/O mode, this is the Input/Output Write Strobe.

ATA/IDE Mode: Input/Output Write Strobe.

- PC\_HRESET/HRESET(Input, Schmitt-Triggered, 100K Pull-Up)

PCMCIA Mode: Active High input Reset signal.

ATA/IDE Mode: Active Low input Reset signal.

- PC\_RDY/BSY/IREQ/HINT (Output, 8 mA)

PCMCIA Mode: In PCMCIA memory mode, this signal is READY/BUSY. This signal will be asserted BUSY by the RESET logic. In PCMCIA I/O mode, this signal is /IREQ.

ATA/IDE Mode: When enabled, the HINT signal is used to interrupt the host (active High).

- PC\_WP/IOIS16/IOCS16 (Output, Tri-State, 8 mA)

PCMCIA Mode: In PCMCIA memory mode, this signal is Write

Protected. In PCMCIA I/O mode, this signal is IOIS16 and indicates

that a 16-bit capable I/O device is being accessed on the PCMCIA

bus.

ATA/IDE Mode: I/O chip select 16 indicates that a 16- bit transfer is active on the bus.

- PC\_WAIT/IOCHRDY (Output, Tri-State, 8 mA)

PCMCIA Mode: Insert Wait States when held active and the chip is being selected in I/O or memory mode.

ATA/IDE Mode: Inserts Wait States when held active, and when the chip is being selected.

- PC\_INPACK/DREQ (Output, Tri-State, 8 mA)

PCMCIA Mode: In PCMCIA I/O mode this signal is Input

Acknowledge. It is asserted by the card when the card is selected and

21

can respond to an I/O cycle at the address on the address bus. ATA/IDE Mode: This signal is Data request (DREQ), defined in ATA. It is issued during DMA data transfers on the data bus.

- PC\_BVD1/STSCHG/PDIAG (I/O, 8 mA)

PCMCIA Memory Mode: Battery Voltage Detect 1, output.

PCMCIA I/O Mode: Status Changed. This signal is used to indicate the change of status in the Pin Replacement Register (I/O Mode) or state of the BVD1 input when in Memory Mode.

ATA/IDE Mode: Passed diagnostics.

- PC\_BVD2/SPKR/DASP/DREQ (I/O, Tri-State, 10 mA)

PCMCIA Memory Mode: Battery Voltage Detect 2, output.

PCMCIA I/O Mode: SPKR, inverted AUDIO\_EXTP signal, output;

PCMCIA ATA Mode: ATA Data Request is the input pin for this signal, when DMA Enable bit is set in Window Start/Range Address registers.

ATA/IDE Mode: Drive active/Slave present DASP.

• ATA\_DATA<15:10> (I/O, Tri-State, 8 mA) ATA/IDE Mode: Host Data Bus, bits: 15,14,13,12,11,10.

**PCMCIA Interface Overview**

### Peripheral or ATA/IDE Signals

- ATA\_DATA<15:10> (I/O, Tri-State, 8 mA) ATA/IDE Mode: Host Data Bus, bits: 15,14,13,12,11,10. Peripheral Mode: Peripheral data bus, bits: 15, 14, 13, 12, 11,10.

- ATA\_DATA9/PACK\_IN (I/O, Tri-State, 8 mA)

ATA/IDE Mode: Host Data Bus, bit: 9.

Peripheral Mode: When 8-bit mode is enabled (on the Local side)

ATA\_DATA9 can be used as a PACK\_IN input.

- ATA\_DATA8/RES1 (I/O, Tri-State, 8 mA)

ATA/IDE Mode: Host Data Bus, bit: 8.

Peripheral Mode: When 8-bit mode is enabled (on the Local side),

ATA\_DATA8 can be used as a RES1 input.

- ATA\_DATA<7:0> (I/O, Tri-State, 8 mA) ATA/IDE Mode: Host Data Bus, bits: 7,6,5,4,3,2,1,0. Peripheral Mode: Peripheral Data Bus, bits: 7,6,5,4,3,2,1,0.

- ATA\_HA<2:0> (Output, 8 mA)

ATA/IDE Mode: ATA Host Address bits used to address the IDE interface chip.

Peripheral Mode: Lower three bits offset from starting address.

- ATA\_HCS0 (Output, 8 mA)

ATA/IDE Mode: ATA Host Chip Select 0, used to select the IDE interface chip.

Peripheral Mode: Chip Select 0 used as a chip select for an external peripheral device as defined by the address range and offset register definition.

- ATA\_HCS1 (Output, 8 mA)

ATA/IDE Mode: ATA Host Chip Select 1, used to select the IDE interface chip.

Peripheral Mode: Chip Select 1 used as a chip select for an external peripheral device as defined by the address range and offset register definition.

7

23

•  $\overline{ATA}$ \_HIOR (Output, 8 mA)

ATA/IDE Mode: ATA Host I/O Read Strobe.

Peripheral Mode: I/O read strobe or memory read strobe, depending

on configuration.

•  $\overline{ATA}$ \_HIOW (Output, 8 mA)

ATA/IDE Mode: ATA Host I/O Write Strobe.

Peripheral Mode: I/O Write Strobe or Memory Write Strobe,

depending on configuration.

• ATA IOCS16 (Input, 100K Pull-Up)

ATA/IDE Mode: I/O channel is 16 bits wide; input on the local ATA

bus.

Peripheral Mode: I/O access is 16 bits wide.

ATA\_IREQ (Input)

ATA/IDE Mode: ATA/IDE host Interrupt Request.

Peripheral Mode: Interrupt Request.

• ATA IOCHRDY (Input, 100K Pull-Up)

ATA/IDE Mode: ATA/IDE I/O Channel Ready-Input.

Peripheral Mode: I/O Channel Ready.

• ATA\_HRESET (Output, 8 mA)

ATA/IDE Mode: ATA Host Reset-Output to the ATA/IDE controller

(programmable).

Peripheral Mode: Host reset output to the peripheral device if

PCMCIA signal is active (programmable).

ATA\_DREQ/BVD1 (Input)

ATA/IDE Mode: ATA/IDE DMA request from the ATA/IDE

controller.

Peripheral Mode: Peripheral bus DMA Request or when in memory

mode Battery Voltage 1 Detect input.

• ATA\_DACK/BVD2 (I/O, 8 mA)

ATA/IDE Mode: ATA/IDE host DMA Acknowledge.

Peripheral Mode: Peripheral Bus DMA Acknowledge. DMA

24

acknowledge is generated by the ZX6017 whenever DMA Acknowledge is enabled in the Window Start/Range Address registers and the address corresponds to the DMA address; or Battery Voltage 2 Detect input in memory mode.

- ATA\_PDASP/EXTP\_WP (I/O, Tri-State, 8 mA)

ATA/IDE Mode: ATA/IDE bus side PDASP signal controlled by internal bits ZEN\_EXT\_PDASP (Input) or ZEN\_INT\_PDASP (Output).

Peripheral Mode: When configured as a Write Protect input, this pin will disable Write on the peripheral bus side.

- ATA\_PDIAG/ATA\_BHE/RING\_IN (I/O, Tri-State, 8 mA)

ATA/IDE Mode: ATA/IDE bus side PDIAG signal controlled by

internal bits ZEN\_EXT\_PDIAG (Input) or ZEN\_INT\_PDIAG

(Output).

Peripheral Mode: When configured as Byte High Enable for memory

boards, ATA\_BHE indicates High byte available, or it can be

configured to be the RING\_IN input signal for the I/O event indicator

CCR4.

- ATA\_MRD (Output, 8 mA)

ATA/IDE Mode: Not used.

Peripheral Mode: External Memory Read Strobe.

- ATA\_MWR (Output, 8 mA)

ATA/IDE Mode: Not used.

Peripheral Mode: External Memory Write Strobe.

### **Serial Interface Signals**

• EE DO (Output, 8 mA, Tri-State)

Master Mode: EEPROM data out Serial data, valid during EE\_SK edge. In master mode, this signal is an output.

Slave Mode: In slave mode, this signal is an output.

• EE SK (I/O, 8 mA)

Master Mode: EEPROM data clock. This signal is an output in master mode. It is active during R/W cycle only.

Slave Mode: In slave mode, this signal is an input.

• EE CS (I/O, 8 mA)

Master Mode: EEPROM data chip select. This signal is an output in master mode.

Slave Mode: In slave mode this signal is an input. This signal is active High.

• EE\_DI (*Input*, 100K Pull-Up)

Master Mode: EEPROM data in. This signal is an input in master mode.

Slave Mode: In slave mode, this signal is an input.

• EE\_MASTER (Input, Schmitt-Triggered, 100K Pull-Up)

Master/Slave mode detect: When set Low, no EEPROM is present.

When set High EEPROM is present.

### **Peripheral Control Signals**

- POR (Input, Schmitt-Triggered, 100K Pull-Up)

Local Power-On Reset signal. A 0.1mF capacitor is recommended on this pin to GND to generate a POR.

- M\_PINT (Output, Tri-State, 8 mA)

Interrupt to local microprocessor

- PC\_MCLK\_IN (Input, Schmitt-Triggered)

Master Clock In. This is an input signal. This clock signal is used to generate all internal timing. All local bus signals are asynchronous to this clock.

- EXTP\_STSCHG/RES2 (Input, 100K Pull-Up)

Status Change Input. This signal outputs the value of the status changed line on the PCMCIA bus if enabled in the CCR register, or it is an input for bit 7 (RSVDEVT3) in CCR4.

- EXTP\_AUDIO (Input 100K Pull-Up)

Audio Input. This input signal reflects the audio output. This signal is active High, and the Speaker output on the PCMCIA bus is active Low.

- EXTP\_PWDN (Output, 8 mA)

Power Down Output. This signal reflects the state of the Power Down bit in the CCR.

- V<sub>SS</sub> (*Input*) Ground.

- V<sub>DD</sub> (Input)

Supply Voltage.

### Addressing Modes

The ZX6017 supports all PCMCIA Addressing Modes:

- PCMCIA Common Memory Mode

- PCMCIA I/O Mode

- PCMCIA ATA IDE Mode

- Pass-through ATA/IDE-to-ATA/IDE Mode

Note: This mode is for users who have a 68-pin PCMCIA connector, but are using ATA/IDE protocol instead of PCMCIA protocol.

The overall ZX6017 mode of operation is controlled by the Interface Configuration Register (00h) bits 3,2. 00 in these two bits sets the device to ATA/IDE mode if the  $\overline{PC}$ \_ATA/ $\overline{HOE}$  pin is Low on power-up and into PCMCIA mode if the pin is High. The default for this register is 00 and the  $\overline{PC}$ \_ATA/ $\overline{HOE}$  pin determines the mode of operation, PCMCIA or ATA/IDE. Table 4 describes these addressing modes.

**Table 4. ZX6017 Addressing Modes**

| Mode/Bus          | PCMCIA  | Peripheral Bus | Comments                               |

|-------------------|---------|----------------|----------------------------------------|

| Memory            | Memory  | Memory         |                                        |

| I/O               | I/O     | I/O            |                                        |

| PCMCIA_ATA_Memory | Memory  | ATA            |                                        |

| PCMCIA_ATA_I/O    | I/O     | Primary ATA    | Contiguous block of at least 16        |

|                   |         | Secondary ATA  | I/O registers is assigned to one card. |

|                   |         | Contiguous ATA |                                        |

| Pass-Through Mode | ATA/IDE | ATA/IDE        |                                        |

Addressing Modes RM001103-0202

28

To place the ZX6017 into proper Addressing mode, a set of Configuration Registers and Memory Maps reside on-chip.

The four on-chip address maps are:

- Memory\_Map\_1

- Memory Map 2

- Memory\_Map\_3

- PCMCIA\_ATA/IDE Map

Memory\_Map\_1, \_2 and \_3 support PCMCIA Memory/IO Mode. The chip can be configured in PCMCIA Mode either by:

- Pulling the PC\_ATA/HOE pin High during RESET;

or by

- Writing 10 in Override bits (bits 3, 2) in the Interface Configuration Register 0 (address 00h), and 0 in bits 0, 1, 2, 6 of the Interface Configuration Register 02 (address 03h).

After placing the device into PCMCIA Mode, each Map can be configured independently through its set of configuration registers.

Each Memory Map contains a set of Configuration Registers consisting of:

- Window Control Register

- Window Start Address LSB Register

- Window Start/Range Address MSB

- Window Range Address LSB

The PCMCIA\_ATA/IDE Map enables chip operation in PCMCIA\_ATA/IDE mode. When in this mode, the chip responds to different types of accesses, depending on the content of the following registers:

• Interface Configuration Register 02, address 03h (bits 0, 1, 6)

RM001103-0202

Addressing Modes

29

- Interface Configuration Register 03, address 04h (bits 0, 1, 2, 3)

- PCMCIA Exception Status Register, address 071h (bit 0)

Table 5 describes programming PCMCIA\_ATA ZX6017 Configuration Registers.

Table 5. Programming PCMCIA\_ATA ZX6017 Configuration Registers

| ICR_2<br>[1:0]<br>addr03 | ICR_02[6]<br>addr03 | ICR_03[3:0]<br>addr04 | CICR_1[7:0]<br>addr2DH | CICR_2[7:0]<br>addr2EH | CCR0[5:0]<br>addr0AH | addr<br>07[0} | Description                                                                    |

|--------------------------|---------------------|-----------------------|------------------------|------------------------|----------------------|---------------|--------------------------------------------------------------------------------|

| X                        | X                   | XXXX                  | xxxxxxxx               | xxxxxxxx               | XXXXX                | 1             | Chip operates<br>in ATA/IDE-<br>to-ATA/IDE<br>passthrough<br>mode              |

| 11                       | 0                   | XXXX                  | xxxxxxx                | xxxxxxx                | xxxxx                | 0             | PCMCIA<br>Mode                                                                 |

| 11                       | 1                   | 1111                  | FFH                    | FFH                    | 00011                | 0             | Enabled access to Primary set of IDE Task File Registers (1Fo-1F7)             |

| 11                       | 1                   | 1111                  | FFH                    | FFH                    | 00011                | 0             | Enabled access<br>to Primary set<br>of IDE Task<br>File Registers<br>(3F6-3F7) |

Addressing Modes RM001103-0202

Table 5. Programming PCMCIA\_ATA ZX6017 Configuration Registers

| ICR_2<br>[1:0]<br>addr03 | ICR_02[6]<br>addr03 | ICR_03[3:0]<br>addr04 | CICR_1[7:0]<br>addr2DH | CICR_2[7:0]<br>addr2EH | CCR0[5:0]<br>addr0AH | addr<br>07[0} | Description                                                                                               |

|--------------------------|---------------------|-----------------------|------------------------|------------------------|----------------------|---------------|-----------------------------------------------------------------------------------------------------------|

| 11                       | 1                   | 1111                  | FFH                    | FFH                    | 00010                | 0             | Enabled access<br>to Secondary<br>set of IDE Task<br>File Registers                                       |

| 11                       | 1                   | 1111                  | FFH                    | FFH                    | 00001                | 0             | PCMCIA_AA<br>Independent<br>IO Mode. Chip<br>responds to<br>any 1/0 access<br>in the range<br>000 to 00Fh |

| 11                       | 1                   | 1111                  | FFH                    | FFH                    | 00000                | 0             | PCMCIA Independent Memory                                                                                 |

|                          |                     |                       |                        |                        |                      |               | Mode. Chip responds                                                                                       |

|                          |                     |                       |                        |                        |                      |               | to any Memory                                                                                             |

|                          |                     |                       |                        |                        |                      |               | access in the                                                                                             |

|                          |                     |                       |                        |                        |                      |               | range 000-<br>00Fh                                                                                        |

Tables 6 through Table 9 provide ZX6017 addressing information in each mode.

RM001103-0202 Addressing Modes

31

**Table 6. PCMCIA Common Memory Mode**

| <b>Function Mode</b> | REG | CE2 | CE1 | <b>A</b> 0 | <u>0E</u> | WE | D15-D8   | D7-D0     |

|----------------------|-----|-----|-----|------------|-----------|----|----------|-----------|

| Standby Mode         | X   | Н   | Н   | X          | X         | X  | High-Z   | High-Z    |

| Byte Access          | Н   | Н   | L   | L          | L         | Н  | High-Z   | Even-Byte |

|                      | Н   | Н   | L   | Н          | L         | Н  | High-Z   | Odd-Byte  |

| Word Access          | Н   | L   | L   | Z          | L         | Н  | Odd-Byte | Even-Byte |

| Odd-Byte only access | Н   | L   | Н   | X          | Н         | L  | Odd-Byte | XX        |

Table 7. PCMCIA I/O Mode

| <b>Function Mode</b> | REG | CE2 | CE1 | <b>A</b> 0 | <del>OE</del> | WE | D15-D8   | D7-D0     |

|----------------------|-----|-----|-----|------------|---------------|----|----------|-----------|

| Standby Mode         | X   | Н   | Н   | X          | X             | X  | High-Z   | High-Z    |

| Byte Access          | Н   | Н   | L   | L          | L             | Н  | High-Z   | Even-byte |

|                      | Н   | Н   | L   | Н          | L             | Н  | High-Z   | Odd-byte  |

| Word Access          | Н   | L   | L   | Z          | L             | Н  | Odd-byte | Even-byte |

| I/O Inhibit          | Н   | X   | X   | X          | L             | Н  | High-Z   | High-Z    |

| Odd-byte only access | L   | L   | Н   | X          | L             | Н  | Odd-byte | High-Z    |

| Byte Access          | L   | Н   | L   | L          | Н             | L  | X        | Even-byte |

|                      | L   | Н   | L   | Н          | Н             | L  | X        | Odd-Byte  |

| Word Access          | L   | L   | L   | L          | Н             | L  | Odd-byte | Even-byte |

| I/O Inhibit          | Н   | X   | X   | X          | Н             | L  | X        | X         |

| Odd-byte only access | L   | L   | Н   | X          | Н             | L  | Odd-byte | X         |

Addressing Modes RM001103-0202

Table 8. PCMCIA\_ATA Memory Mapped Access

| REG# | A10 | A[9:4] | <b>A3</b> | A2 | <b>A</b> 1 | <b>A</b> 0 | OE#             | WE#               |

|------|-----|--------|-----------|----|------------|------------|-----------------|-------------------|

| Н    | L   | X      | L         | L  | L          | L          | Read Data       | Write Data        |

| Н    | L   | X      | L         | L  | L          | Н          | Error           | Feature           |

| Н    | L   | X      | L         | L  | Н          | L          | Sector Count    | Sector Count      |

| Н    | L   | X      | L         | L  | Н          | Н          | Sector Number   | Sector Number     |

| Н    | L   | X      | L         | Н  | L          | L          | Cylinder Low    | Cylinder Low      |

| Н    | L   | X      | L         | Н  | L          | Н          | Cylinder High   | Cylinder High     |

| Н    | L   | X      | L         | Н  | Н          | L          | Drive/Head      | Drive/Head        |

| Н    | L   | X      | L         | Н  | Н          | Н          | Status          | Status            |

| Н    | L   | X      | Н         | L  | L          | L          | Duplicate Even  | Duplicate Even    |

|      |     |        |           |    |            |            | Read Data       | Write Data        |

| Н    | L   | X      | Н         | L  | L          | Н          | Duplicate Odd   | Duplicate Odd     |

|      |     |        |           |    |            |            | Read Data       | Write Data        |

| Н    | L   | X      | Н         | Н  | L          | Н          | Duplicate Error | Duplicate Feature |

| Н    | L   | X      | Н         | Н  | Н          | L          | Alt Status      | Device Control    |

| Н    | L   | X      | Н         | Н  | Н          | Н          | Drive Address   | Reserved          |

| Н    | Н   | X      | X         | X  | X          | L          | Even Read Data  | Even Write Data   |

| Н    | Н   | X      | X         | X  | X          | Н          | Odd Read Data   | Odd Write Data    |

RM001103-0202 Addressing Modes

33

Table 9. PCMCIA\_ATA I/O Mapped Access

| REG# | Primary<br>A[9:0] | Secondary<br>A[9:0] | Contiguous A[3:0] | IORD# = L                   | IOWR# = L                    |

|------|-------------------|---------------------|-------------------|-----------------------------|------------------------------|

| L    | 1F0H              | 170H                | 00H               | Read Data                   | Write Data                   |

| L    | 1F1H              | 171H                | 01H               | Error                       | Feature                      |

| L    | 1F2H              | 172H                | 02H               | Sector Count                | Sector Count                 |

| L    | 1F3H              | 173H                | 03H               | Sector Number               | Sector Number                |

| L    | 1F4H              | 174H                | 04H               | Cylinder Low                | Cylinder Low                 |

| L    | 1F5H              | 175H                | 05H               | Cylinder High               | Cylinder High                |

| L    | 1F6H              | 176H                | 06H               | Drive/Head                  | Drive/Head                   |

| L    | 1F7H              | 177                 | 07H               | Status                      | Command                      |

| L    | _                 | _                   | 08H               | Duplicate Even<br>Read Data | Duplicate Even<br>Write Data |

| L    | _                 | _                   | 09H               | Duplicate Odd               | Duplicate Odd                |

|      |                   |                     |                   | Read Data                   | Write Data                   |

| L    | _                 | _                   | 0DH               | Duplicate Error             | Duplicate<br>Feature         |

| L    | 1F6H              | 376H                | 0EH               | Alt Status                  | Device Control               |

| L    | 3F7H              | 377H                | 0FH               | Drive Access                | Reserved                     |

Addressing Modes RM001103-0202

3/

RM001103-0202 Addressing Modes

### Programming Internal Registers

#### INTRODUCTION

As stated in "Addressing Modes" on page 27, the ZX6017 devices feature a set of on-chip programmable registers that can be programmed either by using the on-board EEPROM Sequencer (MASTER Mode) or by Local Microprocessor (SLAVE Mode). A set of Card Configuration Registers can be accessed from the PCMCIA interface. Table 10 lists the programmable registers.

Table 10. ZX6017 Card Configuration Registers

| EEPROM<br>Address | PCMCIA<br>Address | Register's Name                                    | Access | POR<br>Value | Comments          |

|-------------------|-------------------|----------------------------------------------------|--------|--------------|-------------------|

| 00h               | NA                | Interface Configuration Rg 0                       | R/W    | 00h          |                   |

| 01h               | NA                | Interrupt Enable Rg                                | R/W    | 00h          |                   |

| 02h               | NA                | Interface Configuration Rg 1                       | R/W    | 00h          |                   |

| 03h               | NA                | Interface Configuration Rg 2                       | R/W    | 00h          |                   |

| 04h               | NA                | Interface Configuration Rg 3                       | R/W    | 00h          |                   |

| 05h               | NA                | PCMCIA CCR's Base Rg R/W                           |        | 00h          |                   |

| 06h               | NA                | PCMCIA Interrupt Status Rg                         | R      | 00h          | Note <sup>1</sup> |

| 07h               | NA                | PCMCIA Exception Status Rg                         | R      | 00h          | Note              |

| 08h               | NA                | Attribute RAM Address Rg                           | W      | XX           | Note              |

| 09h               | NA                | Attribute RAM Data Rg                              | R/W    | XX           | Notel             |

| 0Ah               | XX0h              | PCMCIA Configuration Option Rg (CCR0)              |        | 00h          | Note <sup>2</sup> |

| 0Bh               | XX2h              | PCMCIA Card Configuration and Status R/W Rg (CCR1) |        | 00h          | Note <sup>2</sup> |

| 0Ch               | XX4h              | PCMCIA Pin Replacement Rg (CCR2) R/W               |        | 00h          | Note <sup>2</sup> |

**Programming Internal Registers**

RM001103-0202

Table 10.

ZX6017 Card Configuration Registers (Continued)

| EEPROM<br>Address |      |                                               | Access | POR<br>Value | Comments                              |

|-------------------|------|-----------------------------------------------|--------|--------------|---------------------------------------|

| 0Dh               | XX6h | PCMCIA Socket and Copy Rg (CCR3)              | R/W    | 00h          | Note <sup>2</sup>                     |

| 0Eh-0Fh           |      | Reserved                                      |        | XX           |                                       |

| 10h               | NA   | Window 1 Control Rg                           | R/W    | 01h          |                                       |

| 11h               | NA   | Window 1 Start Address LSB Rg                 | R/W    | 00h          |                                       |

| 12h               | NA   | Window 1 Start/Range Address MSB Rg           | R/W    | 00h          |                                       |

| 13h               | NA   | Window 1 Range Address LSB Rg                 | R/W    | 00h          |                                       |

| 14h               | NA   | Window 2 Control Rg                           | R/W    | 01h          |                                       |

| 15h               | NA   | Window 2 Start Address LSB Rg                 | R/W    | 00h          |                                       |

| 16h               | NA   | Window 2 Start/Range Address MSB Rg           | R/W    | 00h          |                                       |

| 17h               | NA   | Window 2 Range Address LSB Rg                 | R/W    | 00h          |                                       |

| 18h               | NA   | Window 3 Control Rg                           | R/W    | 01h          |                                       |

| 19h               | NA   | Window 3 Start Address LSB Rg                 | R/W    | 00h          |                                       |

| 1Ah               | NA   | Window 3 Start/Range Address MSB Rg           | R/W    | 00h          |                                       |

| 1Bh               | NA   | Window 3 Range Address LSB Rg                 | R/W    | 00h          |                                       |

| 1Ch-1Dh           |      | Reserved                                      |        | XX           |                                       |

| 1Eh               | NA   | EEPROM Valid Flag Byte Rg (1Ch)               | R/W    | 00h          | Master Mode only                      |

| 1Fh               | XX8h | PCMCIA I/O Event Indication Rg<br>(CCR4)      | R/W    | 00h          | Note <sup>2</sup> , Note <sup>3</sup> |

| 20h               | 7F0h | EEPROM Addr/Status Rg (CCR5) Back R/W<br>Door |        | 00h          | Note <sup>1</sup>                     |

| 21h               | 7F2h | EEPROM Data Rg (CCR6) Back Door R/W 00h No    |        | Note         |                                       |

| 22h               | 7F4h | EEPROM Command Rg (CCR7) Back<br>Door         | R/W    | 00h          | Note <sup>1</sup>                     |

Table 10. ZX6017 Card Configuration Registers (Continued)

| EEPROM<br>Address | PCMCIA<br>Address | Register's Name                       | Access | POR<br>Value | Comments          |

|-------------------|-------------------|---------------------------------------|--------|--------------|-------------------|

| 23h               | NA                | Revision Control Rg                   | R/W    | 00h          | Note <sup>3</sup> |

| 24h               | 7F6h              | Revision Number Rg                    | R      |              | Note <sup>4</sup> |

| 25h               |                   | Reserved                              | R/W    | XX           |                   |

| 26h               | NA                | Bus Control Rg 1                      | R/W    | 00h          | Note <sup>5</sup> |

| 27h               | NA                | IOIS16 Address Control Rg             | R/W    | 00h          | Note <sup>5</sup> |

| 28h               | NA                | ATA/IDE Dual Drive Control Rg         | R/W    | 00h          | Note <sup>3</sup> |

| 29h               |                   | Reserved                              | R/W    | 00h          |                   |

| 2Ah               | NA                | Power Management Timer Count Value Rg | R/W    | 00h          | Note <sup>3</sup> |

| 2Bh               | NA                | Power Management Control Rg           | R/W    | 00h          | Note <sup>3</sup> |

| 2Ch               | NA                | Interface Con•guration Rg 4           | R/W    | 00h          | Note <sup>3</sup> |

| 2Dh               | NA                | Con•guration Index Compare Rg 1       | R/W    | 00h          | Note <sup>3</sup> |

| 2Eh               | NA                | Con•guration Index Compare Rg 2       | R/W    | 00h          | Note <sup>3</sup> |

| 2Fh               | NA                | Bus Control Rg 2 R/W                  |        | 00h          | Note <sup>3</sup> |

| 30h–FFh           |                   | User-Definable Attribute Memory       | R/W    | XXh          | Note <sup>6</sup> |

|                   |                   | Location 00h–CFh (208-byte)           |        |              |                   |

#### NOTES:

- 1. When the ZX6017 is in Master Mode, the user should program this location in EEPROM with 00h.

- 2. The PCMCIA base address for these registers could be set in the range of 000h–400h. At Power-On Reset (POR), the base is set to 000h.

- 3. User must write the Revision Number (see ZX6017 top mark) to the Revision Control register to unlock these registers.

- 4. The Z86017 BA Revision Number is 10h (see device top mark).

- 5. These registers are only available on the Z16017

- 6. When the ZX6017 is in Master Mode, data at EEPROM addresses 30h-FFh are written locations 00h-CFh of the on-board Attribute Memory. In Slave Mode, Attribute Memory is programmed through registers 08h and 09h.

### **EEPROM REGISTER**

**EEPROM Register**

Address: SELECT 00h

Name: Interface Configuration Register 0

Type: Read/Write

Table 11. Interface Configuration Register: Address 00h

| Bit Placement | acement Bit Name Description |                       |                                                                                                                                                                                       |  |  |  |  |

|---------------|------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bits 1–0      | Set Internal                 | by-32 se<br>these bit | Internal Clock Divider. On Power-On Reset, clock divide-<br>by-32 selects the Master Clock. On Power-On Reset, set<br>these bits to 0 0. Table 12 describes Master Clock<br>Settings. |  |  |  |  |

|               |                              | Bit 1                 | Bit 0                                                                                                                                                                                 |  |  |  |  |

|               |                              | 0                     | 0 Slowest Clock, Clock In divide-by-32                                                                                                                                                |  |  |  |  |

|               |                              | 1                     | 1 Clock In divide-by-16                                                                                                                                                               |  |  |  |  |

|               |                              | 1                     | 0 Clock In divide-by-4                                                                                                                                                                |  |  |  |  |

|               |                              | 1                     | 1 Clock In                                                                                                                                                                            |  |  |  |  |

| Bits 3–2      | EN_OVERIDE                   | selection             | es PCMCIA ATA mode bits, /PC_ATA/HOE n on the PCMCIA interface. On Power-On Reset, stare set to 0. Sample /PC_ATA/HOE.                                                                |  |  |  |  |

|               |                              | Bit 3                 | Bit 2                                                                                                                                                                                 |  |  |  |  |

|               |                              | 0                     | 0 PC_ATA/HOE Sampled to Set Mode                                                                                                                                                      |  |  |  |  |

|               |                              | 0                     | 1 Forces ATA/IDE Pass Through Mode                                                                                                                                                    |  |  |  |  |

|               |                              | 1                     | 0 Forces PCMCIA Mode                                                                                                                                                                  |  |  |  |  |

|               |                              | 1                     | 1 Reserved                                                                                                                                                                            |  |  |  |  |

Table 11. Interface Configuration Register: Address 00h (Continued)

| Bit Placement | Bit Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 4         | EN_RDY_BSY | When this bit is set to 1, the PC_RDY/BSY/REQ/HINT pin is configured as RDY/BSY. To con•gure this pin as an IREQ/HINT, set this bit to 0. On Power-On Reset, the ZX6017 automatically reads the EEPROM and also determines if a PCMCIA device is connected. After the entire attribute memory is loaded and the chip initialization is complete, the READY/BSY signal on the PCMCIA bus indicates READY. Without an EEPROM, the device indicates READY whenever this bit is set and the ZX6017 has determined a PCMCIA bus is connected. |

| Bit 5         | EN_CTR_IRQ | Enables PCMCIA Interrupt Mode. Enables ATA_IREQ pin to control PC_IREQ in I/O Mode. This bit is active when set to 1. On Power-On Reset, this bit is set to 0.                                                                                                                                                                                                                                                                                                                                                                           |

| Bit 6         | EN_INT_POL | Enable local (M_PINT) processor interrupt polarity active Low. This bit is active when set to 1. On Power-On Reset, this bit is set to 0. Interrupt is active High. M_PINT is a tristate driven signal. Whenever an interrupt is present and enabled, M_PINT is driven. If the interrupt is programmed active High, then M_PINT is driven from tri-state to High. If the interrupt polarity selects active Low interrupts, then the interrupt is driven from tri-state to active Low. Also see Register 2Ch.                             |

| Bit 7         | EN_ATA_BHE | When this bit is set to 1, it enables the ATA_PDIAG/ATA_BHE/RING_IN pin to be used as a Byte High Enable pin on a local interface side. Byte High Enable is used to signify that a PCMCIA host is requesting or sending data on the high byte bus pins ATA_DATA[15-8] of the local bus. For ATA_BHE, also see Register 2Fh. When set to 0, ATA_PDIAG/ATA_BHE/RING_IN is used as a local bidirectional PDIAG pin. On Power-On Reset, this bit is set to 0.                                                                                |

40

**Table 12.** Master Clock

| Register 0<br>Bit 1 | Register 0<br>Bit 9 | Clock In | EEPROM<br>CLK Timing | Interrupt<br>Pulse <sup>1</sup> Width | Comments    |

|---------------------|---------------------|----------|----------------------|---------------------------------------|-------------|

| 0                   | 0                   | 50 ns    | 6.4 μs               | 204 μs                                |             |

| 0                   | 1                   | 50 ns    | 3.2 μs               | 102 μs                                |             |

| 1                   | 0                   | 50 ns    | 800 ns               | 25 μs                                 | Recommended |

| 1                   | 1                   | 50 ns    | 200 ns               | 5.25 μs                               |             |

| 0                   | 0                   | 100 ns   | 12.8 μs              | 404 μs                                |             |

| 0                   | 1                   | 100 ns   | 6.4 μs               | 204 μs                                |             |

| 1                   | 0                   | 100 ns   | 1.6 μs               | 50 μs                                 |             |

| 1                   | 1                   | 100 ns   | 400 ns               | 12.5 μs                               | Recommended |

#### NOTES: