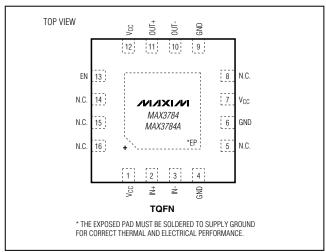

TOP VIEW

### **General Description**

**Pin Configurations**

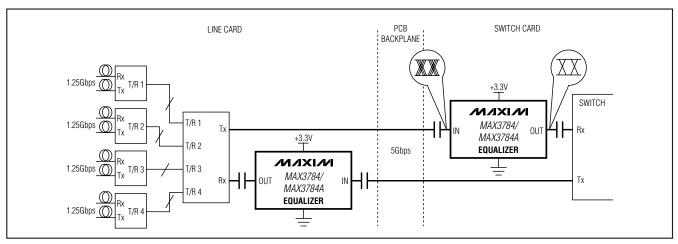

The MAX3784/MAX3784A 5Gbps equalizers provide compensation for transmission-medium losses in up to 40in of FR-4. They are optimized for short-run length and balanced codes such as 8b10b, as found in multiplexed 1.25Gbps Ethernet systems and 4.25Gbps Fibre Channel.

The equalizers use differential CML data inputs and outputs. A standby mode reduces power consumption when the parts are not in use. The MAX3784/ MAX3784A are available in a 4mm × 4mm, 16-pin QFN package that consumes only 185mW at +3.3V.

#### **Features**

- ♦ Spans 40in (1m) of FR-4 PCB

- ♦ 0.18UI Deterministic Jitter Up to 40in

- ♦ Low Power Consumption: 185mW (MAX3784)

- **♦** Equalization Reduces Intersymbol Interference

- ♦ Single +3.3V Supply

- **♦ Standby Mode**

- ♦ Small 4mm × 4mm, 16-Pin QFN Package

### **Applications**

Chassis Life Extension

- 4.25Gbps Fibre Channel

- 4x Multiplexed 1.25Gbps Ethernet (5Gbps)

#### 10 9 ΕN 13 N.C 14 $V_{CC}$ MXIMIMAX3784/ MAX3784A N.C. 15 GND N.C. 5 N.C. 16

\* THE EXPOSED PAD MUST BE SOLDERED TO SUPPLY GROUND FOR CORRECT THERMAL AND ELECTRICAL PERFORMANCE

Pin Configurations continued at end of data sheet.

## **Ordering Information**

| PART         | TEMP<br>RANGE | PIN-<br>PACKAGE | PKG<br>CODE |  |  |

|--------------|---------------|-----------------|-------------|--|--|

| MAX3784UGE   | 0°C to +85°C  | 16 QFN-EP*      | G1644-1     |  |  |

| MAX3784UTE+  | 0°C to +85°C  | 16 TQFN-EP*     | T1644-3     |  |  |

| MAX3784AUGE  | 0°C to +85°C  | 16 QFN-EP*      | G1644-1     |  |  |

| MAX3784AUTE+ | 0°C to +85°C  | 16 TQFN-EP*     | T1644-3     |  |  |

- +Denotes a lead-free package.

- \*Exposed pad.

## **Typical Application Circuit**

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>CC</sub> 0.5V to +6V Input Voltage(-0.5V) to (V <sub>CC</sub> + 0.5V) Continuous Output Current25mA to +25mA Continuous Power Dissipation (T <sub>A</sub> = +85°C) | Operating Ambient Temperature Range0°C to +85°C Storage Temperature Range55°C to +150°C Lead Temperature (soldering, 10s)+300°C |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Continuous Power Dissipation ( $T_A = +85^{\circ}C$ )                                                                                                                                     |                                                                                                                                 |

| 16-Pin QFN (derate 25mW/°C above +85°C)                                                                                                                                                   |                                                                                                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(VCC = +3V \text{ to } +3.6V, TA = 0^{\circ}\text{C to } +85^{\circ}\text{C}$ . Typical values are at  $VCC = +3.3V \text{ and } TA = +25^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                      | SYMBOL                         | CONDITIONS                    |               | MIN            | TYP  | MAX  | UNITS              |                    |

|--------------------------------|--------------------------------|-------------------------------|---------------|----------------|------|------|--------------------|--------------------|

| Supply Power                   |                                | EN = low                      |               |                |      | 30   | mW                 |                    |

|                                |                                | EN = high                     |               |                | 185  | 250  | IIIVV              |                    |

|                                |                                |                               | 10Hz < f <    | 100Hz          |      | 100  |                    |                    |

| Supply-Noise Tolerance         |                                | (Note 1)                      | 100Hz < f <   | 0Hz < f < 1MHz |      | 40   |                    | mV <sub>P-P</sub>  |

|                                |                                |                               | 1MHz < f <    | 2.5GHz         |      | 10   |                    | 1                  |

| Latency                        |                                | From input to output          |               |                |      | 200  |                    | ps                 |

| CML RECEIVER INPUT             | •                              |                               |               |                | •    |      |                    |                    |

| Input Voltage Swing            | VIN                            | Measured differentially a     | at point A ir | Figure 1       | 400  |      | 1000               | mV <sub>P-P</sub>  |

| Return Loss                    |                                | 100MHz to 2.5GHz              |               |                |      | 15   |                    | dB                 |

| Input Resistance               |                                | Differential                  |               |                | 80   | 100  | 120                | Ω                  |

| EQUALIZATION                   |                                |                               |               |                |      |      |                    |                    |

| Residual Deterministic Jitter, |                                | Table 1 (Notes 2–5)           | 20in          |                | 0.13 | 0.21 | Ulp <sub>-</sub> p |                    |

| 5Gbps                          |                                | Table 1 (Notes 2-3)           | 2-5) 40in     |                |      | 0.18 | 0.23               | OIP-P              |

| Residual Deterministic Jitter, |                                | Table 1 (Notes 2-5)           |               | 20in           |      | 0.08 | 0.14               | Ulp <sub>-</sub> p |

| 2.5Gbps                        |                                | Table 1 (Notes 2-3)           | 40in          |                |      | 0.13 | 0.28               | OIP-P              |

| Residual Deterministic Jitter, |                                | Table 1 (Notes 2 E)           |               | 20in           |      | 0.04 | 0.07               | Ulp <sub>-</sub> p |

| 1.25Gbps                       |                                | Table 1 (Notes 2–5)           |               | 40in           |      | 0.07 | 0.15               | OIP-P              |

| Random Jitter                  |                                | (Notes 5, 6)                  |               |                | 1.3  | 1.9  | psrms              |                    |

| CML TRANSMITTER OUTPUT         | (into 100 $\!\Omega$ $\!\pm$   | 1Ω)                           |               |                |      |      |                    |                    |

| Output Voltage Swing           | Vo                             | Billororitial owing, measured | ured          | MAX3784        | 400  |      | 600                | mV <sub>P-P</sub>  |

|                                |                                |                               | MAX3784A      | 550            |      | 750  | IIIVP-P            |                    |

| Transition Time                | t <sub>f,</sub> t <sub>r</sub> | 20% to 80% (Notes 5, 8)       |               | 30             | 45   | 60   | ps                 |                    |

| Output Resistance              |                                | Single ended                  |               | 40             | 50   | 60   | Ω                  |                    |

\_\_\_\_\_\_NIXI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3V \text{ to } +3.6V, T_A = 0^{\circ}\text{C to } +85^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = +3.3V \text{ and } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER          | SYMBOL | CONDITIONS | MIN  | TYP | MAX | UNITS |

|--------------------|--------|------------|------|-----|-----|-------|

| ENABLE CONTROL PIN |        |            |      |     |     |       |

| Input High Voltage |        |            | 1.5  |     |     | V     |

| Input Low Voltage  |        |            |      |     | 0.5 | V     |

| Input High Current |        | (Note 7)   | -150 |     | +10 | μΑ    |

| Input Low Current  |        | (Note 7)   | -150 |     | +10 | μΑ    |

Note 1: Allowed supply noise during jitter tests.

Note 2: Test pattern. This is a combination of K28.5± characters running at the full bit rate and at one-quarter the bit rate. This simulates the multiplexing of four each 1.25Gbps Ethernet data streams.

Pattern (hex) 100 bits

00 FFFF F0F0 FF 0000 0F0F (quarter rate K28.5+, quarter rate K28.5-) 3EB05 (K28.5± 00 1111 1010 11 0000 0101)

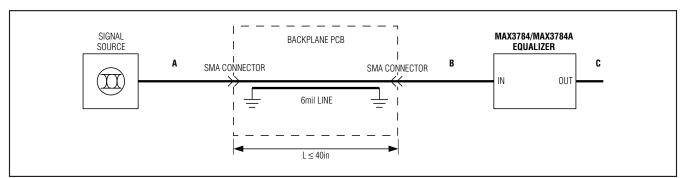

Note 3: Difference in deterministic jitter between reference points A and C in Figure 1.

**Note 4:** Signal source amplitude range is 400mV<sub>P-P</sub> to 1000mV<sub>P-P</sub> differential. Signal is applied differentially at point A as shown in Figure 1. The deterministic jitter at point B must be from media-induced loss and not from clock-source modulation. Deterministic jitter is measured at the 50% vertical level of the signal at point C.

Note 5: Guaranteed by design and characterization.

Note 6: Test pattern is K28.5 with 40in trace.

**Note 7:** On-chip pullup resistor of  $40k\Omega$  (typ). Negative current indicates equalizer sources current.

Note 8: Using 00 0001 1111 or equivalent pattern. Measured over entire input voltage range, max and min media loss and within 2in of output pins.

Figure 1. Test Conditions

#### Table 1. PCB Assumptions (PCB material is FR-4)

| PARAMETER             | CONDITIONS              | MIN  | TYP | MAX   | UNITS |

|-----------------------|-------------------------|------|-----|-------|-------|

| Transmission Line     | Edge-coupled stripline  |      | 6   |       | mils  |

| Relative Permittivity | FR-4 or similar         | 4.4  |     | 4.5   |       |

| Loss Tangent          | FR-4 or similar         | 0.02 |     | 0.022 | _     |

| Metal Thickness       | 0.7 mils (0.5oz copper) |      | 0.7 |       | mils  |

| Impedance             | Differential            | 90   | 100 | 110   | Ω     |

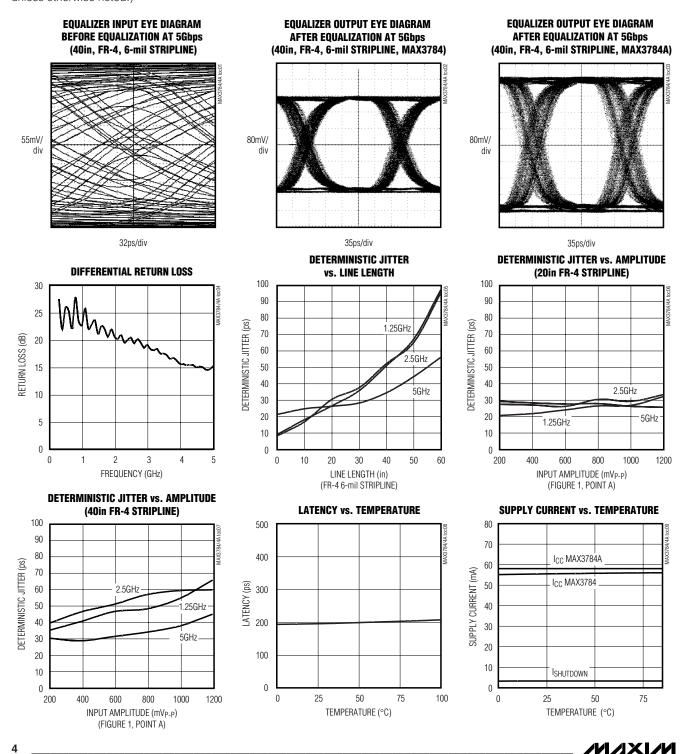

## Typical Operating Characteristics

$(V_{CC} = +3.3V, measurements done at 5Gbps, 800mV_{P-P} board input with 100-bit pattern from Note 2 of the EC Table, T<sub>A</sub> = +25°C, unless otherwise noted.)$

### **Pin Description**

| PIN                 | NAME           | FUNCTION                                                                                                                             |

|---------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1, 7, 12            | Vcc            | +3.3V Supply Voltage                                                                                                                 |

| 2                   | IN+            | Positive Input, CML                                                                                                                  |

| 3                   | IN-            | Negative Input, CML                                                                                                                  |

| 4, 6, 9             | GND            | Supply Ground                                                                                                                        |

| 5, 8, 14, 15,<br>16 | N.C.           | No Connection. Leave unconnected.                                                                                                    |

| 10                  | OUT-           | Negative Output, CML                                                                                                                 |

| 11                  | OUT+           | Positive Output, CML                                                                                                                 |

| 13                  | EN             | Enable Equalizer. A logic high or open selects normal operation. A logic low selects low-power standby mode.                         |

| EP                  | Exposed<br>Pad | Connect to Ground. The exposed pad must be soldered to the circuit board ground plane for proper thermal and electrical performance. |

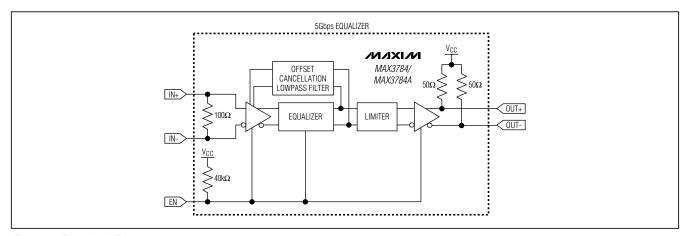

Figure 2. Functional Diagram

### Detailed Description

#### **General Theory of Operation**

The MAX3784/MAX3784A adaptive equalizers extend the reach of transmission lines in high-frequency backplane interconnect applications. They can be used for 4.25Gbps Fibre Channel, 4x 1.25Gbps Ethernet (5Gbps) and other NRZ, 8b10b or short (≤ 20 bits) CID data types. Internally, the MAX3784/MAX3784A are comprised of an equalizer control loop and limiting output driver. The equalizer block reduces intersymbol interference (ISI), compensating for frequency-dependent media-induced loss. The equalization control detects the spectral contents of the input signal and provides a control voltage to the equalizer core, adapting it to different media. The equalizer operation is optimized for short-run, DC-balanced transmission codes.

#### Standby Mode

Standby saves power when the equalizer is not in use. The EN logic input must be set high or open for normal operation. Logic low at EN forces the equalizer into the standby state.

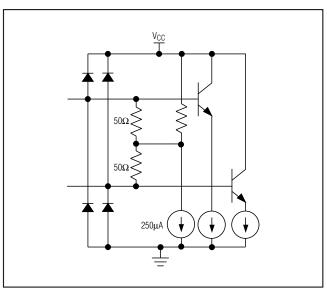

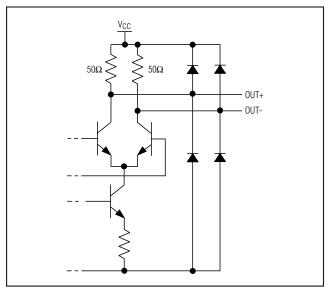

#### **CML Input and Output Buffers**

The input and output buffers are implemented using current-mode logic (CML). Equivalent circuits are shown in Figures 3 and 4. For details on interfacing with CML, refer to Maxim Application Note HFAN-01.0: *Introduction to LVDS, PECL, and CML*. The common-mode voltage of the input and output is above +2.5V. AC-coupling capacitors are required when interfacing this part with devices terminated in voltages such as +1.8V. Values of 0.10µF or greater are recommended.

Figure 3. CML Input Equivalent Circuit

### **Applications Information**

#### **Alternate Data Rates**

The MAX3784/MAX3784A is optimized for automatic operation at 5Gbps. Equalization at other data rates, such as 1.25Gbps and 2.5Gbps, is possible. See the *Typical Operating Characteristics* for Deterministic Jitter vs. Line Length and Deterministic Jitter vs. Amplitude for typical performance at these data rates.

Figure 4. CML Output Equivalent Circuit

#### Layout Considerations

Circuit board layout and design can significantly affect the MAX3784/MAX3784As' performance. Use good high-frequency design techniques, including minimizing ground inductance and connections and using controlled-impedance transmission lines for the high-frequency data signals. Route signals differentially to reduce EMI susceptibility and crosstalk. Solder the exposed pad to supply ground for proper thermal and electrical operation.

Place power-supply decoupling capacitors as close as possible to the V<sub>CC</sub> pins.

## Pin Configurations (continued)

6 \_\_\_\_\_\_\_ /\/\!\\

### **Package Information**

For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | DOCUMENT NO.   |

|--------------|----------------|

| 16 QFN       | <u>21-0106</u> |

| 16 TQFN      | <u>21-0139</u> |

#### \_Revision History

Pages changed at Rev 4: 1–7 (removed package drawings, replaced with table)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

is a registered trademark of Maxim Integrated Products.

© 2007 Maxim Integrated Products