# LMH0344

# 3 Gbps HD/SD SDI Adaptive Cable Equalizer

### **General Description**

The LMH0344 3 Gbps HD/SD SDI Adaptive Cable Equalizer is designed to equalize data transmitted over cable (or any media with similar dispersive loss characteristics). The equalizer operates over a wide range of data rates from 125 Mbps to 2.97 Gbps and supports SMPTE 424M, SMPTE 292M, SMPTE 344M, and SMPTE 259M.

The LMH0344 implements DC restoration to correctly handle pathological data conditions. The equalizer may be driven in either a single ended or differential configuration.

Additional features include separate carrier detect and output mute pins which may be tied together to mute the output when no signal is present. A programmable mute reference is provided to mute the output at a selectable level of signal degradation.

The device is available in two space—saving packages: a 4 X 4 mm 16-pin LLP and even more space—efficient 3 x 3 mm 25-ball MICRO-ARRAY package.

### **Features**

- SMPTE 424M, SMPTE 292M, SMPTE 344M, and SMPTE 259M compliant

- Supports DVB-ASI at 270 Mbps

- Wide range of data rates: 125 Mbps to 2.97 Gbps

- Equalizes up to 120 meters of Belden 1694A at 2.97 Gbps, up to 140 meters of Belden 1694A at 1.485 Gbps, or up to 400 meters of Belden 1694A at 270 Mbps

- Equalizes 0-120m of Belden 1694A at 2.97 Gbps with 0.3 UI maximum output jitter

- Manual bypass and output mute with a programmable threshold

- Single-ended or differential input

- $50\Omega$  differential outputs (internal  $50\Omega$  pullups)

- Single 3.3V supply operation

- 280 mW typical power consumption

- 16-pin LLP or 25-ball MICRO-ARRAY package

- Industrial temperature range: -40°C to +85°C

- HBM ESD Rating: 8 kV

- LLP version footprint compatible with the LMH0044 and LMH0074

- Replaces the Gennum GS2974A or GS2974B

### **Applications**

- SMPTE 424M, SMPTE 292M, SMPTE 344M, and SMPTE 259M serial digital interfaces

- Serial digital data equalization and reception

- Data recovery equalization

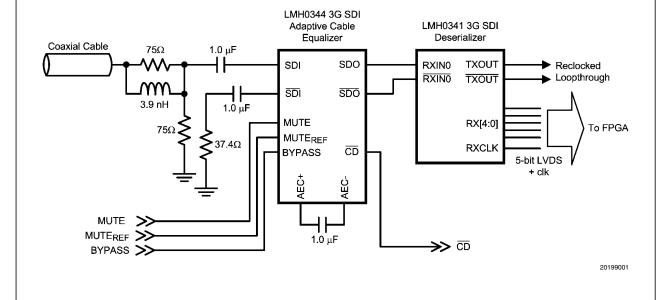

# **Typical Application**

# **Absolute Maximum Ratings** (Note 1)

Supply Voltage 4.0V Input Voltage (all inputs) -0.3V to  $V_{CC}+0.3V$  Storage Temperature Range  $-65^{\circ}$ C to  $+150^{\circ}$ C

Junction Temperature

Lead Temperature (Soldering 4 Sec) +260°C

Package Thermal Resistance

$\begin{array}{lll} \theta_{JA} \ 16\text{-pin LLP} & +40^{\circ}\text{C/W} \\ \theta_{JC} \ 16\text{-pin LLP} & +4.5^{\circ}\text{C/W} \\ \theta_{JA} \ 25\text{-ball MICRO-ARRAY} & +58.1^{\circ}\text{C/W} \\ \text{ESD Rating (HBM)} & 8 \ \text{kV} \\ \text{ESD Rating (MM)} & 400V \\ \text{ESD Rating (CDM)} & 2 \ \text{kV} \end{array}$

# **Recommended Operating Conditions**

Supply Voltage ( $V_{CC} - V_{EE}$ ) 3.3V ±5% Input Coupling Capacitance 1.0  $\mu$ F AEC Capacitor (Connected between AEC+ and AEC-) 1.0  $\mu$ F

Operating Free Air Temperature ( $T_A$ )  $-40^{\circ}C$  to  $+85^{\circ}C$

### **DC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Notes 2, 3).

+125°C

| Symbol             | Parameter                                 | Conditions                      | Reference           | Min | Тур                                   | Max | Units             |

|--------------------|-------------------------------------------|---------------------------------|---------------------|-----|---------------------------------------|-----|-------------------|

| V <sub>CMIN</sub>  | Input Common Mode Voltage                 |                                 | SDI, <del>SDI</del> |     | 1.9                                   |     | V                 |

| V <sub>SDI</sub>   | Input Voltage Swing                       | At LMH0344 input, (Notes 4, 5)  |                     | 720 | 800                                   | 950 | mV <sub>P-P</sub> |

| V <sub>CMOUT</sub> | Output Common Mode Voltage                |                                 | SDO, SDO            |     | V <sub>CC</sub> – V <sub>SDO</sub> /2 |     | V                 |

| V <sub>SDO</sub>   | Output Voltage Swing                      | 100 $\Omega$ load, differential |                     |     | 750                                   |     | mV <sub>P-P</sub> |

|                    | MUTE <sub>REF</sub> DC Voltage (floating) |                                 | MUTE <sub>REF</sub> |     | 1.3                                   |     | V                 |

|                    | MUTE <sub>REF</sub> Range                 |                                 |                     |     | 0.6                                   |     | V                 |

|                    | CD Output Voltage                         | Carrier not present             | CD                  | 2.4 |                                       |     | V                 |

|                    |                                           | Carrier present                 |                     |     |                                       | 0.4 | V                 |

|                    | MUTE Input Voltage                        | Min to mute outputs             | MUTE                | 2.0 |                                       |     | V                 |

|                    |                                           | Max to force outputs active     |                     |     |                                       | 8.0 | V                 |

| I <sub>CC</sub>    | Supply Current                            |                                 |                     |     | 85                                    | 100 | mA                |

### **AC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Note 3).

| Symbol                         | Parameter                        | Conditions                                         | Reference | Min | Тур  | Max  | Units |

|--------------------------------|----------------------------------|----------------------------------------------------|-----------|-----|------|------|-------|

| BR <sub>MIN</sub>              | Minimum Input Data Rate          |                                                    | SDI, SDI  |     | 125  |      | Mbps  |

| BR <sub>Max</sub>              | Maximum Input Data Rate          |                                                    | 7         |     |      | 2970 | Mbps  |

|                                | Jitter for Various Cable Lengths | 270 Mbps, Belden 1694A,<br>0-400 meters (Note 6)   |           |     |      | 0.2  | UI    |

|                                |                                  | 270 Mbps, Belden 1694A,<br>0-400 meters (Note 7)   |           |     | 0.07 |      | UI    |

|                                |                                  | 1.485 Gbps, Belden 1694A,<br>0-140 meters (Note 6) |           |     |      | 0.25 | UI    |

|                                |                                  | 1.485 Gbps, Belden 1694A,<br>0-140 meters (Note 7) |           |     | 0.08 |      | UI    |

|                                |                                  | 2.97 Gbps, Belden 1694A,<br>0-120 meters (Note 6)  |           |     |      | 0.3  | UI    |

|                                |                                  | 2.97 Gbps, Belden 1694A,<br>0-120 meters (Note 7)  |           |     | 0.18 |      | UI    |

| t <sub>r</sub> ,t <sub>f</sub> | Output Rise Time, Fall Time      | 20% - 80%, (Note 4)                                | SDO, SDO  |     | 60   | 130  | ps    |

|                                | Mismatch in Rise/Fall Time       | (Note 4)                                           |           |     | 2    | 15   | ps    |

| t <sub>os</sub>                | Output Overshoot                 | (Note 4)                                           |           |     | 1    | 5    | %     |

| R <sub>OUT</sub>               | Output Resistance                | single-ended                                       | 7         |     | 50   |      | Ω     |

| RL <sub>IN</sub>               | Input Return Loss                | 5 MHz - 1.5 GHz, (Note 8)                          | SDI, SDI  | 15  |      |      | dB    |

|                                |                                  | 1.5 GHz - 3.0 GHz, (Note 8)                        |           | 10  |      |      | dB    |

| R <sub>IN</sub>                | Input Resistance                 | single-ended                                       |           |     | 1.3  |      | kΩ    |

| C <sub>IN</sub>                | Input Capacitance                | single-ended                                       |           |     | 1    |      | pF    |

**Note 1:** "Absolute Maximum Ratings" are those parameter values beyond which the life and operation of the device cannot be guaranteed. The stating herein of these maximums shall not be construed to imply that the device can or should be operated at or beyond these values. The table of "Electrical Characteristics" specifies acceptable device operating conditions.

Note 2: Current flow into device pins is defined as positive. Current flow out of device pins is defined as negative. All voltages are stated referenced to  $V_{\text{EE}} = 0$  Volts.

Note 3: Typical values are stated for  $V_{CC}$  = +3.3V and  $T_A$  = +25°C.

Note 4: Specification is guaranteed by characterization.

Note 5: This specification is for 0m cable only.

**Note 6:** Based on characterization data over the full range of recommended operating conditions of the device. Jitter is measured in accordance with SMPTE RP 184, SMPTE RP 192, and the applicable serial data transmission standard: SMPTE 424M, SMPTE 292M, or SMPTE 259M.

Note 7: Measured with Pseudo Matrix Pathological test signal.

Note 8: Input return loss is dependent on board design. The LMH0344 exceeds this specification on the SD344 evaluation board with a return loss network consisting of an 8.2 nH inductor in parallel with a 0.5 pF capacitor in parallel with the 75 $\Omega$  series resistor on the input.

3

# **Typical Performance Characteristics**

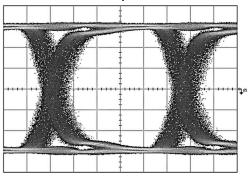

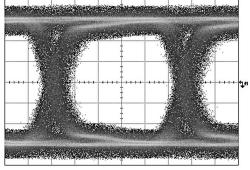

# After Equalization: 120m of Belden 1694A with 2.97 Gbps PRBS

# After Equalization: 120m of Belden 1694A with 2.97 Gbps Pseudo Matrix Pathological

20199005

www.national.com

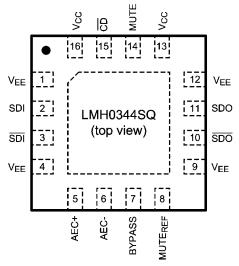

# **Connection Diagrams**

20199003

The exposed die attach pad is a negative electrical terminal for this device. It should be connected to the negative power supply voltage.

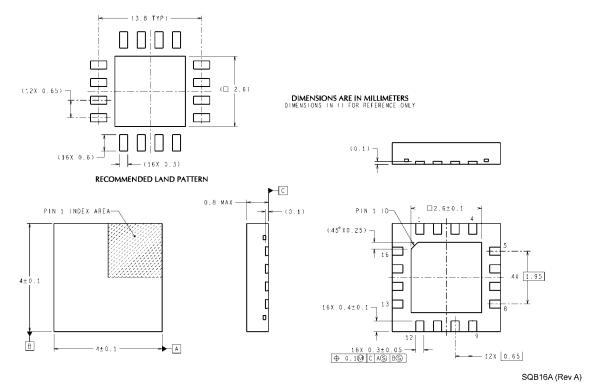

16-Pin LLP Order Number LMH0344SQ See NS Package Number SQB16A

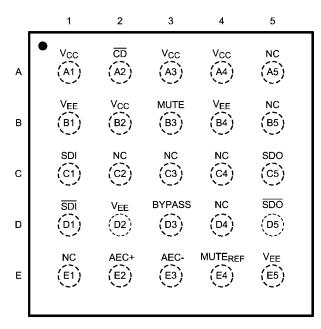

LMH0344GR (top view)

20199006

25-Ball MICRO-ARRAY Order Number LMH0344GR See NS Package Number GRA25A

# **Pin Descriptions**

| LLP Pin             | MICRO-<br>ARRAY Ball          | Name                | Description                                                                                                                                                                                                                                                                                                   |  |

|---------------------|-------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2                   | C1                            | SDI                 | Serial data true input.                                                                                                                                                                                                                                                                                       |  |

| 3                   | D1                            | SDI                 | Serial data complement input.                                                                                                                                                                                                                                                                                 |  |

| 5                   | E2                            | AEC+                | AEC loop filter external capacitor (1µF) positive connection.                                                                                                                                                                                                                                                 |  |

| 6                   | E3                            | AEC-                | AEC loop filter external capacitor (1µF) negative connection.                                                                                                                                                                                                                                                 |  |

| 7                   | D3                            | BYPASS              | Bypasses equalization and DC restoration when high. No equalization occur in this mode.                                                                                                                                                                                                                       |  |

| 8                   | E4                            | MUTE <sub>REF</sub> | Mute reference. Sets the threshold for $\overline{\text{CD}}$ and (with $\overline{\text{CD}}$ tied to MUTE) determines the maximum cable to be equalized before muting. MUTE <sub>REF</sub> may be either unconnected or connected to ground for maximum equalization.                                       |  |

| 10                  | D5                            | SDO                 | Serial data complement output.                                                                                                                                                                                                                                                                                |  |

| 11                  | C5                            | SDO                 | Serial data true output.                                                                                                                                                                                                                                                                                      |  |

| 14                  | ВЗ                            | MUTE                | Output mute. To disable the mute function and enable the output, MUTE must be tied to GND or a low level signal. To force the outputs to a muted state, tie to $V_{CC}$ . $\overline{CD}$ may be tied to this pin to inhibit the output when no input signal is present. MUTE has no function in BYPASS mode. |  |

| 15                  | A2                            | CD                  | Carrier detect. $\overline{\text{CD}}$ is high when no signal is present. $\overline{\text{CD}}$ has no function in BYPASS mode.                                                                                                                                                                              |  |

| 13, 16              | A1, A3, A4, B2                | V <sub>CC</sub>     | Positive power supply (+3.3V).                                                                                                                                                                                                                                                                                |  |

| DAP, 1, 4, 9,<br>12 | B1, B4, D2, E5                | V <sub>EE</sub>     | Negative power supply (ground).                                                                                                                                                                                                                                                                               |  |

| _                   | A5, B5, C2,<br>C3, C4, D4, E1 | NC                  | No connect.                                                                                                                                                                                                                                                                                                   |  |

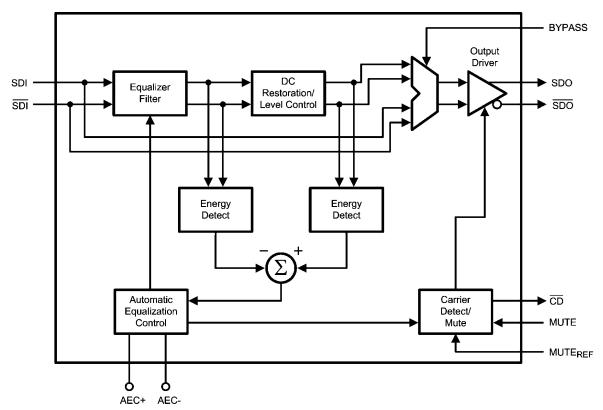

### **Block Diagram**

20199002

# **Device Operation**

#### **BLOCK DESCRIPTION**

The **Equalizer Filter** block is a multi-stage adaptive filter. If Bypass is high, the equalizer filter is disabled.

The **DC Restoration / Level Control** block receives the differential signals from the equalizer filter block. This block incorporates a self-biasing DC restoration circuit to fully DC restore the signals. If Bypass is high, this function is disabled.

The signals before and after the DC Restoration / Level Control block are used to generate the **Automatic Equalization Control (AEC)** signal. This control signal sets the gain and bandwidth of the equalizer filter. The loop response in the AEC block is controlled by an external  $1\mu F$  capacitor placed across the AEC+ and AEC- pins.

The **Carrier Detect / Mute** block generates the carrier detect signal and controls the mute function of the output. This block utilizes the  $\overline{\text{CD}}$  and  $\overline{\text{MUTE}}$  signals along with  $\overline{\text{Mute}}$  Reference ( $\overline{\text{MUTE}}_{\text{RFF}}$ ).

The **Output Driver** produces SDO and SDO.

### MUTE REFERENCE (MUTE<sub>REF</sub>)

The mute reference sets the threshold for  $\overline{\text{CD}}$  and (with  $\overline{\text{CD}}$  tied to MUTE) determines the amount of cable to equalize before automatically muting the outputs. This is set by applying a voltage inversely proportional to the length of cable to equalize. The applied voltage must be greater than the MUTE<sub>REF</sub> floating voltage (typically 1.3V) in order to change the  $\overline{\text{CD}}$  threshold. As the applied MUTE<sub>REF</sub> voltage is increased, the amount of cable that can be equalized before

carrier detect is de-asserted and the outputs are muted is decreased. MUTE<sub>REF</sub> may be left unconnected or connected to ground for maximum equalization before muting.

#### CARRIER DETECT (CD) AND MUTE

Carrier detect  $\overline{CD}$  indicates if a valid signal is present at the LMH0344 input. If MUTE<sub>REF</sub> is used, the carrier detect threshold will be altered accordingly.  $\overline{CD}$  provides a high voltage when no signal is present at the LMH0344 input.  $\overline{CD}$  is low when a valid input signal is detected.

MUTE can be used to manually mute or enable SDO and SDO. Applying a high input to MUTE will mute the LMH0344 outputs by forcing the output to a logic zero. Applying a low input will force the outputs to be active.

CD and MUTE may be tied together to automatically mute the output when no input signal is present.

#### **INPUT INTERFACING**

The LMH0344 accepts either differential or single-ended input. The input must be AC coupled. Transformer coupling is not supported.

The LMH0344 correctly handles equalizer pathological signals for standard definition and high definition serial digital video, as described in SMPTE RP 178 and RP 198, respectively.

### **OUTPUT INTERFACING**

The SDO and  $\overline{\text{SDO}}$  outputs are internally loaded with  $50\Omega$ . They produce a 750 mV<sub>P-P</sub> differential output, or a 375 mV<sub>P-P</sub> single-ended output.

www.national.com 6

# Physical Dimensions inches (millimeters) unless otherwise noted

### 16-Pin LLP Order Number LMH0344SQ NS Package Number SQB16A

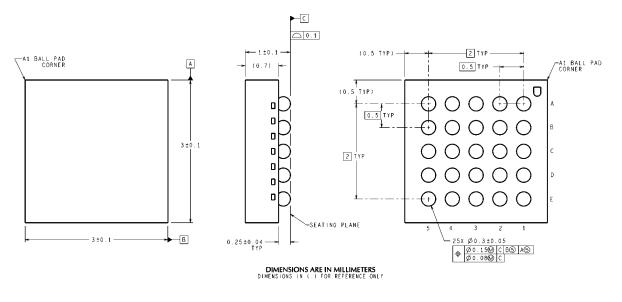

GRA25A (Rev A)

25-Ball MICRO-ARRAY Order Number LMH0344GR NS Package Number GRA25A

# **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support                  |                                |  |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |  |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |  |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

www.national.com