# Rev 9.0, 8/2008

# Multiple Switch Detection Interface with Suppressed Wake-up and 32mA Wetting Current

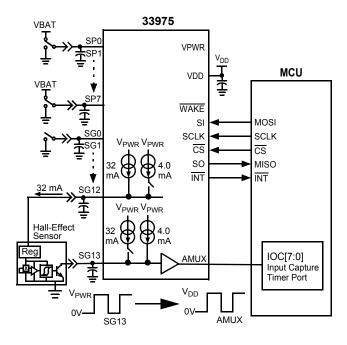

The 33975 Multiple Switch Detection Interface with Suppressed Wake-up is designed to detect the closing and opening of up to 22 switch contacts. The switch status, either open or closed, is transferred to the microprocessor unit (MCU) through a serial peripheral interface (SPI). The device also features a 22-to-1 analog multiplexer for reading inputs as analog.

The 33975 device has two modes of operation, Normal and Sleep. Normal Mode allows programming of the device and supplies switch contacts with pull-up or pull-down current as it monitors the switch change of state. The Sleep Mode provides low quiescent current, which makes the 33975 ideal for automotive and industrial products requiring low sleep state currents.

Improvements are a programmable interrupt timer for Sleep Mode that can be disabled, switch detection currents of 32mA and 4.0mA for switch-to-ground inputs, and an interrupt bit that can be reset.

#### **Features**

- Designed to operate from 5.5V ≤ V<sub>PWR</sub> ≤ 28V

- Switch input voltage: (33975: -14 to 38V) (33975A: -14 to 40V)

- Interfaces to microprocessor using 3.3V/5.0V SPI protocol

- · Selectable wake-up on change of state

- · 14 switch-to-ground inputs

- · 8 programmable inputs (switches to battery or ground)

- Selectable wetting current (32mA or 4.0mA for switch-to-ground inputs)

- Sleep State current V<sub>PWR</sub> 100μA, Vdd 20μA

- Pb-free packaging designated by suffix code EK

# 33975 33975A

# MULTIPLE SWITCH DETECTION INTERFACE WITH SUPPRESSED WAKE-UP

| ORDE           | ORDERING INFORMATION                   |             |  |  |  |  |  |  |  |  |  |  |  |

|----------------|----------------------------------------|-------------|--|--|--|--|--|--|--|--|--|--|--|

| Device         | Temperature<br>Range (T <sub>A</sub> ) | Package     |  |  |  |  |  |  |  |  |  |  |  |

| MC33975EK/R2   |                                        |             |  |  |  |  |  |  |  |  |  |  |  |

| MCZ33975EK/R2  | -40°C to 125°C                         | 32 SOICW-EP |  |  |  |  |  |  |  |  |  |  |  |

| MCZ33975AEK/R2 |                                        |             |  |  |  |  |  |  |  |  |  |  |  |

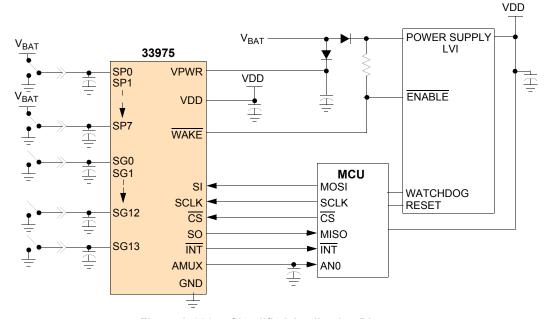

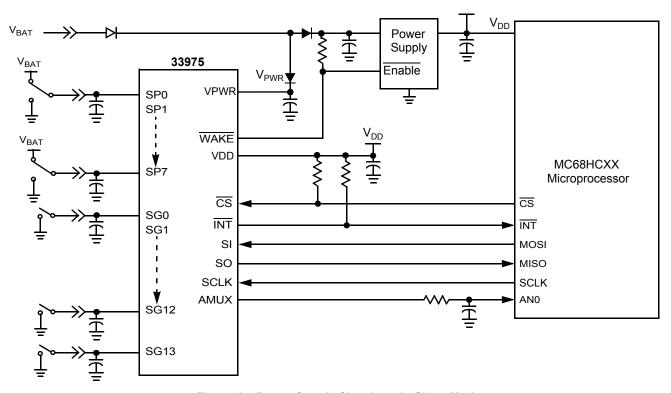

Figure 1. 33975 Simplified Application Diagram

© Freescale Semiconductor, Inc., 2005 - 2007. All rights reserved.

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

# **DEVICE VARIATIONS**

**Table 1. Device Variations**

| Device | Switch Input Voltage Range | Reference<br>Location |

|--------|----------------------------|-----------------------|

| 33975  | -14 to 38V <sub>DC</sub>   | <u>5</u>              |

| 33975A | -14 to 40V <sub>DC</sub>   | <u>5</u>              |

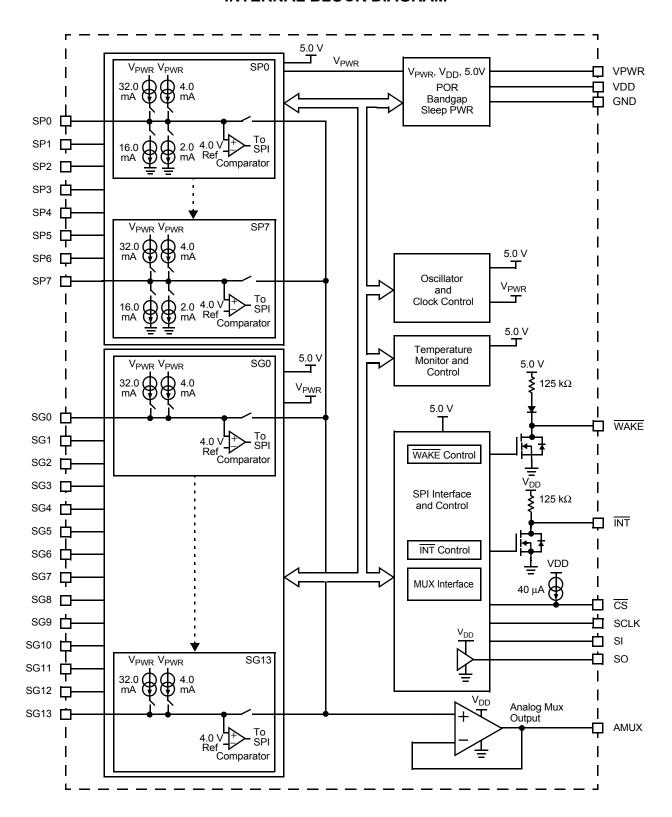

# INTERNAL BLOCK DIAGRAM

Figure 2. 33975 Simplified Internal Block Diagram

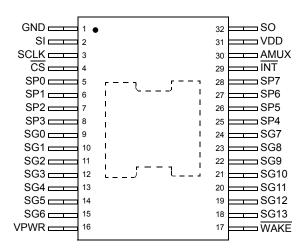

# **PIN CONNECTIONS**

Figure 3. 33975 Pin Connections

#### Table 2. Pin Definitions

A functional description of each Pin can be found in the Functional Pin Description section on page 12.

| Pin            | Pin Name | Formal Name                                                 | Description                                                                                     |

|----------------|----------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 1              | GND      | Ground                                                      | Ground for logic, analog, and switch-to-battery inputs                                          |

| 2              | SI       | SPI Slave In                                                | SPI control data input pin from MCU to 33975                                                    |

| 3              | SCLK     | Serial Clock                                                | SPI control clock input pin                                                                     |

| 4              | CS       | Chip Select                                                 | SPI control chip select input pin from MCU to 33975. Logic [0] allows data to be transferred in |

| 5–8<br>25–28   | SPn      | Programmable Switches 0–3 Programmable Switches 4–7         | Programmable switch-to-battery or switch-to-ground input pins                                   |

| 9–15,<br>18–24 | SGn      | Switch-to-Ground Inputs 0–6<br>Switch-to-Ground Inputs 13–7 | Switch-to-ground input pins                                                                     |

| 16             | VPWR     | Battery Input                                               | Battery supply input pin. This pin requires external reverse battery protection.                |

| 17             | WAKE     | Wake-up                                                     | Open drain wake-up output is designed to control a power supply enable pin                      |

| 29             | ĪNT      | Interrupt                                                   | Open-drain output to MCU is used to indicate input switch change of state                       |

| 30             | AMUX     | Analog Multiplex Output                                     | Analog multiplex output                                                                         |

| 31             | VDD      | Voltage Drain Supply                                        | 3.3/5.0V supply sets SPI communication level for the SO driver                                  |

| 32             | SO       | SPI Slave Out                                               | Provides digital data from 33975 to the MCU                                                     |

### **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these limits may cause malfunction or permanent damage to the device.

| Rating                                                                                                                                    | Symbol           | Value                         | Unit            |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|-----------------|

| ELECTRICAL RATINGS                                                                                                                        |                  |                               |                 |

| VDD Supply Voltage                                                                                                                        | -                | -0.3 to 7.0                   | V <sub>DC</sub> |

| CS, SI, SO, SCLK, INT, AMUX                                                                                                               | -                | -0.3 to 7.0                   | V <sub>DC</sub> |

| WAKE                                                                                                                                      | -                | -0.3 to 40                    | V <sub>DC</sub> |

| VPWR Supply Voltage                                                                                                                       | -                | -0.3 to 50                    | V <sub>DC</sub> |

| VPWR Supply Voltage at -40°C                                                                                                              | -                | -0.3 to 45                    | V <sub>DC</sub> |

| Switch Input Voltage Range<br>33975<br>33975A                                                                                             | -                | -14 to 38<br>-14 to 40        | V <sub>DC</sub> |

| Frequency of SPI Operation (V <sub>DD</sub> = 5.0V)                                                                                       | _                | 6.0                           | MHz             |

| ESD Voltage <sup>(1)</sup> Human Body Model <sup>(2)</sup> Applies to all non-input Pins  Machine Model  Charge Device Model  Corner Pins | V <sub>ESD</sub> | ±2000<br>±2000<br>±200<br>750 | V               |

| Interior Pins                                                                                                                             |                  | 500                           |                 |

#### THERMAL RATINGS

| Operating Temperature            |                  |            | °C |

|----------------------------------|------------------|------------|----|

| Ambient                          | T <sub>A</sub>   | -40 to 125 |    |

| Junction                         | $T_J$            | -40 to 150 |    |

| Case                             | T <sub>C</sub>   | -40 to 125 |    |

| Storage Temperature              | T <sub>STG</sub> | -55 to 150 | °C |

| Power Dissipation <sup>(3)</sup> | P <sub>D</sub>   | 1.7        | W  |

- 1. ESD testing is performed in accordance with the Human Body Model ( $C_{ZAP} = 100pF$ ,  $R_{ZAP} = 1500\Omega$ ), the Machine Model ( $C_{ZAP} = 200pF$ ,  $R_{ZAP} = 0\Omega$ ), and the Charge Device Model.

- 2. All Programmable Switches (SP) and Switch-to-Ground (SG) input pins when tested individually.

- 3. Maximum power dissipation at  $T_J = 150$ °C junction temperature with no heatsink used.

- 4. Thermal resistance between the die and the exposed die pad.

# ELECTRICAL CHARACTERISTICS MAXIMUM RATINGS

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these limits may cause malfunction or permanent damage to the device.

| Rating                                                            | Symbol            | Value  | Unit |

|-------------------------------------------------------------------|-------------------|--------|------|

| ELECTRICAL RATINGS                                                |                   |        |      |

| Thermal Resistance                                                |                   |        | °C/W |

| Junction to Ambient                                               | $R_{	heta JA}$    | 71     |      |

| Between the die and the exposed die pad <sup>(4)</sup>            | $R_{	heta JC}$    | 1.2    |      |

| Peak Package Reflow Temperature During Reflow <sup>(5), (6)</sup> | T <sub>PPRT</sub> | Note 6 | °C   |

- 5. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 6. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

#### STATIC ELECTRICAL CHARACTERISTICS

**Table 4. Static Electrical Characteristics**

Characteristics noted under conditions of  $3.0\text{V} \le \text{V}_{DD} \le 5.5\text{V}$ ,  $8.0\text{V} \le \text{V}_{PWR} \le 28\text{V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{C} \le 125^{\circ}\text{C}$ , unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with  $\text{V}_{PWR}$  = 13V,  $\text{T}_{A}$  = 25°C.

| Characteristic                                                                                                                               | Symbol                                                               | Min              | Тур         | Max                | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------|-------------|--------------------|------|

| POWER INPUT                                                                                                                                  |                                                                      | l                | 1           | 1                  |      |

| Supply Voltage  Supply Voltage Range Quasi-Functional <sup>(7)</sup> Fully Operational  Supply Voltage Range Quasi-Functional <sup>(8)</sup> | V <sub>PWR(QF)</sub><br>V <sub>PWR(FO)</sub><br>V <sub>PWR(QF)</sub> | 5.5<br>8.0<br>28 | -<br>-<br>- | 8.0<br>28<br>38/40 | V    |

| Supply Voltage VPWR Supply Voltage Power On Reset                                                                                            | V <sub>PWR(POR)</sub>                                                | 4.2              | 4.6         | 5.0                | V    |

| Supply Current All Switches Open, Normal Mode, Tri-State Disabled                                                                            | I <sub>PWR(ON)</sub>                                                 | _                | 4.0         | 8.0                | mA   |

| Sleep State Supply Current<br>Scan Timer = 64ms, Switches Open                                                                               | I <sub>PWR(SS)</sub>                                                 | 40               | 70          | 100                | μА   |

| Logic Supply Voltage                                                                                                                         | V <sub>DD</sub>                                                      | 3.0              | -           | 5.5                | V    |

| Logic Supply Current All Switches Open, Normal Mode                                                                                          | I <sub>DD</sub>                                                      | _                | 0.25        | 0.5                | mA   |

| Sleep State Logic Supply Current<br>Scan Timer = 64ms, Switches Open                                                                         | I <sub>DD(SS)</sub>                                                  | _                | 10          | 20                 | μА   |

| SWITCH INPUT                                                                                                                                 |                                                                      | l                |             | 1                  |      |

| Pulse Wetting Current Switch-to-Battery (Current Sink) $5.5V \le V_{PWR} \le 28V$                                                            | I <sub>PULSE</sub>                                                   | 12               | 15          | 18                 | mA   |

| Pulse Wetting Current Switch-to-Ground (Current Source) $5.5V \le V_{PWR} \le 8.0V$ $8.0V \le V_{PWR} \le 28V$                               | I <sub>PULSE</sub>                                                   | 7.0<br>24        | 9.0<br>32   | -<br>36            | mA   |

| Sustain Current Switch-to-Battery Input (Current Sink) $5.5 V \le V_{PWR} \le 28 V$                                                          | Isustain                                                             | 1.8              | 2.1         | 2.4                | mA   |

| Sustain Current Switch-to-Ground Input (Current Source) $5.5V \leq V_{PWR} \leq 8.0V \\ 8.0V \leq V_{PWR} \leq 28V$                          | I <sub>SUSTAIN</sub>                                                 | 0.5<br>3.6       | 1.0<br>4.0  | -<br>4.4           | mA   |

| Sustain Current Matching Between Channels on Switch-to-Ground Inputs $\frac{I_{SUS(MAX)} - I_{SUS(MIN)}}{I_{SUS(MIN)}} \ \ X \ 100$          | I <sub>MATCH</sub>                                                   | _                | 2.0         | 5.0                | %    |

- 7. Device operational. Wetting and sustain currents are reduced. Operating the analog multiplexer below 8.0V is not recommended.

- 8. Thermal considerations must be taken when operating the device above 28V.

# ELECTRICAL CHARACTERISTICS STATIC ELECTRICAL CHARACTERISTICS

# Table 4. Static Electrical Characteristics (continued)

Characteristics noted under conditions of  $3.0V \le V_{DD} \le 5.5V$ ,  $8.0V \le V_{PWR} \le 28V$ ,  $-40^{\circ}C \le T_{C} \le 125^{\circ}C$ , unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with  $V_{PWR}$  = 13V,  $T_{A}$  = 25°C.

| Characteristic                                                                             | Symbol                | Min                   | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----|-----|------|

| SWITCH INPUT (CONTINUED)                                                                   |                       |                       |     |     |      |

| Input Offset Current when Selected as Analog                                               | I <sub>OFFSET</sub>   | -2.0                  | 1.4 | 2.0 | μΑ   |

| Input Offset Voltage when Selected as Analog V <sub>(SP&amp;SGINPUTS)</sub> to AMUX output | V <sub>OFFSET</sub>   | -10                   | 2.5 | 10  | mV   |

| Analog Operational Amplifier Output Voltage<br>Sink 250 μA                                 | V <sub>OL</sub>       | _                     | 10  | 30  | mV   |

| Analog Operational Amplifier Output Voltage<br>Source 250 μA                               | V <sub>OH</sub>       | V <sub>DD</sub> - 0.1 | -   | _   | V    |

| Switch Detection Threshold                                                                 | V <sub>TH</sub>       | 3.70                  | 4.0 | 4.3 | V    |

| Temperature Monitor <sup>(9), (10)</sup>                                                   | T <sub>LIM</sub>      | 155                   | -   | 185 | °C   |

| Temperature Monitor Hysteresis <sup>(10)</sup>                                             | T <sub>LIM(HYS)</sub> | 5.0                   | 10  | 15  | °C   |

<sup>9.</sup> Thermal shutdown of 16mA and 32mA pull-up and pull-down current sources only. 4.0mA and 2.0mA current source/sink and all other functions remain active.

<sup>10.</sup> This parameter is guaranteed by design; however it is not production tested.

### Table 4. Static Electrical Characteristics (continued)

Characteristics noted under conditions of  $3.0\text{V} \le \text{V}_{DD} \le 5.5\text{V},~8.0\text{V} \le \text{V}_{PWR} \le 28\text{V},~40^{\circ}\text{C} \le \text{T}_{C} \le 125^{\circ}\text{C},$  unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with  $\text{V}_{PWR}$  = 13V,  $\text{T}_{A}$  = 25°C.

| Characteristic                                                                        | Symbol                                                      | Min                   | Тур | Max                   | Unit     |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------|-----|-----------------------|----------|

| DIGITAL INTERFACE                                                                     | •                                                           |                       |     | •                     |          |

| Input Logic High-Voltage Thresholds <sup>(11)</sup>                                   | V <sub>IH</sub>                                             | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 | V        |

| Input Logic Low-Voltage Thresholds <sup>(11)</sup>                                    | V <sub>IL</sub>                                             | GND - 0.3             | -   | 0.2 x V <sub>DD</sub> | V        |

| SCLK, SI, Tri-State SO Input Current 0.0 V to V <sub>DD</sub>                         | I <sub>SCLK,</sub> I <sub>SI,</sub><br>I <sub>SO(TRI)</sub> | -10                   | _   | 10                    | μА       |

| CS Input Current<br>CS = V <sub>DD</sub>                                              | I <del>cs</del>                                             | -10                   | _   | 10                    | μΑ       |

| CS Pull-Up Current<br>CS = 0.0V                                                       | I <del>cs</del>                                             | 30                    | -   | 100                   | μА       |

| SO High-State Output Voltage<br>I <sub>SO(HIGH)</sub> = -200μA                        | V <sub>SO(HIGH)</sub>                                       | V <sub>DD</sub> - 0.8 | -   | VDD                   | <b>V</b> |

| SO Low-State Output Voltage  I <sub>SO(HIGH)</sub> = 1.6mA                            | V <sub>SO(LOW)</sub>                                        | _                     | _   | 0.4                   | V        |

| Input Capacitance on SCLK, SI, Tri-State SO <sup>(12)</sup>                           | C <sub>IN</sub>                                             | _                     | -   | 20                    | pF       |

| INT Internal Pull-Up Current                                                          | -                                                           | 15                    | 40  | 100                   | μΑ       |

| INT Voltage INT = Open Circuit                                                        | V <sub>INT</sub> (HIGH)                                     | VDD - 0.5             | _   | VDD                   | V        |

| INT Voltage INT = 1.0mA                                                               | V <sub>INT</sub> (LOW)                                      | _                     | 0.2 | 0.4                   | ٧        |

| WAKE Internal Pull-Up Current                                                         | IWAKE(PU)                                                   | 20                    | 40  | 100                   | μΑ       |

| WAKE Voltage WAKE = Open Circuit                                                      | V <sub>WAKE</sub> (HIGH)                                    | 4.0                   | 4.3 | 5.3                   | V        |

| WAKE Voltage IWAKE = 1.0mA                                                            | VWAKE(LOW)                                                  | _                     | 0.2 | 0.4                   | V        |

| WAKE Voltage <sup>(12)</sup> Maximum Voltage Applied to WAKE Through External Pull-Up | V <sub>WAKE</sub> (MAX)                                     | _                     | _   | 40                    | V        |

- 11. Upper and lower logic threshold voltage levels apply to SI,  $\overline{\text{CS}}$ , and SCLK.

- 12. This parameter is guaranteed by design however, is not production tested.

#### **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions of  $3.0\text{V} \le \text{VDD} \le 5.5\text{V}$ ,  $8.0\text{V} \le \text{V}_{PWR} \le 28\text{V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{\text{C}} \le 125^{\circ}\text{C}$ , unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with  $\text{V}_{PWR} = 13\text{ V}$ ,  $\text{T}_{\text{A}} = 25^{\circ}\text{C}$ .

| Characteristic                                                                       | Symbol                  | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------|-------------------------|-----|-----|-----|------|

| SWITCH INPUT                                                                         |                         |     |     | •   | •    |

| Pulse Wetting Current Time                                                           | t <sub>PULSE(ON)</sub>  | 15  | 16  | 22  | ms   |

| Interrupt Delay Time<br>Normal Mode                                                  | t <sub>INT-DLY</sub>    | _   | 5.0 | 16  | μs   |

| Sleep Mode Switch Scan Time                                                          | t <sub>SCAN</sub>       | 100 | 200 | 300 | μs   |

| Calibrated Scan Timer Accuracy Sleep Mode                                            | <sup>t</sup> SCAN TIMER | _   | _   | 10  | %    |

| Calibrated Interrupt Timer Accuracy Sleep Mode                                       | t <sub>INT TIMER</sub>  | _   | _   | 10  | %    |

| DIGITAL INTERFACE TIMING <sup>(13)</sup>                                             |                         |     |     |     | •    |

| Required Low State Duration on VPWR for Reset <sup>(14)</sup> $V_{PWR} \leq 0.2V$    | t <sub>RESET</sub>      | _   | _   | 10  | μs   |

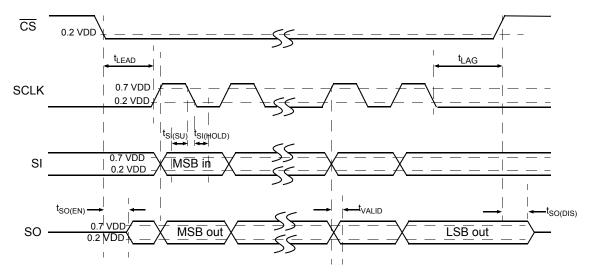

| Falling Edge of CS to Rising Edge of SCLK Required Setup Time                        | t <sub>LEAD</sub>       | 100 | _   | _   | ns   |

| Falling Edge of SCLK to Rising Edge of CS  Required Setup Time                       | t <sub>LAG</sub>        | 50  | -   | _   | ns   |

| SI to Falling Edge of SCLK<br>Required Setup Time                                    | t <sub>SI(SU)</sub>     | 16  | _   | _   | ns   |

| Falling Edge of SCLK to SI<br>Required Hold Time                                     | t <sub>SI(HOLD)</sub>   | 20  | _   | _   | ns   |

| SI, CS, SCLK Signal Rise Time <sup>(15)</sup>                                        | t <sub>R(SI)</sub>      | _   | 5.0 | -   | ns   |

| SI, $\overline{\text{CS}}$ , SCLK Signal Fall Time <sup>(15)</sup>                   | t <sub>F(SI)</sub>      | _   | 5.0 | -   | ns   |

| Time from Falling Edge of $\overline{\text{CS}}$ to SO Low Impedance <sup>(16)</sup> | t <sub>SO(EN)</sub>     | _   | _   | 55  | ns   |

| Time from Rising Edge of CS to SO High Impedance <sup>(17)</sup>                     | t <sub>SO(DIS)</sub>    | _   | _   | 55  | ns   |

| Time from Rising Edge of SCLK to SO Data Valid <sup>(18)</sup>                       | t <sub>VALID</sub>      | _   | 25  | 55  | ns   |

- 13. These parameters are guaranteed by design. Production test equipment uses 4.16MHz, 5.0V SPI interface.

- 14. This parameter is guaranteed by design but not production tested.

- 15. Rise and Fall time of incoming SI,  $\overline{CS}$ , and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

- 16. Time required for valid output status data to be available on the SO pin.

- 17. Time required for output states data to be terminated at the SO pin.

- 18. Time required to obtain valid data out from SO following the rise of SCLK with a 200pF load.

#### **TIMING DIAGRAMS**

Figure 4. SPI Timing Characteristics

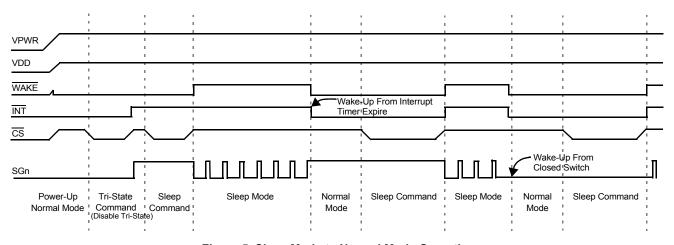

Figure 5. Sleep Mode to Normal Mode Operation

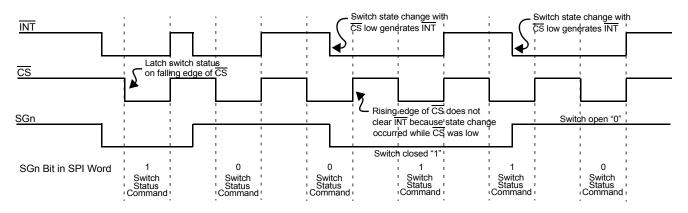

Figure 6. Normal Mode Interrupt Operation

#### **FUNCTIONAL DESCRIPTIONS**

#### INTRODUCTION

The 33975 device is an integrated circuit designed to provide systems with ultra-low quiescent sleep/wake-up modes and a robust interface between switch contacts and a microprocessor. The 33975 replaces many of the discrete components required when interfacing to microprocessor-based systems while providing switch ground offset protection, contact wetting current, and system wake-up.

The 33975 features 8-programmable switch-to-ground or switch-to-battery inputs and 14 switch-to-ground inputs. All

switch inputs may be read as analog inputs through the analog multiplexer (AMUX). Other features include a programmable wake-up timer, programmable interrupt timer, programmable wake-up/interrupt bits, and programmable wetting current settings.

This device is designed primarily for automotive applications but may be used in a variety of other applications such as computer, telecommunications, and industrial controls.

### **FUNCTIONAL PIN DESCRIPTION**

# CHIP SELECT (CS)

The system MCU selects the 33975 to receive communication using the chip select ( $\overline{\text{CS}}$ ) pin. With  $\overline{\text{CS}}$  in a logic low state, command words may be sent to the 33975 via the serial input (SI) pin, and switch status information can be received by the MCU via the serial output (SO) pin. The falling edge of  $\overline{\text{CS}}$  enables the SO output, latches the state of the  $\overline{\text{INT}}$  pin, and the state of the external switch inputs.

Rising edge of the  $\overline{\text{CS}}$  initiates the following operation:

- 1. Disables the SO driver (high-impedance)

- INT pin is reset to logic [1], except when additional switch changes occur during CS low (see <u>Figure 6</u>, page <u>11</u>).

- 1. Activates the received command word, allowing the 33975 to act upon new data from switch inputs.

To avoid any spurious data, it is essential the high-to-low and low-to-high transitions of the  $\overline{\text{CS}}$  signal occur only when SCLK is in a logic low state. A clean  $\overline{\text{CS}}$  signal is needed to ensure no incomplete SPI words are sent to the device. Internal to the 33975 device is an active pull-up to VDD on  $\overline{\text{CS}}$ .

In Sleep Mode the negative edge of  $\overline{\text{CS}}$  (VDD applied) will wake up the 33975 device. Data received from the device during  $\overline{\text{CS}}$  wake-up may not be accurate.

#### **SERIAL CLOCK (SCLK)**

The system clock (SCLK) pin clocks the internal shift register of the 33975. The SI data is latched into the input shift register on the falling edge of SCLK signal. The SO pin shifts the switch status bits out on the rising edge of SCLK. The SO data is available for the MCU to read on the falling edge of SCLK. False clocking of the shift register must be avoided to ensure validity of data. It is essential the SCLK pin be in a logic low state whenever  $\overline{\text{CS}}$  makes any transition. For this reason, it is recommended, though not necessary, that the SCLK pin is commanded to a low logic state as long as the device is not accessed and  $\overline{\text{CS}}$  is in a logic high state. When the  $\overline{\text{CS}}$  is in a logic high state, any signal on the SCLK and SI pin will be ignored and the SO pin is tri-state.

#### **SERIAL INPUT (SI)**

The SI pin is used for serial instruction data input. SI information is latched into the input register on the falling edge of SCLK. A logic high state present on SI will program a *one* in the command word on the rising edge of the CS signal. To program a complete word, 24 bits of information must be entered into the device.

#### **SERIAL OUTPUT (SO)**

The SO pin is the output from the shift register. The SO pin remains tri-stated until the  $\overline{\text{CS}}$  pin transitions to a logic low state. All *open switches* are reported as a *zero*, all *closed switches* are reported as a *one*. The negative transition of  $\overline{\text{CS}}$  enables the SO driver.

The first positive transition of SCLK will make the status data bit 24 available on the SO pin. Each successive positive clock will make the next status data bit available for the MCU to read on the falling edge of SCLK. The SI/SO shifting of the data follows a first-in-first-out protocol, with both input and output words transferring the most significant bit (MSB) first.

# INTERRUPT OUTPUT (INT)

The  $\overline{\text{INT}}$  pin is an interrupt output from the 33975 device. The  $\overline{\text{INT}}$  pin is an open-drain output with an internal pull-up to VDD. In Normal Mode, a switch state change will trigger the  $\overline{\text{INT}}$  pin (when enabled). The  $\overline{\text{INT}}$  pin is latched on the falling edge of  $\overline{\text{CS}}$ , and cleared on the rising edge of  $\overline{\text{CS}}$ . The  $\overline{\text{INT}}$  pin will not clear with rising edge of  $\overline{\text{CS}}$  if a switch contact change has occurred while the  $\overline{\text{CS}}$  was low.

In a multiple 33975 device system with WAKE high and VDD on (Sleep Mode), the falling edge of INT will place all 33975s in Normal Mode.

# **WAKE INPUT (WAKE)**

The WAKE pin is an open-drain output and a wake-up input. The pin is designed to control a power supply Enable pin. In the Normal Mode, the WAKE pin is low. In the Sleep Mode, the WAKE pin is high. The WAKE pin has a pull-up to the internal +5.0V supply.

#### 33975

In Sleep Mode with the  $\overline{\text{WAKE}}$  pin high, the falling edge of  $\overline{\text{WAKE}}$  will place the 33975 in Normal Mode. In Sleep Mode with VDD applied, the  $\overline{\text{INT}}$  pin must be high for a negative edge of  $\overline{\text{WAKE}}$  to wake up the device. If VDD is not applied to the device in Sleep Mode,  $\overline{\text{INT}}$  does not affect the  $\overline{\text{WAKE}}$  operation.

#### LOAD SUPPLY VOLTAGE (VPWR)

The VPWR pin is battery input and Power-ON Reset to the 33975 IC. The VPWR pin requires external reverse battery and transient protection. The maximum input voltage on  $V_{PWR}$  is 50V. All wetting, sustain, and internal logic current is provided from the  $V_{PWR}$  pin.

#### **LOGIC VOLTAGE (VDD)**

The VDD input pin is used to determine logic levels on the microprocessor interface (SPI) pins. Current from VDD is used to drive the SO output, and the pull-up current for  $\overline{\text{CS}}$  and  $\overline{\text{INT}}$  pins. VDD must be applied for a wake-up from the negative edge of  $\overline{\text{CS}}$  or  $\overline{\text{INT}}$ .

#### **GROUND (GND)**

The GND pin provides ground for the IC as well as ground for inputs programmed as switch-to-battery inputs.

#### PROGRAMMABLE SWITCHES (SP0-SP7)

The 33975 device has 8 switch inputs capable of being programmed to read switch-to-ground or switch-to-battery contacts. The input is compared with a 4.0V reference. When programmed to be switch-to-battery, voltages greater than 4.0V are considered closed. Voltages less than 4.0V are considered open. The opposite holds true when inputs are programmed as switch-to-ground. Programming features are defined in Table 6 through Table 11 in the Functional Device Operation section of this datasheet beginning on page 16. Voltages greater than the  $V_{PWR}$  supply voltage will source current through the SP inputs to the VPWR pin. Transient battery voltages greater than 38/40V must be clamped by an external device.

#### SWITCH-TO-GROUND (SG0-SG13)

The SGn pins are switch-to-ground inputs only. The input is compared with a 4.0V reference. Voltages greater than 4.0V are considered open. Voltages less than 4.0V are considered closed. Programming features are defined in Table 6 through Table 11 in the Functional Device Operation section of this datasheet beginning on page 16. Voltages greater than the  $V_{PWR}$  supply voltage will source current through the SG inputs to the VPWR pin. Transient battery voltages greater than 38/40V must be clamped by an external device.

# FUNCTIONAL INTERNAL BLOCK DESCRIPTION MC33975 - Functional Block Diagram **Analog Control** Programmable and Protection Circuitry Monitor Inputs Bandgap Voltage Regulation SP0 - SP7 Temp. Sense Oscillator & Clock **MCU Interface and Control** Monitor Inputs Interrupt/Wake-up SG0 - SG13 **SPI Interface Multiplex Control** Control & Protection Interface & Control Prog. Monitor Monitor

Figure 7. Functional Internal Block Description

# ANALOG CONTROL AND PROTECTION CIRCUITRY:

The 33975 is designed to operate from 5.5V to 38/40V on the VPWR terminal. Characteristics are provided from 8.0V to 28V for the device. Switch contact currents and the internal logic supply are generated from the VPWR terminal. The VDD supply terminal is used to set the SPI communication voltage levels, current source for the SO driver, and pull-up current on  $\overline{\text{INT}}$  and  $\overline{\text{CS}}$ .

The on-chip voltage regulator and bandgap supplies the required voltages to the internal monitor circuitry. The temperature monitor is active in the Normal Mode.

### MCU INTERFACE AND CONTROL:

The 33975 Multiple Switch Detection Interface with Suppressed Wake-up is designed to detect the closing and opening of up to 22 switch contacts. The switch status, either open or closed, is transferred to the microprocessor unit (MCU) through a serial peripheral interface (SPI).

The device also features a 22-to-1 analog multiplexer for reading inputs as analog. The 33975 device has two modes of operation, Normal and Sleep.

#### SWITCH PROGRAMMABLE INPUTS:

Programmable switch detection inputs. These 8 inputs can selectively detect switch closures to Ground or Battery. The 33975 device has 8 switch inputs capable of being programmed to read switch-to-ground or switch-to-battery contacts. The input is compared with a 4.0V reference. When programmed to be switch-to-battery, voltages greater than 4.0V are considered closed. Voltages less than 4.0V are considered open. The opposite holds true when inputs are programmed as switch-to-ground.

#### SWITCH-TO-GROUND INPUTS:

Switch detection interface inputs. These 14 inputs can detect switch closures to ground only. The input is compared with a 4.0V reference. Voltages greater than 4.0V are considered open. Voltages less than 4.0V are considered closed. Note: Each of these inputs may be used to supply current to sensors external to a module.

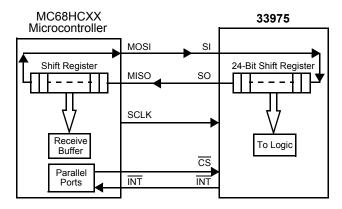

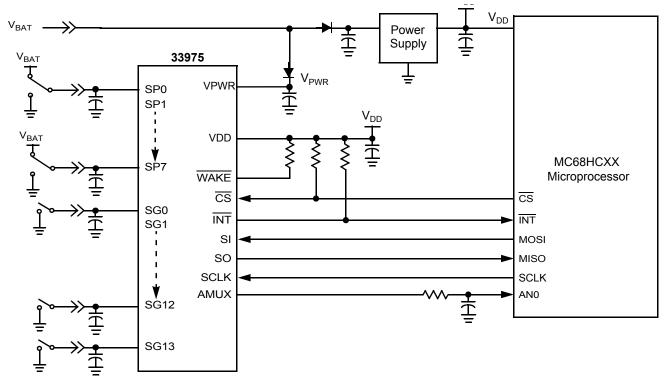

#### MCU INTERFACE DESCRIPTION

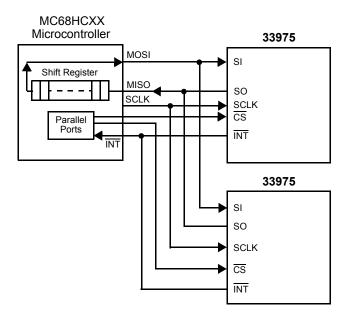

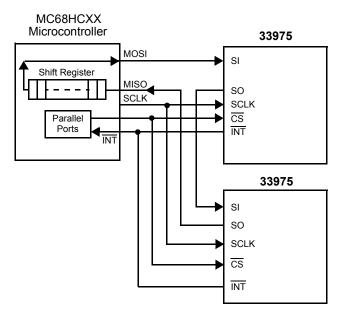

The 33975 device directly interfaces to a 3.3V or 5.0V microcontroller unit (MCU). SPI serial clock frequencies up to 6.0MHz may be used for programming and reading switch input status (production tested at 4.16MHz). Figure 8 illustrates the configuration between an MCU and one 33975.

Serial peripheral interface (SPI) data is sent to the 33975 device through the SI input pin. As data is being clocked into the SI pin, status information is being clocked out of the device by the SO output pin. The response to a SPI command will always return the switch status, reset flag, and thermal flag. Input switch states are latched into the SO register on the falling edge of the chip select  $(\overline{\text{CS}})$  pin. Twenty-four bits are required to complete a transfer of information between the 33975 and the MCU.

Figure 8. SPI Interface with Microprocessor

Two or more 33975 devices may be used in a module system. Multiple ICs may be SPI-configured in parallel or serial. Figures 9 and 10 show the configurations. When using the serial configuration, 48-clock cycles are required to transfer data in/out of the ICs.

Figure 9. SPI Parallel Interface with Microprocessor

Figure 10. SPI Serial Interface with Microprocessor

#### **FUNCTIONAL DEVICE OPERATION**

#### **POWER SUPPLY**

The 33975 is designed to operate from 5.5V to 38/40V on the VPWR pin. Characteristics are provided from 8.0V to 28V for the device. Switch contact currents and the internal logic supply are generated from the VPWR pin. The VDD supply pin is used to set the SPI communication voltage levels, current source for the SO driver, and pull-up current on  $\overline{\text{INT}}$  and  $\overline{\text{CS}}$ .

VDD supply may be removed from the device to reduce quiescent current. If VDD is removed while the device is in Normal Mode, the device will remain in Normal Mode. If VDD is removed in Sleep Mode, the device will remain in Sleep Mode until a wake-up input is received (WAKE high to low, switch input or interrupt timer expires).

Removing VDD from the device disables SPI communication and will not allow the device to wake up from the  $\overline{\text{INT}}$  and  $\overline{\text{CS}}$  pins.

#### **POWER-ON RESET (POR)**

Applying VPWR to the device will cause a Power-ON Reset and place the device in Normal Mode.

Default settings from Power-ON Reset via a VPWR or Reset Command are as follows:

- Programmable switch Set to switch-to-battery

- · All inputs set as wake-up

- · Wetting current on (16mA pull-down, 32mA pull-up)

- Wetting current timer on (20ms)

- · All inputs tri-state

- Analog select 00000 (no input channel selected)

**Note** The 33975 device provides indication that a reset has occurred by placing a logic [1] in bit 22 of the SO buffer. The reset bit is cleared on rising edge of CS.

#### **OPERATIONAL MODES**

The 33975 has two operating modes, Normal Mode and Sleep Mode. A discussion on Normal Mode begins below. A discussion on Sleep Mode begins on page <u>22</u>.

#### **NORMAL MODE**

Normal Mode may be entered by the following events:

- · Application of VPWR to the IC

- · Change-of-switch state (when enabled)

- Falling edge of WAKE

- Falling edge of INT (with VDD = 5.0V and WAKE at Logic [1])

- Falling edge of CS (with VDD = 5.0V)

- · Interrupt timer expires

Only in Normal Mode with VDD applied can the registers of the 33975 be programmed through the SPI.

The registers that may be programmed in Normal Mode are listed below. Further explanation of each register is provided in subsequent paragraphs.

- Programmable Switch Register (Settings Command)

- Wake-up/Interrupt Register (Wake-up/Interrupt Command)

- Wetting Current Register (Metallic Command)

- Wetting Current Timer Register (Wetting Current Timer Enable Command)

- Tri-state Register (Tri-state Command)

- Analog Select Register (Analog Command)

- Calibration of Timers (Calibration Command)

- Reset (Reset Command)

<u>Figure 6</u>, page <u>11</u>, is a graphical description of the device operation in Normal Mode. Switch states are latched into the input register on the falling edge of  $\overline{CS}$ . The  $\overline{INT}$  to the MCU is cleared on the rising edge of  $\overline{CS}$ . However,  $\overline{INT}$  will not clear on the rising edge of  $\overline{CS}$  if a switch has closed during SPI communication ( $\overline{CS}$  low). This prevents switch states from being missed by the MCU.

#### PROGRAMMABLE SWITCH REGISTER

Inputs SP0 to SP7 may be programmable for switch-to-battery or switch-to-ground. These inputs types are defined using the *settings command* (refer to Table 6). To set an SPn input for switch-to-battery, a logic [1] for the appropriate bit must be set. To set an SPn input for switch-to-ground, a logic [0] for the appropriate bit must be set. The MCU may change or update the Programmable Switch Register via software at any time in Normal Mode. Regardless of the setting, when the SPn input switch is closed a logic [1] will be placed in the Serial Output Response Register (refer to Table 17, page 21).

**Table 6. Settings Command**

| Settings Command |    |    |    |    |    |    |    | Not used |    |    |    |    |    |   |   | Battery/Ground Select |     |     |     |     |     |     |     |

|------------------|----|----|----|----|----|----|----|----------|----|----|----|----|----|---|---|-----------------------|-----|-----|-----|-----|-----|-----|-----|

| 23               | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15       | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| 0                | 0  | 0  | 0  | 0  | 0  | 0  | 1  | Х        | Х  | Х  | Х  | Х  | Х  | Х | Х | sp7                   | sp6 | sp5 | sp4 | sp3 | sp2 | sp1 | sp0 |

#### WAKE-UP/INTERRUPT REGISTER

The Wake-up/Interrupt Register defines the inputs that are allowed to wake the 33975 from Sleep Mode or set the  $\overline{\text{INT}}$  pin low in Normal Mode. Programming the wake-up/interrupt bit to logic [0] will disable the specific input from generating an interrupt and will disable the specific input from waking the IC in Sleep Mode (refer to Table 7). Programming the wake-

up/interrupt bit to logic [1] will enable the specific input to generate an interrupt with switch change of state and will enable the specific input as wake-up. The MCU may change or update the Wake-up/Interrupt Register via software at any time in Normal Mode.

Table 7. Wake-Up/Interrupt Command

|    | Wake-up/Interrupt Command |    |    |    |    |    |    |    | Command Bits |          |          |          |          |     |     |     |     |     |     |     |     |     |     |

|----|---------------------------|----|----|----|----|----|----|----|--------------|----------|----------|----------|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 23 | 22                        | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14           | 13       | 12       | 11       | 10       | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| 0  | 0                         | 0  | 0  | 0  | 0  | 1  | 0  | Х  | Х            | Х        | Х        | Х        | Х        | Х   | Х   | sp7 | sp6 | sp5 | sp4 | sp3 | sp2 | sp1 | sp0 |

| 0  | 0                         | 0  | 0  | 0  | 0  | 1  | 1  | Х  | Х            | sg1<br>3 | sg1<br>2 | sg1<br>1 | sg1<br>0 | sg9 | sg8 | sg7 | sg6 | sg5 | sg4 | sg3 | sg2 | sg1 | sg0 |

#### WETTING CURRENT REGISTER

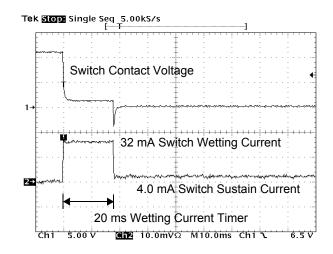

The 33975 has two levels of switch-to-ground contact current, 32mA and 4.0mA, and two levels of switch-to-battery contact current, 16mA and 2.0mA (see Figure 11). The metallic command is used to set the switch contact current level (refer to Table 8). Programming the metallic bit to logic [0] will set the switch wetting current to 2.0mA/4.0mA. Programming the metallic bit to logic [1] will set the switch contact wetting current to 16mA/32mA. The MCU may change or update the Wetting Current Register via software at any time in Normal Mode.

Wetting current is designed to provide higher levels of current during switch closure. The higher level of current is designed to keep switch contacts from building up oxides that form on the switch contact surface.

Figure 11. Contact Wetting and Sustain Current for Switch-to-Ground Input

**Table 8. Metallic Command**

|    |    | Met | allic C | Comm | and |    |    |    |    |          |          |          |          | C   | omma | nd Bi | ts  |     |     |     |     |     |     |

|----|----|-----|---------|------|-----|----|----|----|----|----------|----------|----------|----------|-----|------|-------|-----|-----|-----|-----|-----|-----|-----|

| 23 | 22 | 21  | 20      | 19   | 18  | 17 | 16 | 15 | 14 | 13       | 12       | 11       | 10       | 9   | 8    | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| 0  | 0  | 0   | 0       | 0    | 1   | 0  | 0  | Х  | Х  | Х        | Х        | Х        | Х        | Х   | Х    | sp7   | sp6 | sp5 | sp4 | sp3 | sp2 | sp1 | sp0 |

| 0  | 0  | 0   | 0       | 0    | 1   | 0  | 1  | Х  | X  | sg1<br>3 | sg1<br>2 | sg1<br>1 | sg1<br>0 | sg9 | sg8  | sg7   | sg6 | sg5 | sg4 | sg3 | sg2 | sg1 | sg0 |

#### WETTING CURRENT TIMER REGISTER

Each switch input has a designated 20ms timer. The timer starts when the specific switch input crosses the comparator threshold (4.0V). When the 20ms timer expires, the contact current is reduced from 16mA to 2.0mA for switch-to-battery inputs and 32mA to 4.0mA for switch-to-ground inputs. The wetting current timer may be disabled for a specific input. When the timer is disabled, wetting current will continue to flow through the closed switch contact. With multiple wetting

current timers disabled, power dissipation for the IC must be considered.

The MCU may change or update the Wetting Current Timer Register via software at any time in Normal Mode. This allows the MCU to control the amount of time wetting current is applied to the switch contact. Programming the wetting current timer bit to logic [0] will disable the wetting current timer. Programming the wetting current timer bit to logic [1] will enable the wetting current timer (refer to Table 9).

33975

**Table 9. Wetting Current Timer Enable Command**

| ,  | Wettir | ıg Cuı | rrent 1 | Timer | Comr | nands | <b>S</b> |    |    |          |          |          |          | С   | omma | nd Bi | ts  |     |     |     |     |     |     |

|----|--------|--------|---------|-------|------|-------|----------|----|----|----------|----------|----------|----------|-----|------|-------|-----|-----|-----|-----|-----|-----|-----|

| 23 | 22     | 21     | 20      | 19    | 18   | 17    | 16       | 15 | 14 | 13       | 12       | 11       | 10       | 9   | 8    | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| 0  | 0      | 0      | 0       | 0     | 1    | 1     | 1        | Х  | Х  | Х        | Х        | Х        | Х        | Х   | Х    | sp7   | sp6 | sp5 | sp4 | sp3 | sp2 | sp1 | sp0 |

| 0  | 0      | 0      | 0       | 1     | 0    | 0     | 0        | X  | X  | sg1<br>3 | sg1<br>2 | sg1<br>1 | sg1<br>0 | sg9 | sg8  | sg7   | sg6 | sg5 | sg4 | sg3 | sg2 | sg1 | sg0 |

#### TRI-STATE REGISTER

The *tri-state command* is use to set the SPn or SGn input node as high-impedance (refer to <u>Table 10</u>). By setting the Tri-state Register bit to logic [1], the input will be high-impedance regardless of the metallic command setting. The

comparator on each input remains active. This command allows the use of each input as a comparator with a 4.0V threshold. The MCU may change or update the Tri-state Register via software at any time in Normal Mode.

Table 10. Tri-State Command

|    |    | Tri-S | tate C | omm | ands |    |    |    |    |      |      |      |      | Com | mand | Bits |     |     |     |     |     |     |     |

|----|----|-------|--------|-----|------|----|----|----|----|------|------|------|------|-----|------|------|-----|-----|-----|-----|-----|-----|-----|

| 23 | 22 | 21    | 20     | 19  | 18   | 17 | 16 | 15 | 14 | 13   | 12   | 11   | 10   | 9   | 8    | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| 0  | 0  | 0     | 0      | 1   | 0    | 0  | 1  | Х  | Х  | Х    | Х    | Х    | Х    | Х   | Х    | sp7  | sp6 | sp5 | sp4 | sp3 | sp2 | sp1 | sp0 |

| 0  | 0  | 0     | 0      | 1   | 0    | 1  | 0  | Х  | Х  | sg13 | sg12 | sg11 | sg10 | sg9 | sg8  | sg7  | sg6 | sg5 | sg4 | sg3 | sg2 | sg1 | sg0 |

#### **ANALOG SELECT REGISTER**

The analog voltage on switch inputs may be read by the MCU using the *analog command* (refer to <u>Table 11</u>). Internal to the IC is a 22-to-1 analog multiplexer. The voltage present on the selected input pin is buffered and made available on the AMUX output pin. The AMUX output pin is clamped to a maximum of VDD volts regardless of the higher voltages present on the input pin. After an input has been selected as the analog, the corresponding bit in the next SO data stream will be logic [0]. When selecting a channel to be read as analog, the user must also set the desired current (32mA, 4.0mA, or high-impedance). Setting bit 6 and bit 5 to 0,0 selects the input as high-impedance. Setting bit 6 and bit 5 to

0,1 selects 4.0mA, and 1,0 selects 32mA. Setting bit 6 and bit 5 to 1,1 in the Analog Select Register is not allowed and will place the input as an analog input with high-impedance.

Analog currents set by the *analog command* are pull-up currents for all SGn and SPn inputs (refer to <u>Table 11</u>). The *analog command* does not allow pull-down currents on the SPn inputs. Setting the current to 32mA or 4.0mA may be useful for reading sensor inputs. Further information is provided in the <u>Typical Applications</u> section of this datasheet beginning on page <u>24</u>. The MCU may change or update the Analog Select Register via software at any time in Normal Mode.

**Table 11. Analog Command**

|    |    | Ana | alog C | omm | and |    |    |    |    |    | N  | ot use | ed |   |   |   | Cur<br>Sel | rent<br>ect | An | alog C | Chann | el Sel | ect |

|----|----|-----|--------|-----|-----|----|----|----|----|----|----|--------|----|---|---|---|------------|-------------|----|--------|-------|--------|-----|

| 23 | 22 | 21  | 20     | 19  | 18  | 17 | 16 | 15 | 14 | 13 | 12 | 11     | 10 | 9 | 8 | 7 | 6          | 5           | 4  | 3      | 2     | 1      | 0   |

| 0  | 0  | 0   | 0      | 0   | 1   | 1  | 0  | Х  | Х  | Х  | Х  | Х      | Х  | Х | Х | Х | 32<br>mA   | 4.0<br>mA   | 0  | 0      | 0     | 0      | 0   |

Table 12. Analog Channel

| Bits 43210 | Analog Channel Select |

|------------|-----------------------|

| 00000      | No Input Selected     |

| 00001      | SG0                   |

| 00010      | SG1                   |

| 00011      | SG2                   |

| 00100      | SG3                   |

| 00101      | SG4                   |

| 00110      | SG5                   |

| 00111      | SG6                   |

| 01000      | SG7                   |

| 01001      | SG8                   |

| 01010      | SG9                   |

| 01011      | SG10                  |

| 01100      | SG11                  |

| 01101      | SG12                  |

| 01110      | SG13                  |

| 01111      | SP0                   |

| 10000      | SP1                   |

| 10001      | SP2                   |

| 10010      | SP3                   |

| 10011      | SP4                   |

| 10100      | SP5                   |

| 10101      | SP6                   |

| 10110      | SP7                   |

#### **CALIBRATION OF TIMERS**

In cases where an accurate time base is required, the user may calibrate the internal timers using the *calibration* command (refer to Table 13). After the 33975 device receives the calibration command, the device expects  $512\mu s$  logic [0] calibration pulse on the  $\overline{CS}$  pin. The pulse is used to calibrate the internal clock. No other SPI pins should transition during this  $512\mu s$  calibration pulse. Because the

oscillator frequency changes with temperature, calibration is required for an accurate time base. Calibrating the timers has no affect on the quiescent current measurement. The calibration command simply makes the time base more accurate. The *calibration command* may be used to update the device on a periodic basis. All reset conditions clear the calibration register and places the device in the uncalibrated state.

**Table 13. Calibration Command**

|    |    | Calib | ration | Com | mand |    |    |    |    |    |    |    |    | C | omma | ınd Bi | ts |   |   |   |   |   |   |

|----|----|-------|--------|-----|------|----|----|----|----|----|----|----|----|---|------|--------|----|---|---|---|---|---|---|

| 23 | 22 | 21    | 20     | 19  | 18   | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7      | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 0  | 0     | 0      | 1   | 0    | 1  | 1  | Х  | Х  | Х  | Х  | Х  | Х  | Х | Х    | Х      | Х  | Х | Х | Х | Х | Х | Х |

#### **RESET**

The reset command resets all registers to Power-ON Reset (POR) state. Refer to <u>Table 15</u>, page <u>20</u>, for POR

states or the paragraph entitled Power-ON Reset (POR) on page <u>16</u> of this datasheet.

Table 14. Reset Command

|    |    | Re | set Co | omma | ınd |    |    |    |    |    |    |    |    | C | omma | ınd Bi | ts |   |   |   |   |   |   |

|----|----|----|--------|------|-----|----|----|----|----|----|----|----|----|---|------|--------|----|---|---|---|---|---|---|

| 23 | 22 | 21 | 20     | 19   | 18  | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7      | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 1  | 1  | 1      | 1    | 1   | 1  | 1  | Х  | Х  | Х  | Х  | Х  | Х  | Х | Х    | Х      | Х  | Х | Х | Х | Х | Х | Х |

#### **SPI COMMAND SUMMARY**

<u>Table 15</u> below provides a comprehensive list of SPI commands recognized by the 33975 and the reset state of each register. <u>Table 16</u> and <u>Table 17</u> contain the Serial

Output (SO) data for input voltages greater or less than the threshold level. Open switches are always indicated with a logic [0], closed switches are indicated with logic [1].

**Table 15. SPI Command Summary**

| MS                                                | В  |    | Com | ıman | d Bits | s  |    |    |    |    |      | Setti | ing B | its  |     |     |     |           |                |     | LSB |     |     |     |

|---------------------------------------------------|----|----|-----|------|--------|----|----|----|----|----|------|-------|-------|------|-----|-----|-----|-----------|----------------|-----|-----|-----|-----|-----|

|                                                   | 23 | 22 | 21  | 20   | 19     | 18 | 17 | 16 | 15 | 14 | 13   | 12    | 11    | 10   | 9   | 8   | 7   | 6         | 5              | 4   | 3   | 2   | 1   | 0   |

| Switch Status<br>Command                          | 0  | 0  | 0   | 0    | 0      | 0  | 0  | 0  | Х  | х  | х    | х     | х     | х    | х   | х   | Х   | х         | х              | Х   | х   | х   | х   | Х   |

| Settings Command Bat=1, Gnd=0 (Default state = 1) | 0  | 0  | 0   | 0    | 0      | 0  | 0  | 1  | X  | х  | х    | х     | х     | х    | х   | х   | SP7 | SP6       | SP5            | SP4 | SP3 | SP2 | SP1 | SP0 |

| Wake-up/Interrupt Bit<br>Wake-up=1                | 0  | 0  | 0   | 0    | 0      | 0  | 1  | 0  | Х  | Х  | Х    | х     | Х     | х    | Х   | х   | SP7 | SP6       | SP5            | SP4 | SP3 | SP2 | SP1 | SP0 |

| Nonwake-up=0<br>(Default state = 1)               | 0  | 0  | 0   | 0    | 0      | 0  | 1  | 1  | Х  | Х  | SG13 | SG12  | SG11  | SG10 | SG9 | SG8 | SG7 | SG6       | SG5            | SG4 | SG3 | SG2 | SG1 | SG0 |

| Metallic Command Metallic = 1                     | 0  | 0  | 0   | 0    | 0      | 1  | 0  | 0  | Х  | Х  | Х    | Х     | Х     | х    | Х   | Х   | SP7 | SP6       | SP5            | SP4 | SP3 | SP2 | SP1 | SP0 |

| Non-metallic = 0 (Default state = 1)              | 0  | 0  | 0   | 0    | 0      | 1  | 0  | 1  | Х  | Х  | SG13 | SG12  | SG11  | SG10 | SG9 | SG8 | SG7 | SG6       | SG5            | SG4 | SG3 | SG2 | SG1 | SG0 |

| Analog Command                                    | 0  | 0  | 0   | 0    | 0      | 1  | 1  | 0  | Х  | х  | х    | х     | х     | х    | х   | х   | Х   | 32mA<br>0 | 4.0m<br>A<br>0 | 0   | 0   | 0   | 0   | 0   |

| MS                                                       | В            |            | Com | ıman | d Bit | S   |     |     |     |     |      | Setti | ing B | its  |     |     |     |     |              |              | LSB          |               |               |               |

|----------------------------------------------------------|--------------|------------|-----|------|-------|-----|-----|-----|-----|-----|------|-------|-------|------|-----|-----|-----|-----|--------------|--------------|--------------|---------------|---------------|---------------|

| Wetting Current Timer                                    | 0            | 0          | 0   | 0    | 0     | 1   | 1   | 1   | Х   | Х   | Х    | Х     | Х     | Х    | Х   | Х   | SP7 | SP6 | SP5          | SP4          | SP3          | SP2           | SP1           | SP0           |

| Timer ON = 1 Timer OFF = 0 (Default state = 1)           | 0            | 0          | 0   | 0    | 1     | 0   | 0   | 0   | х   | х   | SG13 | SG12  | SG11  | SG10 | SG9 | SG8 | SG7 | SG6 | SG5          | SG4          | SG3          | SG2           | SG1           | SG0           |

| Tri-state Command Input Tri-state=1                      | 0            | 0          | 0   | 0    | 1     | 0   | 0   | 1   | х   | Х   | х    | х     | х     | х    | х   | х   | SP7 | SP6 | SP5          | SP4          | SP3          | SP2           | SP1           | SP0           |

| Input Active = 0                                         | 0            | 0          | 0   | 0    | 1     | 0   | 1   | 0   | Х   | х   | SG13 | SG12  | SG11  | SG10 | SG9 | SG8 | SG7 | SG6 | SG5          | SG4          | SG3          | SG2           | SG1           | SG0           |

| Calibration Command<br>(Default state -<br>uncalibrated) | 0            | 0          | 0   | 0    | 1     | 0   | 1   | 1   | х   | x   | х    | х     | x     | х    | х   | х   | х   | х   | х            | х            | х            | х             | x             | х             |

| Sleep Command<br>(See Sleep<br>Mode on page<br>22)       | 0            | 0          | 0   | 0    | 1     | 1   | 0   | 0   | х   | х   | х    | х     | х     | х    | х   | х   | Х   | х   | int<br>timer | int<br>timer | int<br>timer | scan<br>timer | scan<br>timer | scan<br>timer |

| Reset Command                                            | 0            | 1          | 1   | 1    | 1     | 1   | 1   | 1   | Х   | Х   | Х    | Х     | Х     | х    | Х   | х   | Х   | Х   | Х            | х            | Х            | Х             | Х             | х             |

| SO Response Will<br>Always Send                          | therm<br>flg | RST<br>flg | SP7 | SP6  | SP5   | SP4 | SP3 | SP2 | SP1 | SP0 | SG13 | SG12  | SG11  | SG10 | SG9 | SG8 | SG7 | SG6 | SG5          | SG4          | SG3          | SG2           | SG1           | SG0           |

Table 16. Serial Output (SO) Bit Data

| Type of Input | Input<br>Programmed | Voltage on<br>Input Pin | SO SPI Bit |

|---------------|---------------------|-------------------------|------------|

| SP            | Switch to Ground    | SPn < 4.0V              | 1          |

|               | Switch to Ground    | SPn > 4.0V              | 0          |

|               | Switch to Battery   | SPn < 4.0V              | 0          |

|               | Switch to Battery   | SPn > 4.0V              | 1          |

| SG            | N/A                 | SGn < 4.0V              | 1          |

|               | N/A                 | SGn > 4.0V              | 0          |

Table 17. Serial Output (SO) Response Register

#### **EXAMPLE OF NORMAL MODE OPERATION**

The operation of the device in Normal Mode is defined by the states of the programmable internal control registers. A typical application may have the following settings:

- · Programmable switch set to switch-to-ground

- All inputs set as wake-up

- Wetting current on (32mA)

- Wetting current timer on (20ms)

- · All inputs tri-state-disabled (comparator is active)

- Analog select 00000 (no input channel selected)

With the device programmed as above, an interrupt will be generated with each switch contact change of state (open-toclose or close-to-open) and 32mA of contact wetting current will be source for 20ms. The  $\overline{\text{INT}}$  pin will remain low until switch status is acknowledged by the microprocessor. It is critical to understand  $\overline{\text{INT}}$  will not be cleared on the rising edge of  $\overline{\text{CS}}$  if a switch closure occurs while the  $\overline{\text{CS}}$  is low. The maximum duration a switch state change can exist without acknowledgement depends on the software response time to the interrupt. Figure 6, page 11, shows the interaction between changing input states and the  $\overline{\text{INT}}$  and  $\overline{\text{CS}}$  pins.

If desired the user may disable interrupts (*wake-up/interrupt command*) from the 33975 device and read the switch states on a periodic basis. Switch activation and deactivation faster than the MCU read rate will not be acknowledged.

33975

The 33975 device will exit the Normal Mode and enter the Sleep Mode only with a valid sleep command.

#### **SLEEP MODE**

Sleep Mode is used to reduce system quiescent currents. Sleep Mode may be entered only by sending the *sleep command*. All register settings programmed in Normal Mode will be maintained in Sleep Mode.

The 33975 will exit Sleep Mode and enter Normal Mode when any of the following events occur:

- Input switch change of state (when enabled)

- · Interrupt timer expire

- Falling edge of WAKE

- Falling edge of INT (with VDD = 5.0V and WAKE at Logic [1])

- Falling edge of CS (with VDD = 5.0V)

- · Power-on reset (POR)

The VDD supply may be removed from the device during Sleep Mode. However removing VDD from the device in Sleep Mode will disable a wake-up from falling edge of  $\overline{\text{INT}}$  and  $\overline{\text{CS}}$ .

**Note**: In cases where  $\overline{\text{CS}}$  is used to wake the device, the first SO data message is not valid.

The sleep command contains settings for two programmable timers for Sleep Mode, the interrupt timer and the scan timer, as shown in Table 18.

Table 18. Sleep Command

|    |    | Sle | ep Co | omma | nd |    |    |    |    |    |    |    |    | C | omma | nd Bi | ts |           |           |           |            |            |            |

|----|----|-----|-------|------|----|----|----|----|----|----|----|----|----|---|------|-------|----|-----------|-----------|-----------|------------|------------|------------|

| 23 | 22 | 21  | 20    | 19   | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7     | 6  | 5         | 4         | 3         | 2          | 1          | 0          |

| 0  | 0  | 0   | 0     | 1    | 1  | 0  | 0  | Х  | Х  | Х  | Х  | Х  | Х  | Х | Х    | Х     | Х  | int timer | int timer | int timer | scan timer | scan timer | scan timer |

The interrupt timer is used as a periodic wake-up timer. When the timer expires, an interrupt is generated and the device enters Normal Mode.

**Note**: The interrupt timer in the 33975 device may be disabled by programming the interrupt bits to logic [1 1 1].

<u>Table 19</u> shows the programmable settings of the Interrupt timer.

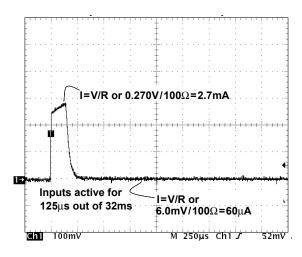

The scan timer sets the polling period between input switch reads in Sleep Mode. The period is set in the *sleep command* and may be set to 000 (no period) to 111 (64ms). In Sleep Mode when the scan timer expires, inputs will behave as programmed prior to sleep command. The 33975 will wake up for approximately 125µs and read the switch inputs. At the end of the 125µs, the input switch states are compared with the switch state prior to sleep command. When switch state changes are detected, an interrupt (when enabled; refer to *wake-up/interrupt command* description on page 17) is generated and the device enters Normal Mode. Without switch state changes, the 33975 will reset the scan timer, inputs become tri-state, and the Sleep Mode continues until the scan timer expires again.

<u>Table 20</u> shows the programmable settings of the Scan timer.

**Note**: The interrupt and scan timers are disabled in the Normal Mode.

Table 19. Interrupt Timer

| Bits 543 Interrupt Period |                      |  |  |

|---------------------------|----------------------|--|--|

| 000                       | 32ms                 |  |  |

| 001                       | 64ms                 |  |  |

| 010                       | 128ms                |  |  |

| 011                       | 256ms                |  |  |

| 100                       | 512ms                |  |  |

| 101                       | 1.024s               |  |  |

| 110                       | 2.048s               |  |  |

| 111                       | No interrupt wake-up |  |  |

Table 20. Scan Timer

| Bits 210 | Scan Period |

|----------|-------------|

| 000      | No Scan     |

| 001      | 1.0ms       |

| 010      | 2.0ms       |

| 011      | 4.0ms       |

| 100      | 8.0ms       |

| 101      | 16ms        |

| 110      | 32ms        |

| 111      | 64ms        |

Figure 5, page 11, is a graphical description of how the 33975 device exits Sleep Mode and enters Normal Mode. Notice that the device will exit Sleep Mode when the interrupt timer expires or when a switch change of state occurs. The falling edge of  $\overline{\text{INT}}$  triggers the MCU to wake from Sleep state. Figure 12 illustrates the current consumed during Sleep Mode. During the 125μs, the device is fully active and switch states are read. The quiescent current is calculated by integrating the normal running current over scan period plus approximately  $60\mu\text{A}$ .

Figure 12. Sleep Current Waveform

#### **TEMPERATURE MONITOR**

With multiple switch inputs closed and the device programmed with the wetting current timers disabled, considerable power will be dissipated by the IC. For this reason temperature monitoring has been implemented. The temperature monitor is active in the Normal Mode only. When the IC temperature is above the thermal limit, the temperature monitor will do all of the following:

- · Generate an interrupt.

- Force all wetting current sources to revert to 2.0mA/ 4.0mA sustain currents

- Maintain the 2.0mA/4.0mA sustain currents and all other functionality.

- · Set the thermal flag bit in the SPI output register.

The thermal flag bit in the SPI word will be cleared on the rising edge of  $\overline{\text{CS}}$  provided the die temperature has cooled below the thermal limit. When die temperature has cooled below thermal limit, the device will resume previously programmed settings.

#### TYPICAL APPLICATIONS

The 33975's primary function is the detection of open or closed switch contacts. However, there are many features that allow the device to be used in a variety of applications. The following is a list of applications to consider for the IC:

- · Sensor power supply

- Switch monitor for metallic or elastomeric switches

- · Analog sensor inputs (Ratiometric)

- · Power MOSFET/LED driver and monitor

- · Multiple 33975 devices in a module system

The following paragraphs describe the applications in detail.

#### SENSOR POWER SUPPLY

Each input may be used to supply current to sensors external to a module. Many sensors such as Hall effect, pressure sensors, and temperature sensors require a supply voltage to power the sensor, and provide an open collector or analog output. Figure 13 shows how the 33975 may be used to supply power and interface to these types of sensors. In an application where the input makes continuous transitions, consider using the wake-up/interrupt command to disable the interrupt for the particular input.

Figure 13. Sensor Power Supply

#### **METALLIC/ELASTOMERIC SWITCH**

Metallic switch contacts often develop higher contact resistance over time owing to contact corrosion. The corrosion is induced by humidity, salt, and other elements that exist in the environment. For this reason the 33975 provides two settings for contacts. When programmed for metallic switches, the device provides higher wetting current to keep switch contacts free of oxides. The higher current occurs for the first 20ms of switch closure. Where longer duration of wetting current is desired, the user may send the wetting current timer command and disable the timer. Wetting current will be continuous to the closed switch. After the time period set by the MCU, the wetting current timer command may be sent again to enable the timer. The user must consider power dissipation on the device when disabling the timer. (Refer to the paragraph entitled Temperature Monitor, page 23.)

To increase the amount of wetting current for a switch contact, the user has two options. Higher wetting current to a switch may be achieved by paralleling SGn or SPn inputs. This will increase wetting current by 32mA for each input added to the switch-to-ground contact and 16mA for switch-to-battery contacts. The second option is to simply add an external resistor pull-up to the  $V_{PWR}$  supply for switch-to-ground inputs or a resistor to ground for a switch-to-battery input. Adding an external resistor has no effect on the operation of the device.

Elastomeric switch contacts are made of carbon and have a high contact resistance. Resistance of 1.0 k $\Omega$  is common. In applications with elastomeric switches, the pull-up and pull-down currents must be reduced to prevent excessive power dissipation at the contact. Programming for a lower current settings is provided in the Functional Device Operation Section beginning on page  $\underline{16}$  under  $\underline{Table~8}$ , Metallic Command.

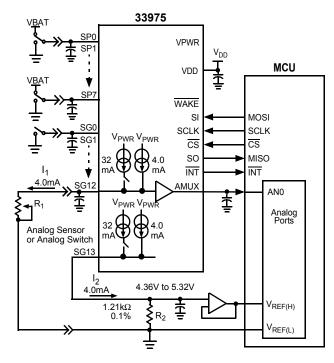

#### **ANALOG SENSOR INPUTS (RATIOMETRIC)**

The 33975 features a 22-to-1 analog multiplexer. Setting the binary code for a specific input in the *analog command* allows the microcontroller to perform analog to digital conversion on any of the 22 inputs. On rising edge of the  $\overline{\text{CS}}$ , the multiplexer connects a requested input to the AMUX pin. The AMUX pin is clamped to max of VDD volts regardless of the higher voltages present on the input pin. After an input has been selected as the analog, the corresponding bit in the next SO data stream will be logic [0].

The input pin, when selected as analog, may be configured as analog with high-impedance, analog with 4.0mA pull-up, or analog with 32mA pull-up. Figure 14, page 25, shows how the 33975 may be used to provide a ratiometric reading of variable resistive input.

Figure 14. Analog Ratiometric Conversion

To read a potentiometer sensor, the wiper should be grounded and brought back to the module ground, as illustrated in <u>Figure 14</u>. With the wiper changing the impedance of the sensor, the analog voltage on the input will represent the position of the sensor.

Using the Analog feature to provide 4.0mA of pull-up current to an analog sensor may induce error due to the accuracy of the current source. For this reason, a ratiometric conversion must be considered. Using two current sources (one for the sensor and one to set the reference voltage to the A/D converter) will yield a maximum error (owing to the 33975) of 4%.

Higher accuracy may be achieved through module level calibration. In this example, we use the resistor values from Figure 14 and assume the current sources are 4% from each other. The user may use the module end-of-line tester to calculate the error in the A/D conversion. By placing a 1.0k $\Omega$ , 0.1% resistor in the end-of-line test equipment and assuming a perfect 4.0mA current source from the 33975, a calculated A/D conversion may be obtained.

ADC =

$$\frac{11 \times R1}{12 \times R2} \times 255$$

ADC =  $\frac{4.0 \text{mA} \times 1.0 \text{k}\Omega}{4.0 \text{mA} \times 1.21 \text{k}\Omega} \times 255$

ADC = 210 counts

Using the equation yields the following:

The ADC value of 213 counts is the value with 0% error (neglecting the resistor tolerance and AMUX input offset voltage). Now calculate the count value induced by the mismatch in current sources. From a sample device the maximum current source was measured at 3.979mA and minimum current source was measured at 3.933mA. This yields 1.16% error in A/D conversion due to the current source mismatch. The A/D measurement will be as follows:

ADC =

$$\frac{3.933 \text{ mA x } 1.0 \text{k}\Omega}{3.979 \text{ mA x } 1.21 \text{k}\Omega} \times 255$$

ADC = 208 counts

This A/D conversion is 1.16% low in value. The error correction factor of 1.0115 may be used to correct the value:

An error correction factor may then be stored in E<sup>2</sup> memory and used in the A/D calculation for the specific input. Each input used as analog measurement will have a dedicated calibrated error correction factor.

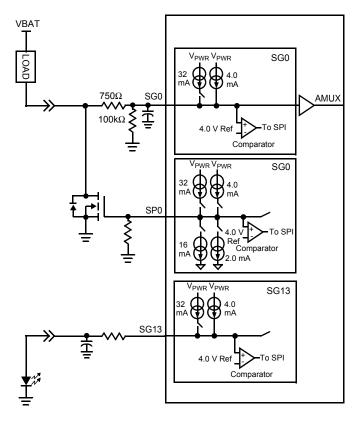

#### POWER MOSFET/LED DRIVER AND MONITOR

Because of the flexible programming of the 33975 device, it may be used to drive small loads like LEDs or MOSFET gates. It was specifically designed to power up in the Normal Mode with the inputs tri-state. This was done to ensure the LEDs or MOSFETs connected to the 33975 power up in the off-state. The Switch Programmable (SP0–SP7) inputs have a source-and-sink capability, providing effective MOSFET gate control. To complete the circuit, a pull-down resistor should be used to keep the gate from floating during the Sleep Modes. Figure 15, page 26, shows an application where the SG0 input is used to monitor the drain-to-source voltage of the external MOSFET. The 750 $\Omega$  resistor is used to set the drain-to-source trip voltage. With the 4.0mA current source enabled, an interrupt will be generated when the drain-to-source voltage is approximately 1.0V.

Figure 15. MOSFET or LED Driver Output

The sequence of commands (from Normal Mode with inputs tri-state) required to set up the device to drive a MOSFET are as follows:

- wetting current timer enable command Disable SPn wetting current timer (refer to <u>Table 9</u>, page <u>18</u>).

- metallic command Set SPn to 16/32 mA or 2.0/4.0 mA gate drive current (refer to <u>Table 8</u>, page <u>17</u>).

- settings command Set SPn as switch-to-battery (refer to <u>Table 6</u>, page <u>16</u>).

- tri-state command Disable tri-state for SPn (refer to <u>Table 10</u>, page <u>18</u>).

After the *tri-state command* has been sent (tri-state disable), the MOSFET gate will be pulled to ground. From this point forward the MOSFET may be turned on and off by sending the *settings command*:

- settings command –SPn as switch-to-ground (MOSFET ON).

- settings command –SPn as switch-to-battery (MOSFET OFF).

Monitoring of the MOSFET drain in the OFF state provides open load detection. This is done by using an input comparator. With the SGn input in tri-state, the load will pull up the input to battery. With the load open, the SGn pin is pulled down to ground through an external resistor. The open load is indicated by a logic [1] in the SO data bit.

The analog command may be used to monitor the drain voltage in the MOSFET ON state. By sourcing 4.0 mA of

current to the 750  $\Omega$  resistor, the analog voltage on the SGn pin will be approximately:

$$V_{SGn} = I_{SGn} \times 750\Omega + V_{DS}$$

As the voltage on the drain of the MOSFET increases, so does the voltage on the SGn pin. With the SGn pin selected as analog, the MCU may perform the A/D conversion.