# LXT9883/9863

## Advanced 10/100 Unmanaged Repeater

## **Datasheet**

Order Number: 249115-003

August 2001

The LXT9883 is an advanced, 3.3V, 8-port 10/100 repeater. The LXT9883 is compatible with previous generations of Intel repeaters from the LXT980 and LXT918 families. Eight ports directly support 100BASE-TX/10BASE-T copper media. Two additional Media Independent Interface (MII) ports (10/100Mbps selectable) connect to Media Access Controllers (MACs) for bridge/switch applications. The LXT9863 offers the same features and functionality in a six-port device. This data sheet uses the singular designation "LXT98x3" to refer to both devices.

The LXT98x3 provides auto-negotiation with parallel detection for the PHY ports. The LXT98x3 provides two internal repeater state machines—one operating at 10 Mbps and one at 100 Mbps. Once configured, the LXT98x3 automatically connects each port to the appropriate repeater. The LXT98x3 also provides two Inter-Repeater Backplanes (IRBs) for expansion—one operating at 10 Mbps and one at 100 Mbps. Up to 240 twisted-pair and MII ports can logically be combined into one repeater.

## **Product Features**

- Six or eight 10/100 ports with integrated twisted-pair PHYs including integrated filters

- Two 10/100 MIIs for bridging.

- Independent segments for 10Mbps and 100 Mbps operation.

- Cascadable Inter-Repeater Backplanes (IRBs), with option for 5V stacking compatibility.

- Integrated LED drivers with user-selectable modes.

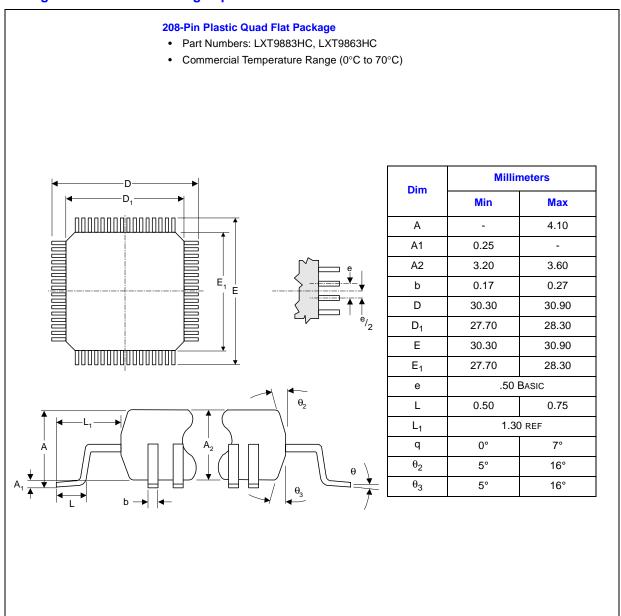

- Available in 208-pin QFP package.

- Operating temperature range: 0-70°C, ambient.

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The LXT9883/9863 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2001

\*Third-party brands and names are the property of their respective owners.

Datasheet

2

Document #: 249115 Revision #: 003 Rev. Date: 08/07/01

| 1.0 | ) Block Diagram |                                              |    |  |  |  |  |

|-----|-----------------|----------------------------------------------|----|--|--|--|--|

| 2.0 | Pin A           | Assignments and Signal Descriptions          | 8  |  |  |  |  |

| 3.0 | Fund            | ctional Description                          | 16 |  |  |  |  |

|     | 3.1             | Introduction                                 | 16 |  |  |  |  |

|     | 3.2             | Port Configuration                           |    |  |  |  |  |

|     | 0               | 3.2.1 Auto-Negotiation                       |    |  |  |  |  |

|     |                 | 3.2.2 Link Establishment and Port Connection |    |  |  |  |  |

|     | 3.3             | Interface Descriptions                       |    |  |  |  |  |

|     |                 | 3.3.1 Twisted-Pair Interface                 |    |  |  |  |  |

|     |                 | 3.3.2 Media Independent Interface            |    |  |  |  |  |

|     | 3.4             | Repeater Operation                           |    |  |  |  |  |

|     |                 | 3.4.1 100 Mbps Repeater Operation            | 19 |  |  |  |  |

|     |                 | 3.4.2 10 Mbps Repeater Operation             | 20 |  |  |  |  |

|     | 3.5             | Requirements                                 | 20 |  |  |  |  |

|     |                 | 3.5.1 Power                                  | 20 |  |  |  |  |

|     |                 | 3.5.2 Clock                                  |    |  |  |  |  |

|     |                 | 3.5.3 Bias Resistor                          |    |  |  |  |  |

|     |                 | 3.5.4 Reset                                  |    |  |  |  |  |

|     |                 | 3.5.5 IRB Bus Pull-ups                       |    |  |  |  |  |

|     | 3.6             | LED Operation                                |    |  |  |  |  |

|     |                 | 3.6.1 LEDs at Start-up                       |    |  |  |  |  |

|     |                 | 3.6.2 LED Event Stretching                   |    |  |  |  |  |

|     |                 | 3.6.3 Serial LED Interface                   |    |  |  |  |  |

|     |                 | 3.6.4 Serial Shifting                        |    |  |  |  |  |

|     |                 | 3.6.4.1 Serial LED Signals                   |    |  |  |  |  |

|     |                 | 3.6.4.2 Activity Graph LEDs                  |    |  |  |  |  |

|     |                 | 3.6.6 LED Modes                              |    |  |  |  |  |

|     |                 | 3.6.6.1 LED Mode 1                           |    |  |  |  |  |

|     |                 | 3.6.6.2 LED Mode 1                           |    |  |  |  |  |

|     |                 | 3.6.6.3 LED Mode 3                           |    |  |  |  |  |

|     |                 | 3.6.6.4 LED Mode 4                           |    |  |  |  |  |

|     | 3.7             | IRB Operation                                | 28 |  |  |  |  |

|     |                 | 3.7.1 RB Signal Types                        | 28 |  |  |  |  |

|     |                 | 3.7.2 10M-Only Operation                     | 29 |  |  |  |  |

|     |                 | 3.7.2.1 MAC IRB Access                       | 29 |  |  |  |  |

|     |                 | 3.7.3 LXT98x/91x/98xx Compatibility          | 29 |  |  |  |  |

|     | 3.8             | MII Port Operation                           | 31 |  |  |  |  |

|     |                 | 3.8.1 Preamble Handling                      | 31 |  |  |  |  |

| 4.0 | Appl            | lication Information                         | 32 |  |  |  |  |

|     | 4.1             | General Design Guidelines                    |    |  |  |  |  |

|     | 4.2             | Power and Ground                             |    |  |  |  |  |

|     |                 | 4.2.1 Supply Filtering                       |    |  |  |  |  |

|     |                 | 4.2.2 Ground Noise                           | 33 |  |  |  |  |

3

Document #: 249115 Revision #: 003 Rev. Date: 08/07/01

## **Contents**

|          | 4.2.3 Power and Ground Plane Layout Considerations |                                |                                               |    |  |  |  |  |

|----------|----------------------------------------------------|--------------------------------|-----------------------------------------------|----|--|--|--|--|

|          | 4.2.4                                              | Chassis                        | Ground                                        | 34 |  |  |  |  |

|          | 4.2.5                                              |                                | IAS Pin                                       |    |  |  |  |  |

|          | 4.2.6                                              |                                | ninations                                     |    |  |  |  |  |

|          | 4.2.7                                              |                                | -Pair Interface                               |    |  |  |  |  |

|          |                                                    | 4.2.7.1                        | Magnetics Information                         |    |  |  |  |  |

|          | 4.2.8                                              |                                |                                               |    |  |  |  |  |

|          | 4.2.9                                              |                                | cuits                                         |    |  |  |  |  |

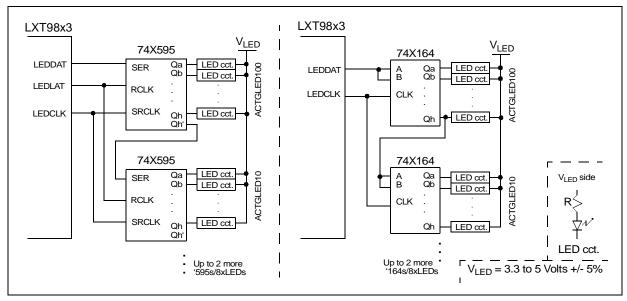

|          |                                                    | 4.2.9.1                        | Direct Drive LEDs                             |    |  |  |  |  |

|          |                                                    | 4.2.9.2                        | 3                                             |    |  |  |  |  |

|          | 4.3 Inter-F                                        | 4.2.9.3                        | Serial LEDs<br>Backplane Compatibility        |    |  |  |  |  |

|          | 4.3.1                                              |                                | ackplane—3.3V Only                            |    |  |  |  |  |

|          | 4.3.1                                              |                                | ackplane—3.3V or 5V                           |    |  |  |  |  |

|          | 4.5.2                                              | 4.3.2.1                        | ·                                             |    |  |  |  |  |

|          |                                                    | 4.3.2.2                        |                                               |    |  |  |  |  |

|          |                                                    | 4.3.2.3                        | 3.3V and 5.0V Stacking Boards Cannot Be Mixed |    |  |  |  |  |

| - ^      | T10                                                |                                | <u> </u>                                      |    |  |  |  |  |

| 5.0      | rest Specifi                                       | cations                        |                                               | 44 |  |  |  |  |

| 6.0      | Mechanical                                         | Specifica                      | tions                                         | 56 |  |  |  |  |

| 1 2      |                                                    |                                | amnents                                       |    |  |  |  |  |

| 3        |                                                    |                                | peater Architecture                           |    |  |  |  |  |

| 4        |                                                    |                                | Sealer Alchitecture                           |    |  |  |  |  |

| 5        |                                                    |                                | ling                                          |    |  |  |  |  |

| 6        |                                                    |                                | aling                                         |    |  |  |  |  |

| 7        |                                                    | _                              | n                                             |    |  |  |  |  |

| 8        |                                                    |                                |                                               |    |  |  |  |  |

| 9        |                                                    |                                | on                                            |    |  |  |  |  |

| 10       |                                                    |                                | onnections                                    |    |  |  |  |  |

| 11       | Typical Tw                                         | isted-Pair                     | Port Interface and Power Supply Filtering     | 38 |  |  |  |  |

| 12       |                                                    |                                |                                               |    |  |  |  |  |

| 13       |                                                    |                                | Drive & Multiplexed Configuration Inputs      |    |  |  |  |  |

| 14       |                                                    |                                |                                               |    |  |  |  |  |

| 15       |                                                    | •                              | nection between LXT98x and LXT98x3            |    |  |  |  |  |

| 16       |                                                    | •                              | 3 Implementation                              |    |  |  |  |  |

|          | 7 Typical 10 Mbps IRB Implementation               |                                |                                               |    |  |  |  |  |

| 18<br>19 | , , ,                                              |                                |                                               |    |  |  |  |  |

| 20       |                                                    |                                | All Timing                                    |    |  |  |  |  |

| 21       |                                                    |                                | Timing                                        |    |  |  |  |  |

| 22       |                                                    |                                | Port Timing                                   |    |  |  |  |  |

| 23       |                                                    |                                | Timing                                        |    |  |  |  |  |

| 24       |                                                    |                                | iming                                         |    |  |  |  |  |

| 25       |                                                    |                                | Port Timing                                   |    |  |  |  |  |

| 26       | •                                                  | LXT98x3 Package Specifications |                                               |    |  |  |  |  |

## **Contents**

# **Tables**

| 1  | MII #1 Signal Descriptions                        | 9  |

|----|---------------------------------------------------|----|

| 2  | MII #2 Signal Descriptions                        | 10 |

| 3  | Inter-Repeater Backplane Signal Descriptions      | 11 |

| 4  | Twisted-Pair Port Signal Descriptions             | 13 |

| 5  | LED Signal Descriptions                           | 14 |

| 6  | Power Supply and Indication Signal Descriptions   | 15 |

| 7  | Miscellaneous Signal Descriptions                 | 16 |

| 8  | Serial LED Port Bit Stream                        | 23 |

| 9  | ACTGLED Display Modes                             | 24 |

| 10 | LED Terms                                         | 24 |

| 11 | LED Mode 1 Indications                            | 25 |

| 12 | LED Mode 2 Indications                            | 26 |

| 13 | LED Mode 3 Indications                            | 27 |

| 14 | LED Mode 4 Indications                            |    |

| 15 | Cascading and Stacking Connections                |    |

| 16 | IRB Signal Details                                |    |

| 17 | LXT98x3 Magnetics Specifications                  |    |

| 18 | Oscillator Manufacturers                          |    |

| 19 | Absolute Maximum Ratings                          |    |

| 20 | Operating Conditions                              |    |

| 21 | Input System Clock1 Requirements                  |    |

| 22 | I/O Electrical Characteristics                    |    |

| 23 | 100 Mbps IRB Electrical Characteristics           |    |

| 24 | 10 Mbps IRB Electrical Characteristics            |    |

| 25 | 100BASE-TX Transceiver Electrical Characteristics |    |

| 26 | 10BASE-T Transceiver Electrical Characteristics   |    |

| 27 | 100 Mbps TP Port-to-Port Delay Timing Parameters  |    |

| 28 | 100BASE-TX MII-to-TP Port Timing Parameters       |    |

| 29 | 100BASE-TX TP-to-MII Timing Parameters            |    |

| 30 | 10BASE-T MII-to-TP Timing Parameters              |    |

| 31 | 10BASE-T TP-to-MII Port Timing Parameters         |    |

| 32 | 100 Mbps TP-to-IRB Timing Parameters1             |    |

| 33 | 10 Mbps TP-to-IRB Timing Parameters1              |    |

| 34 | 10 Mbps IRB-to TP Port Timing Parameters          | 55 |

# **Revision History**

| Date          | Revision | Page   | Description                                                                                                                                  |                                                                                                  |

|---------------|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| August 2001   | 003      | 44     | Modify the Absolute Maximum Ratings Supply Voltage value to 4.0V.                                                                            |                                                                                                  |

|               |          | 21, 37 | Modified clock requirements language.                                                                                                        |                                                                                                  |

|               |          | 21     | Replaced TBD value under reset to 3.15V.                                                                                                     |                                                                                                  |

|               | 002      | 33     | Replaced TBDs in fourth para under Supply Filtering to 1000 mA and 1500 mA.                                                                  |                                                                                                  |

|               |          |        | 36                                                                                                                                           | Replaced TBDs in fourth bullet under Twisted-Pair Interface to 1000 mA and 1500 mA.              |

|               |          | 37     | Modified Oscillator Manufacturers table                                                                                                      |                                                                                                  |

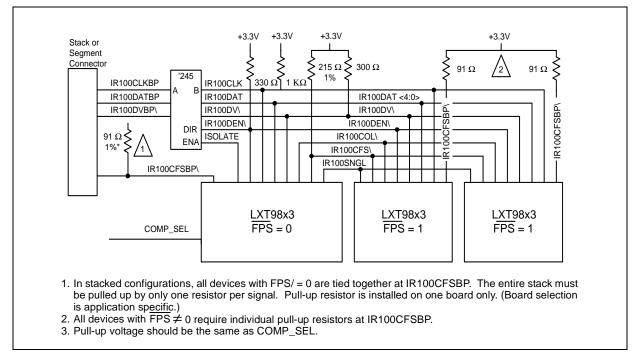

| February 2001 |          | 002    | 43                                                                                                                                           | Typical 100 Mbps IRB Implementation table: Modified note 2 (replaced "FPS/ = 0" with "FPS/ ≠ 0." |

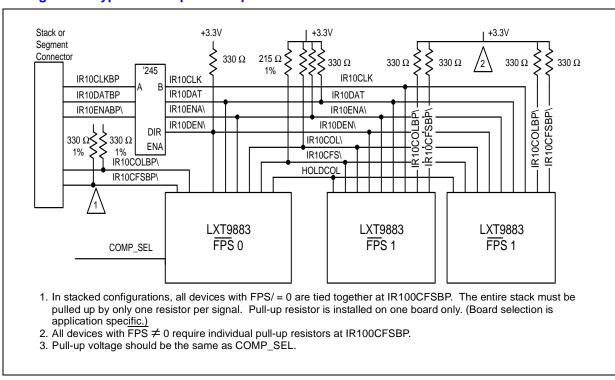

|               |          | 43     | Typical 10 Mbps IRB Implementation table: Modified note 2 (replaced "FPS/ = 0" with "FPS/ ≠ 0."                                              |                                                                                                  |

|               |          | 44     | Absolute Maximum Ratings table: Replaced TBD for Supply Voltage under Max to 3.45. Deleted Operating Temperature lines and values.           |                                                                                                  |

|               |          | 44     | Operating Conditions table: For Power Consumption: removed Auto-Negotiation values. Changed description and values for 8- and 6-port active. |                                                                                                  |

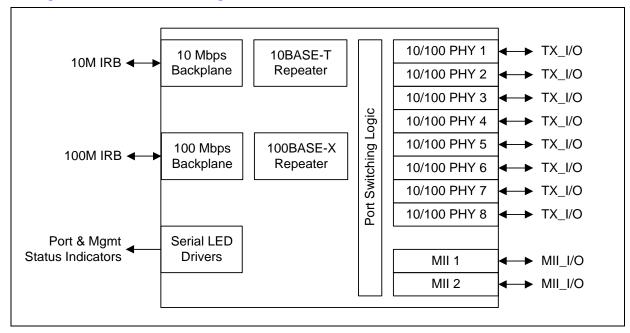

# 1.0 Block Diagram

Figure 1. LXT98x3 Block Diagram

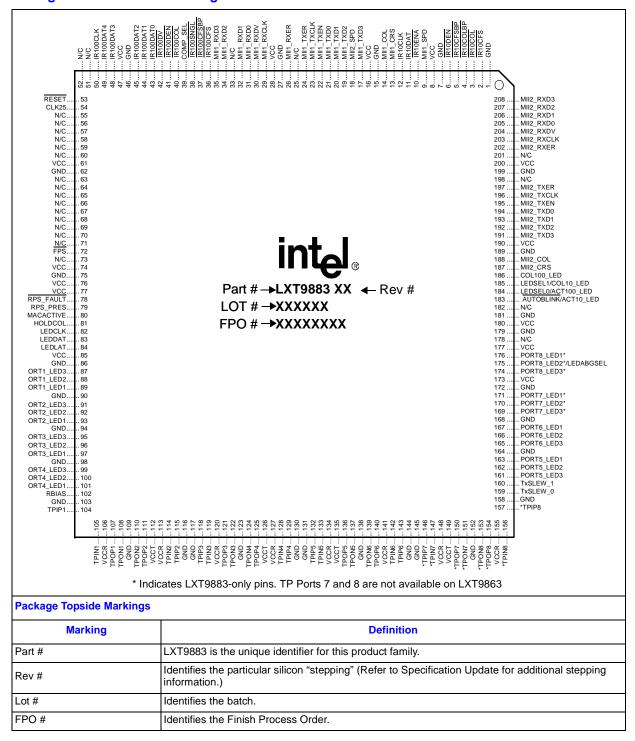

## 2.0 Pin Assignments and Signal Descriptions

Figure 2. LXT9883 Pin Assignments

Table 1. MII #1 Signal Descriptions

| Pin                  | Symbol                                           | Type <sup>1, 2</sup> | Description                                                                                                                                                                                                            |

|----------------------|--------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                    | MII1_SPD                                         | I<br>PU              | Speed Select - MII 1. This signal is sensed at power up, hardware reset, and software reset. Selects operating speed of the respective MII (MAC) interface. High = 100 Mbps. Low = 10 Mbps.                            |

| 31<br>32<br>34<br>35 | MII1_RXD0<br>MII1_RXD1<br>MII1_RXD2<br>MII1_RXD3 | 0                    | Receive Data - MII 1. The LXT98x3 transmits received data to the controller on these outputs. Data is driven on the falling edge of MII1_RXCLK.                                                                        |

| 30                   | MII1_RXDV                                        | 0                    | Receive Data Valid - MII 1. Active High signal, synchronous to MII1_RXCLK, indicates valid data on MII1_RXD<3:0>.                                                                                                      |

| 29                   | MII1_RXCLK                                       | 0                    | Receive Clock - MII 1. MII receive clock for expansion port. This is a 2.5 or 25 MHz clock derived from the CLK25 input (refer to Table 7 on page 16).                                                                 |

| 26                   | MII1_RXER                                        | 0                    | Receive Error - MII 1. Active High signal, synchronous to MII1_RXCLK, indicates invalid data on MII1_RXD<3:0>.                                                                                                         |

| 24                   | MII1_TXER                                        | I                    | <b>Transmit Error - MII 1.</b> MII1_TXER is a 100M-only signal. The MAC asserts this input when an error has occurred in the transmit data stream. The LXT98x3 responds by sending 'Invalid Code Symbols' on the line. |

| 23                   | MII1_TXCLK                                       | 0                    | <b>Transmit Clock - MII 1.</b> This is a 2.5 or 25 MHz clock derived from the CLK25 input (refer to Table 7 on page 16).                                                                                               |

| 22                   | MII1_TXEN                                        | I                    | <b>Transmit Enable - MII 1.</b> External controllers drive this input High to indicate data is transmitted on the MII1_TXD<3:0> pins. Ground this input if unused.                                                     |

| 21<br>20<br>19<br>17 | MII1_TXD0<br>MII1_TXD1<br>MII1_TXD2<br>MII1_TXD3 | I                    | Transmit Data - MII 1. External controllers use these inputs to transmit data to the LXT98x3. The LXT98x3 samples MII1_TXD<3:0> on the rising edge of MII1_TXCLK, when MII1_TXEN is High.                              |

| 14                   | MII1_COL                                         | 0                    | Collision - MII 1. The LXT98x3 drives this signal High to indicate a collision occurred.                                                                                                                               |

| 13                   | MII1_CRS                                         | 0                    | Carrier Sense - MII 1. Active High signal indicates LXT98x3 is transmitting or receiving.                                                                                                                              |

$<sup>1. \</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, A = Analog, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Input/Output, OD$

OS = Open Source, PD = Pull Down, PU = Pull Up.

NC = No Clamp. Pad does not clamp input in the absence of power.

2. Pins are 5V tolerant, unless indicated.

Table 2. MII #2 Signal Descriptions

| Pin                      | Symbol                                           | Type <sup>1, 2</sup> | Description                                                                                                                                                                                      |

|--------------------------|--------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18                       | MII2_SPD                                         | I<br>PU              | Speed Select - MII 2. This signal is sensed at power up, hardware reset, and software reset. Selects operating speed of the respective MII (MAC) interface. High = 100 Mbps. Low = 10 Mbps.      |

| 205<br>206<br>207<br>208 | MII2_RXD0<br>MII2_RXD1<br>MII2_RXD2<br>MII2_RXD3 | 0                    | Receive Data - MII 2. The LXT98x3 transmits received data to the controller on these outputs. Data is driven on the falling edge of MII2_RXCLK.                                                  |

| 204                      | MII2_RXDV                                        | 0                    | Receive Data Valid - MII 2. Active High signal, synchronous to MII2_RXCLK, indicates valid data on MII2_RXD<3:0>.                                                                                |

| 203                      | MII2_RXCLK                                       | 0                    | Receive Clock - MII 2. MII receive clock for expansion port. This is a 2.5 or 25 MHz clock derived from the CLK25 input (refer to Table 7 on page 16).                                           |

| 202                      | MII2_RXER                                        | 0                    | Receive Error - MII 2. Active High signal, synchronous to MII2_RXCLK, indicates invalid data on MII2_RXD<3:0>.                                                                                   |

| 197                      | MII2_TXER                                        | I                    | <b>Transmit Error - MII 2.</b> MII2_TXER is a 100M-only signal. The MAC asserts this input when errors occurs in the transmit data stream. The LXT98x3 sends 'Invalid Code Symbols' on the line. |

| 196                      | MII2_TXCLK                                       | 0                    | <b>Transmit Clock - MII 2.</b> This is a 2.5 or 25 MHz clock derived from the CLK25 input (refer to Table 7 on page 16).                                                                         |

| 195                      | MII2_TXEN                                        | I                    | <b>Transmit Enable - MII 2.</b> External controllers drive this input High to indicate data is transmitted on the MII2_TXD<3:0> pins. Ground this input if unused.                               |

| 194<br>193<br>192<br>191 | MII2_TXD0<br>MII2_TXD1<br>MII2_TXD2<br>MII2_TXD3 | I                    | <b>Transmit Data - MII 2.</b> External controllers use these inputs to transmit data to the LXT98x3. The LXT98x3 samples MII2_TXD<3:0> on the rising edge of MII2_TXCLK, when MII2_TXEN is High. |

| 188                      | MII2_COL                                         | 0                    | Collision - MII 2. The LXT98x3 drives this signal High to indicate a collision occurred.                                                                                                         |

| 187                      | MII2_CRS                                         | 0                    | Carrier Sense - MII 2. Active High signal indicates LXT98x3 is transmitting or receiving.                                                                                                        |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, A = Analog, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Drain,

OS = Open Source, PD = Pull Down, PU = Pull Up.

NC = No Clamp. Pad does not clamp input in the absence of power.

2. Pins are 5V tolerant, unless indicated.

Table 3. Inter-Repeater Backplane Signal Descriptions

| Pin                        | Symbol                                                        | Type <sup>1, 2</sup>              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|----------------------------|---------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                            | Common IRB Signals                                            |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 39                         | COMP_SEL                                                      | AI                                | Compatibility Mode Select. 3.3V on this pin causes the IRCFSBP signals to operate in 3.3V only mode. 5V on this pin causes the IR100CFSBP or IR10CFSBP signals to operate in 5V backwards compatibility mode with LXT98x devices.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                            |                                                               |                                   | 100 Mbps IRB Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 36                         | ĪR100CFS <sup>3</sup>                                         | A I/O<br>OD                       | 100 Mbps IRB Collision Force Sense. A three-level signal that determines number of active ports on the "logical" repeater. High level (3.3V) indicates no ports active; Mid level (approx. 1.6V) indicates one port active; Low level (0V) indicates more than one port active, resulting in a collision. This signal requires a 215 $\Omega$ pull-up resistor, and connects between ICs on the same board.                                                                                                                                 |  |  |  |  |  |

| 37                         | ĪR100CFSBP                                                    | A I/O<br>OD                       | 100 Mbps IRB Collision Force Sense - Backplane. This three-level signal functions the same as $\overline{\text{IR100CFS}}$ ; however, it connects between ICs with $\overline{\text{FPS}}$ = 0, on different boards. $\overline{\text{IR100CFSBP}}$ requires a single 91 $\Omega$ pull-up resistor in each stack. This signal can be set in either 5V or 3.3V modes by the COMP_SEL pin.                                                                                                                                                    |  |  |  |  |  |

| 38                         | ĪR100SNGL                                                     | I/O<br>Schmitt PU                 | 100 Mbps Single Driver State. This active Low signal is asserted by the device with FPS = 0 when a packet is received from one or more ports. Do not connect this signal between boards.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 40                         | ĪR100COL                                                      | I/O<br>Schmitt PU                 | 100 Mbps Multiple Driver State. This active Low signal is asserted by the device with FPS = 0 when a packet is being received from more than one port (collision). Do not connect this signal between boards.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 41                         | IR100DEN                                                      | O<br>OD                           | 100 Mbps IRB Driver Enable. This output provides directional control for an external bidirectional transceiver (74LVT245) used to buffer the 100 Mbps IRB in multi-board applications. It must be pulled up by a 330Ω resistor. When there are multiple devices on one board, tie all IR100DEN outputs together. If IR100DEN is tied directly to the DIR pin on a 74LVT245, attach the on-board IR100DAT, IR100CLK, and IR100DV signals to the "B" side of the 74LVT245, and connect the off-board signals to the "A" side of the 74LVT245. |  |  |  |  |  |

| 42                         | ĪR100DV                                                       | I/O<br>Schmitt<br>OD<br>PU        | 100 Mbps IRB Data Valid. This active Low signal indicates port activity on the repeater. IR100DV frames the clock and data of the packet on the backplane. This signal requires a $300\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 43<br>44<br>45<br>48<br>49 | IR100DAT0<br>IR100DAT1<br>IR100DAT2<br>IR100DAT3<br>IR100DAT4 | I/O<br>Tri-state<br>Schmitt<br>PU | 100 Mbps IRB Data. These bidirectional signals carry 5-bit data on the 100 Mbps IRB. Data is driven on the falling edge and sampled on the rising edge of IR100CLK. Buffer these signals between boards.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 50                         | IR100CLK                                                      | I/O<br>Tri-state<br>Schmitt<br>PD | 100 Mbps IRB Clock. This bidirectional, non-continuous, 25 MHz clock is recovered from received network traffic. Schmitt triggering is used to increase noise immunity. This signal must be pulled to VCC when idle. One 1 k $\Omega$ pull-up resistor on both sides of a 74LVT245 buffer is recommended.                                                                                                                                                                                                                                   |  |  |  |  |  |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Drain, OS = Open Source, PD = Pull Down, PU = Pull Up. Even if the IRB is not used, required pull-up resistors must be installed as listed above.

NC = No Clamp. Pad does not clamp input in the absence of power.

Pins are 5V tolerant, unless indicated.

IR100CFS is not 5V tolerant.

<sup>4.</sup> IR10CFS is **not** 5V tolerant.

Table 3. Inter-Repeater Backplane Signal Descriptions (Continued)

| Pin | Symbol               | Type <sup>1, 2</sup>              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----|----------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     | 10 Mbps IRB Signals  |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 11  | IR10DAT              | I/O<br>OD<br>PD                   | 10 Mbps IRB Data. This bidirectional signal carries data on the 10 Mbps IRB. Data is driven and sampled on the rising edge of the corresponding IRCLK. This signal must be pulled High by a $330\Omega$ resistor. Buffer this signal between boards.                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 12  | IR10CLK              | I/O<br>Tri-state<br>Schmitt<br>PD | 10 Mbps IRB Clock. This bidirectional, non-continuous, 10 MHz clock is recovered from received network traffic. During idle periods, the output is high-impedance. Schmitt triggering is used to increase noise immunity.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 6   | ĪR10DEN              | O<br>OD                           | 10 Mbps IRB Driver Enable. This output provides directional control for an external bidirectional transceiver (74LVT245) used to buffer the IRBs in multi-board applications. It must be pulled up by a 330 $\Omega$ resistor. When there are multiple devices on one board, tie all IR10DEN outputs together. If IR10DEN is tied directly to the DIR pin on a 74LVT245, attach the on-board IR10DAT, IR10CLK and IR10ENA signals to the "B" side of the 74LVT245, and connect the off-board signals to the "A" side of the 74LVT245. |  |  |  |  |

| 10  | ĪR10ENA              | I/O<br>OD<br>PU                   | 10 Mbps IRB Enable. This active Low output indicates carrier presence on the IRB. A $330\Omega$ pull-up resistor is required to pull the IR10ENA output High when the IRB is idle. When there are multiple devices, tie all IR10ENA outputs together. Buffer these signals between boards.                                                                                                                                                                                                                                            |  |  |  |  |

| 3   | ĪR10COL              | I/O<br>OD<br>PU                   | 10 Mbps IRB Collision. This output is driven Low to indicate a collision occurred on the 10 Mbps segment. A $330\Omega$ resistor is required on each board to pull this signal High when there is no collision. Do not connect between boards and do not buffer.                                                                                                                                                                                                                                                                      |  |  |  |  |

| 4   | ĪR10COLBP            | I/O<br>OD                         | 10 Mbps IRB Collision - Backplane. This active Low output has the same function as IR10COL, but is used between boards. Attach this signal only from the device with FPS = 0 to the backplane or connector, <i>without buffering</i> . The output must be pulled up by one $330\Omega$ resistor per stack.                                                                                                                                                                                                                            |  |  |  |  |

| 2   | ĪR10CFS <sup>4</sup> | A, I/O<br>OD                      | <b>10 Mbps IRB Collision Force Sense.</b> This three-state analog signal indicates transmit collision when driven Low. IR10CFS requires a 215Ω, 1% pull-up resistor. Do not connect this signal between boards and do not buffer.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 5   | IR10CFSBP            | A I/O<br>OD                       | Note: 10 Mbps IRB Collision Force Sense - Backplane. Functions the same as IR10CFS, but connects between boards. Attach this signal only from the device with FPS = 0 to the backplane or connector, without buffering. This signal requires one 330Ω, 1% pull-up resistor per stack. This signal can be set for 5V or 3.3V modes by the COMP_SEL pin.                                                                                                                                                                                |  |  |  |  |

| 80  | MACACTIVE            | I<br>PD                           | Note: MAC Active. Active High input allows external ASICs to participate in 10 Mbps IRB. Driving data onto the IRB requires the external ASIC assert MACACTIVE High for one clock cycle, then assert IR10ENA Low. ASIC monitors IR10COL (active Low) for collision. By using MACACTIVE, the repeater—not the MAC—drives the three-level IR10CFS pin.                                                                                                                                                                                  |  |  |  |  |

| 81  | HOLDCOL              | I/O<br>PD                         | Note: Hold Collision for 10 Mbps mode. This active High signal is driven by the device with FPS = 0 to extend a non-local transmit collision to other devices on the same board. Do not attach the HOLDCOL signals from different boards together.                                                                                                                                                                                                                                                                                    |  |  |  |  |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Drain, OS = Open Source, PD = Pull Down, PU = Pull Up. Even if the IRB is not used, required pull-up resistors must be installed as listed above.

NC = No Clamp. Pad does not clamp input in the absence of power.

<sup>2.</sup> Pins are 5V tolerant, unless indicated.

<sup>3.</sup> IR100CFS is **not** 5V tolerant. 4. IR10CFS is **not** 5V tolerant.

Table 4. Twisted-Pair Port Signal Descriptions

| Pin        | Symbol            | Type <sup>1</sup> | Description                                                                                                                                                                                                           |                                                                                                                                                                    |                                |                                              |  |

|------------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------|--|

| 107, 108   | TPOP1, TPON1      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 111, 110   | TPOP2, TPON2      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 121, 122   | TPOP3, TPON3      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 125, 124   | TPOP4, TPON4      | Caution: AO       |                                                                                                                                                                                                                       | <b>Twisted-Pair Outputs - Ports 1 through 8.</b> These pins are the positive and negative outputs from the respective ports' twisted-pair line drivers. For unused |                                |                                              |  |

| 136, 137   | TPOP5, TPON5      | Caution. AO       |                                                                                                                                                                                                                       | can be left open.                                                                                                                                                  |                                |                                              |  |

| 140, 139   | TPOP6, TPON6      |                   | , , ,                                                                                                                                                                                                                 | ·                                                                                                                                                                  |                                |                                              |  |

| 150, 151   | TPOP7, TPON7      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 154, 153   | TPOP8, TPON8      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 104, 105   | TPIP1, TPIN1      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 115, 114   | TPIP2, TPIN2      | Caution: Al       | <b>Twisted-Pair Inputs - Ports 1 through 8.</b> These pins are the positive and negative inputs to the respective ports' twisted-pair receivers. For unused ports, tie together with $100\Omega$ resistors and float. |                                                                                                                                                                    |                                |                                              |  |

| 118, 119   | TPIP3, TPIN3      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 129, 128   | TPIP4, TPIN4      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 132, 133   | TPIP5, TPIN5      | Caution. Al       |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 143, 142   | TPIP6, TPIN6      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 146, 147   | TPIP7, TPIN7      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

| 157, 156   | TPIP8, TPIN8      |                   |                                                                                                                                                                                                                       |                                                                                                                                                                    |                                |                                              |  |

|            |                   |                   |                                                                                                                                                                                                                       | Tx Output Slew<br>(rise and fall time                                                                                                                              |                                | 1. These pins select the TX output slew rate |  |

|            |                   |                   | TxSLEW_1                                                                                                                                                                                                              | TxSLEW_0                                                                                                                                                           | Slew Rate (Rise and Fall Time) |                                              |  |

| 160<br>159 | TxSLEW_1 TxSLEW 0 | PD                | 0                                                                                                                                                                                                                     | 0                                                                                                                                                                  | 2.5 ns                         |                                              |  |

| 159        | IXOLEVV_U         |                   | 0                                                                                                                                                                                                                     | 1                                                                                                                                                                  | 3.1 ns                         |                                              |  |

|            |                   |                   | 1                                                                                                                                                                                                                     | 0                                                                                                                                                                  | 3.7 ns                         |                                              |  |

|            |                   |                   |                                                                                                                                                                                                                       | 1                                                                                                                                                                  | 1                              | 4.3 ns                                       |  |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, A = Analog, AI = Analog Input, AO = Analog Output, A I/O = Analog Input/Output,

OD = Open Drain,

OS = Open Source, PD = Pull Down, PU = Pull Up.

NC = No Clamp. Pad does not clamp input in the absence of power.

**Table 5. LED Signal Descriptions**

| Pin                                               | Symbol                                                                                                       | Type <sup>1, 2</sup>        | Description                                                                                                                                                                                                 |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 184<br>185                                        | LEDSEL0<br>LEDSEL1                                                                                           | l <sup>3</sup><br>O - OD/OS | LED Mode Select - Input. See Note 3 in footer below.  00 = Mode 1, 01 = Mode 2, 10 = Mode 3, 11 = Mode 4  These pins are shared with the LEDACT100, LEDCOL10 outputs.                                       |

| 175                                               | LEDABGSEL                                                                                                    | I <sup>3</sup><br>O - OD/OS | LED Activity Bar Graph Mode Select - Input. See Note 2 in footer below.  0 = Base-10 Mode, 1 = Base-2 Mode  Refer to "Activity Graph LEDs" on page 23.  This pin is shared with the Port8_LED2 output.      |

| 183                                               | AUTOBLINK                                                                                                    | I <sup>3</sup><br>O - OD/OS | LED Blink Mode Select - Input. See Note 3 in footer below.  0 = Auto blink on, 1 = Auto blink off This pin is shared with the LEDACT100, LEDCOL10 outputs.                                                  |

| 83                                                | LEDDAT                                                                                                       | 0                           | <b>LED Data</b> . Serial data stream that is shifted into external Serial-to-Parallel LED drivers. See "Serial LED Interface" on page 22                                                                    |

| 84                                                | LEDLAT                                                                                                       | 0                           | <b>LED Latch</b> . Parallel load clock for external Serial-to-Parallel LED drivers. See "Serial LED Interface" on page 22                                                                                   |

| 82                                                | LEDCLK                                                                                                       | 0                           | LED Clock. Serial data stream clock for external Serial-to-Parallel LED drivers. See "Serial LED Interface" on page 22                                                                                      |

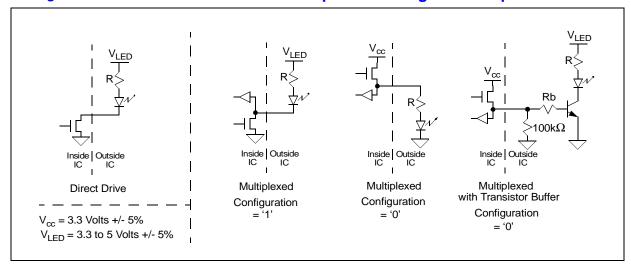

| 176<br>171<br>167<br>163<br>101<br>97<br>93<br>89 | PORT8_LED1 PORT7_LED1 PORT6_LED1 PORT5_LED1 PORT4_LED1 PORT3_LED1 PORT2_LED1 PORT1_LED1                      | O<br>OD                     | <b>LED Driver 1 - Ports 1 through 8.</b> Programmable LED driver. Active Low. See "Direct Drive LEDs" on page 24  Port8_LED1 must be pulled High via a 100–500 k $\Omega$ resistor if LED circuit not used. |

| 175<br>170<br>166<br>162<br>100<br>96<br>92<br>88 | PORT8_LED2<br>PORT7_LED2<br>PORT6_LED2<br>PORT5_LED2<br>PORT4_LED2<br>PORT3_LED2<br>PORT2_LED2<br>PORT1_LED2 | O<br>OD                     | LED Driver 2 - Ports 1 through 8. Programmable LED driver. Active Low. See "Direct Drive LEDs" on page 24 The Port8_LED2 pin is shared with the LEDABGSEL configuration input.                              |

| 174<br>169<br>165<br>161<br>99<br>95<br>91        | PORT8_LED3<br>PORT7_LED3<br>PORT6_LED3<br>PORT5_LED3<br>PORT4_LED3<br>PORT3_LED3<br>PORT2_LED3<br>PORT1_LED3 | O<br>OD                     | <b>LED Driver 3 - Ports 1 through 8</b> . Programmable LED driver. Active Low. See "Direct Drive LEDs" on page 24  Port8_LED3 must be pulled High via a 100–500 kΩ resistor if LED circuit not used.        |

| 185                                               | COL10_LED                                                                                                    | I<br>O - OD/OS              | 10M Collision LED Driver. Active output indicates collision on 10M segment. This pin is shared with the LEDSEL1 configuration input.                                                                        |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, A = Analog, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Drain,

OS = Open Source, PD = Pull Down, PU = Pull Up. Even if the IRB is not used, required pull-up resistors must be installed as listed above.

NC = No Clamp. Pad does not clamp input in the absence of power.

<sup>2.</sup> Pins are 5V tolerant, unless indicated.

<sup>3.</sup> Input must be static; Refer to "LED Pins Multiplexed with Configuration Inputs" on page 39. for information on pin use.

Table 5. LED Signal Descriptions (Continued)

| Pin | Symbol     | Type <sup>1, 2</sup> | Description                                                                                                                                                          |

|-----|------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 186 | COL100_LED | I<br>O - OD/OS       | <b>100M Collision LED Driver</b> . Active output indicates collision on 100M segment.                                                                                |

| 183 | ACT10_LED  | I<br>O - OD/OS       | <b>10M Activity LED Driver</b> . Active output indicates activity on 10M segment. This pin is shared with the AUTOBLINK configuration input (refer to Note 3 below). |

| 184 | ACT100_LED | I<br>O - OD/OS       | 100M Activity LED Driver. Active output indicates activity on 100M segment. This pin is shared with the LEDSEL0 configuration input (refer to Note 3 below).         |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, A = Analog, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Drain,

**Table 6. Power Supply and Indication Signal Descriptions**

| Pin                                                                                                                                                                         | Symbol | Type <sup>1, 2</sup> | Description                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8, 16, 28,<br>47, 61, 74,<br>76, 77, 85,<br>173, 177,<br>180, 190,<br>200                                                                                                   | vcc    | -                    | Power Supply Inputs. Each of these pins must be connected to a common +3.3 VDC power supply. A de-coupling capacitor to digital ground should be supplied for every one of these pins.                                                           |

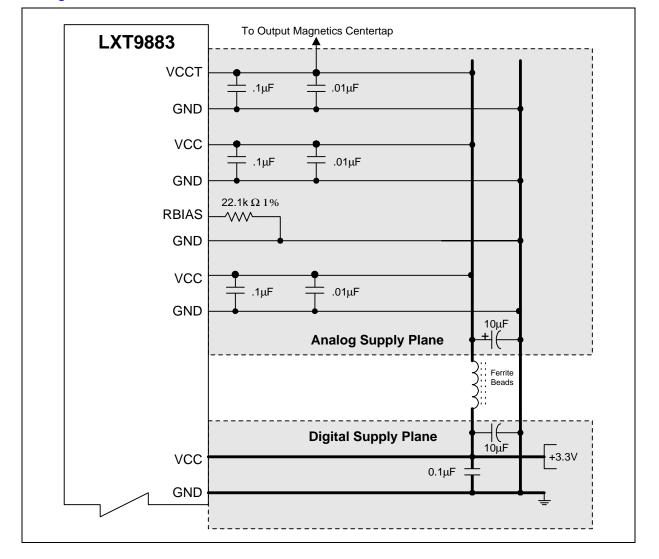

| 106, 113,<br>120, 127,<br>134, 141,<br>148, 155                                                                                                                             | VCCR   | -                    | Analog Supply Inputs - Receive. Each of these pins must be connected to a common +3.3 VDC power supply. A de-coupling capacitor to GND should be supplied for every one of these pins. Use ferrite beads to create a separate analog VCC plane.  |

| 112, 126,<br>135, 149                                                                                                                                                       | VCCT   | -                    | Analog Supply Inputs - Transmit. Each of these pins must be connected to a common +3.3 VDC power supply. A de-coupling capacitor to GND should be supplied for every one of these pins. Use ferrite beads to create a separate analog VCC plane. |

| 1, 7, 15, 27,<br>46, 62, 75,<br>86, 90, 94,<br>98, 103,<br>109, 116,<br>117, 123,<br>130, 131,<br>138, 144,<br>145, 152,<br>158, 164,<br>168, 172,<br>179, 181,<br>189, 199 | GND    | -                    | <b>Ground.</b> Connect each of these pins to system ground plane.                                                                                                                                                                                |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, A = Analog, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Drain

OS = Open Source, PD = Pull Down, PU = Pull Up. Even if the IRB is not used, required pull-up resistors must be installed as listed above.

NC = No Clamp. Pad does not clamp input in the absence of power.

<sup>2.</sup> Pins are 5V tolerant, unless indicated.

<sup>3.</sup> Input must be static; Refer to "LED Pins Multiplexed with Configuration Inputs" on page 39. for information on pin use.

OS = Open Source, PD = Pull Down, PU = Pull Up.

NC = No Clamp. Pad does not clamp input in the absence of power.

<sup>2.</sup> Pins are 5V tolerant, unless indicated.

Table 6. Power Supply and Indication Signal Descriptions (Continued)

| Pin | Symbol    | Type <sup>1, 2</sup> | Description                                                                                                                                                                                     |

|-----|-----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 102 | RBIAS     | А                    | <b>RBIAS.</b> Used to provide bias current for internal circuitry. The 100 $\mu$ A bias current is provided through an external 22.1 k $\Omega$ , 1% resistor to GND.                           |

| 79  | RPS_PRES  | I<br>PD              | Redundant Power Supply Present. Active High input indicates presence of redundant power supply. Tie Low if not used.                                                                            |

| 78  | RPS_FAULT | I<br>PU              | Redundant Power Supply Fault. Active Low input indicates redundant power supply fault. The state of this input is reflected in the RPS_LED output (refer to LED section). Tie High if not used. |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, A = Analog, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Drain,

**Table 7. Miscellaneous Signal Descriptions**

| Pin                                                           | Symbol | Type <sup>1, 2</sup> | Description                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------------------------------------------|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

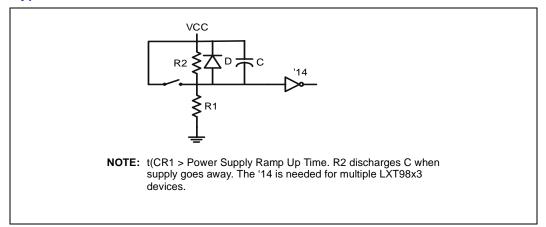

| 53                                                            | RESET  | I<br>Schmitt         | Reset. This active Low input causes internal circuits, state machines and counters to reset (address tracking registers do not reset). On power-up, devices should not be brought out of reset until the power supply stabilizes 3.3V. When there are multiple devices, it is recommended all be supplied to a common reset driven by an 'LS14 or similar device. |  |

| 54                                                            | CLK25  | I<br>Schmitt         | 25 MHz system clock. Refer to Table 21 on page 44.                                                                                                                                                                                                                                                                                                                |  |

| 72                                                            | FPS    | l<br>TTL             | First Position Select. In multi-chip configurations, this pin identifies one device on each board that drives the HOLDCOL signal to extend non-local collisions to other devices on the board. Set Low for first device on the PCB. Set High for all other devices on the PCB.                                                                                    |  |

| 25, 33, 51, 52,<br>55-60, 63-71,<br>73, 178, 182,<br>198, 201 | N/C    | -                    | No Connects. Leave these pins unconnected.                                                                                                                                                                                                                                                                                                                        |  |

<sup>1.</sup> I = Input, O = Output, I/O = Input/Output, D = Digital, A = Analog, AI = Analog Input, A I/O = Analog Input/Output, OD = Open Drain,

## 3.0 Functional Description

## 3.1 Introduction

As a fully integrated IEEE 802.3 compliant repeater capable of 10 Mbps and 100 Mbps operation, the LXT98x3 is a versatile device allowing great flexibility in Ethernet design solutions. Figure 3 shows a typical application. Refer to "Application Information" on page 32. for specific circuit implementations.

OS = Open Source, PD = Pull Down, PU = Pull Up.

NC = No Clamp. Pad does not clamp input in the absence of power.

<sup>2.</sup> Pins are 5V tolerant, unless indicated.

OS = Open Source, PD = Pull Down, PU = Pull Up.

NC = No Clamp. Pad does not clamp input in the absence of power.

<sup>2.</sup> Pins are 5V tolerant, unless indicated.

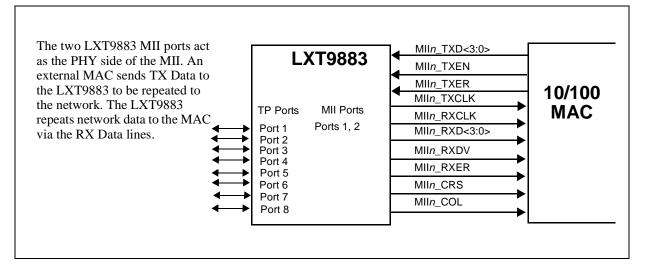

This multi-port repeater provides six (LXT9863) or eight (LXT9883) 10BASE-T/100BASE-TX ports. In addition, each device also provides two Media Independent Interface (MII) expansion ports that may be connected to 10/100 MACs.

The LXT98x3 provides two repeater state machines and two Inter-Repeater Backplanes (IRB) on a single chip—one for 10 Mbps and one for 100 Mbps operation. The 100 Mbps repeater meets IEEE 802.3 Class II requirements. The auto-negotiation capability of the LXT98x3 allows it to communicate with connected nodes and configure itself accordingly.

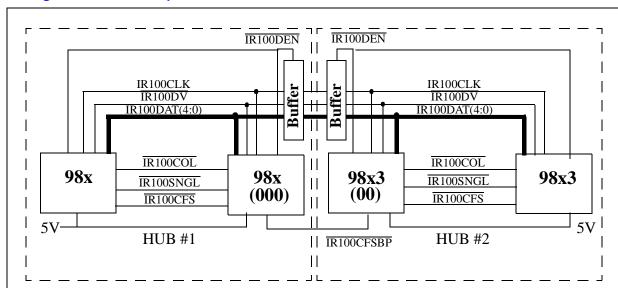

The segmented backplane simplifies dual-speed operation, and allows multiple devices to be stacked and function as one logical Class II repeater. Up to 240 ports (192 TP ports and 48 MII ports) can be supported in a single stack.

LXT9883 IC Backplan **LXT9883 IC** Buffer **LXT9883 IC** 10M Backplane 10/100 10 Mbps 10BASE-T PHY Backplane Repeater 10 Backplane 10/100 PHY Buffer 100BASE-X 100 Mbps 100M Backplane 10/100 Repeater Backplane PHY 10/100 PHY 10/100 PHY 10/100 MII to MII Bridge PHY MII 10/100 MII Dr PHY 10/100 LED PHY **Drivers**

Figure 3. Typical LXT9883 Repeater Architecture

## 3.2 Port Configuration

The LXT98x3 powers up in auto-negotiation mode for all twisted-pair ports.

## 3.2.1 Auto-Negotiation

All TP ports on power-up are configured to establish link via auto-negotiation. The port and link partner establish link conditions by exchanging Fast Link Pulse (FLP) bursts. Each FLP burst contains 16 bits of data advertising the port's capabilities. If the link partner does not support autonegotiation, the LXT98x3 determines link state by listening for 100 Mbps IDLE symbols or 10 Mbps link pulses. If it detects either of these signals, it configures the port accordingly.

### 3.2.2 Link Establishment and Port Connection

Once a port establishes link, the LXT98x3 automatically connects it to the appropriate repeater state machine. If link loss is detected and auto-negotiation is enabled, the port returns to the autonegotiation state.

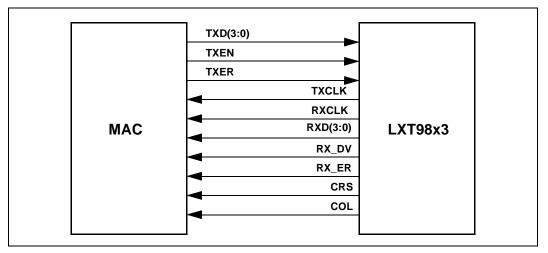

## 3.3 Interface Descriptions

The LXT9883 and LXT9863 provide eight and six network interface ports, respectively. Each port is a twisted-pair interface that directly supports 100BASE-TX (100TX) and 10BASE-T (10T) Ethernet applications and fully complies with IEEE 802.3 standards. A common termination circuit is used.

#### 3.3.1 Twisted-Pair Interface

The LXT98x3 pinout is optimized for dual-height RJ-45 connectors. The twisted-pair interface for each port consists of two differential signal pairs — one for transmit and one for receive. The transmit signal pair is TPOP/TPON, the receive signal pair is TPIP/TPIN.

The transmitter requires magnetics with 1:1 turns ratio. The center tap of the primary side of the transmit winding must be tied to a quiet VCC for proper operation.

The receiver requires magnetics with a 1:1 turns ratio, and a load of 100  $\Omega$ . When the twisted-pair port is enabled, the receiver actively biases its inputs to approximately 2.8V. A 4 k $\Omega$  load is always present across the TPIP/TPIN pair.

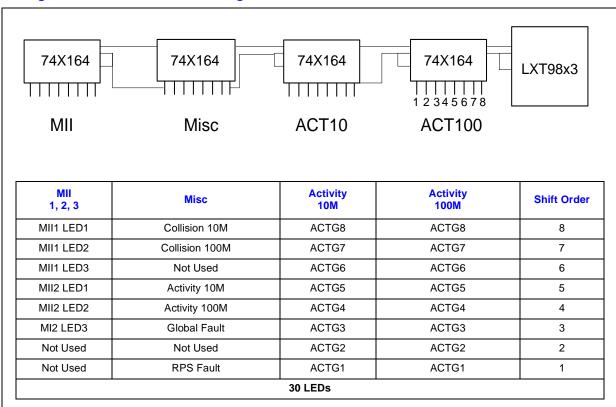

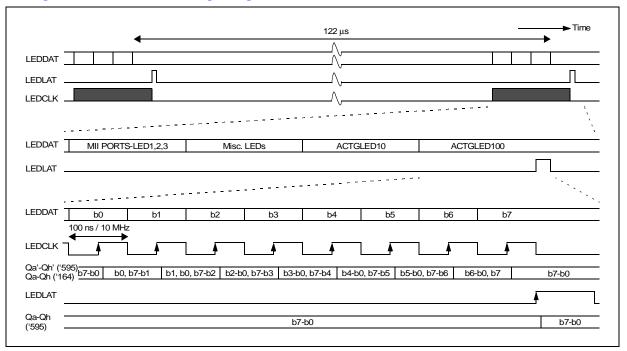

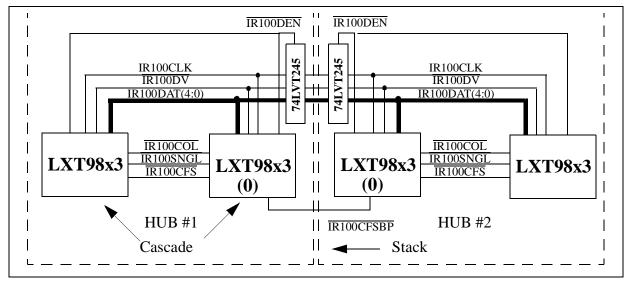

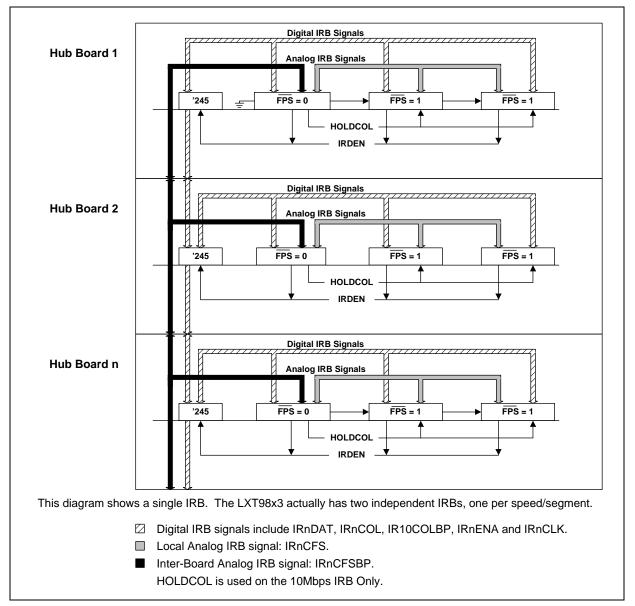

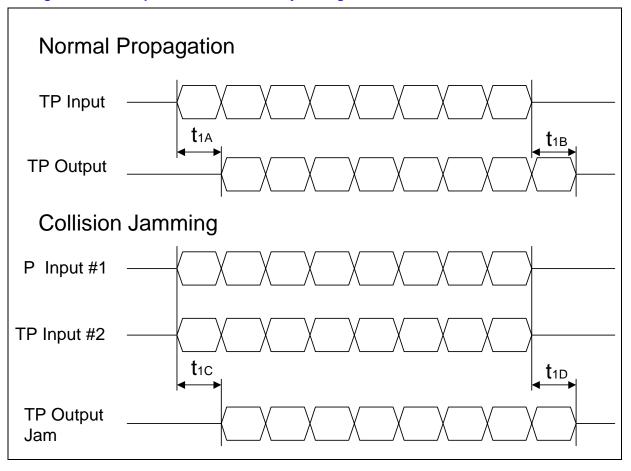

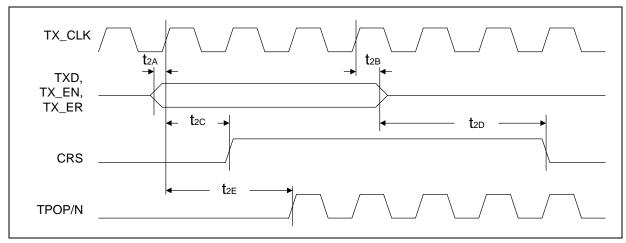

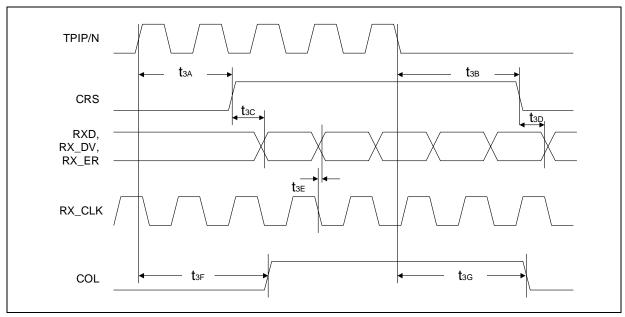

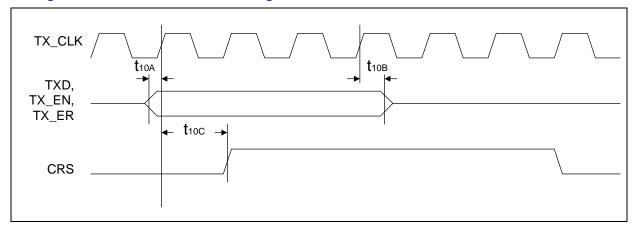

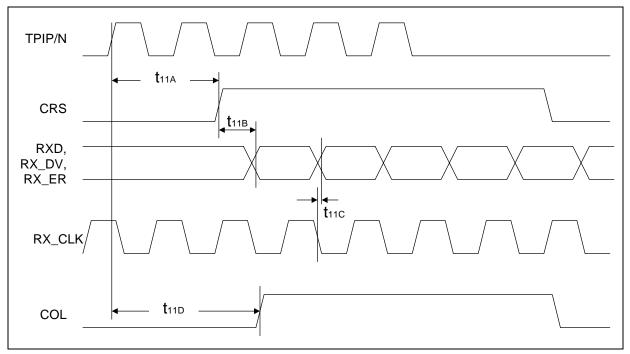

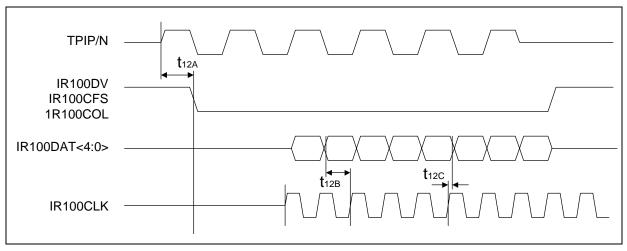

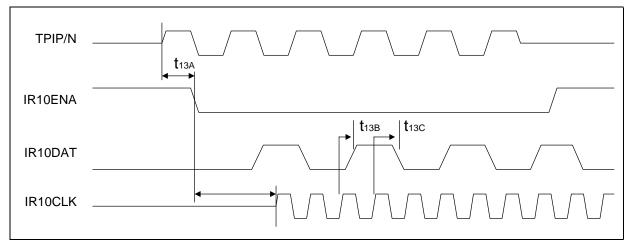

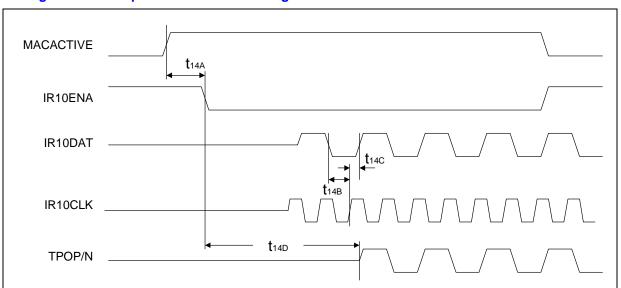

When used in 100TX applications, the LXT98x3 sends and receives a continuous, scrambled 125 Mbps MLT-3 waveform on this interface. In the absence of data, IDLE symbols are sent and received in order to maintain the link.