# CCD Signal Processors with Integrated Timing Driver

# AD9848/AD9849

#### **FEATURES**

AD9848: 10-Bit, 20 MHz Version AD9849: 12-Bit, 30 MHz Version Correlated Double Sampler (CDS) -2 dB to +10 dB Pixel Gain Amplifier (*PxGA*®) 2 dB to 36 dB 10-Bit Variable Gain Amplifier (VGA) 10-Bit 20 MHz A/D Converter (AD9848) 12-Bit 30 MHz A/D Converter (AD9849) Black Level Clamp with Variable Level Control Complete On-Chip Timing Driver *Precision Timing*<sup>™</sup> Core with 1 ns Resolution @ 20 MSPS On-Chip 3 V Horizontal and RG Drivers (AD9849) 48-Lead LQFP Package

APPLICATIONS Digital Still Cameras

#### **PRODUCT DESCRIPTION**

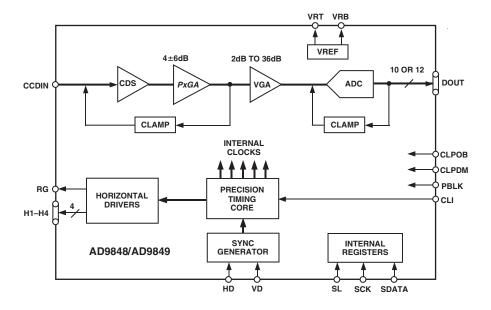

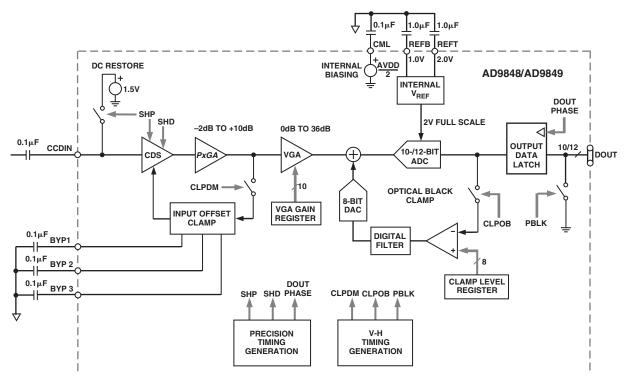

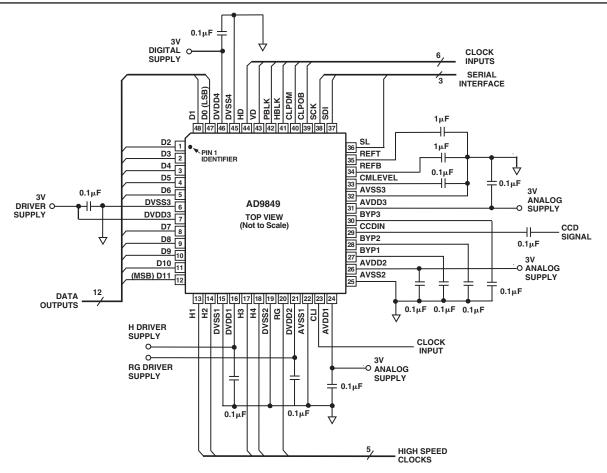

The AD9848 and AD9849 are highly integrated CCD signal processors for digital still camera applications. Both include a complete analog front end with A/D conversion, combined with a programmable timing driver. The *Precision Timing* core allows adjustment of high speed clocks with approximately 1 ns resolution.

The AD9848 is specified at pixel rates of 20 MHz, and the AD9849 is specified at 30 MHz. The analog front end includes black level clamping, CDS, PxGA, VGA, and a 10-bit or 12-bit A/D converter. The timing driver provides the high speed CCD clock drivers for RG and H1–H4. Operation is programmed using a 3-wire serial interface.

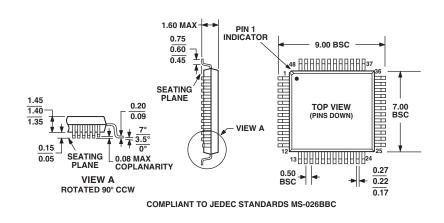

Packaged in a space saving 48-lead LQFP, the AD9848 and AD9849 are specified over an operating temperature range of  $-20^{\circ}$ C to  $+85^{\circ}$ C.

#### FUNCTIONAL BLOCK DIAGRAM

PxGA is a registered trademark and Precision Timing is a trademark of Analog Devices, Inc.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© 2003 Analog Devices, Inc.

# AD9848/AD9849-SPECIFICATIONS

# **GENERAL SPECIFICATIONS**

| Parameter                                | Min | Тур | Max  | Unit |

|------------------------------------------|-----|-----|------|------|

| TEMPERATURE RANGE                        |     |     |      |      |

| Operating                                | -20 |     | +85  | °C   |

| Storage                                  | -65 |     | +150 | °C   |

| MAXIMUM CLOCK RATE                       |     |     |      |      |

| AD9848                                   | 20  |     |      | MHz  |

| AD9849                                   | 30  |     |      | MHz  |

| POWER SUPPLY VOLTAGE, AD9848             |     |     |      |      |

| Analog (AVDD1, 2, 3)                     | 2.7 |     | 3.6  | V    |

| Digital1 (DVDD1) H1-H4                   | 2.7 |     | 3.6  | V    |

| Digital2 (DVDD2) RG                      | 2.7 |     | 3.6  | V    |

| Digital3 (DVDD3) D0-D11                  |     | 3.0 |      | V    |

| Digital4 (DVDD4) All Other Digital       |     | 3.0 |      | V    |

| POWER SUPPLY VOLTAGE, AD9849             |     |     |      |      |

| Analog (AVDD1, 2, 3)                     | 2.7 |     | 3.6  | V    |

| Digital1 (DVDD1) H1-H4                   | 3.0 |     | 5.5  | V    |

| Digital2 (DVDD2) RG                      | 3.0 |     | 5.5  | V    |

| Digital3 (DVDD3) D0-D11                  |     | 3.0 |      | V    |

| Digital4 (DVDD4) All Other Digital       |     | 3.0 |      | V    |

| POWER DISSIPATION, AD9848                |     |     |      |      |

| 20 MHz, DVDD1, 2 = 3 V, 100 pF H Loading |     | 220 |      | mW   |

| Total Shutdown Mode                      |     | 1   |      | mW   |

| POWER DISSIPATION, AD9849                |     |     |      |      |

| 30 MHz, DVDD1, 2 = 5 V, 100 pF H Loading |     | 450 |      | mW   |

| Total Shutdown Mode                      |     | 1   |      | mW   |

# **DIGITAL SPECIFICATIONS** $(T_{MIN} \text{ to } T_{MAX}, \text{ AVDD1} = \text{DVDD3}, \text{DVD24} = 2.7 \text{ V}, \text{DVDD1}, \text{DVDD2} = 2.7 \text{ V} (\text{AD9848}), \text{DVD1}, \text{DVD2} = 5.25 \text{ V} (\text{AD9849}), C_L = 20 \text{ pF}, \text{ unless otherwise noted.})$

| Parameter                                         | Symbol              | Min  | Тур | Max  | Unit |

|---------------------------------------------------|---------------------|------|-----|------|------|

| LOGIC INPUTS                                      |                     |      |     |      |      |

| High Level Input Voltage                          | V <sub>IH</sub>     | 2.1  |     |      | V    |

| Low Level Input Voltage                           | V <sub>IL</sub>     |      |     | 0.6  | V    |

| High Level Input Current                          | I <sub>IH</sub>     |      | 10  |      | μΑ   |

| Low Level Input Current                           | I <sub>IL</sub>     |      | 10  |      | μA   |

| Input Capacitance                                 | C <sub>IN</sub>     |      | 10  |      | pF   |

| LOGIC OUTPUTS                                     |                     |      |     |      |      |

| High Level Output Voltage, $I_{OH}$ = 2 mA        | V <sub>OH</sub>     | 2.2  |     |      | V    |

| Low Level Output Voltage, $I_{OL} = 2 \text{ mA}$ | V <sub>OL</sub>     |      |     | 0.5  | V    |

| CLI INPUT                                         |                     |      |     |      |      |

| High Level Input Voltage                          |                     |      |     |      |      |

| (AVDD1, 2 + 0.5 V)                                | V <sub>IH-CLI</sub> | 1.85 |     |      | V    |

| Low Level Input Voltage                           | V <sub>IL-CLI</sub> |      |     | 0.85 | V    |

| RG AND H-DRIVER OUTPUTS, AD9848                   |                     |      |     |      |      |

| High Level Output Voltage                         |                     |      |     |      |      |

| (DVDD1, 2 – 0.5 V)                                | V <sub>OH</sub>     | 2.2  |     |      | V    |

| Low Level Output Voltage                          | V <sub>OL</sub>     |      |     | 0.5  | V    |

| Maximum Output Current (Programmable)             |                     | 24   |     |      | mA   |

| Maximum Load Capacitance                          |                     | 100  |     |      | pF   |

| RG AND H-DRIVER OUTPUTS, AD9849                   |                     |      |     |      |      |

| High Level Output Voltage                         |                     |      |     |      |      |

| (DVDD1, 2 – 0.5 V)                                | V <sub>OH</sub>     | 4.75 |     |      | V    |

| Low Level Output Voltage                          | V <sub>OL</sub>     |      |     | 0.5  | V    |

| Maximum Output Current (Programmable)             |                     | 24   |     |      | mA   |

| Maximum Load Capacitance                          |                     | 100  |     |      | pF   |

# $\label{eq:added_matrix} AD9848-ANALOG SPECIFICATIONS \quad (T_{MIN} \ to \ T_{MAX}, \ AVDD = DVDD = 3.0 \ V, \ f_{CLI} = 20 \ MHz, \ unless \ otherwise \ noted.)$

| Parameter                                                                                                                                                                                   | Min        | Тур                               | Max     | Unit                                      | Notes                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------|---------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDS<br>Gain<br>Allowable CCD Reset Transient*<br>Max Input Range Before Saturation*<br>Max CCD Black Pixel Amplitude*                                                                       | 1.0        | 0<br>500<br>150                   |         | dB<br>mV<br>V p-p<br>mV                   | See Input Waveform in Note                                                                                                                                                                     |

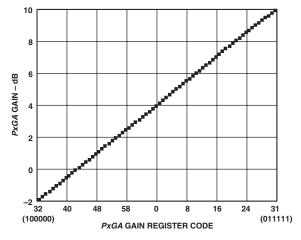

| PIXEL GAIN AMPLIFIER ( <i>PxGA</i> )<br>Max Input Range<br>Max Output Range<br>Gain Control Resolution<br>Gain Monotonicity<br>Gain Range<br>Min Gain (32)<br>Med Gain (0)<br>Max Gain (31) | 1.0<br>1.6 | 64<br>Guaranteed<br>-2<br>4<br>10 |         | V p-p<br>V p-p<br>Steps<br>dB<br>dB<br>dB | Medium Gain (4 dB) Is Default Setting                                                                                                                                                          |

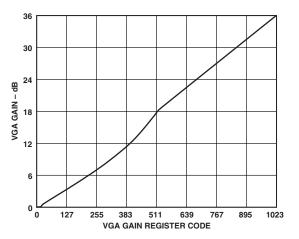

| VARIABLE GAIN AMPLIFIER (VGA)<br>Max Input Range<br>Max Output Range<br>Gain Control Resolution<br>Gain Monotonicity<br>Gain Range<br>Low Gain (91)<br>Max Gain (1023)                      | 1.6<br>2.0 | 1024<br>Guaranteed<br>2<br>36     |         | V p-p<br>V p-p<br>Steps<br>dB<br>dB       |                                                                                                                                                                                                |

| BLACK LEVEL CLAMP<br>Clamp Level Resolution<br>Clamp Level<br>Min Clamp Level (0)<br>Max Clamp Level (255)                                                                                  |            | 256<br>0<br>63.75                 |         | Steps<br>LSB<br>LSB                       | Measured at ADC Output                                                                                                                                                                         |

| A/D CONVERTER<br>Resolution<br>Differential Nonlinearity (DNL)<br>No Missing Codes<br>Full-Scale Input Voltage                                                                              | 10         | ±0.4<br>Guaranteed<br>2.0         | ±1.0    | Bits<br>LSB<br>V                          |                                                                                                                                                                                                |

| VOLTAGE REFERENCE<br>Reference Top Voltage (VRT)<br>Reference Bottom Voltage (VRB)                                                                                                          |            | 2.0<br>1.0                        |         | V<br>V                                    |                                                                                                                                                                                                |

| SYSTEM PERFORMANCE<br>VGA Gain Accuracy<br>Low Gain (91)<br>Max Gain (1023)<br>Peak Nonlinearity, 500 mV Input Signal<br>Total Output Noise<br>Power Supply Rejection (PSR)                 | 5<br>38    | 6<br>39.5<br>0.2<br>0.2<br>40     | 7<br>41 | dB<br>dB<br>%<br>LSB rms<br>dB            | Specifications Include Entire Signal Chain<br>Gain Includes 4 dB Default <i>PxGA</i> Gain<br>12 dB Gain Applied<br>AC Grounded Input, 6 dB Gain Applied<br>Measured with Step Change on Supply |

\*Input signal characteristics defined as follows:

**∠**₹` 500mV TYP RESET TRANSIENT 1V MAX INPUT SIGNAL RANGE 150mV MAX OPTICAL BLACK PIXEL

# $\label{eq:additional} AD9849-ANALOG SPECIFICATIONS \quad (T_{MIN} \ to \ T_{MAX}, \ AVDD = DVDD = 3.0 \ V, \ f_{CLI} = 30 \ MHz, \ unless \ otherwise \ noted.)$

| Min        | Тур                                                                                              | Max                                                   | Unit                                                  | Notes                                                                                                           |

|------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1.0        | 0<br>500<br>150                                                                                  |                                                       | dB<br>mV<br>V p-p<br>mV                               | See Input Waveform in Note                                                                                      |

| 1.0<br>1.6 | 64<br>Guaranteed<br>-2<br>4<br>10                                                                |                                                       | V p-p<br>V p-p<br>Steps<br>dB<br>dB<br>dB             | Medium Gain (4 dB) Is Default Setting                                                                           |

| 1.6<br>2.0 | 1024<br>Guaranteed<br>2<br>36                                                                    |                                                       | V p-p<br>V p-p<br>Steps<br>dB<br>dB                   |                                                                                                                 |

|            | 256<br>0<br>255                                                                                  |                                                       | Steps<br>LSB<br>LSB                                   | Measured at ADC Output                                                                                          |

| 12         | ±0.5<br>Guaranteed<br>2.0                                                                        | ±1.0                                                  | Bits<br>LSB<br>V                                      |                                                                                                                 |

|            | 2.0<br>1.0                                                                                       |                                                       | V<br>V                                                |                                                                                                                 |

| 5<br>38    | 6<br>39.5<br>0.2                                                                                 | 7<br>41                                               | dB<br>dB<br>%                                         | Specifications Include Entire Signal Chain<br>Gain Includes 4 dB Default <i>PxGA</i> Gain<br>12 dB Gain Applied |

|            | 1.0         1.0         1.6         2.0         1.6         2.0         1.2         5         38 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                           |

\*Input signal characteristics defined as follows:

500mV TYP RESET TRANSIENT 1V MAX INPUT SIGNAL RANGE 150mV MAX OPTICAL BLACK PIXEL

Specifications subject to change without notice.

# **TIMING SPECIFICATIONS** $(C_L = 20 \text{ pF}, f_{CLI} = 20 \text{ MHz} (AD9848) \text{ or } 30 \text{ MHz} (AD9849), \text{ Serial Timing in Figures 3a and 3b, unless otherwise noted.}$

| Parameter                                        | Symbol              | Min   | Тур | Max | Unit   |

|--------------------------------------------------|---------------------|-------|-----|-----|--------|

| MASTER CLOCK (CLI), AD9848                       |                     |       |     |     |        |

| CLI Clock Period                                 | t <sub>CLI</sub>    | 50    |     |     | ns     |

| CLI High/Low Pulsewidth                          | t <sub>ADC</sub>    | 25    |     |     | ns     |

| Delay From CLI to Internal Pixel Period Position | t <sub>CLIDLY</sub> |       | 6   |     | ns     |

| MASTER CLOCK (CLI), AD9849                       |                     |       |     |     |        |

| CLI Clock Period                                 | t <sub>CONV</sub>   | 33.33 |     |     | ns     |

| CLI High/Low Pulsewidth                          | t <sub>ADC</sub>    | 16.67 |     |     | ns     |

| EXTERNAL MODE CLAMPING                           |                     |       |     |     |        |

| CLPDM Pulsewidth                                 | t <sub>CDM</sub>    | 4     | 10  |     | Pixels |

| CLPOB Pulsewidth*                                | t <sub>COB</sub>    | 2     | 20  |     | Pixels |

| SAMPLE CLOCKS                                    |                     |       |     |     |        |

| SHP Rising Edge to SHD Rising Edge (AD9848)      | t <sub>S1</sub>     | 20    |     |     | ns     |

| SHP Rising Edge to SHD Rising Edge (AD9849)      | t <sub>S1</sub>     | 13    |     |     | ns     |

| DATA OUTPUTS                                     |                     |       |     |     |        |

| Output Delay from Programmed Edge                | t <sub>OD</sub>     |       | 6   |     | ns     |

| Pipeline Delay                                   | -00                 |       | 9   |     | Cycles |

| SERIAL INTERFACE                                 |                     |       |     |     |        |

| Maximum SCK Frequency                            | f <sub>SCLK</sub>   | 10    |     |     | MHz    |

| SL to SCK Setup Time                             | tLS                 | 10    |     |     | ns     |

| SCK to SL Hold Time                              | t <sub>LH</sub>     | 10    |     |     | ns     |

| SDATA Valid to SCK Rising Edge Setup             | t <sub>DS</sub>     | 10    |     |     | ns     |

| SCK Falling Edge to SDATA Valid Hold             | t <sub>DH</sub>     | 10    |     |     | ns     |

| SCK Falling Edge to SDATA Valid Read             | t <sub>DV</sub>     | 10    |     |     | ns     |

\*Maximum CLPOB pulsewidth is for functional operation only. Wider typical pulses are recommended to achieve low noise clamp reference.

| Parameter                 | With<br>Respect To | Min  | Max         | Unit |

|---------------------------|--------------------|------|-------------|------|

| AVDD1, 2, 3               | AVSS               | -0.3 | +3.9        | V    |

| DVDD1, DVDD2 (AD9848)     | DVSS               | -0.3 | +3.9        | V    |

| DVDD1, DVDD2 (AD9849)     | DVSS               | -0.3 | +5.5        | V    |

| DVDD3, 4                  | DVSS               | -0.3 | +3.9        | V    |

| Digital Outputs           | DVSS3              | -0.3 | DVDD3 + 0.3 | V    |

| CLPOB, CLPDM, BLK         | DVSS4              | -0.3 | DVDD4 + 0.3 | V    |

| CLI                       | AVSS               | -0.3 | AVDD + 0.3  | V    |

| SCK, SL, SDATA            | DVSS4              | -0.3 | DVDD4 + 0.3 | V    |

| VRT, VRB                  | AVSS               | -0.3 | AVDD + 0.3  | V    |

| BYP1–3, CCDIN             | AVSS               | -0.3 | AVDD + 0.3  | V    |

| Junction Temperature      |                    |      | 150         | °C   |

| Lead Temperature (10 sec) |                    |      | 300         | °C   |

#### ABSOLUTE MAXIMUM RATINGS

#### THERMAL CHARACTERISTICS

Thermal Resistance 48-Lead LQFP Package  $\theta_{IA} = 92^{\circ}C$

#### **ORDERING GUIDE**

| Model      | Temperature<br>Range | Package<br>Description               | Package<br>Option |

|------------|----------------------|--------------------------------------|-------------------|

| AD9848AKST | -20°C to +85°C       | Thin Plastic Quad<br>Flatpack (LQFP) | ST-48             |

| AD9849AKST | –20°C to +85°C       | Thin Plastic Quad<br>Flatpack (LQFP) | ST-48             |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9848/AD9849 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

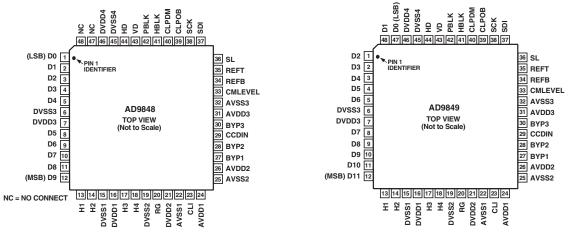

#### PIN CONFIGURATION

#### PIN FUNCTION DESCRIPTIONS

| Pin    | Mnemonic | Type* | Description                                                         |

|--------|----------|-------|---------------------------------------------------------------------|

| 1–5    | D0-D4    | DO    | Data Outputs AD9848 Only                                            |

| 1–5    | D2-D6    | DO    | Data Outputs AD9849 Only                                            |

| 6      | DVSS3    | Р     | Digital Ground 3 – Data Outputs                                     |

| 7      | DVDD3    | Р     | Digital Supply 3 – Data Outputs                                     |

| 8-12   | D5-D9    | DO    | Data Outputs (D9 is MSB) AD9848 Only                                |

| 8-12   | D7–D11   | DO    | Data Outputs (D9 is MSB) AD9849 Only                                |

| 13, 14 | H1, H2   | DO    | Horizontal Clocks (to CCD)                                          |

| 15     | DVSS1    | Р     | Digital Ground 1 – H Drivers                                        |

| 16     | DVDD1    | Р     | Digital Supply 1 – H Drivers                                        |

| 17, 18 | H3, H4   | DO    | Horizontal Clocks (to CCD)                                          |

| 19     | DVSS2    | Р     | Digital Ground 1 – RG Driver                                        |

| 20     | RG       | DO    | Reset Gate Clock (to CCD)                                           |

| 21     | DVDD2    | Р     | Digital Supply 2 – RG Driver                                        |

| 22     | AVSS1    | Р     | Analog Ground 1                                                     |

| 23     | CLI      | DI    | Master Clock Input                                                  |

| 24     | AVDD1    | Р     | Analog Supply 1                                                     |

| 25     | AVSS2    | Р     | Analog Ground 2                                                     |

| 26     | AVDD2    | Р     | Analog Supply 2                                                     |

| 27     | BYP1     | AO    | Bypass Pin (0.1 µF to AVSS)                                         |

| 28     | BYP2     | AO    | Bypass Pin (0.1 µF to AVSS)                                         |

| 29     | CCDIN    | AI    | Analog Input for CCD Signal                                         |

| 30     | BYP3     | AO    | Bypass Pin (0.1 µF to AVSS)                                         |

| 31     | AVDD3    | Р     | Analog Supply 3                                                     |

| 32     | AVSS3    | Р     | Analog Ground 3                                                     |

| 33     | CMLEVEL  | AO    | Internal Bias Level Decoupling (0.1 µF to AVSS)                     |

| 34     | REFB     | AO    | Reference Bottom Decoupling (1.0 µF to AVSS)                        |

| 35     | REFT     | AO    | Reference Top Decoupling (1.0 µF to AVSS)                           |

| 36     | SL       | DI    | 3-Wire Serial Load (from μP)                                        |

| 37     | SDI      | DI    | 3-Wire Serial Data Input (from µP)                                  |

| 38     | SCK      | DI    | 3-Wire Serial Clock (from $\mu P$ )                                 |

| 39     | CLPOB    | DI    | Optical Black Clamp Pulse                                           |

| 40     | CLPDM    | DI    | Dummy Black Clamp Pulse                                             |

| 41     | HBLK     | DI    | HCLK Blanking Pulse                                                 |

| 42     | PBLK     | DI    | Preblanking Pulse                                                   |

| 43     | VD       | DI    | Vertical Sync Pulse                                                 |

| 44     | HD       | DI    | Horizontal Sync Pulse                                               |

| 45     | DVSS4    | Р     | Digital Ground 4 - VD, HD, CLPOB, CLPDM, HBLK, PBLK, SCK, SL, SDATA |

| 46     | DVDD4    | Р     | Digital Supply 4 - VD, HD, CLPOB, CLPDM, HBLK, PBLK, CK, SL, SDATA  |

| 47, 48 | NC       | NC    | Internally Not Connected AD9848 Only                                |

| 47, 48 | D0, D1   | DO    | Data Output (D0 is LSB) AD9849 Only                                 |

\*Type: AI = Analog Input, AO = Analog Output, DI = Digital Input, DO = Digital Output, P = Power

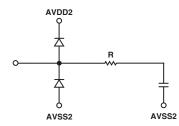

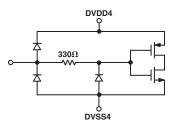

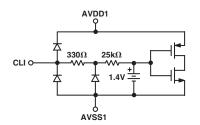

#### EQUIVALENT INPUT/OUTPUT CIRCUITS

Circuit 1. CCDIN (Pin 29)

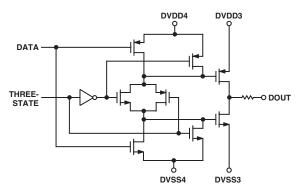

Circuit 4. Digital Inputs (Pins 36-44)

#### Circuit 2. CLI (Pin 23)

Circuit 3. Data Outputs D0-D11 (Pins 1-5, 8-12, 47-48)

Circuit 5. H1–H4 and RG (Pins 13, 14, 17, 18, 20)

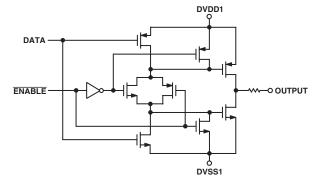

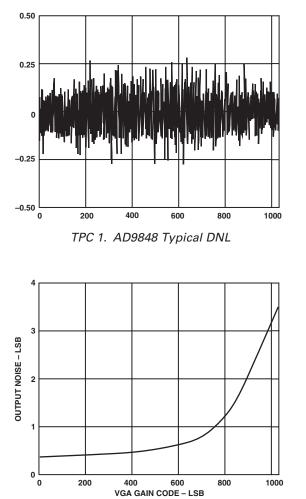

# AD9848/AD9849—Typical Performance Characteristics

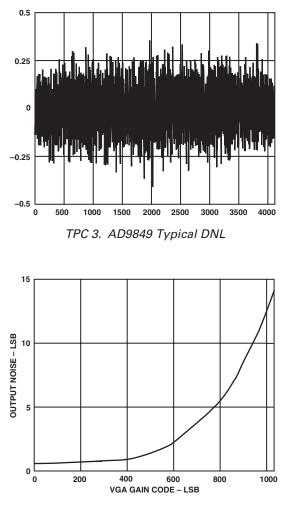

TPC 2. AD9848 Output Noise vs. VGA Gain Setting

TPC 4. AD9849 Output Noise vs. VGA Gain Setting

#### SYSTEM OVERVIEW

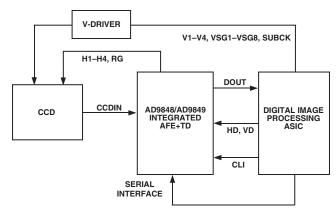

Figure 1a. Typical Application (Internal Mode)

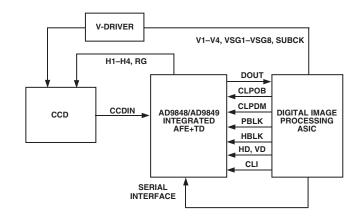

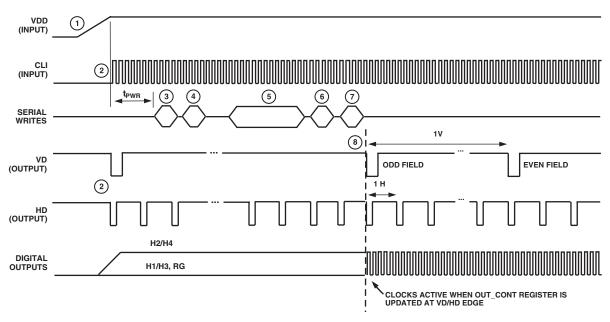

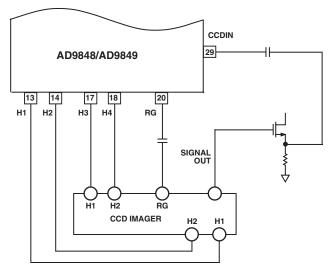

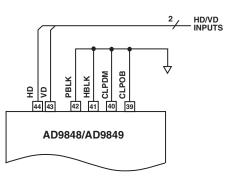

Figures 1a and 1b show the typical system application diagrams for the AD9848/AD9849. The CCD output is processed by the AD9848/AD9849's AFE circuitry, which consists of a CDS, PxGA, VGA, black level clamp, and A/D converter. The digitized pixel information is sent to the digital image processor chip, where all post-processing and compression occurs. To operate the CCD, CCD timing parameters are programmed into the AD9848/AD9849 from the image processor, through the 3-wire serial interface. From the system master clock, CLI, provided by the image processor, the AD9848/AD9849 generates the high speed CCD clocks and all internal AFE clocks. All AD9848/AD9849 clocks are synchronized with VD and HD.

Figure 1a shows the AD9848/AD9849 used in Internal Mode, in which all the horizontal pulses (CLPOB, CLPDM, PBLK, and HBLK) are programmed and generated internally. Figure 1b shows the AD9848/AD9849 operating in External Mode, in which the horizontal pulses are supplied externally by the image processor.

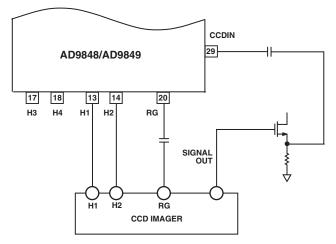

The H-drivers for H1–H4 and RG are included in the AD9848/ AD9849, allowing these clocks to be directly connected to the CCD. H-drive voltage of 5 V is supported in the AD9849.

Figure 1b. Typical Application (External Mode)

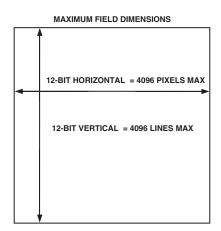

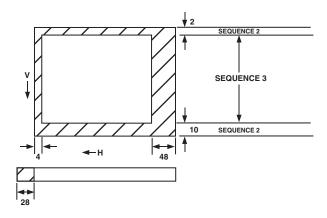

Figure 2 shows the horizontal and vertical counter dimensions for the AD9848/AD9849. All internal horizontal clocking is programmed using these dimensions to specify line and pixel locations.

Figure 2. Vertical and Horizontal Counters

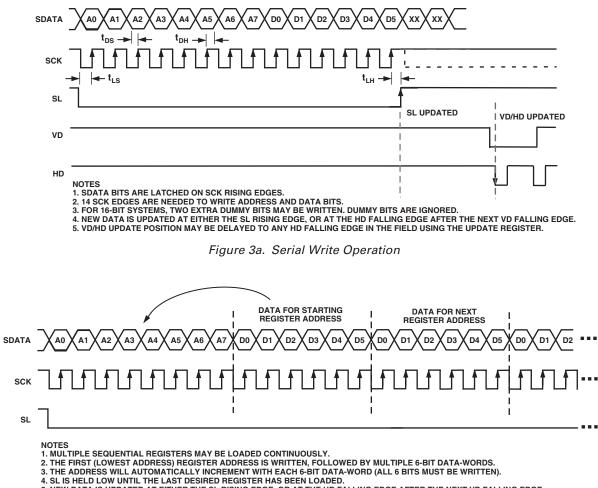

#### SERIAL INTERFACE TIMING

5. NEW DATA IS UPDATED AT EITHER THE SL RISING EDGE, OR AT THE HD FALLING EDGE AFTER THE NEXT VD FALLING EDGE.

Figure 3b. Continuous Serial Write Operation

#### **COMPLETE REGISTER LISTING**

Table I.

| Register     | Description                              | Register  | Description               |

|--------------|------------------------------------------|-----------|---------------------------|

| oprmode      | AFE Operation Modes                      | h1drv     | H1 Drive Current          |

| ctlmode      | AFE Control Modes                        | h2drv     | H2 Drive Current          |

| preventpdate | Prevents Loading of VD-Updated Registers | h3drv     | H3 Drive Current          |

| readback     | Enables Serial Register Readback Mode    | h4drv     | H4 Drive Current          |

| vdhdpol      | VD/HD Active Polarity                    | rgpol     | RG Polarity               |

| fieldval     | Internal Field Pulse Value               | rgposloc  | RG Positive Edge Location |

| hblkretime   | Retimes the H1 hblk to Internal Clock    | rgnegloc  | RG Negative Edge Location |

| tgcore_rstb  | Reset Bar Signal for Internal TG Core    | rgdrv     | RG Drive Current          |

| h12pol       | H1/H2 Polarity Control                   | shpposloc | SHP Sample Location       |

| hlposloc     | H1 Positive Edge Location                | shdposloc | SHD Sample Location       |

| h1negloc     | H1 Negative Edge Location                | _         | _                         |

NOTES

1. All addresses and default values are expressed in hexadecimal.

2. All registers are VD/HD updated as shown in Figure 3a, except for the above-listed registers that are SL updated.

#### Accessing a Double-Wide Register

There are many double-wide registers in the AD9848/AD9849, for example, oprmode, clpdmtog1\_0, and clpdmscp3, and so on. These registers are configured into two consecutive 6-bit registers with the least significant six bits located in the lower of the two addresses and the remaining most significant bits located in the higher of the two addresses. For example, the six LSBs of the clpdmscp3 register, clpdmscp3[5:0], are located at Address 0x81. The most significant six bits of the clpdmscp3 register, clpdmscp3[11:6], are located at Address 0x82. The following rules must be followed when accessing double-wide registers:

- 1. When accessing a double-wide register, BOTH addresses must be written to.

- 2. The lower of the two consecutive addresses for the doublewide register must be written to first. In the example of the

clpdmscp3 register, the contents of Address 0x81 must be written first followed by the contents of Address 0x82. The register will be updated after the completion of the write to Register 0x82, either at the next SL rising edge or next VD/HD falling edge.

- 3. A single write to the lower of the two consecutive addresses of a double-wide register that is not followed by a write to the higher address of the registers is not permitted. This will not update the register.

- 4. A single write to the higher of the two consecutive addresses of a double-wide register that is not preceded by a write to the lower of the two addresses is not permitted. Although the write to the higher address will update the full double-wide register, the lower six bits of the register will be written with an indeterminate value if the lower address was not written first.

| Address   | Bit<br>Content | Width | Default<br>Value | Register Name | Register Description                            |

|-----------|----------------|-------|------------------|---------------|-------------------------------------------------|

| AFE Regis | sters # Bits 5 | 6     |                  |               |                                                 |

| 00        | [5:0]          | 6     | 00               | oprmode[5:0]  | AFE Operation Mode (See AFE Register Breakdown) |

| 01        | [1:0]          | 2     | 00               | oprmode[7:6]  |                                                 |

| 02        | [5:0]          | 6     | 16               | ccdgain[5:0]  | VGA Gain                                        |

| 03        | [3:0]          | 4     | 02               | ccdgain[9:6]  |                                                 |

| 04        | [5:0]          | 6     | 00               | refblack[5:0] | Black Clamp Level                               |

| 05        | [1:0]          | 2     | 02               | refblack[7:6] |                                                 |

| 06        | [5:0]          | 6     | 00               | ctlmode       | Control Mode (See AFE Register Breakdown)       |

| 07        | [5:0]          | 6     | 00               | pxga gain0    | PxGA Color 0 Gain                               |

| 08        | [5:0]          | 6     | 00               | pxga gain1    | PxGA Color 1 Gain                               |

| 09        | [5:0]          | 6     | 00               | pxga gain2    | PxGA Color 2 Gain                               |

| 0A        | [5:0]          | 6     | 00               | pxga gain3    | PxGA Color 3 Gain                               |

| Miscell | aneous/Extra | # Bits 26 |    |                |                                                                                   |

|---------|--------------|-----------|----|----------------|-----------------------------------------------------------------------------------|

| 0F      | [5:0]        | 6         | 00 | INITIAL2       | See Recommended Power-Up Sequence Section. Should be set to "4" decimal (000100). |

| 16      | [0]          | 1         | 00 | out_cont       | Output Control (0 = Make All Outputs DC Inactive)                                 |

| 17      | [5:0]        | 6         | 00 | update[5:0]    | Serial Data Update Control. Sets the line within the field                        |

| 18      | [5:0]        | 6         | 00 | update[11:6]   | for serial data update to occur.                                                  |

| 19      | [0]          | 1         | 00 | preventupdate  | Prevent the Update of the "VD/HD Updated" Registers                               |

| 1B      | [5:0]        | 6         | 00 | doutphase      | DOUT Phase Control                                                                |

| 1C      | [0]          | 1         | 00 | disablerestore | Disable CCDIN DC Restore Circuit during PBLK                                      |

|         | 503          |           |    |                | (1 = Disable)                                                                     |

| 1D      | [0]          | 1         | 00 | vdhdpol        | VD/HD Active Polarity (0 = Low Active, 1 = High Active)                           |

| 1E      | [0]          | 1         | 01 | fieldval       | Internal Field Pulse Value (0 = Next Field Odd,<br>1 = Next Field Even)           |

| 1F      | [0]          | 1         | 00 | hblkretime     | Re-Sync hblk to h1 Clock                                                          |

| 20      | [5:0]        | 6         | 00 | INITIAL1       | See Recommended Power-Up Sequence Section. Should be                              |

| 20      | [0:0]        | 0         | 00 |                | set to "53" decimal (110101).                                                     |

| 26      | [0]          | 1         | 00 | tgcore_rstb    | TG Core Reset_Bar (0 = Hold TG Core in Reset,                                     |

|         |              |           |    |                | 1 = Resume Normal Operation)                                                      |

REV. A

| Address  | Bit<br>Content | Width | Default<br>Value | Register Name        | Register Description                                                                                                        |

|----------|----------------|-------|------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| CLPDM #  | Bits 146       | 1     |                  |                      |                                                                                                                             |

| 64<br>65 | [0]<br>[0]     | 1 1   | 01 00            | clpdmdir<br>clpdmpol | CLPDM Internal/External (0 = Internal, 1 = External)<br>CLPDM External Active Polarity (0 = Low Active,<br>1 = High Active) |

| 66       | [0]            | 1     | 01               | clpdmspol0           | Sequence #0: Start Polarity for CLPDM                                                                                       |

| 67       | [5:0]          | 6     | 2C               | clpdmtog1_0[5:0]     | Sequence #0: Toggle Position 1 for CLPDM                                                                                    |

| 68       | [5:0]          | 6     | 00               | clpdmtog1_0[11:6]    |                                                                                                                             |

| 69       | [5:0]          | 6     | 35               | clpdmtog2_0[5:0]     | Sequence #0: Toggle Position 2 for CLPDM                                                                                    |

| 6A       | [5:0]          | 6     | 00               | clpdmtog2_0[11:6]    |                                                                                                                             |

| 6B       | [0]            | 1     | 01               | clpdmspol1           | Sequence #1: Start Polarity for CLPDM                                                                                       |

| 6C       | [5:0]          | 6     | 3E               | clpdmtog1_1[5:0]     | Sequence #1: Toggle Position 1 for CLPDM                                                                                    |

| 6D       | [5:0]          | 6     | 02               | clpdmtog1_1[11:6]    |                                                                                                                             |

| 6E       | [5:0]          | 6     | 16               | clpdmtog2_1[5:0]     | Sequence #1: Toggle Position 2 for CLPDM                                                                                    |

| 6F       | [5:0]          | 6     | 03               | clpdmtog2_1[11:6]    |                                                                                                                             |

| 70       | [0]            | 1     | 00               | clpdmspol2           | Sequence #2: Start Polarity for CLPDM                                                                                       |

| 71       | [5:0]          | 6     | 3F               | clpdmtog1_2[5:0]     | Sequence #2: Toggle Position 1 for CLPDM                                                                                    |

| 72       | [5:0]          | 6     | 3F               | clpdmtog1_2[11:6]    |                                                                                                                             |

| 73       | [5:0]          | 6     | 3F               | clpdmtog2_2[5:0]     | Sequence #2: Toggle Position 2 for CLPDM                                                                                    |

| 74       | [5:0]          | 6     | 3F               | clpdmtog2_2[11:6]    |                                                                                                                             |

| 75       | [0]            | 1     | 01               | clpdmspol3           | Sequence #3: Start Polarity for CLPDM                                                                                       |

| 76       | [5:0]          | 6     | 3F               | clpdmtog1_3[5:0]     | Sequence #3: Toggle Position 1 for CLPDM                                                                                    |

| 77       | [5:0]          | 6     | 3F               | clpdmtog1_3[11:6]    |                                                                                                                             |

| 78       | [5:0]          | 6     | 3F               | clpdmtog2_3[5:0]     | Sequence #3: Toggle Position 2 for CLPDM                                                                                    |

| 79       | [5:0]          | 6     | 3F               | clpdmtog2_3[11:6]    |                                                                                                                             |

|          |                | 0     | 00               | clpdmscp0            | CLPDM Sequence-Change-Position #0 (Hardcoded to 0)                                                                          |

| 7A       | [1:0]          | 2     | 00               | clpdmsptr0           | CLPDM Sequence Pointer for SCP #0                                                                                           |

| 7B       | [5:0]          | 6     | 3F               | clpdmscp1[5:0]       | CLPDM Sequence-Change-Position #1                                                                                           |

| 7C       | [5:0]          | 6     | 3F               | clpdmscp1[11:6]      |                                                                                                                             |

| 7D       | [1:0]          | 2     | 00               | clpdmsptr1           | CLPDM Sequence Pointer for SCP #1                                                                                           |

| 7E       | [5:0]          | 6     | 3F               | clpdmscp2[5:0]       | CLPDM Sequence-Change-Position #2                                                                                           |

| 7F       | [5:0]          | 6     | 3F               | clpdmscp2[11:6]      |                                                                                                                             |

| 80       | [1:0]          | 2     | 00               | clpdmsptr2           | CLPDM Sequence Pointer for SCP #2                                                                                           |

| 81       | [5:0]          | 6     | 3F               | clpdmscp3[5:0]       | CLPDM Sequence-Change-Position #3                                                                                           |

| 82       | [5:0]          | 6     | 3F               | clpdmscp3[11:6]      |                                                                                                                             |

| 83       | [1:0]          | 2     | 00               | clpdmsptr3           | CLPDM Sequence Pointer for SCP #3                                                                                           |

| Address | Bit<br>Content | Width | Default<br>Value | Register Name     | Register Description                                 |

|---------|----------------|-------|------------------|-------------------|------------------------------------------------------|

| CLPOB # | Bits 146       |       |                  |                   |                                                      |

| 84      | [0]            | 1     | 01               | clpobdir          | CLPOB Internal/External (0 = Internal, 1 = External) |

| 85      | [0]            | 1     | 00               | clpobpol          | CLPOB External Active Polarity (0 = Low Active,      |

|         |                |       |                  |                   | 1 = High Active)                                     |

| 86      | [0]            | 1     | 01               | clpobpol0         | Sequence #0: Start Polarity for CLPOB                |

| 87      | [5:0]          | 6     | 0E               | clpobtog1_0[5:0]  | Sequence #0: Toggle Position 1 for CLPOB             |

| 88      | [5:0]          | 6     | 00               | clpobtog1_0[11:6] |                                                      |

| 89      | [5:0]          | 6     | 2B               | clpobtog2_0[5:0]  | Sequence #0: Toggle Position 2 for CLPOB             |

| 8A      | [5:0]          | 6     | 00               | clpobtog2_0[11:6] |                                                      |

| 8B      | [0]            | 1     | 01               | clpobpol1         | Sequence #1: Start Polarity for CLPOB                |

| 8C      | [5:0]          | 6     | 2B               | clpobtog1_1[5:0]  | Sequence #1: Toggle Position 1 for CLPOB             |

| 8D      | [5:0]          | 6     | 06               | clpobtog1_1[11:6] |                                                      |

| 8E      | [5:0]          | 6     | 3F               | clpobtog2_1[5:0]  | Sequence #1: Toggle Position 2 for CLPOB             |

| 8F      | [5:0]          | 6     | 3F               | clpobtog2_1[11:6] |                                                      |

| 90      | [0]            | 1     | 00               | clpobspol2        | Sequence #2: Start Polarity for CLPOB                |

| 91      | [5:0]          | 6     | 3F               | clpobtog1_2[5:0]  | Sequence #2: Toggle Position 1 for CLPOB             |

| 92      | [5:0]          | 6     | 3F               | clpobtog1_2[11:6] |                                                      |

| 93      | [5:0]          | 6     | 3F               | clpobtog2_2[5:0]  | Sequence #2: Toggle Position 2 for CLPOB             |

| 94      | [5:0]          | 6     | 3F               | clpobtog2_2[11:6] |                                                      |

| 95      | [0]            | 1     | 01               | clpobspol3        | Sequence #3: Start Polarity for CLPOB                |

| 96      | [5:0]          | 6     | 3F               | clpobtog1_3[5:0]  | Sequence #3: Toggle Position 1 for CLPOB             |

| 97      | [5:0]          | 6     | 3F               | clpobtog1_3[11:6] |                                                      |

| 98      | [5:0]          | 6     | 3F               | clpobtog2_3[5:0]  | Sequence #3: Toggle Position 2 for CLPOB             |

| 99      | [5:0]          | 6     | 3F               | clpobtog2_3[11:6] |                                                      |

|         |                | 0     | 00               | clpobscp0         | CLPOB Sequence-Change-Position #0 (Hardcoded to 0)   |

| 9A      | [1:0]          | 2     | 03               | clpobsptr0        | CLPOB Sequence Pointer for SCP #0                    |

| 9B      | [5:0]          | 6     | 01               | clpobscp1[5:0]    | CLPOB Sequence-Change-Position #1                    |

| 9C      | [5:0]          | 6     | 00               | clpobscp1[11:6]   |                                                      |

| 9D      | [1:0]          | 2     | 01               | clpobsptr1        | CLPOB Sequence Pointer for SCP #1                    |

| 9E      | [5:0]          | 6     | 02               | clpobscp2[5:0]    | CLPOB Sequence-Change-Position #2                    |

| 9F      | [5:0]          | 6     | 00               | clpobscp2[11:6]   |                                                      |

| A0      | [1:0]          | 2     | 00               | clpobsptr2        | CLPOB Sequence Pointer for SCP #2                    |

| A1      | [5:0]          | 6     | 37               | clpobscp3[5:0]    | CLPOB Sequence-Change-Position #3                    |

| A2      | [5:0]          | 6     | 03               | clpobscp3[11:6]   |                                                      |

| A3      | [1:0]          | 2     | 03               | clpobsptr3        | CLPOB Sequence Pointer for SCP #3                    |

| Address  | Bit<br>Content | Width | Default<br>Value | Register Name     | Register Description                                                        |

|----------|----------------|-------|------------------|-------------------|-----------------------------------------------------------------------------|

| HBLK # B | Sits 147       | -     |                  | 1                 |                                                                             |

| A4       | [0]            | 1     | 01               | hblkdir           | HBLK Internal/External (0 = Internal, 1 = External)                         |

| A5       | [0]            | 1     | 00               | hblkpol           | HBLK External Active Polarity (0 = Low Active,                              |

| A6       | [0]            | 1     | 01               | hblkextmask       | 1 = High Active)<br>HBLK External Masking Polarity (0 = Mask H1 and H3 Low, |

| A0       | [0]            |       | 01               | HOIKextillask     | 1 = Mask H1 and H3 High)                                                    |

| A7       | [0]            | 1     | 01               | hblkmask0         | Sequence #0: Masking Polarity for HBLK                                      |

| A8       | [5:0]          | 6     | 3E               | hblktog1_0[5:0]   | Sequence #0: Toggle Low Position for HBLK                                   |

| A9       | [5:0]          | 6     | 00               | hblktog1_0[11:6]  |                                                                             |

| AA       | [5:0]          | 6     | 0D               | hblkbtog2_0[5:0]  | Sequence #0: Toggle High Position for HBLK                                  |

| AB       | [5:0]          | 6     | 06               | hblkbtog2_0[11:6] |                                                                             |

| AC       | [0]            | 1     | 01               | hblkmask1         | Sequence #1: Masking Polarity for HBLK                                      |

| AD       | [5:0]          | 6     | 38               | hblktog1_1[5:0]   | Sequence #1: Toggle Low Position for HBLK                                   |

| AE       | [5:0]          | 6     | 00               | hblktog1_1[11:6]  |                                                                             |

| AF       | [5:0]          | 6     | 3C               | hblktog2_1[5:0]   | Sequence #1: Toggle High Position for HBLK                                  |

| B0       | [5:0]          | 6     | 02               | hblktog2_1[11:6]  |                                                                             |

| B1       | [0]            | 1     | 00               | hblkmask2         | Sequence #2: Masking Polarity for HBLK                                      |

| B2       | [5:0]          | 6     | 3F               | hblktog1_2[5:0]   | Sequence #2: Toggle Low Position for HBLK                                   |

| B3       | [5:0]          | 6     | 3F               | hblktog1_2[11:6]  |                                                                             |

| B4       | [5:0]          | 6     | 3F               | hblktog2_2[5:0]   | Sequence #2: Toggle High Position for HBLK                                  |

| B5       | [5:0]          | 6     | 3F               | hblktog2_2[11:6]  |                                                                             |

| B6       | [0]            | 1     | 01               | hblkmask3         | Sequence #3: Masking Polarity for HBLK                                      |

| B7       | [5:0]          | 6     | 3F               | hblktog1_3[5:0]   | Sequence #3: Toggle Low Position for HBLK                                   |

| B8       | [5:0]          | 6     | 3F               | hblktog1_3[11:6]  |                                                                             |

| B9       | [5:0]          | 6     | 3F               | hblktog2_3[5:0]   | Sequence #3: Toggle High Position for HBLK                                  |

| BA       | [5:0]          | 6     | 3F               | hblktog2_3[11:6]  |                                                                             |

|          |                | 0     | 00               | hblkscp0          | HBLK Sequence-Change-Position #0 (Hardcoded to 0)                           |

| BB       | [1:0]          | 2     | 00               | hblksptr0         | HBLK Sequence Pointer for SCP #0                                            |

| BC       | [5:0]          | 6     | 3F               | hblkscp1[5:0]     | HBLK Sequence-Change-Position #1                                            |

| BD       | [5:0]          | 6     | 3F               | hblkscp1[11:6]    |                                                                             |

| BE       | [1:0]          | 2     | 00               | hblksptr1         | HBLK Sequence Pointer for SCP #1                                            |

| BF       | [5:0]          | 6     | 3F               | hblkscp2[5:0]     | HBLK Sequence-Change-Position #2                                            |

| C0       | [5:0]          | 6     | 3F               | hblkscp2[11:6]    |                                                                             |

| C1       | [1:0]          | 2     | 00               | hblksptr2         | HBLK Sequence Pointer for SCP #2                                            |

| C2       | [5:0]          | 6     | 3F               | hblkscp3[5:0]     | HBLK Sequence-Change-Position #3                                            |

| C3       | [5:0]          | 6     | 3F               | hblkscp3[11:6]    |                                                                             |

| C4       | [1:0]          | 2     | 00               | hblksptr3         | HBLK Sequence Pointer for SCP #3                                            |

| Address   | Bit<br>Content | Width       | Default<br>Value | Register Name     | Register Description                                                                                |

|-----------|----------------|-------------|------------------|-------------------|-----------------------------------------------------------------------------------------------------|

| PBLK # Bi | ts 146         |             |                  |                   |                                                                                                     |

| C5        | [0]            | 1           | 01               | pblkdir           | PBLK Internal/External (0 = Internal, 1 = External)                                                 |

| C6        | [0]            | 1           | 00               | pblkpol           | PBLK External Active Polarity (0 = Low Active,<br>1 = High Active)                                  |

| C7        | [0]            | 1           | 01               | pblkspol0         | Sequence #0: Start Polarity for PBLK                                                                |

| C8        | [5:0]          | 6           | 3D               | pblktog1_0[5:0]   | Sequence #0: Toggle Position 1 for PBLK                                                             |

| C9        | [5:0]          | 6           | 00               | pblktog1_0[11:6]  |                                                                                                     |

| CA        | [5:0]          | 6           | 2A               | pblkbtog2_0[5:0]  | Sequence #0: Toggle Position 2 for PBLK                                                             |

| CB        | [5:0]          | 6           | 06               | pblkbtog2_0[11:6] |                                                                                                     |

| CC        | [0]            | 1           | 00               | pblkspol1         | Sequence #1: Start Polarity for PBLK                                                                |

| CD        | [5:0]          | 6           | 2A               | pblktog1_1[5:0]   | Sequence #1: Toggle Position 1 for PBLK                                                             |

| CE        | [5:0]          | 6           | 06               | pblktog1_1[11:6]  |                                                                                                     |

| CF        | [5:0]          | 6           | 3F               | pblktog2_1[5:0]   | Sequence #1: Toggle Position 2 for PBLK                                                             |

| D0        | [5:0]          | 6           | 3F               | pblktog2_1[11:6]  |                                                                                                     |

| D1        | [0]            | 1           | 00               | pblkspol2         | Sequence #2: Start Polarity for PBLK                                                                |

| D2        | [5:0]          | 6           | 3F               | pblktog1_2[5:0]   | Sequence #2: Toggle Position 1 for PBLK                                                             |

| D3        | [5:0]          | 6           | 3F               | pblktog1_2[11:6]  |                                                                                                     |

| D4        | [5:0]          | 6           | 3F               | pblktog2_2[5:0]   | Sequence #2: Toggle Position 2 for PBLK                                                             |

| D5        | [5:0]          | 6           | 3F               | pblktog2_2[11:6]  |                                                                                                     |

| D6        | [0]            | 1           | 01               | pblkspol3         | Sequence #3: Start Polarity for PBLK                                                                |

| D7        | [5:0]          | 6           | 3F               | pblktog1_3[5:0]   | Sequence #3: Toggle Position 1 for PBLK                                                             |

| D8        | [5:0]          | 6           | 3F               | pblktog1_3[11:6]  |                                                                                                     |

| D9        | [5:0]          | 6           | 3F               | pblktog2_3[5:0]   | Sequence #3: Toggle Position 2 for PBLK                                                             |

| DA        | [5:0]          | 6           | 3F               | pblktog2_3[11:6]  |                                                                                                     |

|           |                | 0           | 00               | pblkscp0          | PBLK Sequence-Change-Position #0 (Hardcoded to 0)                                                   |

| DB        | [1:0]          | 2           | 02               | pblksptr0         | PBLK Sequence Pointer for SCP #0                                                                    |

| DC        | [5:0]          | 6           | 01               | pblkscp1[5:0]     | PBLK Sequence-Change-Position #1                                                                    |

| DD        | [5:0]          | 6           | 00               | pblkscp1[11:6]    |                                                                                                     |

| DE        | [1:0]          | 2           | 01               | pblksptr1         | PBLK Sequence Pointer for SCP #1                                                                    |

| DF        | [5:0]          | 6           | 02               | pblkscp2[5:0]     | PBLK Sequence-Change-Position #2                                                                    |

| E0        | [5:0]          | 6           | 00               | pblkscp2[11:6]    |                                                                                                     |

| E1        | [1:0]          | 2           | 00               | pblksptr2         | PBLK Sequence Pointer for SCP #2                                                                    |

| E2        | [5:0]          | 6           | 37               | pblkscp3[5:0]     | PBLK Sequence-Change-Position #3                                                                    |

| E3        | [5:0]          | 6           | 03               | pblkscp3[11:6]    |                                                                                                     |

| E4        | [1:0]          | 2           | 02               | pblksptr3         | PBLK Sequence Pointer for SCP #3                                                                    |

| H1-H4, R0 | , SHP, SHI     | D # Bits 53 |                  |                   |                                                                                                     |

| E5        | [0]            | 1           | 00               | h1pol             | H1/H2 Polarity Control (0 = No Inversion, 1 = Inversion)                                            |

| E6        | [5:0]          | 6           | 00               | h1posloc          | H1 Positive Edge Location                                                                           |

| E7        | [5:0]          | 6           | 20               | h1negloc          | H1 Negative Edge Location                                                                           |

| E8        | [2:0]          | 3           | 03               | h1drv             | H1 Drive Strength ( $0 = OFF$ , $1 = 3.5 \text{ mA}$ , $2 = 7 \text{ mA}$ ,                         |

| 20        | [2:0]          |             |                  |                   | 3 = 10.5  mA, 4 = 14  mA, 5 = 17.5  mA, 6 = 21  mA, 7 = 24.5  mA                                    |

| E9        | [2:0]          | 3           | 03               | h2drv             | H2 Drive Strength                                                                                   |

| EA        | [2:0]          | 3           | 03               | h3drv             | H3 Drive Strength                                                                                   |

| EB        | [2:0]          | 3           | 03               | h4drv             | H4 Drive Strength                                                                                   |

| EC        | [0]            | 1           | 00               | rgpol             | RG Polarity Control (0 = No Inversion, 1 = Inversion)                                               |

| ED        | [5:0]          | 6           | 00               | rgposloc          | RG Positive Edge Location                                                                           |

| EE        | [5:0]          | 6           | 10               | rgnegloc          | RG Negative Edge Location                                                                           |

| EF        | [2:0]          | 3           | 02               | rgdrv             | RG Drive Strength ( $0 = OFF$ , $1 = 3.5 \text{ mA}$ , $2 = 7 \text{ mA}$ , $3 = 10.5 \text{ mA}$ , |

| -         | []             |             |                  | 0                 | 4 = 14  mA, 5 = 17.5  mA, 6 = 21  mA, 7 = 24.5  mA                                                  |

| F0        | [5:0]          | 6           | 24               | shpposloc         | SHP (Positive) Edge Sampling Location                                                               |

| F1        | [5:0]          | 6           | 00               | shdposloc         | SHD (Positive) Edge Sampling Location                                                               |

| Address  | Bit<br>Content                                  | Width                                                                        | Default<br>Value | Register Name                                                                                            | Register Description                                                                                                                                                                                                                                                        |

|----------|-------------------------------------------------|------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AFE REGI | STER BREA                                       | KDOWN                                                                        |                  | 1                                                                                                        |                                                                                                                                                                                                                                                                             |

| oprmode  | [7:0]                                           |                                                                              | 8'h0             |                                                                                                          | Serial Address:<br>8'h00 {oprmode[5:0]}, 8'h01 {oprmode[7:6]}                                                                                                                                                                                                               |

|          | [1:0]<br>[2]<br>[3]<br>[4]<br>[5]<br>[6]<br>[7] | 2'h0<br>2'h1<br>2'h2<br>2'h3                                                 |                  | powerdown[1:0]<br>disblack<br>test mode<br>test mode<br>test mode<br>test mode<br>test mode<br>test mode | Full Power<br>Fast Recovery<br>Reference Standby<br>Total Shutdown<br>Disable Black Loop Clamping (High Active)<br>Test Mode—Should Be Set LOW<br>Test Mode—Should Be Set HIGH<br>Test Mode—Should Be Set LOW<br>Test Mode—Should Be Set LOW<br>Test Mode—Should Be Set LOW |

| ctlmode  | [5:0]                                           |                                                                              | 6'h0             |                                                                                                          | Serial Address: 8'h06 {cltmode[5:0]}                                                                                                                                                                                                                                        |

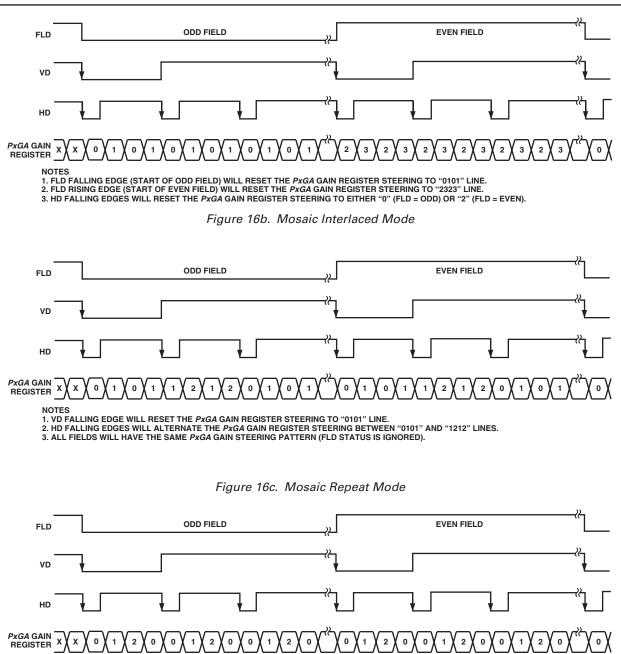

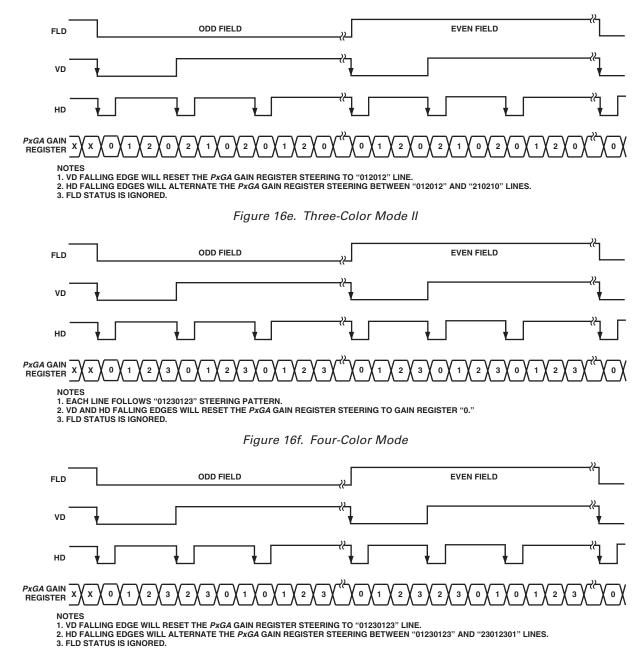

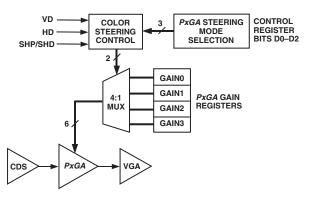

|          | [2:0]<br>[3]<br>[4]                             | 3'h0<br>3'h1<br>3'h2<br>3'h3<br>3'h4<br>3'h5<br>3'h6<br>3'h7<br>1'h0<br>1'h1 |                  | ctlmode[2:0]<br>enablepxga<br>outputlat                                                                  | Off<br>Mosaic Separate<br>VD Selected/Mosaic Interlaced<br>Mosaic Repeat<br>Three-Color<br>Three-Color II<br>Four-Color II<br>Four-Color II<br>Enable <i>PxGA</i> (High Active)<br>Latch Output Data on Selected DOUT Edge<br>Leave Output Latch Transparent                |

|          | [5]                                             | 1'h1<br>1'h0<br>1'h1                                                         |                  | tristateout                                                                                              | ADC Outputs Are Driven<br>ADC Outputs Are Three-Stated                                                                                                                                                                                                                      |

#### **PRECISION TIMING HIGH SPEED TIMING** GENERATION

The AD9848 and AD9849 generate flexible high speed timing signals using the *Precision Timing* core. This core is the foundation for generating the timing used for both the CCD and the AFE; the reset gate RG, horizontal drivers H1–H4, and the SHP/SHD sample clocks. A unique architecture makes it routine for the system designer to optimize image quality by providing precise control over the horizontal CCD readout and the AFE correlated double sampling.

#### **Timing Resolution**

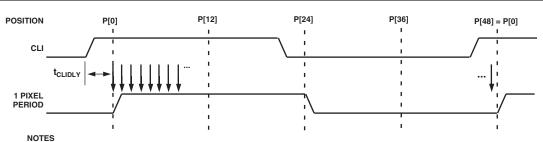

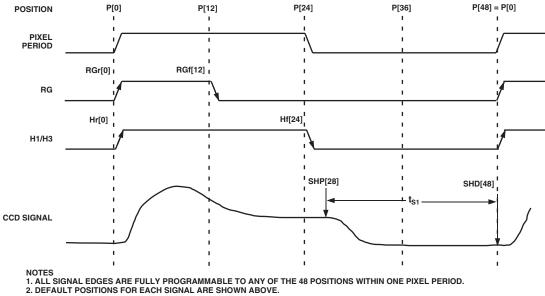

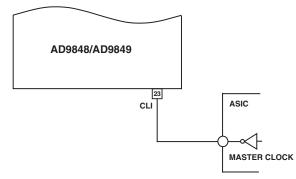

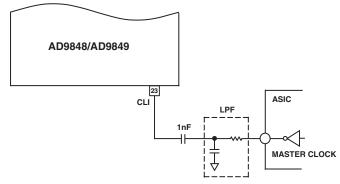

The *Precision Timing* core uses a  $1 \times$  master clock input (CLI) as a reference. This clock should be the same as the CCD pixel clock frequency. Figure 4 illustrates how the internal timing core divides the master clock period into 48 steps or edge positions. Therefore, the edge resolution of the *Precision Timing* core is (t<sub>CLI</sub>/48). For more information on using the CLI input, see the Driving the CLI Input section.

#### High Speed Clock Programmability

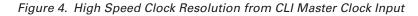

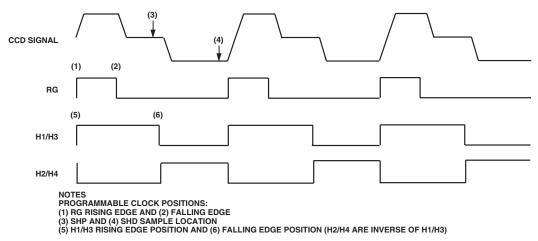

Figure 5 shows how the high speed clocks RG, H1–H4, SHP, and SHD are generated. The RG pulse has programmable rising and falling edges and may be inverted using the polarity control. The horizontal clocks H1 and H3 have programmable rising and falling edges and polarity control. The H2 and H4 clocks are always inverses of H1 and H3, respectively. Table II summarizes the high speed timing registers and their parameters.

The edge location registers are six bits wide, but there are only 48 valid edge locations available. Therefore, the register values are mapped into four quadrants, with each quadrant containing 12 edge locations. Table III shows the correct register values for the corresponding edge locations. Figure 6 shows the range and default locations of the high speed clock signals.

1. PIXEL CLOCK PERIOD IS DIVIDED INTO 48 POSITIONS, PROVIDING FINE EDGE RESOLUTION FOR HIGH SPEED CLOCKS. 2. THERE IS A FIXED DELAY FROM THE CLI INPUT TO THE INTERNAL PIXEL PERIOD POSITIONS ( $t_{CLIDLY}$  = 6 ns TYP).

Figure 5. High Speed Clock Programmable Locations

Figure 6. High Speed Clock Default and Programmable Locations

| Register Name | Length | Range              | Description                                                           |

|---------------|--------|--------------------|-----------------------------------------------------------------------|

| POL           | 1b     | High/Low           | Polarity Control for H1, H3, and RG (0 = No Inversion, 1 = Inversion) |

| POSLOC        | 6b     | 0-47 Edge Location | Positive Edge Location for H1, H3, and RG                             |

|               |        |                    | Sample Location for SHP, SHD                                          |

| NEGLOC        | 6b     | 0-47 Edge Location | Negative Edge Location for H1, H3, and RG                             |

| DRV           | 3b     | 0-7 Current Steps  | Drive Current for H1-H4 and RG Outputs (3.5 mA per Step)              |

| Table II. | H1-H4, | RG, SHP | , SHD Timing | Parameters |

|-----------|--------|---------|--------------|------------|

|-----------|--------|---------|--------------|------------|

#### Table III. Precision Timing Edge Locations

| Quadrant | Edge Location (Decimal) | Register Value (Decimal) | Register Value (Binary) |

|----------|-------------------------|--------------------------|-------------------------|

| Ι        | 0 to 11                 | 0 to 11                  | 000000 to 001011        |

| II       | 12 to 23                | 16 to 27                 | 010000 to 011011        |

| III      | 24 to 35                | 32 to 43                 | 100000 to 101011        |

| IV       | 36 to 47                | 48 to 59                 | 110000 to 111011        |

#### H-Driver and RG Outputs

In addition to the programmable timing positions, the AD9848/ AD9849 features on-chip output drivers for the RG and H1–H4 outputs. These drivers are powerful enough to directly drive the CCD inputs. The H-driver current can be adjusted for optimum rise/fall time into a particular load by using the DRV registers. The RG drive current is adjustable using the RGDRV register. Each 3-bit DRV register is adjustable in 3.5 mA increments, with the minimum setting of 0 equal to OFF or three-state, and the maximum setting of 7 equal to 24.5 mA.

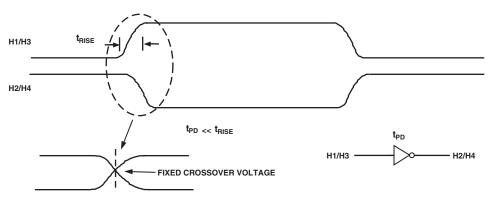

As shown in Figure 7, the H2/H4 outputs are inverses of H1/H3. The internal propagation delay resulting from the signal inversion is less than 1 ns, which is significantly less than the typical rise time driving the CCD load. This results in a H1/H2 crossover voltage at approximately 50% of the output swing. The crossover voltage is not programmable.

#### Digital Data Outputs

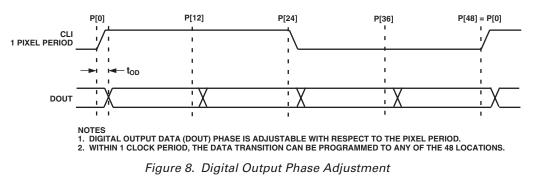

The AD9848/AD9849 data output phase is programmable using the DOUTPHASE register. Any edge from 0 to 47 may be programmed, as shown in Figure 8.

#### HORIZONTAL CLAMPING AND BLANKING

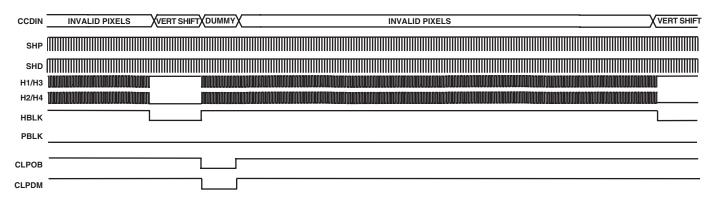

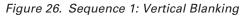

The AD9848/AD9849's horizontal clamping and blanking pulses are fully programmable to suit a variety of applications. As with the vertical timing generation, individual sequences are defined for each signal and are then organized into multiple regions during image readout. This allows the dark pixel clamping and blanking patterns to be changed at each stage of the readout to accommodate different image transfer timing and high speed line shifts.

Figure 7. H-Clock Inverse Phase Relationship

Figure 11. HBLK Masking Control

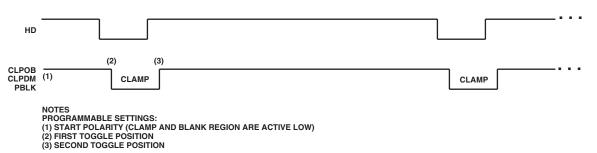

#### Individual CLPOB, CLPDM, PBLK Sequences

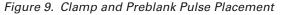

The AFE horizontal timing consists of CLPOB, CLPDM, and PBLK, as shown in Figure 9. These three signals are independently programmed using the registers in Table IV. SPOL is the start polarity for the signal, and TOG1 and TOG2 are the first and second toggle positions of the pulse. All three signals are active low and should be programmed accordingly. Up to four individual sequences can be created for each signal.

#### Individual HBLK Sequences

Downloaded from Elcodis.com electronic components distributor

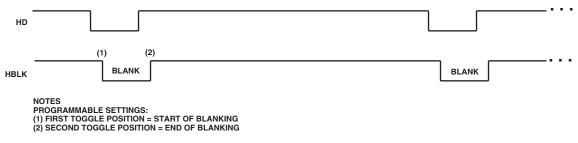

The HBLK programmable timing shown in Figure 10 is similar to CLPOB, CLPDM, and PBLK. However, there is no start polarity control. Only the toggle positions are used to designate the start and the stop positions of the blanking period. Additionally, there is a polarity control HBLKMASK that designates the polarity of the horizontal clock signals H1–H4 during the blanking period. Setting HBLKMASK high will set H1 = H3 = low and

H2 = H4 = high during the blanking, as shown in Figure 11. Up to four individual sequences are available for HBLK.

#### **Horizontal Sequence Control**

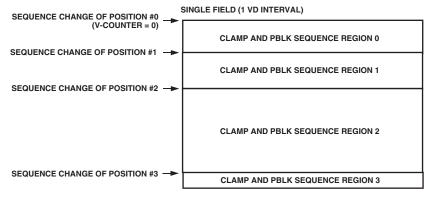

The AD9848/AD9849 uses Sequence Change Positions (SCP) and Sequence Pointers (SPTR) to organize the individual horizontal sequences. Up to four SCPs are available to divide the readout into four separate regions, as shown in Figure 12. The SCP 0 is always hard-coded to line 0, and SCP1–3 are register programmable. During each region bounded by the SCP, the SPTR registers designate which sequence is used by each signal. CLPOB, CLPDM, PBLK, and HBLK each have a separate set of SCP. For example, CLPOBSCP1 will define Region 0 for CLPOB, and in that region any of the four individual CLPOB sequences may be selected with the CLPOBSPTR registers. The next SCP defines a new region and in that region each signal can be assigned to a different individual sequence. The Sequence Control Registers are summarized in Table VI.

UP TO FOUR INDIVIDUAL HORIZONTAL CLAMP AND BLANKING REGIONS MAY BE PROGRAMMED WITHIN A SINGLE FIELD, USING THE SEQUENCE CHANGE POSITIONS.

Figure 12. Clamp and Blanking Sequence Flexibility

| Table IV. | CLPOB.                            | CLPDM.                | PBLK | Individual | Sequence | Parameters       |

|-----------|-----------------------------------|-----------------------|------|------------|----------|------------------|

|           | $o_{\mathbf{D}} \circ \mathbf{D}$ | <b>UIIIIIIIIIIIII</b> |      |            | orquenee | I WI WIII VCVI U |

| Register Name | Length | Range                 | Description                                                      |

|---------------|--------|-----------------------|------------------------------------------------------------------|

| SPOL          | 1b     | High/Low              | Starting Polarity of Clamp and Blanking Pulses for Sequences 0-3 |

| TOG1          | 12b    | 0-4095 Pixel Location | First Toggle Position within the Line for Sequences 0-3          |

| TOG2          | 12b    | 0-4095 Pixel Location | Second Toggle Position within the Line for Sequences 0–3         |

#### Table V. HBLK Individual Sequence Parameters

| Register Name | Length | Range                 | Description                                                                |

|---------------|--------|-----------------------|----------------------------------------------------------------------------|

| HBLKMASK      | 1b     | High/Low              | Masking Polarity for H1 for Sequences $0-3$ ( $0 = H1$ Low, $1 = H1$ High) |

| HBLKTOG1      | 12b    | 0–4095 Pixel Location | First Toggle Position within the Line for Sequences 0–3                    |

| HBLKTOG2      | 12b    | 0-4095 Pixel Location | Second Toggle Position within the Line for Sequences 0–3                   |

#### Table VI. Horizontal Sequence Control Parameters for CLPOB, CLPDM, PBLK, and HBLK

| Register Name | Length | Range               | Description                                      |

|---------------|--------|---------------------|--------------------------------------------------|

| SCP1–SCP3     | 12b    | 0–4095 Line Number  | CLAMP/BLANK SCP to Define Horizontal Regions 0-3 |

| SPTR0-SPTR3   | 2b     | 0–3 Sequence Number | Sequence Pointer for Horizontal Regions 0-3      |

#### **H-Counter Synchronization**

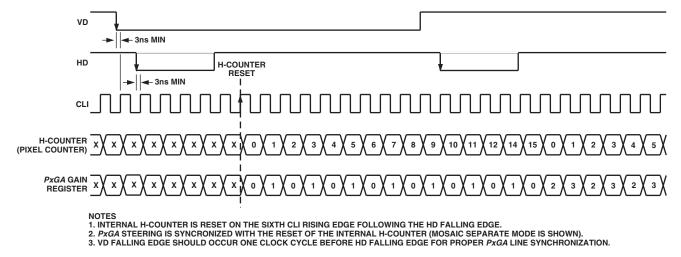

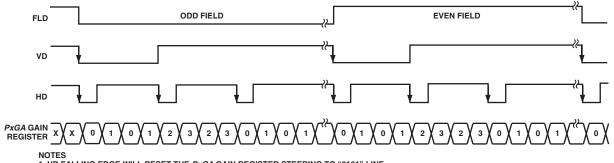

The H-Counter reset occurs on the sixth CLI rising edge following the HD falling edge. The PxGA steering is synchronized with the reset of the internal H-Counter (see Figure 13).

Figure 13. H-Counter Synchronization

#### **POWER-UP PROCEDURE**

Figure 14. Recommended Power-Up Sequence

#### **Recommended Power-Up Sequence**

When the AD9848 and AD9849 are powered up, the following sequence is recommended (refer to Figure 14 for each step).

- 1. Turn on power supplies for AD9848/AD9849.

- 2. Apply the master clock input CLI, VD, and HD.