### World Modem<sup>TM</sup> Secure

### Features

- Self-contained 300 2400 baud modem family

- V.21, V.22, V.23, Bell 103, Bell 212A Error Correction

- Compliant with global regulatory standards

- ✓ Serial host interface

- ∠ Internal UART with HW/SW flow control

- Supports standard alarm protocols

- Caller ID detection and decode

- See Phone Line Snoop and Tamper Detection

- Pin Compatible with all Copeland Communications modem products.

- $\swarrow$  Low power consumption 20mA

- $\swarrow$  Low Power Standby Mode 100uA

- ∠ Small footprint 1.045" X 2.54"

### Applications

- Second Se

- ∠ Point-of-sale terminals

- ∠ Set-top boxes

- ✓ Vending & gaming machines

- ✓ Security Systems

- *«* Remote telemetry and SCADA

- ✓ OEM applications

- Bridge for other CCI products

## Description

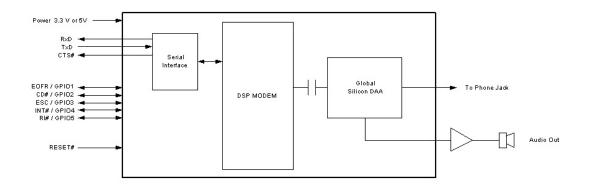

The CC-2401K2 World modem<sup>™</sup> Secure is a compact integrated 2400 baud modem with World Modem<sup>™</sup> compatibility. The modem features a transformer-less DAA meeting global telephone system requirements, no electro-mechanical components and flexible DSP data pump. The modem is user-configurable to meet virtually all global telecom requirements. The modem supports serial host communications via flexible internal UART. The modem conforms to the industry standard World Modem<sup>™</sup> mechanical and interface specifications. Because of its built-in features and flexibility, many applications and OEM products can be created using the World Modem<sup>™</sup> Secure. The World Modem<sup>™</sup> Secure is an ideal modem for world-wide embedded applications due to its flexibility, global compliance, small size, low power consumption and upgradeability. Copeland Communications World modems are software and plug compatible with many other Copeland Communications Socket products. In addition, the CC-2401K2 features include fast connect times for electronics point-of-sale applications and alarm protocols for security systems.

# Table of Contents

| Features                             |

|--------------------------------------|

| Applications                         |

| Description                          |

| Block Diagram                        |

| Serial Interface                     |

| Mechanical Outline                   |

| Features                             |

| Functional Description               |

| Host Interface                       |

| Line Interface                       |

| Command / Data Mode 10               |

| Flow Control 10                      |

| Power Save Modes10                   |

| Global Operation                     |

| Parallel Phone Detection             |

| On-Hook Intrusion Detection          |

| Off-Hook Intrusion Detection         |

| Interrupt Detection                  |

| Loop Current Detection               |

| Loss of Carrier Detection            |

| Overcurrent Detection                |

| Caller ID Monitor/Bellcore Caller ID |

| UK Caller ID                         |

| V.23 Operation / V.23 Reversing      |

| V.42 HDLC Operation                  |

| Fast Connect                         |

| AT Command Set                       |

| Command Line Execution               |

| AT Command Set Description17         |

| Alarm Industry AT Commands           |

| Modem Result Codes and Call Progress |

| Automatic Call Progress Detection    |

| Manual Call Progress Detection       |

| Low Level DSP Control                |

| DSP registers                        |

| Call Progress Filters                |

| CE DECLARATION OF CONFORMITY         |

| Revision Information                 |

| Contact Information                  |

| Warranty                             |

| Legal                                |

Page 2 of 66

# Block Diagram

Page 3 of 66

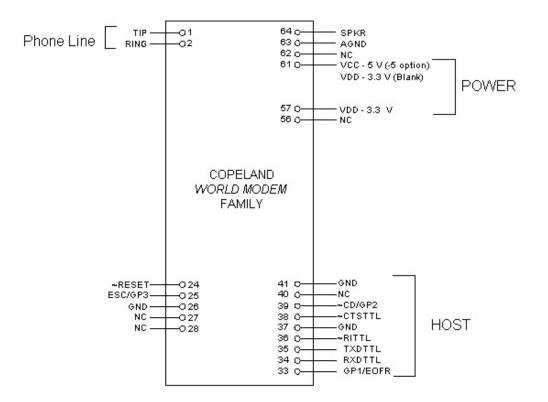

# Serial Interface

The pin out of the serial modem is shown in the figure below.

Note: Signals on pins 24, 25, 33-40 are TTL.

### Serial Host Interface

The host interface control and data signals are 3.3 volts and are 5 volt tolerant. The World modem II modems can be directly connected into 3.3 or 5 volt systems. On 5V models (CC-2401K2-xx5), connect pin 61 to 5V. On 3.3V models, connect Pin 61 to +3.3V.

# WARNING: DO NOT CONNECT PIN 61 TO 5V ON 3.3 VOLT MODELS. NEW World Modem II models do not have pins 56 or 57 populated.

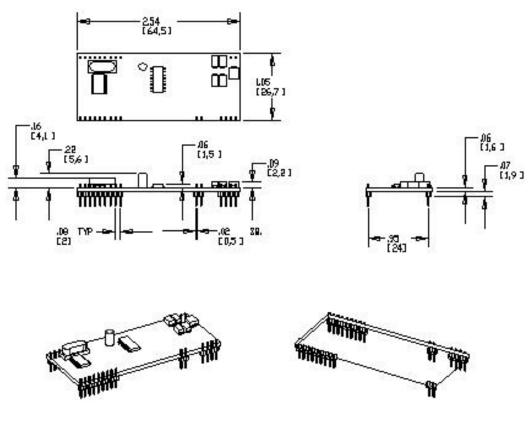

## Mechanical Outline

#### Mechanical

The modem module is on an 0.062 thick FR-4 PC board. The module has two rows of 2mm pins located 24mm on center. The module is designed to plug into 2 mm sockets with the same 24 mm spacing.

Due to the low mass of the board, no retention is required aside from the sockets. A large tie-wrap may be used to insure retention in high shock or vibration environments, if desired.

### **Detailed Specifications**

| Item                     | Specification                                           |  |  |

|--------------------------|---------------------------------------------------------|--|--|

| Data Rate                |                                                         |  |  |

| 2400 bps                 | V.22, V.23, Bell 212A                                   |  |  |

| 1200 bps                 | V.22, V.23, Bell 212A                                   |  |  |

| 300 bps                  | V.21, Bell 103                                          |  |  |

| Data Format              |                                                         |  |  |

| Bit format               | Selectable 8,9, bits per character                      |  |  |

| Compatibility            | V.23, V.22bis, V.21, Bell 212A & Bell 103               |  |  |

| Control                  | AT command set                                          |  |  |

| Host Interface           |                                                         |  |  |

| Serial                   | TTL - 8, 9 bit asynchronous data @ 2400-307200 bps rate |  |  |

| Flow Control             | CTS, DCD, RI                                            |  |  |

| Features                 |                                                         |  |  |

| Caller ID                | Bellcore (US) & ETSI (European)                         |  |  |

| PCM/CODEC                |                                                         |  |  |

| Parallel Phone Detection | On-hook and off-hook detection                          |  |  |

| International Operation  | Via programmable control registers                      |  |  |

| Dialing                  | DTMF & pulse                                            |  |  |

| Power Requirements       |                                                         |  |  |

| Voltage                  | 3.3 V Nominal                                           |  |  |

| Current                  | 3.0V Minimum                                            |  |  |

|                          | 3.6V Maximum                                            |  |  |

|                          | 25 mA Operating Maximum                                 |  |  |

|                          | 100 µA Standby Maximum                                  |  |  |

| Environmental            |                                                         |  |  |

| Temp Range               | Commercial 0C-70C                                       |  |  |

|                          | (contact factory for extended temperature options)      |  |  |

| Compliance               | FCC part 15                                             |  |  |

|                          | FCC part 68                                             |  |  |

|                          | EN55022                                                 |  |  |

|                          | EN55024                                                 |  |  |

|                          | EN61000                                                 |  |  |

|                          | TBR-21                                                  |  |  |

#### **Asynchronous Serial Interface**

The Asynchronous Serial Interface is a complete UART consisting of Receive and Transmit signals as well as CTS, DCD and RI control signals.

The UART is programmable to support a number of baud rates and data formats. Supported data rates and formats are:

Data Bits: 8 Stop Bits: 1 Baud Rates: 300, 1200, 2400 (default), 9600, 19200, 38400, 115200, 307200

Page 6 of 66

#### Status

In addition to flow control, the modem provides two hardware status signals . These signals are multiplexed and may be used as general purpose IO signals:

DCD

RI

**Reset** – A hardware reset is provided to reset the modem controller on power-up or to force the modem back to its default settings. This active low signal has an on-board pull up. Leave this pin unconnected if hardware reset is not needed.

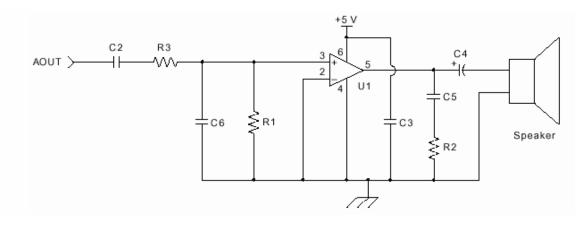

#### Audio Output

The World Modem II modules support an analog (audio) output. This analog signal can be used for call progress monitoring.

#### **Optional Call Progress Monitor**

| ouggeotea component valaco |                          |  |  |  |

|----------------------------|--------------------------|--|--|--|

| Symbol                     | Value                    |  |  |  |

| C2, C3, C5                 | 0.1 μF, 16 V, ±20%       |  |  |  |

| C4                         | 100 µF, 16 V, Elec. ±20% |  |  |  |

| C6                         | 820 pF, 16 V, ±20%       |  |  |  |

| R1                         | 10 k?, 1/10 W, ±5%       |  |  |  |

| R2                         | 10 ?, 1/10 W, ±5%        |  |  |  |

| R3                         | 47 k?, 1/1 W, ±5%        |  |  |  |

| U1                         | LM386                    |  |  |  |

#### **Suggested Component Values**

Page 7 of 66

# **Functional Description**

The CC-2401K2 is a complete modem with integrated DAA that provides a programmable line interface meeting all global telephone line requirements. The modem accepts simple AT commands and provides connect rates up to 2400 baud, full-duplex. The modem supports V.42 hardware support through HDLC framing. To minimize handshake times, the CC-2401K2 can implement a V.22-based fast connect. V.23 reversing protocol and standard alarm formats including SIA are also supported.

The World Modem II family of products is ideal for embedded applications due to its small form factor, low power consumption and global compliance. The CC-2401K2 contains everything necessary to connect to the Public Switched Telephone Network (PTSN). All that is needed is a connector to the local phone line. No external filtering or fusing are required.

The CC-2401K2 is designed for rapid design into existing modem applications. The modem interfaces directly to a microcontroller's UART. The CC-EVAL kit comes with full schematics to help design and a fully functional board to connect to a PC serial port for rapid testing and evaluation.

The modem can be fully programmed to meet international telephone line interface requirements with full compliance to FCC, TBR21, JATE and other country-specific PTT specifications. The CC-2401 is designed to meet worldwide requirements for out-of-band energy, billing-tone immunity, high voltage surges, and safety requirements.

| Configuration | Modulation | Carrier Frequency | Data Rate       | Standard             |

|---------------|------------|-------------------|-----------------|----------------------|

|               |            | (Hz)              | (bps)           | Compliance           |

| V.21          | FSK        | 1080/1750         | 300             | Full                 |

| V.22*         | DPSK       | 1200/2400         | 1200            | Full                 |

| V.22bis*      | QAM        | 1200/2400         | 2400            | No retrain           |

| V.23          | FSK        | 1300/2100         | 1200/75         | Full; plus reversing |

| V.23          | FSK        | 1300/1700         | 600/75          | (Europe)             |

| Bell 103      | FSK        | 1170/2125         | 300             | Full                 |

| Bell 212A     | DPSK       | 1200/2400         | 1200            | Full                 |

| Security      | DTMF       | -                 | 40              | Full                 |

| SIA-Pulse     | Pulse      | -                 | Low             | Full                 |

| SIA Format    | FSK        | 1170/2125         | 300 half-duplex | 300 bps only         |

\* **NOTE:** The CC-2401 only adjusts its DCE rate from 2400 bps to 1200 bps if it is connecting to a V.22-only (1200 bps only modem. Because the V.22bis specification does not outline a fallback procedure, the host should implement a fallback mechanism consisting of hanging up and connecting at a lower baud rate. Retraining to accommodate changes in line conditions that occur during a call must be implemented by terminating the call and redialing.

Page 8 of 66

### **Host Interface**

The host interface is serial TTL. The default host speed of 2400 baud and 8N1 format (8 data bits, no parity bit and 1 stop bit). The defaults can be changes after initialization by using standard AT commands. A true RS-232 interface is available on the World modem Evaluation Board.

To change the serial baud rate, the command ATSE0=xxx where xxx is (a carriage return must follow every command for it to be effected):

| DTE Rate (bps) | SE0[2:0] (SD) |

|----------------|---------------|

| 300            | 000           |

| 1200           | 001           |

| 2400           | 010           |

| 9600           | 011           |

| 19200          | 100           |

| 38400          | 101           |

| 115200         | 110           |

| 307200         | 111           |

As soon as the command is issued, the host must change its baud rate to match the World Modem II's new data rate.

#### Line Interface

The CC-2401 can be configured to any of the Bell and CCITT operation modes listed in table <SC>. In V.22bis, the modem connects at 1200 bps if the other modem is configured for V.22. The CC-2401 also supports S1A and other protocols for the security industry. Contact the factory for other modem configurations.

| Protocol              | Register S07 Value |

|-----------------------|--------------------|

| V.22bis               | 0x06               |

| V.22                  | 0x02               |

| V.21                  | 0x03               |

| Bell 212A             | 0x00               |

| Bell 103              | 0x01               |

| V.23 (1200 tx, 75 rx) | 0x14               |

| V.23 (75 tx, 1200 rx) | 0x24               |

| V.23 (600 tx, 75 rx)  | 0x10               |

| V.23 (75 tx, 600 rx)  | 0x20               |

The CC-2401 does not continuously check for stop bits on the incoming digital data. If the TXD pin is not high, the RXD pin may echo meaningless characters to the host. This requires the UART to flush its receiver FIFO upon initialization.

Page 9 of 66

### **Command / Data Mode**

On Reset, the CC-2401 is in command mode. In this mode, the modem accepts AT commands. Type "ATDT#" (tone dial) to initiate a call once the modem has been initialized. Use ATDP for pulse lines. Every command must be followed by a carriage return. Once a connection is established, the modem responds with "c, "d", or "v" and enter data mode. Once in this mode, the modem will not respond to AT style commands. There are three ways to return to command mode:

- Use the ESC pin. To enable the ESC pin feature, set SE2[5:4) = 11. A positive edge on this pin will return the modem to command mode. To reenter data mode, type "ATO".

- Use 9-bit data mode. If 9-bit data format with escape is configured a 1 detected on bit 9 returns the modem to command mode. To enable this feature, set SE0[3] (ND) = 1 and S15[0] (NBE) = 1. Again, use "ATO" to return to data mode.

- Use "+++". The escape sequence is a sequence of three escape characters that are set in S-register SOF ("+" character is the default escape). If this sequence is seen and the modem detects no activity on the line before or after, the modem will return to command mode.

No matter the escape method, when carrier is lost, the modem will return to command mode and reports "N".

#### Flow Control

Flow control is only needed if the DTE and DCE rate are not the same. If the DTE rate is set higher than the line (DCE), flow control is required to prevent data loss to the transmitter.

To control data flow, the CTS pin is used. When CTS is asserted, the CC-2401 is ready to accept a character. While CTS is negated, no data should be sent to the modem on TXD. To simplify flow control, the CC-2401 has an integrated ten character transmit FIFO and allows for two different CTS reporting methods. By default, the CTS pin is negated as soon as a start bit is detected on the TXD pin and remains negated until the modem is ready to accept another character. Setting SFC7[7]=1 (CTSM), CTS is negated when the FIFO is 70% full and is reasserted when the FIFO is 30% full.

#### **Power Save Modes**

The CC-2401 has three low power modes:

- DSP Power down. The DSP processor can be powered down by setting SEB[3](PDDE) = 1. In this mode, the serial interface still functions and the modem detects ringing and intrusion. No modem modes or tone detection features function.

- Wake on Ring. Issuing ATz command causes the modem into a low power mode where both the controller and DSP are powered down. Only an incoming ring, a low TXD signal, or a total reset will power up the modem again. Return from wake-on-ring triggers the INT pin if S09[6] (WOR) = 1.

- Total Power down. SF1[5] = 1 and SF1[6] = 1 places the modem into total powerdown mode. All logic, including the crystal, is powered down.

Page 10 of 66

### **Global Operation**

The CC-2401 provides a programmable line interface to meet international telephone line requirements. The following table provides the register settings required to meet various country PTT standards.

| Register              | SF5                                                                                        |             |              |               |                | SF6             |              |

|-----------------------|--------------------------------------------------------------------------------------------|-------------|--------------|---------------|----------------|-----------------|--------------|

| Country               | OHS                                                                                        | ILIM        | RZ           | RT            | MINI[1:0]      | DCV[1:0]        | ACT[3:0]     |

| Australia             | 10                                                                                         | 0           | 0            | 0             | 00             | 00              | 0011         |

| Brazil <sup>1</sup>   | 00                                                                                         | 0           | 0            | 0             | 00             | 00              | 0000         |

| TBR21 <sup>2</sup>    | 00                                                                                         | 1           | 0            | 0             | 11             | 11              | 0011         |

| Czech                 | 00                                                                                         | 0           | 0            | 0             | 11             | 11              | 0011         |

| Republic              |                                                                                            |             |              |               |                |                 |              |

| FCC <sup>3</sup>      | 00                                                                                         | 0           | 0            | 0             | 11             | 11              | 0000         |

| Latvia                | 00                                                                                         | 1           | 0            | 0             | 11             | 11              | 0011         |

| Malaysia <sup>4</sup> | 00                                                                                         | 0           | 0            | 0             | 00             | 00              | 0000         |

| New                   | 00                                                                                         | 0           | 0            | 0             | 11             | 11              | 0100         |

| Zealand               |                                                                                            |             |              |               |                |                 |              |

| Nigeria               | 00                                                                                         | 11          | 0            | 0             | 11             | 11              | 0011         |

| Philippines           | 00                                                                                         | 0           | 0            | 0             | 00             | 00              | 0000         |

| Poland,               | 00                                                                                         | 0           | 1            | 1             | 11             | 11              | 0000         |

| Slovenia              |                                                                                            |             |              |               |                |                 |              |

| South Africa          | 10                                                                                         | 0           | 1            | 0             | 11             | 11              | 0000         |

| South Korea           | 00                                                                                         | 00          | 1            | 0             | 11             | 11              | 0000         |

| Notes:                |                                                                                            |             |              |               |                |                 |              |

| 1. Th                 | e following co                                                                             | untries req | uire the sam | e settings as | Brazil: Armen  | ia, China, Egy  | pt, Georgia, |

|                       |                                                                                            |             |              | , Malaysia, N | Aoldova, Oman  | , Pakistan, Qat | ar, Russia,  |

| -                     | ia, Taiwan, Tl                                                                             | ,           |              |               |                |                 |              |

|                       | 0                                                                                          |             | •            | •             | TBR21: Austr   |                 | •            |

|                       | •                                                                                          | •••         |              | · ·           | ean Union, Fin |                 | •            |

|                       | Greece, Guadeloupe, Iceland, Ireland, Israel, Italy, Lebanon, Liechtenstein, Luxembourg,   |             |              |               |                |                 |              |

|                       | Aalta, Martinique, Morocco, Netherlands, Norway, Polynesia (French), Portugal, Reunion,    |             |              |               |                |                 |              |

|                       | bain, Sweden, Switzerland, Turkey, and the United Kingdom.                                 |             |              |               |                |                 |              |

|                       | he following countries require the same settings as FCC: Argentina, Brunei, Canada, Chile, |             |              |               |                |                 |              |

|                       | olumbia, Dubai, Equador, El Salvador, Guam, Hong Kong, Hungary, India, Indonesia,          |             |              |               |                |                 |              |

|                       | vait, Macao, Mexico, Peru, Puerto Rico, Romania, Saudi Arabia, Singapore, Slovakia,        |             |              |               |                |                 |              |

| Tu                    | unisia, UAE, USA, Venezuela, Yemen.                                                        |             |              |               |                |                 |              |

4. Supported for loop current = 20mA.

### **Parallel Phone Detection**

The CC-2401 can detect when another telephone, modem or other device that is using the phone line. This allows the host to avoid interrupting another phone call when the phone line is already in use and to intelligently handle the interruption when the modem is using the phone line.

#### **On-Hook Intrusion Detection**

When the CC-2401 is sharing the telephone line with other devices, it is important that it not interrupt a call in progress. To detect when another device is using a shared telephone line, the host can use the modem to monitor the TIP-RING dc voltage with the LVS[7:0] bits (SDB). This register has a resolution of 1V per bit with an accuracy of about  $\pm 10\%$ . Bits 0 through 6 of the 8 bit signed 2's complement number indicate the line voltage value. Bit 7 indicates the polarity of TIP and RING.

When all devices on the phone line are on-hook, there is no loop current through TIP and RING. Therefore, the voltage is at maximum. On most telephone lines, this is a minimum of 40V. When a device goes off-hook the TIP-RING voltage drops. On most telephone lines, this off-hook voltage is a maximum of 20V.

Page 11 of 66

If the host checks the voltage via LVS before initiating a call (or going off-hook for any reason), the modem can be used to determine if another device is using the telephone line. One way to do this is to verify the voltage in LVS is above a fixed threshold, such as 30V.

#### **Off-Hook Intrusion Detection**

Once a call has begun and the modem is in data mode, the serial port is used for modem data making it difficult for the host to monitor registers. Therefore, when the modem is off-hook, an algorithm is implemented to automatically monitor the TIP-RING loop current via the LCS register (SF3). Because the TIP-RING voltage drops significantly when off-hook, TIP-RING current is a better indicator of another device using the phone line. The LCS[7:0] bits have a resolution of 1.1mA per bit. An LCS register value of 0x00 indicates less than the required loop current is present, and a value of 0xff indicates excessive current draw (> 120mA if ILIM = 0 or > 60mA if ILIM = 1). The user can read these bits directly through the LCS register. Upon detecting an intrusion, an "I" result code is sent to the host if it is in the call negotiation stage or command mode. Otherwise, the modem can be programmed to generate an interrupt to notify the host of the intrusion.

The off-hook intrusion algorithm monitors the value of LCS (SF3) at a sample rate determined by the DGSR (SDF, bits 6:0) register (40 ms units). The algorithm compares each LCS sample to the reference value in the ACL register (S12). If LCS is lower than ACL by an amount greater than DCL (S11, bits 4:0), the algorithm waits for another LCS sample, and if the next LCS sample is also lower than ACL by an amount greater than DCL, an interrupt occurs. This helps the modem avoid a false parallel phone detection (PPD) interrupt due to glitches on the phone line. The ACL is continually updated with the value of LCS as outlined below. The algorithm can be outlined as follows:

$\begin{array}{ll} \mathsf{IF} & \mathsf{LCS}(t) = \mathsf{LCS}(t-40 \mbox{ ms x DGSR}) \\ & \mbox{and} \\ & \mbox{ LCS}(t) - \mathsf{ACL} > \mathsf{DCL} \\ \hline \\ \mathsf{THEN} & & \\ & \mathsf{ACL} = \mathsf{LCS}(t) \\ & \mbox{ IF} & (\mathsf{ACL} - \mathsf{LCS}[t-40 \mbox{ ms x DGSR}]) > \mathsf{DCL}) \\ & \mbox{ and} \\ & & (\mathsf{ACL} - \mathsf{LCS}[t]) > \mathsf{DCL}) \\ \hline \\ \hline \\ \mathsf{THEN} & \mbox{ an intrusion interrupt is sent to the host.} \end{array}$

The off-hook intrusion algorithm does not begin to operate immediately after going off-hook. This avoids accidental interrupts occurring as a result of transients resulting from the modem itself going from on-hook to off-hook. The time delay between the modem going off-hook and the start of the intrusion algorithm is about 1 second. This can be adjusted using the IST register (S82, bits 7:4).

The off-hook intrusion algorithm may also be disabled for a period of time after dialing begins via the IB register (S82, bits 2:1). This avoids triggering an interrupt due to pulse dialing, open-switch intervals or line transients from central office switching. Intrusion can be disabled from the start of dialing to the end of dialing (IB = Dib), from the start of dialing to the timeout of the IS (S29, bits 7:0) by setting IB = 11. The off-hook intrusion algorithm is only suspended (not disabled) during this IB interval and sustains through the end of the interval triggers a PPD interrupt.

#### **Interrupt Detection**

The interrupt pin (pin 55) can be programmed to alert the host of loss-of-carrier, loss-of-phone-line voltage/current, parallel phone detection, and other interrupts listed in the interrupt status mask (S08). After the host receives an interrupt via the INT# pin, the host should issue the AT:I command. This command causes a read-clear of the WOR, PPD, NLD, RI, OCD, and REV bits of the S09 register and raises (deactivates) the INT# pin. All the interrupt status bits in the register S09 remain high after being set until cleared by the AT:I command.

#### Loop Current Detection

The CC-2401 can monitor the loss of loop current. This feature can be enabled by setting S08[4] (NLDM) = 1. This feature is disabled by default. If the loop current is too low for normal DAA operation, S09[4] (NLD) is set.

Page 12 of 66

During this event, if the NLR result code is enabled by setting S62[1](NLR) = 1, the "I" result code is sent. Once the loop current returns to a normal current state, the "L" result code is sent. The INT# pin is also asserted if enabled.

#### Loss of Carrier Detection

The CC-2401 has two methods of implementing a loss of carrier function. If GPIO4 is programmed as INT# and if S08[7](CDM)=1, INT# asserts in data mode when a loss of carrier is detected. The carrier detect function may also be implemented on GPIO2 by setting SE2[3:2] (GPIO2) = 01 and SOC[7](CDE) = 1.

#### **Overcurrent Detection**

The CC-2401 begins monitoring for an overcurrent condition at a programmable time set by S32 (OCDT) after going off-hook (default = 20ms). If an overcurrent condition is detected, the CC-2401 sets S09[1] interrupt status. As long as GPIO4 is programmed as INT and the overcurrent mask bit is enabled by setting S08[1](OCDM) = 1, INT asserts during an overcurrent situation. The host may then check S09[1] (OCD) via the AT:I command to confirm that an overcurrent condition occurred.

#### Caller ID Monitor/Bellcore Caller ID

The CC-2401 continuously monitors the phone line for the caller ID mark signals. This can be useful in systems that require detection of caller ID data before the ring signal, voice mail indicator signals and Type II caller ID monitor support. To force the CC-2401 into caller ID monitor mode, set SOC[6:5] (CIDM) = 11.

**NOTE:** CIDM should be disabled before going off-hook.

#### UK Caller ID

The CC-2401 starts searching for the Idle State Tone Alert Signal. When this signal has been detected, the modem transmits an "a" to the host. After the Idle State Tone Alert Signal is completed, the modem applies the wetting pulse for the required 15 ms by quickly going off-hook and on-hook. From this point on, the algorithm is identical to that of Bellcore in that it searches for the channel seizure signal and the marks before echoing an "m" and then reports the decoded caller ID data.

#### V.23 Operation / V.23 Reversing

The CC-2401 supports full V.23 operation including the V.23 reversing procedure. V.23 operation is enabled by setting S07 (MF1) =  $xx10xx00_b$  of  $xx01xx00_b$ . If S07[5] (V23R) = 1, the CC-2401 receives data at 75 bps and receives data at 600 or 1200 bps. If S07[4] (V23T) = 1, the CC-2401 Receives data at 75 bps and transmits data at 600 or 1200 bps. S07[2] (BAUD) is the 1200 or 600 bps indicator. BAUD = 1 b enables the 1200/600 V.23 channel to run at 1200 bps, while BAUD = 0b enables 600 bps operation.

When a V.23 connection is established, the modem responds with a "c" if the connection is made with the modem transmitting at 1200/600 bps and receiving at 75 bps. The modem responds with a "v" character if a V.23 connection is established with the modem transmitting at 75 bps and receiving at 1200/600 bps.

The CC-2401 supports V.23 turnaround procedure, allowing a modem that is transmitting at 75 bps to initiate a "turnaround" procedure so it can begin transmitting data at 1200/600 bps and receiving data at 75 bps. The modem is defined as being in V.23 master mode if it is transmitting at 75 bps and as being in slave mode if it is transmitting at 1200/600 bps.

#### Modem in Master Mode

To perform a direct turnaround once a modem connection is established, the master host goes into online command mode by sending an escape command (Escape pin activation, TIES, or ninth bit escape) to the master modem.

**NOTE**: The host can initiate a turnaround only if the CC-2401 is the master.

Page 13 of 66

The host then sends the ATRO command to the CC-2401 to initiate a V.23 turnaround and return to online data mode.

The CC-2401 then changes its carrier frequency from 390 Hz to 1300 Hz) and wait to detect a 390 Hz carrier for 440 ms. If the modem detects more than 40 ms of a 390 Hz carrier in a time window of 440 ms, it echoes the "c" response. If the modem does not detect more than 40 ms of a 390 Hz carrier in a time window of 440 ms, it hangs up and echoes the "N" (no carrier) character as a response.

#### Modem in Slave Mode

Enable Slave mode by configuring GPIO4 and INT# (SE2[7:6][GPIO4] = 11). The CC-2401 performs a reverse turnaround when it detects a carrier drop longer than 20 ms. The CC-2401 then reverses and waits to detect a 1300 Hz carrier for 400 ms. If the CC-2401 detects more than 40 ms of a 1300 Hz carrier in a time window of 400 ms, it sets the S09[7] bit and the next character echoed by the CC-2401 is a "v".

If the CC-2401 doe not detect more than 40 ms of the 1300 Hz carrier in a time window of 400 ms, it reverses again and waits to detect a 390 Hz carrier for 440 ms. Then if the CC-2401 detects more than 40 ms of a 390 Hz carrier in a time window of 220 ms, it sets the S09[7] bit, and the CC-2401 echoes a "c".

At this point, if the CC-2401 does not detect more than 40 ms of the 390 Hz carrier in a time window of 440 ms, it hangs up, sets the S09[7] bit, and the CC-2401 echoes a "N" (no carrier).

Successful completion of a turnaround procedure in master or slave mode automatically updates S07[4](V23T) and S07[5] (V23R) to indicate the new status of the V.23 connection.

To avoid using the INT# pin, the host may also be notified of the INT# condition using the 9-bit data mode. Setting S15[0] (NBE) = 1 and S0C[3] (9BF) =  $0_b$  configures the ninth bit on the CC-2401 TXD path to function exactly as the INT# pin has been described.

#### V.42 HDLC Operation

The CC-2401 supports V.42 through hardware HDLC framing in all modem data modes. Frame packing and unpacking including opening and closing flag generation and detection, CRC computation and checking, zero insertion and deletion, and modem data transmission and reception are all performed by the CC-2401. V.42 error correction and V.42bis data compression must be performed by the host.

The digital link interface in this mode uses the same UART interface (8-bit data mode and 9-bit data formats) as in the asynchronous modes, and the ninth data bit may be used as an escape by setting S15[0](NBE) = 1. When using HDLC in 9-bit data mode, if the ninth bit is not used as an escape, it is ignored.

To use the HDLC feature on the CC-2401, the host must enable HDLC operation by setting S13[1](HDEN) = 1. The host may initiate the call or answer the call using either the "ATDT#", the "ATA" command or the auto answer mode. Auto answer mode is implemented by setting register S00 (NR) to a non-zero value. When the call is connected, a "c", "d" or a "v" result is echoed to the host controller. The host may now send and receive data across the UART using either the 8 or 9 bit data formats with flow control.

Once in this state, the CC-2401 begins framing data into the HDLC format. On the transmit side, if no data is available from the host, the HDLC flag pattern is sent repeatedly. When data is available, the CC-2401 computes the CRC code throughout the frame, and the data is sent with the HDLC zero-bit insertion algorithm.

HDLC flow control operates in a similar manner to normal asynchronous flow control across the UART. To operate flow control using the CTS pin to indicate when the CC-2401 is ready to accept a character, a DTE rate higher than the line rate should be selected. The method of transmitting HDLC frames is as follows:

1. After the call is connected, the host should begin sending the frame data to the CC-2401 using the CTS# flow control to ensure data synchronicity.

Page 14 of 66

**Data Sheet**

- 2. When the frame is complete, the host should simply stop sending data to the CC-2401. Since the CC-2401 does not yet recognize the end of frame, it expects an extra byte and asserts CTS. If CTS is used to cause a host interrupt, this final interrupt should be ignored by the host.

- 3. When the CC-2401 is ready to send the next byte, if it has not yet received any data from the host, it recognizes this as an end of frame, raises CTS, calculates the final CRC code, transmits the code and begins transmitting stop flags.

- 4. After transmitting the first stop flag, the CC-2401 lowers CTS indicating that it is ready to receive the next frame from the host. At this point, the process begins again at step 1.

The method for receiving HDLC frames follows:

- After the call is connected, the CC-2401 searches for flag data. Once the first non flag word is detected, the CRC is continuously computed and the data is sent across the UART to the host after removing the HDLC zero-bit insertion. The DTE rate of the host must be at least as high as that of data transmission. HDLC mode only works with 8 bit data words; the ninth bit is used only for escape on TXD and end of frame received (EOFR) on RXD.

- 2. When the CC-2401 detects the stop flag, it sends the last data word in the frame as well as the two CRC bytes and determine if the CRC checksum matches. Thus, the last two bytes are not frame data but are the CRC bytes, which can be discarded by the host. If the checksum matches, the CC-2401 sends "G" (good). If the checksum does not match, the CC-2401 sends "e" (error). In addition, if the CC-2401 detects an abort (seven or more contiguous ones), it sends an "A". When the "G", "e", or "A" (referred to as a frame result word) is sent, the CC-2401 raises the EOFR (end of frame receive) pin. The GPIO1 pin must be configured as EOFR by setting SE4[3](GPE) = 1. In addition to using the EOFR pin to indicate that the byte is a frame result word, if in 9 bit data mode, (set S15[0] (NBE) = 1), the ninth bit is raised if the byte is a frame result word. To program this mode, set S0C[3] (9BF) = 1 and SE0[3] (ND) = 1.

- 3. When the next frame of data is detected, EOFR is lowered and the process repeats with step 1.

When receiving HDLC frames, the host begins receiving data asynchronously from the CC-2401. When each byte is received, the host should check the EOFR pin (or the ninth data bit). If the EOFR pin (or ninth data bit) is low, the data is valid frame data. If the EOFR pin (or ninth bit) is high, the data is a frame result word.

#### Fast Connect

In modem applications that require fast connection times, it is possible to reduce the length of the handshake. Additional modem handshaking control can be adjusted through the registers shown in the following table. These registers are most useful if the user has control of both the originating and answering modems. When the fast connect settings are used, there may be unintended data received initially. The host must tolerate these bytes.

| Register | Name | Function                              | Units        | Default | Fast    |

|----------|------|---------------------------------------|--------------|---------|---------|

|          |      |                                       |              |         | Connect |

| S1E      | TATL | Transmit Answer Tone Length           | 1 s          | 0x03    | 00      |

| S1F      | ATTD | Answer Ton to Transmit Delay          | 5/3 ms       | 0x2D    | 00      |

| S20      | UNL  | Unscrambled Ones Length-V.22          | 5/3 ms       | 0x5D    | 00      |

| S21      | TSOD | Transmit Scrambled Ones Delay – V.22  | 53.3 ms      | 0x09    | 00      |

| S22      | TSOL | Transmit Scrambled Ones Length – V.22 | 5/3 ms       | 0xA2    | 00      |

| S23      | VDDL | V.22/22b Data Delay Low               | 5/3 ms       | 0xCB    | 00      |

| S24      | VDDH | V.22/22b Data Delay High              | (256) 5/3 ms | 0x08    | 00      |

| S34      | TASL | Answer Tone Length                    | 5/3 ms       | 0x5A    | F0      |

|          |      | (only used in S1E[TATL] = 0x00)       |              |         |         |

| S35      | RSOL | Receive V.22 Scrambled Ones Length    | 5/3 ms       | 0xA2    | 00      |

Page 15 of 66

# AT Command Set

The CC-2401 provides several vital functions including AT command parsing, DAA control, connect sequence control, DCE protocol control, intrusion detection, parallel phone off-hook detection, escape control, caller ID control and formatting, ring detect, DTMF control, call progress monitoring, and HDLC framing. The controller uses AT (Attention) commands and S-Registers to configure and control the modem.

The modem has two modes of operation: Command mode and data mode. The CC-2401 is asynchronous in both modes. At power up, after a reset, before a connection to another modem is made, after a connection is dropped (hang up or lost) and during an escape sequence out of data mode (ESC pin, "+++" or other break), the modem is in command mode.

The CC-2401 supports a subset of the typical modem AT command set since it is intended for use with a dedicated microcontroller instead of general terminal applications. AT commands begin with the letters "AT" and are followed directly (no space) by the command. All commands are case sensitive. All AT commands must be entered in upper case including AT. The exceptions are w, r, m, q and z (wakeup on ring).

AT commands can be divided into two groups: Control commands and configuration commands. Control commands, such as ATD, cause the modem to perform an action. The value of this type of command is changed at a particular time to perform a particular action.

Configuration commands change modem characteristics until they are modified or reversed by a subsequent configuration command or the modem is reset. Modem configuration status can be determined with the use of "ATSR?" (followed by a carriage return), where "R" is the two character hexadecimal address of an S-register.

A command line is defined as a string of characters starting with "AT" and ending with an end of line character <CR> (13 decimal). Command lines may contain several commands one after the other. If there are no characters between "AT" and <CR>, the modem responds with a "O" after the carriage return.

### **Command Line Execution**

The characters in a command line are executed one at a time. Unexpected command characters are ignored, but unexpected data characters may be interpreted incorrectly.

After the modem has executed a command line, the result code corresponding to the last command executed is returned to the terminal or host. To echo command line characters, set the CC-2401 to echo mode using the E1 command. All numeric arguments, including the address and value of an S-register, are in hexadecimal format and two digits must always be entered.

#### <CR> End Of Line Character

This character is typed to end a command line. The value of the <CR> character is 13 decimal (the ASCII carriage return character). When the modem detects the carriage return, it executes the commands in the command line.

Note: Commands that do not require a response are executed immediately and do not need a <CR>.

| Command | Function                                |  |  |  |

|---------|-----------------------------------------|--|--|--|

| A       | Answer line immediately with modem      |  |  |  |

| DT#     | Tone dial number                        |  |  |  |

| DP#     | Pulse dial number                       |  |  |  |

| E       | Local echo on/off                       |  |  |  |

| H0      | Go on hook (hang up)                    |  |  |  |

| H1      | Go off hook                             |  |  |  |

| 1       | Chip revision                           |  |  |  |

| :1      | Interrupt read and clear                |  |  |  |

| Μ       | Speaker control options                 |  |  |  |

| 0       | Return online                           |  |  |  |

| RO      | V.23 reverse                            |  |  |  |

| S       | Read/write S-Registers                  |  |  |  |

| w##     | Write S-Register in binary              |  |  |  |

| r#      | Read S-Register in binary               |  |  |  |

| m#      | Monitor S-Register in binary            |  |  |  |

| q#      | Read S-Register in binary               |  |  |  |

| VO      | Result code with no carriage return     |  |  |  |

| V1      | Result code with added carriage returns |  |  |  |

| Z       | Software reset                          |  |  |  |

| Z       | Wakeup on ring                          |  |  |  |

#### **AT Command Set Description**

#### A Answer

The "A" command makes the modem go off hook and respond to an incoming call. This command is to be executed after the CC-2401 has indicated a ring has occurred. The modem indicates an incoming ring by sending an "R" to the UART.

This command is aborted if any other character is transmitted to the modem before the answer process is completed. Auto answer mode is entered by setting S00 (NR) to a non-zero value. NR indicates the number of rings before answering the line. After answering, the modem communicates by whatever protocol has been determined via the modem control registers in S07 (MF1). If no transmit charier signal is received from the calling modem within the time specified in S39 (CDT), the modem hangs up and enters the idle state.

#### D Dial

#### DT# Tone Dial Number

#### DP# Pulse Dial Number

The D commands cause the modem to dial the specified telephone number in the string following the command. The ATH1 command can be used to go off hook without detecting a dial tone or dialing.

The dial string must contain only the digits "0-9, "\*", "#", "A", "B", "C", "D", or the modifiers ";", "/", or ",". A "," causes a two second delay (added to the spacing value in S04) in dialing. "/" causes a 125 ms delay in dialing (added to the spacing value in S04). The ";" returns the device to command mode after dialing and must be the last character.

If any character is received by the CC-2401 between the ATDT#<CR> command and when the connection is made ("c" or "d" is echoed), the extra character is interpreted as an abort and the CC-2401 returns to command mode ready to accept AT commands. A line feed character immediately following the <CR> is treated as an extra character and aborts the call.

If the modem does not have to dial (ATDT<CR> with no dial string), the modem assumes the call was manually established and attempts to make a connection.

#### Automatic Tone/Pulse Dialing

The CC-2401 can be configured to attempt DTMF dialing and automatically revert to pulse dialing if it determines that the line is not DTMF-capable.

Page 17 of 66

For example, using 12345 as the number to be dialed, it is normally accomplished through either the ATDT12345 or ATDP12345 command. In the force pulse dialing mode of operation, the following string should be issued:

#### ATDT1,p12345

If the result code is a "t", the dialing was accomplished using DTMF dialing. If the result code is "tt", the dialing was accomplished using pulse dialing.

In the above example, the CC-2401 dials the first digit "1" using DTMF. The "," is used to pause in order to ensure that the central office has had time to accept the DTMF digit "1". When the CC-2401 processes the "p" command, it attempts to detect a dial tone. If a dial tone is detected, the DTMF digit "1" was not effective, hence, the line does not support DTMF dialing. Conversely, if the dial tone is not detected, the DTMF digit "1" was effective, and the line supports DTMF dialing. The character after the "p" may or may not be dialed depending on whether the DTMF digit "1" was effective or not. If the "1" was effective, the character after the "p" is skipped. The next DTMF digit to be dialed is "2". Subsequent digits are all DTMF. If the "1" was not effective, the first character after the "p" (the "1") is pulse dialed, and subsequent digits are all pulse dialed.

#### E Command Line Echo

Tells the CC-2401 whether or not to echo characters sent from the terminal.

E0 Does not echo characters sent from the terminal E1

Echoes characters sent from the terminal.

#### H0 Hangup

Hang up and go into command mode.

#### H1 Off hook

Go off hook.

#### I Chip Identification

This command returns the chip revision code of the chipset. (A, B, C, etc).

#### **I**6

Displays the modem model number "2401"

#### :I Interrupt Read

Reports the contents of the interrupt status register (S09). The WOR, PPD, NLD, RI, OCD and REV bits are also cleared and the INT pin is deactivated.

#### M Speaker On/Off Options

These options are used to control the AOUT pin for use with a speaker.

M0

Speaker always off.

M1

Speaker on until carrier established.

M2

Speaker always on.

M3

Speaker on after last digit dialed, off at carrier detect.

#### **O** Return to Online Mode

This command returns the modem to online mode. It is used to return to data mode after an escape sequence to resume communications with the remote modem.

#### **RO Turn-Around**

This command initiates a V.23 "direct turnaround" sequence and returns online.

Page 18 of 66

#### S **Register Control**

#### SR=N

Writes an S-register. This command writes the value "N" to the S-register specified by "R". "R" is a hexadecimal number and "N" must also be a hexadecimal number from 00-FF. This command does not wait for a carriage return <CR> before taking effect. Two digits must always be entered for both "R" and "N".

#### SR?

Read an S-register. This command causes the CC-2401 to return the value of the S-register specified by R in hex format. R must be a hexadecimal number. Two digits must always be entered for "R".

#### w## Write S-Register in Binary

This command writes a register in binary format. The first byte following the "w" is the address in binary format and the second byte is the data in binary format. This is a faster method to write registers than the "SR=N" command and is recommended for use by a host controller.

#### r# **Read S-Register in Binary**

This command reads a register in binary format. The byte following the "r" is the address in binary format. The modem returns the contents of this register in binary format. This is a faster method to read registers than the "SR?" command and is recommended for use by a host controller.

#### **Monitor S-Register in Binary** rm#

This command monitors a register in binary format. The byte following the "m" is the address in binary. The CC-2401 constantly transmits the contents of the register at the set baud rate until a new byte is transmitted to the device. The new byte is ignored and viewed as a stop command. The modem result codes should be disabled before using this command.

**q# Read S-Register in Binary** This command is the same as the r# command. The response from the CC-2401 is formatted as 0x55 followed by the contents of the register in binary. This guarantees that the register contents are always preceded by 0x66 and allows the result codes to remain enabled.

#### V **Result Code Options**

V0

Result codes reported according to Table 14. <SC>

V1

Result codes reported with an additional carriage return and line feeds (default).

#### Ζ Software Reset

This command initiates a software reset causing all registers, except E0 to default to their powerup value.

#### Wakeup on Ring (lower case "z")

The CC-2401 enters a low power mode. In this mode, only the line side of the modem is functional. An incoming ring signal or line transient causes the modem to power up and send a "R" to the UART. Any other character received on the RXD pin also causes the modem to exit the wakeup on ring state. Return from wake on ring cal also be set to trigger the INT# pin by setting S08[6] (WORM) = 1.

#### **Alarm Industry AT Commands**

The CC-2401 supports a complete set of commands necessary for making connections in security industry systems. The CC-2401 is configurable in two modes for these applications. The first mode uses DTMF messaging and is selected with the "!1" command. The second mode uses FSK transmit with a tone acknowledgement and is selected by "!2".

The following are a few general comments about the use of "!" commands. Specific details for each command are given below. The first instance of the "!" must be on the same line as the ATDT or ATDP command. DRT must be set to data mode (SE4[5:4](DRT) =  $0_b$ ) before attempting to send tones after a "!" command. The three data-mode escape sequence ("+++", "escape" pin and "ninth-bit") only function in "!2" mode. However,

Page 19 of 66

using the "+++" or "ninth-bit" is not recommended because characters could be sent to and misinterpreted by the remote modem. Only the "escape pin" <SC> is recommended for use in the "!2" mode. The "!1" mode has a special escape provision described below. The AT commands for Alarm Industry applications are described in the following table.

| Command | Function                                     |

|---------|----------------------------------------------|

| !1      | Dial and switch to DTMF security mode        |

| !2      | Dial and switch to "SIA Format"              |

| X1      | SIA half-duplex mode search                  |

| X2      | SIA half-duplex return online as transmitter |

| X3      | SIA half-duplex return online as receiver    |

#### !1

Dial number and follow the DTMF security protocol. The format for this command is as follows:

ATDT<phone number>!1<message 1><CR> K !<message 2><CR> K !<message 3><CR> K K !<message n><CR>

The modem dials the phone number and returns "r" (ring), "b" (busy), and "c" (connect) as appropriate. "c" returns only after the modem detects the Handshake Tone. After a 250 ms delay, the modem sends the DTMF tones containing the first message data and listens for a Kissoff Tone. If a Kissoff Tone shorter than or equal to the value stored in S36(KTL)(default = 1 second) is detected, the CC-2401 echoes a "K". A "k" is sent if the length of the Kissoff Tone is longer than the S36(KTL) value. The controller can then send the next message. All messages must be preceded by a "!" and followed by a <CR> and received by the CC-2401 within 250 ms after the "K" is echoed. Setting S0C[0](MCH) = 1 causes a "." to be echoed when the DTMF tone is turned on and a "/" character to be echoed when the DTMF tone is turned off. This helps the host monitor the status of the message being sent. The previous message can be resent if the host responds with a "-" after the CC-2401 echoes a "K". Any character other than a "!" or a "~" sent to the modem immediately after the "K" causes the modem to escape to the command mode and remain off hook. Any character except "!" and "~" sent during the transmission of a message causes the message to be aborted and the modem to return to command mode.

If the Kissoff Tone is not received within 1.25 seconds, the modem echoes a " $^{n}$ ". A " $_{n}$ " from the host causes the last message to be resent. Any character other than a "!" or a " $_{n}$ " sent to the modem immediately after the " $^{n}$ " causes the modem to escape to command mode and remain off hook.

#### !2

Dial the number and follow the "SIA Format" protocol for Alarm System Communications.

The modem dials the phone number and echoes "r" (ring), "b" (busy), and "c" (connect) as appropriate. "c" echoes only after the CC-2401 detects the Handshake Tone and the speed synchronization signal is sent. The signaling is at 300 bps, half-duplex FSK. The host can send the first SIA block after the "c" is received. Once the block is transmitted, the modem can monitor for the acknowledge tone by completing the following sequence:

- 1. Place the CC-2501 in command mode by pulsing the ESCAPE pin. The "+++" and "hinth-bit" escape modes operate in the "!2" mode but are not recommended because they can send unwanted characters to the remote modem.

- 2. Issue the "ATX1" command to turn the modem transmitter off and begin monitoring for the acknowledgement tones.

- 3. Monitor for a positive (negative) acknowledgement "P" ("N") after the tone has been detected for at least 400 ms.

Page 20 of 66

4. The modem, still in command mode, can be placed online as a transmitter by issuing the "ATX2" command or a receiver by issuing the "ATX3" command. If tonal acknowledgement is not used, the host can toggle the ESCAPE pin to place the CC-2401 in command mode and issue an "ATX2" or an "ATX3" command to reverse data direction.

This sequence can be repeated for long messages.

### Modem Result Codes and Call Progress

The following table shows the modem result codes that can be used in call progress monitoring. All result codes are a single character to speed up communication and ease host processing.

| Command  | Function                                    |

|----------|---------------------------------------------|

| а        | British Telecom Caller ID Idle Tone Alert   |

|          | Detected                                    |

| b        | Busy Tone Detected                          |

| С        | Connect                                     |

| d        | Connect 1200 bps (when programmed as        |

|          | V.22bis modem)                              |

| f        | Hookswitch Flash or Battery Reversal        |

|          | Detected                                    |

| Н        | Modem Automatically Hanging Up in !2, !1.   |

| 1        | Intrusion Completed (parallel phone back on |

|          | hook)                                       |

| i        | Intrusion Detected (parallel phone off hook |

|          | and on the line)                            |

| K        | Kissoff Tone Detected                       |

| k        | Contact ID Kissoff Tone too long (!1)       |

| L        | Phone Line Detected                         |

| <u> </u> | No Phone Line Detected                      |

| m        | Caller ID Mark Signal Detected              |

| N        | No Carrier Detected                         |

| n        | No Dial tone (time-out set by CW[S02])      |

| 0        | Modem OK Response                           |

| R        | Incoming Ring Signal Detected               |

| r        | Ringback Tone Detected                      |

| t        | Dial Tone                                   |

| V        | Connect 75 bps TX (V.23 originate only)     |

| х        | Overcurrent State Detected After and Off    |

|          | Hook Event                                  |

| ^        | Kissoff tone detection required             |

|          | Dialing Complete                            |

#### **Automatic Call Progress Detection**

The CC-2401 has the ability to detect dial, busy and ringback tones automatically. The following is a description of the algorithms that have been implemented for these three tones.

- Dial Tone. The dial tone detector looks for a dial tone after going off hook and before dialing is initiated. This can be bypassed by enabling blind dialing (set S07[6](BD) = 1). After going off hook, the modem waits the number of seconds in S01 (DW) before searching for the dial tone. In order for a dial tone to be detected, it must be present for the length of time programmed in S1C (DTT). Once the dial tone is detected, dialing commences. If a dial tone is not detected within the time programmed in S02 (CW), the CC-2401 hangs up and returns an "n" to the user.

- **Busy/Ringback Tone**. After dialing is completed, the CC-2401 monitors for Busy/Ringback and modem answer tones. The busy and ringback tone detectors both use the call progress energy detector. The registers that set the cadence for busy and ringback are listed in the following table.

Page 21 of 66

| Register | Name | Function                 | Units     |

|----------|------|--------------------------|-----------|

| S16      | BTON | Busy tone on time        | 10 ms     |

| S17      | BTOF | Busy tone off time       | 10 ms     |

| S18      | BTOD | Busy tone delta time     | 10 ms     |

| S19      | RTON | Ringback tone on time    | 53.333 ms |

| S1A      | RTOF | Ringback tone off time   | 53.333 ms |

| S1B      | RTOD | Ringback tone Delta time | 53.333 ms |

#### **Manual Call Progress Detection**

Because other call progress tones beyond those described above may exist, the CC-2401 supports manual call progress. This requires the host to read and write the low-level DSP registers and may require realtime control by the host. Manual call progress may be required for detection of application specific ringback, dial tone and busy signals. The section on DSP level control should be read before attempting manual call progress detection.

The call progress biquad filters can be programmed to have a custom frequency response and detection level.

Four dedicated user defined frequency detectors can be programmed to search for individual tones. The four detectors have center frequencies that can be set by registers UDFD1-4. SE5[6][TDET] [SE8 = 0x02] Read Only Definition can be monitored, along with TONE, to detect energy at these user defined frequencies. The default trip-threshold for UDFD1-4 is -43 dBm but can be modified with register UDFSL.

By issuing the "ATDT;" command, the modem goes off hook and returns to command mode. The user can then put the DSP into call progress monitoring by first setting SE8 = 0x02. Next, set Se5(DSP2) = 0x00 so no tones are transmitted, and set SE6 (DSP3) to the appropriate code, depending on which types of tones are to be detected.

Page 22 of 66

#### **Global Ringer and Busy Tone Cadence Settings**

| Country                                                         | RTON | RTOF | RTOD | BTON | BTOF | STOD |

|-----------------------------------------------------------------|------|------|------|------|------|------|

| _                                                               | S18  | S1A  | S1B  | S16  | S17  | S18  |

| Australia                                                       | 0x07 | 0x03 | 0x01 | 0x25 | 0x25 | 0x04 |

| Austria                                                         | 0x12 | 0x5D | 0x0A | 0x1E | 0x1E | 0x03 |

| Belgium                                                         | 0x12 | 0x38 | 0x06 | 0x32 | 0x32 | 0x05 |

| Brazil                                                          | 0x12 | 0x4B | 0x08 | 0x19 | 0x19 | 0x03 |

| Bulgaria                                                        | 0x12 | 0x4B | 0x08 | 0x14 | 0x32 | 0x05 |

| China                                                           | 0x12 | 0x4B | 0x08 | 0x23 | 0x23 | 0x04 |

| Cyprus                                                          | 0x1C | 0x38 | 0x06 | 0x32 | 0x32 | 0x05 |

| Czech Republic                                                  | 0x12 | 0x4B | 0x08 | 0x18 | 0x24 | 0x0A |

| Denmark                                                         | 0x0E | 0x8C | 0x0F | 0x19 | 0x19 | 0x03 |

| Finland                                                         | 0x0E | 0x5D | 0x0A | 0x1E | 0x1E | 0x03 |

| France                                                          | 0x1C | 0x41 | 0x07 | 0x32 | 0x32 | 0x05 |

| Germany                                                         | 0x12 | 0x4B | 0x08 | 0x32 | 0x32 | 0x05 |

| Great Britain                                                   | 0x07 | 0x03 | 0x01 | 0x25 | 0x25 | 0x04 |

| Greece                                                          | 0x12 | 0x4B | 0x08 | 0x1E | 0x1E | 0x03 |

| Hong Kong, New Zealand                                          | 0x07 | 0x03 | 0x01 | 0x32 | 0x32 | 0x05 |

| Hungary                                                         | 0x17 | 0x46 | 0x0F | 0x1E | 0x1E | 0x03 |

| Iceland                                                         | 0x16 | 0x58 | 0x09 | 0x19 | 0x19 | 0x03 |

| India                                                           | 0x07 | 0x03 | 0x01 | 0x4B | 0x4B | 0x08 |

| Ireland                                                         | 0x07 | 0x03 | 0x01 | 0x32 | 0x32 | 0x05 |

| Italy, Netherlands,<br>Norway, Thailand,<br>Switzerland, Israel | 0x12 | 0x4B | 0x08 | 0x32 | 0x32 | 0x05 |

| Japan, Korea                                                    | 0x12 | 0x25 | 0x04 | 0x32 | 0x32 | 0x05 |

| Luxembourg                                                      | 0x12 | 0x4B | 0x08 | 0x30 | 0x30 | 0x05 |

| Malaysia                                                        | 0x07 | 0x03 | 0x01 | 0x23 | 0x41 | 0x07 |

| Malta                                                           | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 |

| Mexico                                                          | 0x12 | 0x4B | 0x08 | 0x19 | 0x19 | 0x03 |

| Poland                                                          | 0x12 | 0x4B | 0x10 | 0x32 | 0x32 | 0x05 |

| Portugal                                                        | 0x12 | 0x5D | 0x0A | 0x32 | 0x32 | 0x05 |

| Singapore                                                       | 0x07 | 0x03 | 0x01 | 0x4B | 0x4B | 0x08 |

| Spain                                                           | 0x1C | 0x38 | 0x06 | 0x14 | 0x14 | 0x02 |

| Sweden                                                          | 0x12 | 0x5D | 0x0A | 0x19 | 0x19 | 0x03 |

| Taiwan                                                          | 0x12 | 0x25 | 0x04 | 0x32 | 0x32 | 0x05 |

| U.S., Canada (default)                                          | 0x25 | 0x4B | 0x08 | 0x32 | 0x32 | 0x05 |

At this point, users can program their own algorithm to monitor the detected tones. If the host dials, it should do so by blind dialing, setting the dial timeout S01 (DW) to zero seconds and issuing an "ATDT<Phone Number>;<CR>". This causes the modem to dial and return to command mode.

Once the host has detected an answer tone using manual call progress, the host should immediately execute the "ATDT" command in order to make a connection. This causes the CC-2401 to search for the modem answer tone and begin the correct connect sequence.

In manual call progress, the DSP can be programmed to detect specific tones. The result of the detection is reported in SE5 (SE8 = 0x2) as described above. The output is priority encoded such that if multiple tones are detected, the one with the highest priority whose detection is also enabled is reported.

In manual call progress, the modem can be programmed to generate specific tones. For example, setting SE5[2:0](TONC) = 110b generates the user defined tone (as indicated by UFRQ).

Page 23 of 66

### Data Sheet

| DTMF | Keyboard   | Contact  | То  | nes  |

|------|------------|----------|-----|------|

| Code | Equivalent | ID Digit | Low | High |

| 0    | 0          | 0        | 941 | 1336 |

| 1    | 1          | 1        | 697 | 1209 |

| 2    | 2          | 2        | 697 | 1336 |

| 3    | 3          | 3        | 697 | 1447 |

| 4    | 4          | 4        | 770 | 1209 |

| 5    | 5          | 5        | 770 | 1336 |

| 6    | 6          | 6        | 770 | 1477 |

| 7    | 7          | 7        | 852 | 1209 |

| 8    | 8          | 8        | 852 | 1336 |

| 9    | 9          | 9        | 852 | 1447 |

| 10   | D          | -        | 941 | 1633 |

| 11   | *          | В        | 941 | 1209 |

| 12   | #          | С        | 941 | 1447 |

| 13   | A          | D        | 697 | 1633 |

| 14   | В          | E        | 770 | 1633 |

| 15   | С          | F        | 852 | 1633 |

Page 24 of 66

### Low Level DSP Control

Although not necessary for most applications, the low-level control functions are available for very specific applications requiring direct DSP control.

#### **DSP** registers

Several DSP registers are accessible through the CC-2401 controller via S-registers. SE5, SE6 and SE8 are used to write data to specific DSP registers and read status. SE8 defines the function of SE5 and SE6 depending on whether they are being written or read from. Care must be exercised when writing to DSP registers. DSP registers can only be written while the CC-2401 is on hook and in command mode. Writing to any register address not listed or writing out of range values is likely to cause the DSP to exhibit unpredictable behavior.

The DSP register address is 16 bit, and the DSP data field is 14 bits wide. DSP register addresses and data are written in hexadecimal. To write a value to a DSP register the register address is written and then the data. When SE8 = 0x00, SE5(DADL) is written with the low bits [7:0] of the DSP register address, and SE6(DADH) is written with the high bits ([15:8]) of the data word corresponding to the previously written address.

Page 25 of 66

#### Low Level DSP Parameters

| DSP Reg.<br>Addr. | Name  | Description                                                                                                     | Function                                                  | Default<br>(dec) |

|-------------------|-------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------|

| 0x0002            | SMTL  | DAA modem full-scale transmit level, default =-10 dBm                                                           | Level = 20log <sub>10</sub> (XTML/4096) -10<br>dBm        | 4096             |

| 0x0003            | DTML  | DTMF high-tone transmit level,<br>default = -5.5 dBm                                                            | Level=20log <sub>10</sub> (DTML/4868) -5.5<br>dBm         | 4868             |

| 0x0004            | DTMT  | DTMF twist ratio (low/high),<br>Default = -2 dBm.                                                               | Level = 20log <sub>10</sub> (DTMT/3277) – 2<br>dB         | 3277             |

| 0x0005            | UFRQ  | User-defined transmit tone<br>frequency. See register SE5<br>(SE8=0x02(Write Only)).                            | f = (9600/512) UFRQ (Hz)                                  | 91               |

| 0x0006            | CPDL  | Call progress detect level,<br>default = -43 dBm                                                                | Level = 20log <sub>10</sub> (4096/CPDL) -43<br>dBm        | 4096             |

| 0x0007            | UDFD1 | User-defined frequency<br>detector 1. Center frequency<br>for detector 1.                                       | UDFD1 = 8192 cos (2p f/9600)                              | 4987             |

| 0x0008            | UDFD2 | User-defined frequency detector 2. Center frequency for detector 2.                                             | UDFD2 = 8192 cos (2p f/9600)                              | 536              |

| 0x0009            | UDFD3 | User-defined frequency<br>detector 3. Center frequency<br>for detector 3.                                       | UDFD3 = 8192 cos (2p f/9600)                              | 4987             |

| 0x000A            | UDFD4 | User-defined frequency<br>detector 4. Center frequency<br>for detector 4.                                       | UDFD4 = 8192 cos (2p f/9600)                              | 536              |

| 0x000B            | TGNL  | Tone generation level<br>associated with TONC<br>(SE5(SE8 = 0x02) Write Only<br>Definition), default = -10 dBm. | Level = 20log <sub>10</sub> (TGNL/2896)<br>- 10 dBm       | 2896             |

| 0x000E            | UDFSL | Sensitivity setting for UDFD1-4 detectors, default = -43 dBm.                                                   | Sensitivity = 10log <sub>10</sub><br>(UDFSL/4096) -43 dBm | 4096             |

| 0x0024            | CONL  | Carrier ON level. Carrier is valid once it reaches this level.                                                  | Level = 20log <sub>10</sub> (2620/CONL) –<br>43 dBm.      |                  |

| 0x0025            | COFL  | Carrier OFF level. Carrier is<br>invalid once it falls below this<br>level.                                     | Level = 20log <sub>10</sub> (3300/COFL) –<br>45.5 dBm.    | 3300             |

| 0x0026            | AONL  | Answer ON level. Answer<br>tone is valid once it reaches<br>this level.                                         | Level = 10log <sub>10</sub> (AONL/107) - 43<br>dBm.       | 67               |

| 0x0027            | AOFL  | Answer OFF level. Answer<br>tone is invalid once it falls<br>below this level.                                  | Level = 10log <sub>10</sub> (AOFL/58) - 45.5<br>dBm.      | 37               |

Page 26 of 66

| SE8  |     |      | SE6                                                                                                                                                                                                                                                                                                      |      | SE5                                                                            |

|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------|

|      | R/W | Name | Description                                                                                                                                                                                                                                                                                              | Name | Description                                                                    |

| 0x00 | W   | DADH | DSP register address bits [15:8]                                                                                                                                                                                                                                                                         | DADL | DSP Register address bits<br>[7:0]                                             |

| 0x01 | W   | DDH  | DSP register data bits [15:8]                                                                                                                                                                                                                                                                            | DDL  | DSP register data bits [7:0]                                                   |

| 0x02 | R   |      |                                                                                                                                                                                                                                                                                                          | DSP1 | 7 = DSP data available<br>6 = Tone detected<br>5 = Reversed<br>4:0 = Tone type |