PRELYMINARY DATA

### 6+2-CH. MULTISTANDARD AUDIO DECODER

#### 1 FEATURES

- *DVD Audio* decoder:

- Meridian Lossless Packing (MLP), with up to 6 channels,

- Uncompressed LPCM with 1-8 channels,

- Precision of up to 24 bits and sample rates of between 44.1 kHz and 192 kHz.

- *Dolby Digital* <sup>(\*)</sup> decoder:

- Decodes 5.1 *Dolby Digital Surround.*

- Output up to 6 channels. downmix modes: 1, 2, 3 or 4 channels.

- MPEG -1 2- channel audio decoder, layers I and II.

- MPEG-2 6-channel audio decoder, layer II.

- 24 bits decoding precision.

- MP3 (MPEG layer III) decoder.

- Accepts MPEG-2 PES stream format for: MPEG-2, MPEG-1, Dolby Digital and linear PCM.

- Karaoke System.

- Prologic decoder.

- Downmix for Dolby Prologic compatible.

- A separate (2-ch) PCM output available for simultaneous playing and recording.

- Bitstream input interface: serial, parallel or SPDIF.

- SPDIF and IEC-61937 input interface.

- SPDIF and IEC-61937 output interface.

- PLL for internal PCM clock generation. frequencies supported: 44.1KHz family (22.05, 88.2, 176.4) and 48KHz family (24, 48, 96, 192).

- PCM: transparent, downsampling 192 to 96 Khz and 96 to 48kHz.

- PTS handling control on-chip.

- No external DRAM required

- I<sup>2</sup>C or parallel control bus

- Embedded Development RAM for customizable software capability.

- Configurable internal PLLs for system and audio clocks, from an externally provided clock.

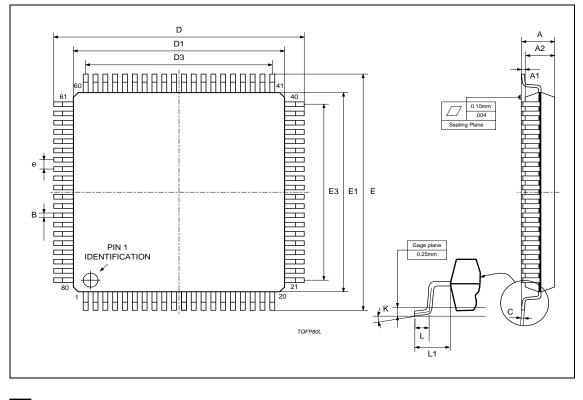

- 80-PIN TQFP package

TQFP80 ORDERING NUMBER: STA310

- 2.5V (for core) and 3V (for I/O) power supply.

3V Capable I/O Pads .

- True-SPDIF input receiver supporting AES/ EBU, IEC958, S/PDIF.

- No external chip required.

- Differential or single ended inputs can be decoded.

#### APPLICATIONS

- High-end audio equipment.

- DVD consumer players.

- Set top box.

- HDTV .

- Multimedia PC.

- (\*) "Dolby ", "AC-3" and "ProLogic" are trademarks of Dolby Laboratories.

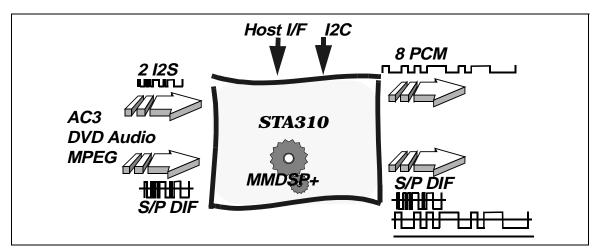

#### DESCRIPTION

The STA310 is a fully integrated Audio Decoder capable of decoding all the above listed formats.

Encoded input data can be entered either by a serial (I2S or SPDIF) or a parallel interface. A second input data stream (I2S) is available for micro input.

The control interface can be either  $l^2C$  or a parallel 8bit interface. No external DRAM is necessary for a total of 35ms surround delays.

June 2003

This is preliminary information on a new product now in development. Details are subject to change without notice.

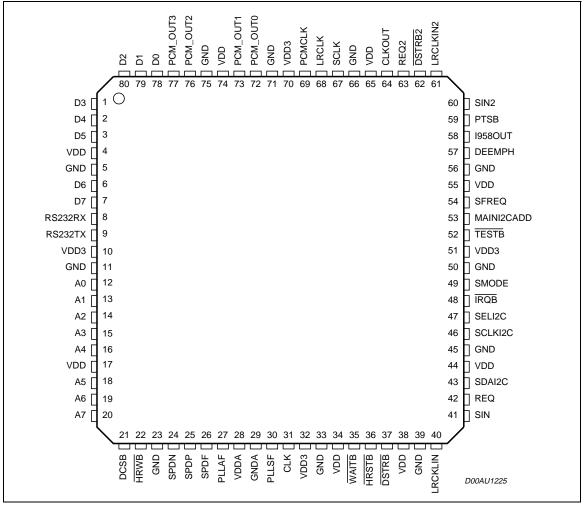

#### 2 STA310 AUDIO DECODER PIN DESCRIPTION

| Pin Number                             | Name                                   | Туре               | Function                                                                                  |

|----------------------------------------|----------------------------------------|--------------------|-------------------------------------------------------------------------------------------|

| CONTROL INTER                          | RFACES                                 |                    |                                                                                           |

| 48                                     | IRQB                                   | O <sup>(1)</sup>   | Interrupt Signal (level), active low                                                      |

| 47                                     | SELI2C                                 | l (2)              | Selects the Control Interface (when high: serial interface; when low: parallel interface) |

| I <sup>2</sup> C Control Inter         | rface                                  |                    |                                                                                           |

| 43                                     | SDAI2C                                 | I/O <sup>(1)</sup> | I <sup>2</sup> C Serial Data                                                              |

| 46                                     | SCLKI2C                                | I                  | I <sup>2</sup> C Clock                                                                    |

| 53                                     | MAINI2CADR                             | (2)                | Determines the slave address                                                              |

| Parallel Control                       | Interface                              |                    |                                                                                           |

| 78 - 79 - 80 - 1<br>2 - 3 - 6 - 7      | D0 - D1 - D2 - D3<br>D4 - D5 - D6 - D7 | I/O                | Host Data                                                                                 |

| 12 - 13 - 14 - 15<br>16 - 18 - 19 - 20 | A0 - A1 - A2 - A3<br>A4 - A5 - A6 - A7 | I                  | Host Address                                                                              |

| 21                                     | DCSB                                   | I                  | Chip Select, active low                                                                   |

| 22                                     | R/W                                    | I                  | Read/Write Selection: read access when high, write access when low                        |

| 35                                     | WAITB                                  | O <sup>(3)</sup>   | Data Acknowledge, active low                                                              |

| DATA INPUT INT                         | ERFACE                                 |                    |                                                                                           |

| First Serial Data                      | Interface (I <sup>2</sup> S)           |                    |                                                                                           |

| 37                                     | DSTRB                                  | I                  | Clock Input Data, active low                                                              |

| 41                                     | SIN                                    | I                  | Serial Input Data                                                                         |

| 40                                     | LRCLKIN                                | I                  | Word Clock for the Input                                                                  |

| 42                                     | REQ                                    | 0                  | Handshake for the Data Transfer, aconfigurable by the SIN_SETUP register                  |

| Second Serial Da                       | ata Interface (I <sup>2</sup> S)       |                    |                                                                                           |

| 62                                     | DSTRB2                                 | I                  | Clock Input Data, active low                                                              |

| 60                                     | SIN2                                   | I                  | Serial Input Data                                                                         |

| 61                                     | LRCLKIN2                               | I                  | Word Clock for the Input                                                                  |

| 63                                     | REQ2                                   | 0                  | Handshake for the Data Transfer, active low                                               |

| DATA OUTPUT II                         | NTERFACES                              |                    | •                                                                                         |

| 69                                     | PCMCLK                                 | I/O                | Oversampling Clock input for STA310 when generated externally                             |

| DAC Interface                          |                                        |                    |                                                                                           |

| 67                                     | SCLK                                   | 0                  | Bit Clock for the DAC                                                                     |

**\_\_\_**

2/90

Downloaded from  $\underline{Elcodis.com}$  electronic components distributor

| 2 STA310 AUDIO DECODER PIN DESCRIPTION ( | (continued) |

|------------------------------------------|-------------|

|------------------------------------------|-------------|

| Pin Number       | Name                  | Туре             | Function                                                                                                                                                                  |

|------------------|-----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 68               | LRCLK                 | 0                | Word Clock for the DAC                                                                                                                                                    |

| 72               | PCM_OUT0              | 0                | Data from a Prologic downmix (VCR_L/VCR_R)                                                                                                                                |

| 73               | PCM_OUT1              | 0                | Data for the first DAC (Left/Right)                                                                                                                                       |

| 76               | PCM_OUT2              | 0                | Data for the second DAC (Centre/Sub)                                                                                                                                      |

| 77               | PCM_OUT3              | 0                | Data for the third DAC (LeftSur/RightSur)                                                                                                                                 |

| IEC958 Interface | (S/PDIF) - One Output | t Port., O       | ne Input Ports.                                                                                                                                                           |

| 58               | 1958OUT               | 0                | S/PDIF Signal                                                                                                                                                             |

| 25               | SPDP                  | I                | First differential input of S/P DIF port                                                                                                                                  |

| 24               | SPDN                  | I                | Second differential input of S/P DIF port                                                                                                                                 |

| 26               | SPDF                  | I                | External Filter                                                                                                                                                           |

| 28               | VDDA                  | I                | Analog VDD for S/P DIF Input port                                                                                                                                         |

| 29               | GNDA                  | I                | Analog GND for S/P DIF Input port                                                                                                                                         |

| STATUS INFORM    | IATION                |                  |                                                                                                                                                                           |

| PCM Related Infe | ormation              |                  |                                                                                                                                                                           |

| 54               | SFREQ                 | 0                | Then high, indicates that the sampling freq. is either 44.1Khz or 22.05Khz.<br>When low, indicates that the sampling frequency is either 32 Khz, 48 Khz, 24 Khz or 16Khz. |

| 57               | DEEMPH                | 0                | Indicates if de-emphasis is performed.                                                                                                                                    |

| Audio Video Syr  | chronization          |                  |                                                                                                                                                                           |

| 59               | PTSB                  | 0                | Indicates that a PTS has been detected, active low.                                                                                                                       |

| Other Signals    |                       |                  |                                                                                                                                                                           |

| 31               | CLK                   | I                | Master Clock Input Signal.                                                                                                                                                |

| 36               | RESET                 | l <sup>(2)</sup> | Reset signal input, active low.                                                                                                                                           |

| 52               | TESTB                 | I <sup>(2)</sup> | Reserved pin: to be connected to VDD                                                                                                                                      |

| 49               | SMODE                 | I                | Reserved pin : to be connected to GND                                                                                                                                     |

| RS232 Interface  |                       | 1                |                                                                                                                                                                           |

| 8                | RS232RX               | I                |                                                                                                                                                                           |

| 9                | RS232TX               | 0                |                                                                                                                                                                           |

| PLLs INTERFAC    | ES                    |                  |                                                                                                                                                                           |

| 64               | CLKOUT                | 0                | System clock output with programmable division ratio                                                                                                                      |

| 27               | PLLAF                 | I                | External Filter For Audio PLL.                                                                                                                                            |

**57**

#### 2 STA310 AUDIO DECODER PIN DESCRIPTION (continued)

| Pin Number                                                | Name  | Туре | Function                        |

|-----------------------------------------------------------|-------|------|---------------------------------|

| 30                                                        | PLLSF | I    | External Filter For System PLL. |

| Power and Grou                                            | nd    | •    |                                 |

| 5 - 11 - 23 - 33 -<br>39 - 45 - 50 - 56<br>- 66 - 71 - 75 | GND   | GND  | Ground                          |

| 4 - 17 - 34 - 38<br>44 - 55 - 65 - 74                     | VDD   | VDD  | 2.5V Power Supply               |

| 10 - 32 - 51 - 70                                         | VDD3  | VDD3 | 3.3V Power Supply               |

Notes (1) Open Drain

(2) Internal Pull-up

(3) Tri-State

#### PIN CONNECTION (Top view)

57

1

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameters                   | Value             | Unit |

|--------|------------------------------|-------------------|------|

| Vdd    | 2.5V Power Supply Voltage    | -0.5 to 3.3       | V    |

|        | 2.5V Input or Output Voltage | -0.5 to (Vdd+0.5) | V    |

| Vdd3   | 3.3V Power Supply Voltage    | -0.5 to 4         | V    |

|        | 3.3V Input or Output Voltage | -0.5 to (Vdd+0.5) | V    |

**ELECTRICAL CHARACTERISTICS** (V<sub>DD</sub> = 3.3V + -0.3V; T<sub>amb</sub> = 0 to 70°C; Rg =  $50 \Omega$  unless otherwise specified

#### DC OPERATING CONDITIONS

| Symbol | Parameters                     | Value      | Unit |  |  |  |

|--------|--------------------------------|------------|------|--|--|--|

| Vcc    | Power Supply Voltage           | 2.5        | V    |  |  |  |

| Tj     | Operating Junction Temperature | -20 to 125 | °C   |  |  |  |

#### **GENERAL INTERFACE**

| Symbol               | Parameters                                           | Conditions     | Min  | Тур | Max | Unit | Note |

|----------------------|------------------------------------------------------|----------------|------|-----|-----|------|------|

| l <sub>il</sub>      | Low level input current without pull-up device       | Vi = 0V        |      |     | 1   | μA   | 1    |

| l <sub>ih</sub>      | High level input current without pull-down device    | Vi = Vdd       |      |     | 1   | μA   | 1    |

| I <sub>oz</sub>      | Tri-state output leakage without pull-up/down device | Vi = 0V or Vdd |      |     | 1   | μA   | 1    |

| I <sub>latchup</sub> | I/O Latch-up current                                 | V<0V, V>Vdd    | 200  |     |     | mA   | 2    |

| Vesd                 | Electrostatic protection                             | Leakage <1µA   | 2000 |     |     | V    | 3    |

Note: 1. The leakage currents are generally very small, <1nA. The value given here, 1μA, is a maximum that can occur after an Electrostatic Stress on the pin.</li>

2. V> Vdd3 for 3.3V buffers.

2. I/warea Bady Model

3. Human Body Model

#### LVTTL & LVCMOS DC Input Specification 2.7V <Vdd3 <3.6V

| Symbol              | Parameters                        | Conditions | Min | Тур | Max  | Unit | Note |

|---------------------|-----------------------------------|------------|-----|-----|------|------|------|

| Vil                 | Low level input voltage           |            |     |     | 0.8  | V    | 1    |

| V <sub>ih</sub>     | High level input voltage          |            | 2.0 |     |      | V    | 1    |

| V <sub>ilhyst</sub> | Low level threshold input falling |            | 0.8 |     | 1.35 | V    | 1    |

| V <sub>ihhyst</sub> | High level threshold input rising |            | 1.3 |     | 2.0  | V    | 1    |

| V <sub>hyst</sub>   | Schmitt trigger hysteresis        |            | 0.3 |     | 0.8  | V    | 1    |

Note: 1. Takes into account 200mV voltage drop in both supply lines. 2. X in the source/sink current under worst case conditions and is reflected in the name of the I/O cell according to the drive capability

#### ELECTRICAL CHARACTERISTICS (continued)

| Symbol | Parameters                    | Conditions | Min | Тур | Max | Unit | Note |

|--------|-------------------------------|------------|-----|-----|-----|------|------|

| lpu    | Pull-up current               | Vi = 0V    |     | -66 | 0.8 | μΑ   | 1    |

| Rpu    | Equivalent Pull-up resistance | Vi = 0V    |     | 50  |     | KΩ   |      |

Note: 1. Min condition:  $V_{DD} = 2.7V$ , 125°C Min precess Max condition:  $V_{DD} = 3.6V$ , -20°C Max

#### POWER DISSIPATION

| Symbol | Parameters        | Conditions                     | Min | Тур    | Max | Unit | Note |

|--------|-------------------|--------------------------------|-----|--------|-----|------|------|

| PD     | Power Dissipation | Sampling frequecy ≤ 24KHz      |     | t.b.d. |     | mW   | 1    |

|        | $@V_{DD} = 2.4V$  | Sampling frequecy $\leq$ 32KHz |     | t.b.d. |     | mW   | 1    |

|        |                   | Sampling frequecy ≤ 48KHz      |     | t.b.d. |     | mW   | 1    |

#### INTRODUCTION

The STA310 is a fully integrated multi-format audio decoder. It accepts as input, audio data streams coded with all the formats listed above.

**A**7/

#### 2.1 Inputs and Outputs

#### 2.1.1 Data Inputs

- Through a parallel interface (shared with the control interface)

- Through a serial interface (for all the I<sup>2</sup>S formats)

- Through a S/P DIF (SPDIF or IEC-61937 standards).

- Trough a second, independent, **1**<sup>2</sup>**S** (for application like i..e. Karaoke mixing).

#### 2.1.2 Data outputs

- The PCM audio ooutput interface, which provide:

- PCM data on 4 outputs:

- Left/Right,

- Centre/Subwoofer

- Left Surround/Right Surround.

• Data From a Prologic downmix (encoder)

"Lrclk" "Sclk" "PcmClk"

#### - S/P DIF Output

#### 2.1.3 Control I/F

I2C slave or parallel interface:

The device configuration and the command issuing is done via this interface. To facilitate the contact with the MCU, 2 interrupt lines (IRQB and INTLINE) are available.

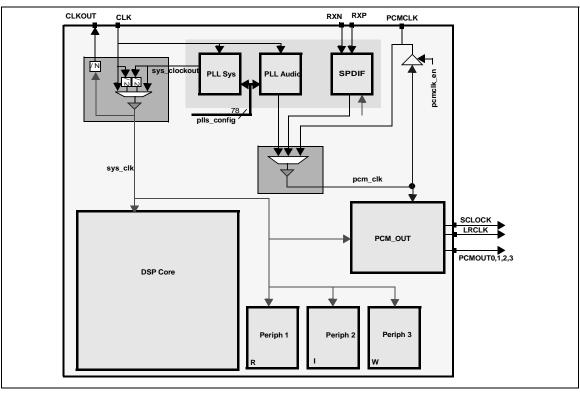

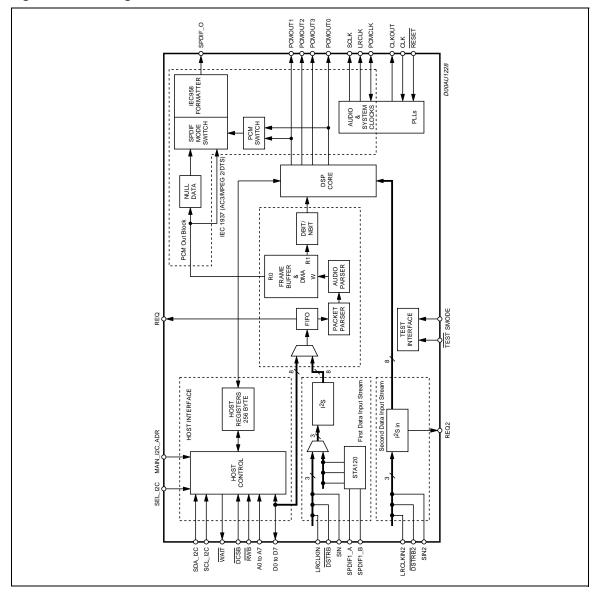

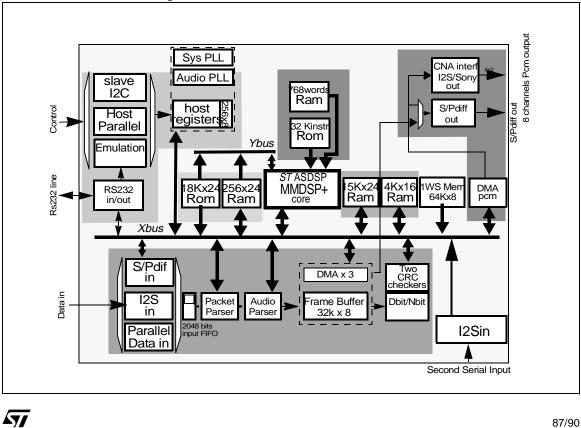

#### **3 ARCHITECTURE OVERVIEW**

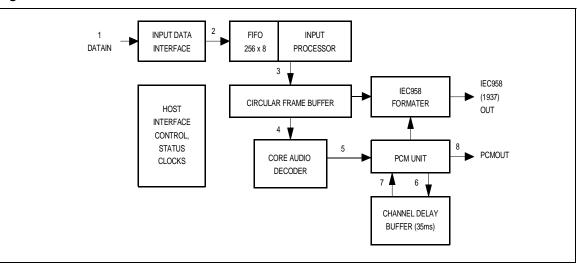

#### 3.1 Data flow

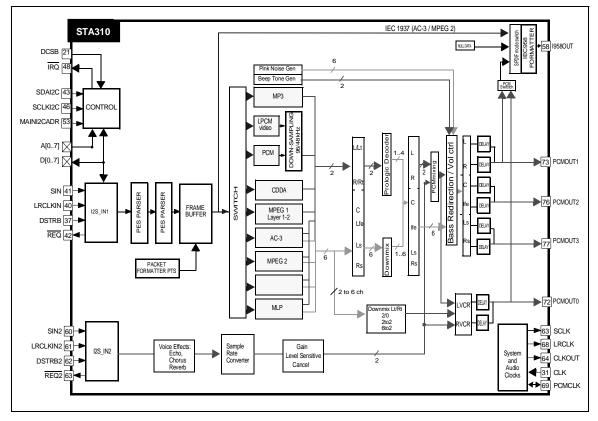

The STA310 is based on a programmable MMDSP+ core optimized for audio decoding algorithms.

Dedicated hardware has been added to perform specific operations such as bitstream depacking or IEC data formatting.

The arrows in Figure 3 indicate the data flow within the chip.

The compressed bitstream is input via the data input interface.

Data are transferred on a byte basis to the FIFO. This FIFO allows burst input data at up to 33Mbit/s.

The input processor, which is composed of a packet parser and an audio parser, unpacks the bitstream (Packet parser) and verifies the syntax of the incoming stream (audio parser).

The compressed audio frames with their associated information (PTS) are stored into the circular frame buffer.

While a second frame is stored in the circular frame buffer, the first frame is extracted by the audio core decoder which decodes it to produce audio samples.

The PCM unit converts the samples to the PCM format. The PCM unit controls also the channel delay buffer in order to delay each channel independently.

In parallel, the IEC unit transmits non compressed data or compressed data according to the selected mode. In the compressed mode, the data are extracted directly from the circular buffer and formatted according to the IEC-61937 standard. In non compressed mode, the left and right PCM channels formatted by the PCM unit are output by the IEC unit, according to the SPDIF standard

#### Figure 1. Architecture and data flows

#### 3.2 Functional diagram

#### Figure 2. Audio decoder top level functional diagram

#### 3.3 Control interface description

The IC can be controlled either by a host using an I<sup>2</sup>C interface, or by a general purpose host interface.

These interfaces provide the same functions and are described in the following sections. The selection is performed by the means of the pin SELI2C: when high, this pin indicates that the I<sup>2</sup>C interface is used. When low, the parallel interface is used.

#### 3.3.1 Parallel control interface

When the pin SELI2C is low, the control of the chip is performed through the parallel interface. When accessing the device through the parallel interface, the following signals are used:

- The address bus A[7..0]. It is used to select one of the 256 register locations.

- The data bus DATA[7..0]. If a read cycle is requested, the data lines D[7:0] will be driven by the IC. For a write cycle, the STA310 will latch the data placed on the data lines when the WAIT signal is driven high.

- The signal R/W. It defines the type of register access: either read (when high), or write (when low). Some registers can be either written or read, some are read only, some are write only.

- The signal DCSB. A cycle is defined by the assertion of the signal DCSB.

Note: 1. The address bus A[7..0], and read/write signal  $R/\overline{W}$  must be setup before the  $\overline{DCSB}$  line is activated.

#### 8/90

- The signal WAIT. This signal is always driven low in response to the DCSB assertion.

The timing diagrams for the parallel control interface are given in *Electrical specifications* on page 5.

#### 3.4 I<sup>2</sup>C control interface

When the pin SELI2C is high, the chip is controlled through the I<sup>2</sup>C interface. The I<sup>2</sup>C unit works at up to 400kHz in slave mode with 7-bit addressing.

- The Pin MAINI2CADR selects the device address. When MAINI2CADR is high the slave address is 0x5C, when low the device address is equal to the value on the address bus (A0...A6).

- The pin SDAI2C is the serial data line.

- The pin SCLKI2C is the serial clock.

The I<sup>2</sup>C Bus standard does not specify sub-addressing. There are thus potentially multiple ways to implement it. Any implementation that respects the standard is of course legal but a particular implementation is used by many companies. The following paragraphs describe this implementation.

#### 3.4.1 Protocol description

For write accesses only, the first data which follows the slave address is always the sub-address.

This is the one and only way to declare the sub-address. It should be noticed that the sub-address is implemented as a standard data on the I<sup>2</sup>C Bus protocol point of view. It is a sub-address because the slave knows that it must load its address pointer with the first data sent by the master.

See in the Appendix X.x for I<sup>2</sup>C message format examples.

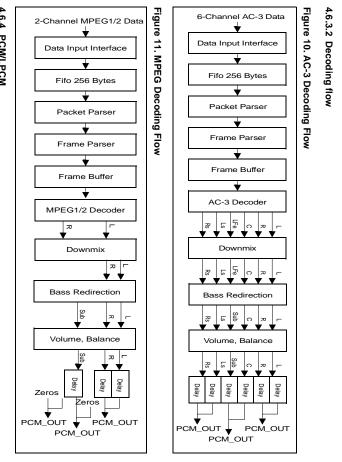

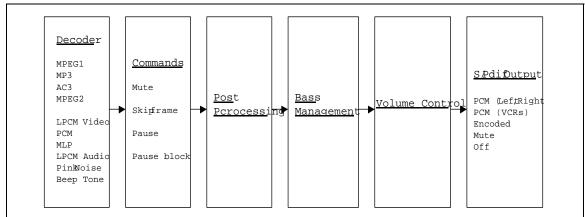

#### 3.5 Decoding process

The decoding process in the STA310 is done in several stages:

- Parsing,

- Main decoding,

- Post decoding,

- Bass redirection,

- Volume and Balance control.

Each of the stages can be activated or bypassed according to the configuration registers.

#### Parsing

The bitstream parsing (performed by the input processor) is in charge of discarding all the non audio information in order to transmit to the next stage (the circular frame buffer) only the audio elementary stream (AC3, MPEG1/2, LPCM, PCM, DVD Audio).

The parsing stage operates in two phases: the packet parser unpacks the stream, the audio parser checks the syntax of the bitstream.

#### Main Decoding

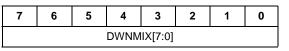

The input of this stage is an elementary stream, the outputs are decoded samples. The number of output channels is defined by the downmix register (1 channel up to 6 channels). For details, please refer to the description of the register.

The decoding formats currently supported are AC3, MPEG1 layers I and II, MPEG2 layer II, LPCM. It is necessary to select the appropriate stream format by configuring the registers STREAMSEL and DECODESEL before running the decoder.

#### **Post Decoding**

The post decoding includes specific PCM processing: DC filter, de-emphasis filter, downsampling filter. These filters can be independently enabled or disabled through the register DWSMODE.

It provides also a Pro Logic decoder, which is described in detail in a next section.

#### **Bass Redirection**

This stage redirects the low frequency signals to the subwoofer.

The subwoofer is extracted from the other channels (L, R, C, Ls, Rs, LFe). There are six possible configurations to extract the subwoofer channel, which can be selected thanks to the OCFG register.

#### Volume and Balance Control

The volume is a master volume (no independent control for each channel). It is controlled by the PCMSCALE register, which enables to attenuate the signals by steps of 2dB.

Two balance controls are available: one for Left/Right channels, one for Left Surround/Right Surround channels. They are configurable by means of registers BAL\_LR (Left-Right Balance) and BAL\_SUR (Left Surround-Right Surround Balance), which provide attenuation of signals by steps of 0.5dB.

#### 4 OPERATION

#### 4.1 Reset

The STA310 can be reset either by a hardware reset or by a software reset:

- The hardware reset is sent when the pin RESET is activated low during at least 60ns. This is equivalent to a power-on reset.

This resets all the configuration registers, i.e. PLL registers (PLLSYS, PLLPCM), Interrupt registers (INTE, INT, ERROR), interface registers (SIN\_SETUP, CAN\_SETUP) and command registers (SOFTRESET, RUN, PLAY, MUTE, SKIP\_FRAME, REPEAT\_FRAME).

- The software reset is sent when the register SOFTRESET is written to 1 (the register is automatically reset once the software reset is performed). It resets only the interrupt related registers (INTE, INT, ERROR) and the command registers (SOFTRESET, RUN, PLAY, MUTE, SKIP\_FRAME, REPEAT\_FRAME). All other decoding configurations are not changed by softreset.

Some information concerning the post-processing are anywayt of date after a soft-reset

Note: 1. The chip must be soft reset before changing any configuration register.

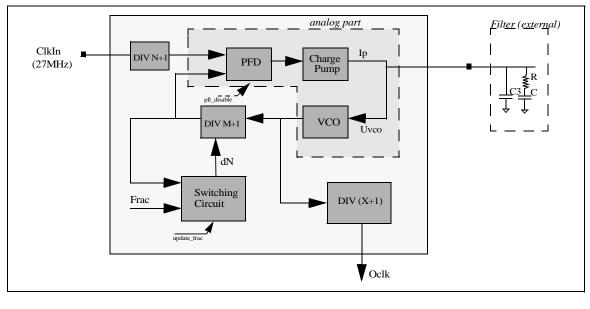

#### 4.2 Clocks

There are two embedded PLLs in the STA310: the system PLL and the PCM PLL. The following is the block diagram of the system and audio clocks used in the STA310

Figure 3. PLL Block Diagram

Figure 4. Block Diagram of Functional PLL

#### 4.2.1 System clock

The system clock sent to the DSP core and the peripherals can be derived from 4 sources and the selection is performed through an Host Register; external clock, external clock divided by 2, internal system PLL and internal system PLL divided by 2.

The system PLL is used to create the system clock from the input clock. This PLL is software programmable through the Host Registers mechanism. The system PLL is used to set the any frequency up to the maximum allowed device speed. After hard reset the system clock is running at 47.25MHz. An RC network must be connected to the filter Pin PLLSF.

The system clock is output on the pin CLKOUT after a programmable divider ranging from 1 to 16.

#### 4.2.2 DAC clocks

#### 4.2.2.1 PCM clock

The PCM clock can be either input to the device or generated by the internal PLL or recovered by the embedded SPDIF receiver. The selection is done via the Host Registers.

After a hardware reset, the internal PLL is disabled and the PCMCLK pad is an input. PCMCLK may be equal to the PCM output bit rate, or it may be an integer multiple of this, allowing the use of oversampling D-A converters.

The internal fractional PLL is able to generate PCMCLK at any "FsX Oversampling Factor" frequencies, where Fs is any multiple or sub-multiple of the two 44.1kHz and 48kHz sampling frequencies. An RC network must be connected to the filter pin PLLAF; refer to External circuitry on page 9 for recommended values.

If the PCMCLK is recovered from the embedded SPDIF receiver, the only supported overampling frquency is 128 Fs.

#### 4.2.2.2 Bit clock SCLK

The PCM serial clock SCLK is the bit clock. It provides clocks for each time slot (16 cycles for each channel in 16-bit mode, 32 cycles for each channel in 18-, 20-, 24-bit modes). The frequency of SCLK is therefore fixed to 2 x Nb time slots x Fs, where Fs is the sample frequency.

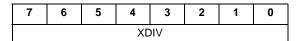

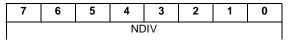

The clock is derived from the clock PCMCLK. The register PCMDIVIDER must be configured according to the selected output precision and the frequency of PCMCLK, so that the device can construct SCLK:

Fsclk = Fpcmclk / (2 x (PCMDIVIDER+1)) gives

| PCM Divider Value | Mode Description                    |

|-------------------|-------------------------------------|

| 5                 | PCMCLK = 384 Fs, DAC is 16-bit mode |

| 3                 | PCMLK = 256 Fs, DAC is 16-bit mode  |

| 2                 | PCMLK = 384 Fs, DAC is 32-bit mode  |

| 1                 | PCMLK = 256 Fs, DAC is 32-bit mode  |

#### Table 1.

The value of PCMDIVIDER = 0 is reserved. If this number is loaded, the divider is bypassed and the frequency of SCLK equals the frequency of PCMCLK. The PCMDIVIDER register must be setup before the output of SCLK starts.

This can be done by first disabling PCM outputs, by de-asserting the MUTE and PLAY commands and then writing into the PCMDIVIDER register. Once the register is setup, the MUTE and/or PLAY commands can be asserted. PCMDIVIDER can not be changed "on the fly".

#### 4.2.2.3 Word clock LRCLK

The frequency of LRCLK is given by:

- FIrclk = Fsclk/32; for 16 bit PCM output,

- FIrclk = Fsclk/64; for 18, 20 or 24 bits PCM output.

No special configuration is required. The polarity can be changed in the register PCMCONF, by setting up the field INV as needed.

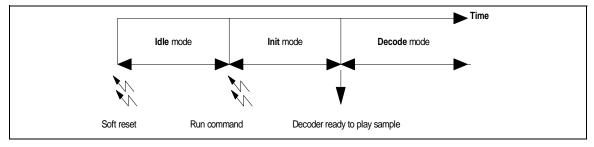

#### 4.3 Decoding states

There are two different decoder states: Idle state and decode state (see <Blue HT>Figure 3). To change states, register

#### Figure 5. Decoding States

#### Idle Mode

This is the state entered after a hardware or software reset. In this state, the embedded DSP does not decode, i.e. no data are processed. The chip is waiting for the RUN command, and during this state all configuration registers must be initialized. In this state, even if the chip is not processing data, the DACs clocks can be output, which enables to setup the external DACs. Once the PCMCLK, SCLK and LRCLK clocks are configured, it is possible to output them by setting the MUTE register.I

#### Table 2. Idle mode. play and mute commands effects

| Play | Mute | Clock (SCLK, LRCLK) State | PCM Output |

|------|------|---------------------------|------------|

| Х    | 0    | Not running               | 0          |

| Х    | 1    | Running                   | 0          |

Note: 1. The PLAY command has no effect in this state as the decoder is not running. It can however be sent and it will be taken into account as soon as the decoder enters the decode state.

#### Decode Mode

This state is entered after the RUN command has been sent (i.e. RUN register = 1). In this mode, the data are processed. The decoder can play sound, or mute the outputs, by using the PLAY and MUTE registers:

- To decode streams, the PLAY register must be set. When decoding, the sound will be sent to outputs if the MUTE register is reset. The outputs are muted if the MUTE register is set.

- To stop decoding, the PLAY register should be reset. Resuming decoding is performed by writing PLAY to 1 again

| Play | Mute | Clock State | PCM Output      | Decoding |

|------|------|-------------|-----------------|----------|

| 0    | 0    | Not running | 0               | No       |

| 0    | 1    | Running     | 0               | No       |

| 1    | 0    | Running     | Decoded Samples | Yes      |

| 1    | 1    | Running     | 0               | Yes      |

Table 3. Decode Mode. Play and Mute commands effects

Note: 1. It is not possible to change configuration registers in this state. It is necessary to soft reset the chip before. Only the following registers can be changed "on-the-fly": PCM\_SCALE, BAL\_LR, BAL\_SUR, OCFG, DOWNMIX registers.

#### 4.4 Data input interface description.

#### Figure 6. Block Diagram of Data Flow

Two independent inputs are available on the STA310.

The main one allows to enter input data stream through through:

- A serial interface (referred to as Data Serial Interface),

- And a parallel interface (referred to as Data Parallel Interface).

The choice is performed by the register SIN\_SETUP.

#### 4.4.1 Data serial interface

When the serial mode is selected, the bitstreams can be entered into the STA310 through either:

- a four-signal data interface or ,

- trough a SPDIF input (no external circuit is required).

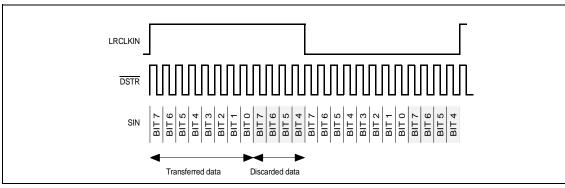

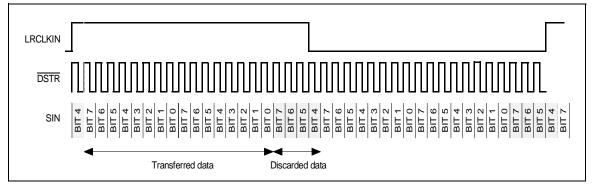

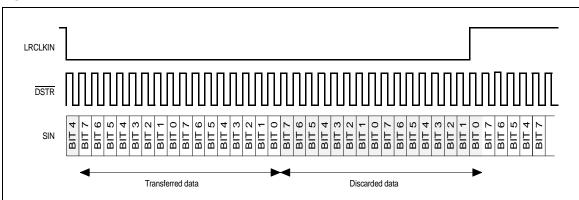

The four-signal data interface (see Figure 5) provides:

- An input data line SIN,

- An input clock DSTR,

- A word clock input LRCLKIN

- And a hand-shake output signal  $\overline{\text{REQ}}$ .

Note: 1. Only 16-bit PCM streams are supported. For 20-bit or 24-bit PCM, the 4 or 8 least significant bits are ignored

The specifications of those signals can be configured by the means of the register CAN\_SETUP.

Two modes exist in serial mode, one that uses the LRCLKIN pin and one that does not use the LRCLKIN pin.

#### 4.4.1.1 Modes without the LRCLKIN pin

In this mode the signal LRCLKIN is not used by the <u>STA310</u>. The input data SIN is sampled <u>on the rising edge</u> of DSTR. When the STA310 input buffer is full the REQ signal is asserted. The polarity of REQ signal is programmable through the register SIN\_SETUP. The data must be sent most significant bits first.

When the decoder cannot accept further data the REQ is de-asserted and the DSTR clock must be stopped as soon as possible to avoid data loss. After the REQ is de-asserted, the decoder is still able to accept data for a limited number of clock cycles.

The maximum number of data that can be transmitted with respect to the change of  $\overline{REQ}$  is given by the following formula: Nbits = 23 - 6 \*  $\overline{F_{DSTR}}/33MHz$ , where:  $\overline{F_{DSTR}}$  is the  $\overline{DSTR}$  clock frequency, (max is 33 MHz).

#### 4.4.1.2 Modes using the LRCLKIN pin

When receiving data from an A/D converter or from an S/PDIF receiver, the signal LRCLKIN is used.

The LRCLKIN signal is used to make the distinction between the left and right channels. Any edge of the LR-CLKIN signal indicates a word boundary.

The data transfer between the input interface and the FIFO is done on a byte basis. After the edge (rising or falling) of the LRCLKIN, a new byte is transferred to the first stage of the STA310 every 8 DSTR clock cycles.

If the number of time slots is not a multiple of 8, the remaining data is lost. The polarity of LRCLKIN and DSTR is programmable.

The LRCLKIN can be delayed by one time slot, in order to support PCM delayed mode. All these configurations are programmable through the CAN\_SETUP register.

The register CAN\_SETUP has 4 significant bits, and each bit has a specific meaning, see CAN\_SETUP on page 41.

Only the first byte is transferred to the STA310 because the number of time slots is 12 (8 + 4). SIN and LRCLKIN are sampled on the falling edge of DSTR In this case SIN\_SETUP = 3 and CAN\_SETUP = LeftFirstChannel + FallingStrobe + AllSlot = 2 + 4 + 8 = 14

#### Table 4.

|       | When Set                                                   | When Clear                                | Name             |

|-------|------------------------------------------------------------|-------------------------------------------|------------------|

| Bit 0 | The input data is one slot delayed with respect to LRCLKIN | The input data is not delayed             | DelayMode        |

| Bit 1 | First channel when LRCLKIN is set                          | First channel when LRCLKIN is reset       | LeftFirstChannel |

| Bit 2 | Data are sampled on falling edge of DSTR                   | Data are sampled on rising edge of DSTR   | FallingStrobe    |

| Bit 3 | All the bytes are extracted                                | Only the first 16 data bits are extracted | AllSlot          |

#### Figure 7.

Example 2: Only the first 2 bytes are transferred to the STA310 because the number of slots is 20 (16 + 4). SIN and LRCLKIN are sampled on the falling edge of DSTR. The data is in delayed mode. The register configuration is SIN\_SETUP=3 and CAN\_SETUP = DelayMode + LeftFirstChannel + FallingStrobe

+ AllSlot = 1 + 2 + 4 + 8 = 15. This mode is a specific mode where only the first 16 data bits are transferred. The remaining bits are discarded. The register configuration is SIN\_SETUP = 3 and CAN\_SETUP = DelayMode + FallingStrobe = 1 + 4 = 5.

#### 4.4.1.3 SPDIF Input

A true SPDIF Input **SPDIF** (PCM audio samples) or **IEC-61937** (compressed data) is selectable as a main serial input.

#### 4.4.1.4 Autodetected formats

The STA310 cut 2.0 is able the following audio format changes on the s/pdif input

#### Table 5. Audio Format detection

| BEFORE  | AFTER |

|---------|-------|

| BEI ORE | ALLEN |

| AC3     | PCM   |

| AC3     | MPEG  |

| MPEG    | AC3   |

| MPEG    | PCM   |

| PCM     | AC3   |

| PCM     | MPEG  |

#### 4.4.1.5 Second Input

A second independent input allows to input bitstreams in serial mode.

This second input can be used, to input audio stream from a microphone, while we decode a data stream trough the main input.

#### 4.4.2 Data parallel interface

Two ways are available to input data in parallel mode:

- Either through the parallel data bus, shared with the external controller,

- Or through the DATAIN register

#### 4.4.2.1 Using the parallel data bus

In this mode the data must be presented on the 8-bit parallel host data bus D[7..0]. Note that this bus is shared with the external controller. On the rising clock of DSTR the data byte is sampled by the STA310. The signal REQ is used to signal when the input FIFO is full. When REQ is de-asserted the transfer must be stopped to avoid data loss.

After the REQ is de-asserted, the decoder is still able to accept data for a limited number of clock cycles.

The maximum number of data that can be transmitted with respect to the change of  $\overline{REQ}$  is given by the following formula: Nbits = 23 - 6 \*  $F_{DSTR}$ /33MHz, where:  $F_{DSTR}$  is the  $\overline{DSTR}$  clock frequency, (max is 33 MHz).

The signals DSTR and DCSB are used to make the distinction between Stream Data (strobed by DSTR) and Control Data (strobed by DCSB). To avoid conflicts, the DSTR signal and the DCSB signal must respect given timing constraints.

#### 4.4.2.2 Using the DATAIN register

The data can be input by using the control parallel interface as if accessing any other register.

The signal DCSB is therefore used. When using this register to input data stream, there is no need to byte-align the data.

Figure 8.

#### Figure 9.

#### 4.5 Streams parsers

The parsing stage is operated by two parts: the packet parser and the audio parser.

The packet parser unpacks stream, sorts packets and transmit data to the audio parser. The audio parser verifies the stream syntax, extracts non-audio data and sends audio data to the frame buffer.

#### Packet parser

Before unpacking packets and transmitting data, the packet parser needs to detect the packet start by recognizing the packet synchronization word. It is possible to force the parser to search for two packet synchronization words before starting to unpack and transmit.

This is done by setting the register PACKET\_LOCK to 1. Otherwise, the packet parser will start handling the stream once it has detected information matching the packet synchronization word.

The packet parser is also able to perform selective decoding: it can decode audio packets that are matching a specified Id. This Id is specified in AUDIO\_ID and AUDIO\_ID\_EXt registers, and the function is enabled by setting the AUDIO\_ID\_EN register.

#### Audio parser

The audio parser needs to detect the audio synchronization word corresponding to the type of stream that must be decoded. It is possible to force the audio parser to detect more than one synchronization word before parsing.

This is done by setting the SYNC\_LOCK register to a value between 1 and 3 - number of supplementary sync words to detect before considering to be synchronized.

The status of synchronization of both parsers is provided in the register SYNC\_STATUS. Each time the synchronization status of one of the two parsers changes, the interrupt SYN is generated (if enabled) and the status can be read in SYNC\_STATUS.

#### 4.6 Decoding modes

#### 4.6.1 AC-3

The STA310 is Dolby Digital certified for class A products. The decoder must be programmed so to specify the stream format as AC-3 encoded: register DECODESEL = 0.

In the sections below are provided the modes specific to the AC-3 decoding.

#### 4.6.1.1 Compression modes

Four compression modes are provided in the STA310:

18/90

- Custom A (also named custom 0 in Dolby specifications),

- Custom D (also named custom 1 in Dolby specifications),

- Line mode,

- RF mode.

These modes refer to different implementation of the dialog normalization and dynamic range control features. The mode is selected by programming the register COMP\_MOD to the appropriate value.

#### Line Mode

In Line Mode (COMP\_MOD = 2), the dialog normalization is always enabled. It is done by the decoder itself and the dialog is reproduced at a constant level.

The dynamic range control variable encoded in the bitstream is used and can be scaled by the two scaling registers HDR (for high-level cut compression) and LDR (for low-level boost compression). In case of 2/0 downmix, the high-level cut compression is not scalable.

#### **RF Mode**

In RF Mode (COMP\_MOD=3), the dialog normalization is always performed by the decoder. The dialog is reproduced at a constant level.

The dynamic range control and heavy compression variables encoded in the bitstream are used, but the compression scaling is not allowed. This means that the HDR and LDR registers can not be used in this mode. A +11dB gain shift is applied on the output channels.

#### **Custom A Mode**

In Custom A mode (COMP\_MOD=0), the dialog normalization is not performed by the decoder and must be done by another circuit externally.

The dynamic range control variable encoded in the bitstream is used and can be scaled by the two scaling registers HDR (for high-level cut compression) and LDR (for low-level boost compression).

#### **Custom D Mode**

In Custom D mode (COMP\_MOD=1), the dialog normalization is performed by the decoder. The dynamic range control variable encoded in the bitstream is used and can be scaled by the two scaling registers HDR (for high-level cut compression) and LDR (for low-level boost compression).

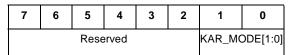

#### 4.6.1.2 Karaoke mode

The AC-3 decoder is karaoke aware and capable.

A karaoke bitstream can be composed of 5 channels: L for Left, R for Right, M for guide Melody, V1 for vocal track 1 and V2 for Vocal track 2.

- When in karaoke aware mode, the channels L,R and M are reproduced, and the channels V1 and V2 are reproduced at a level fixed by the bitstream.

- When in karaoke capable mode, it is possible to choose to reproduce one, two or none of the two incoming vocal tracks, V1 and V2.

The karaoke decoder is activated by the use of KARAMODE register, which specifies the downmix for the different modes. This register replaces DOWNMIX register. It is however possible to consider the incoming karaoke channels as any other multichannel stream and output it with a downmix specified in DOWNMIX register. For details, refer to the Digital Audio Compression AC-3 ATSC standard, annex C.

#### 4.6.1.3 Dual Mode

The Dual Mode corresponds to a mode where two completely independent mono program channels (e.g. bilingual) are encoded in the bitstream, referenced to as channel 1 and channel 2.

The possible ways to output channels on left/right outputs are:

- Output channel 1 on both L/R outputs,

- Output channel 2 on both L/R outputs,

- Mix channels 1 and 2 to monophonic and output on both L/R,

- Output channel 1 on Left output, and channel 2 on Right output.

This channels downmix is specified in the register DUALMODE.

#### 4.6.2 MPEG

The STA310 is able to decode MPEG-1 layerI and layerII encoded data, as well as MPEG-2 layer I, layer II data without extension (i.e. 2-channel streams).

The MPEG input format should be specified in the DECODESEL register:

- DECODESEL=1 for MPEG1. The MC bit in MC\_OFF register should be set.

- DECODESEL=2 for MPEG2. The MC bit in MC\_OFF register should be set.

#### 4.6.3 MP3

The STA310 is able to decoder MPEG2 layer III (MP3) data.

The MP3 input format aboved be specified in the DECODESEL register:

- DECODESEL=9 for MP3.

#### 4.6.3.1 Dual Mode

The Dual Mode corresponds to a mode where two completely independent mono program channels (e.g. bilingual) are encoded in the 2-channel incoming bitstream, referenced to as channel 1 and channel 2.

The audio decoder allows to:

- Output channel 1 on both L/R outputs,

- Output channel 2 on both L/R outputs,

- Mix channels 1 and 2 to monophonic and output on both L/R,

- Output channel 1 on Left output, and channel 2 on Right output.

The output configuration is chosen by special downmix for dual mode through register MPEG\_DUAL.

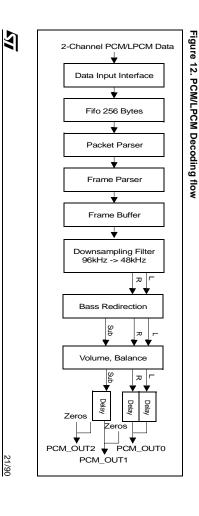

# 4.6.4 PCM/LPCM

The decoder supports PCM (2-channels) and LPCM Video (8-channels) and Audio (6-channels) streams. This is selected by DECODESEL=3.

# 4.6.4.1 Downsampling filter

When decoding PCM/LPCM streams encoded at 96kHz, it is possible to use a filter that downsamples the stream from 96kHz to 48kHz. The chip can not output streams at 96kHz. The register DWSMODE is used to configure the use of this filter.

#### 4.6.5 MLP

MLP is a lossless coding system for use on digital audio data originally represented as linear PCM. MLP is mandatory in DVD Audio. It allows transmission and storage of up to 6 channels. each up to 24 bits precision and with sample rates between 44.1 KHz and 192KHz.

- DECODESEL = 8

#### 4.6.6 CDDA

- DECODESEL = 5

#### 4.6.7 Beep Tone

- DECODESEL = 7

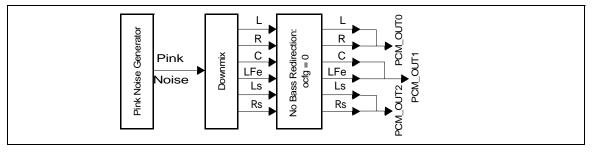

#### 4.6.8 Pink noise generator

The pink noise generator can be used to position the speakers in the listening room so to benefit of the best listening conditions.

The decoder must be programmed so to generate pink noise by writing 4 in the DECODESEL register. The DOWNMIX register is used to select independently the channels on which the pink noise will be output.

When generating pink noise, the output configuration should be: OCFG=0 and PCM\_SCALE=0.

#### Figure 13. Pink Noise Generator Flow

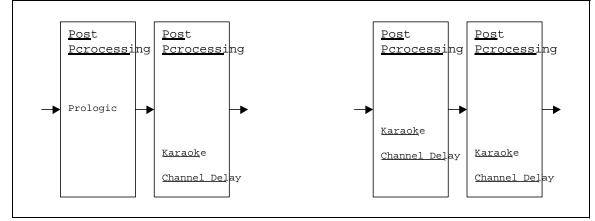

#### 4.7 Post Processing

The following post processing alghorithms are available

#### 4.7.1 Prologic

#### Pro Logic Compatible Downmix

The STA310 can decode an AC-3 multichannel bitstream and encode it to provide a 2-channel Pro Logic compatible output (Lt, Rt). These 2 channels are the result of a specific downmix referred to as Pro Logic compatible. This downmix is selected by the register DOWNMIX. The 2 channels can be used as the input of a Pro Logic decoder and player (e.g. home theatre).

#### Pro Logic Decoding

The STA310 can decode a 2-channel Pro Logic bitstream. The 2 channels could come from a CD player, an AC-3 2-channel bitstream or an MPEG1 bitstream. The 2-channel bitstream can be converted into a 4-channel output (L, R, C, S). The surround (S) is simultaneously sent on Ls and Rs channels. A Pro Logic downmix en-

22/90

ables to configure which channels to output on PCM data. This is done through the register PL\_DWN.

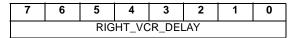

An auto-balance feature is available and activated through PL\_AB register. The delay on surround channel is configurable thanks to the LSDLY register (while resetting the RSDLY register).

The bass redirection is performed after the Pro Logic decode. The same bass redirection configuration than those available in non-Pro Logic modes can be used except that the surround channels will not be added to the bass redirection. In the case of AC-3 or MPEG the STA310 is therefore capable of first decoding the AC-3 or MPEG stream then performing the Pro Logic decode.

#### 4.7.2 Others

- Karaoke system

- Bass Management + Volume Control

- Deemphasis

- DC Remove

#### 4.8 How to choose a decoder

To set up the device you have to select two registers.

The first one is DECODESEL for Audio data type,

The second one is STREAMSEL for Transport data type,

The STREAMSEL can be set-up as follows:

- 0= PES

- 1= PES DVD Video

- 2= Packet MPEG1

3= Elementary stream or IEC.60958

- 4= reserved

- 5= IEC.61937

- 6= PES DVD Audio

So the possible configurations on listed in the following table:

#### Table 6. Possible configurations:

| STREAMSEL | DECODESEL | MODE                                                  |

|-----------|-----------|-------------------------------------------------------|

| 0         | 0         | MPEG2 PES carrying Dolby Digital (ATSC)               |

| 0         | 1         | MPEG2 PES carrying MPEG1 frames                       |

| 0         | 2         | MPEG2 PES carrying MPEG2 frames                       |

| 1         | 0         | MPEG2 PES carrying Dolby Digital frames for DVD Video |

| 1         | 2         | MPEG2 PES carrying MPEG2 frames for DVD Video         |

| 1         | 3         | MPEG2 PES carrying Linear PCM frames for DVD Video    |

| 1         | 1         | MPEG1 packet carrying MPEG1 frames                    |

| 3         | 0         | Dolby Digital frame elementary streams                |

| 3         | 1         | MPEG1 frame elementary streams                        |

| 3         | 2         | MPEG2 frame elementary streams                        |

| 3         | 3         | Stereo PCM (16bits samples)                           |

| 3         | 4         | Pink Noise Generator                                  |

|  | 5 | 7 |

|--|---|---|

|--|---|---|

| STREAMSEL | DECODESEL | MODE                                        |  |  |  |  |

|-----------|-----------|---------------------------------------------|--|--|--|--|

| 3         | 5         | CDDA frames                                 |  |  |  |  |

| 3         | 7         | Beep Tone Generator                         |  |  |  |  |

| 3         | 9         | MP3 frame elementary streams                |  |  |  |  |

| 5         | 0         | IEC61937 Input with Dolby Digital frames    |  |  |  |  |

| 5         | 1         | IEC61937 Input with MPEG1 frames            |  |  |  |  |

| 5         | 2         | IEC61937 Input with MPEG2 frames            |  |  |  |  |

| 6         | 3         | MPEG2 PES carrying Linear PCM for DVD Audio |  |  |  |  |

| 6         | 8         | MPEG2 PES carrying MPL for DVD Audio        |  |  |  |  |

#### 4.9 How to Program a Post Processing

#### 4.9.1 2 registers for the mode:

PDEC (0x62) to define the type of PostProcessing

| PDEC | MODE                   |  |  |

|------|------------------------|--|--|

| 0x01 | Prologic               |  |  |

| 0x02 | MPEG 1/2 Dynamic Range |  |  |

| 0x08 | Double Stereo          |  |  |

| 0x10 | DC Remove              |  |  |

| 0x20 | Deemphasis filter      |  |  |

#### 4.9.2 1 or 2 registers to control the "PostProcessing"

Prologic decoder (PDEC = 0x01):

| PL ABL WS (0x64)  | Effect                     |

|-------------------|----------------------------|

| 1                 | AutoBalance                |

| 2                 | WideSurround               |

| PL DOWNMIX (0x65) | Prologic DownMix           |

| 0,1,2             | Prologic not applied       |

| 3                 | 3/0 (L, R, C)              |

| 4                 | 2/1 (L, R, Ls) Phantom     |

| 5                 | 3/1 (L, R, Ls)             |

| 6                 | 2/2 (L, R, Ls, Rs) Phantom |

| 7                 | 3/2 (L, C, R, Ls, Rs)      |

**Remark:** When playing "Dolby Digital Prologic encoded", if PL\_DOWNMIX is correctly set, Prologic decoder' is automatically applied even if the register "PDEC" different to 1.

## 4.10 What Can Be Processed at the Same Time Same Time 1

#### Same Time 2

#### 5 PCM OUTPUT CONFIGURATIONS

#### 5.1 Output configurations

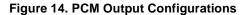

The figure below shows the different configurations supported at PCM output stage. They are selected by the OCFG register contents.

- In configuration 1, 3 and 4, the main channels are attenuated by 18.5dB, and the LFE by 8.5dB before summing.

After digital/analog conversion, the subwoofer preamplifier has to compensate for the different gains of the main channels and subwoofer.

- In configuration 2, the main channels are attenuated by 16dB and the LFE by 6dB before processing.

- In configuration 0, outputs are only scaled and rounded (see next section).

The same configurations will be used in case of a decoded Pro Logic program with the exception that the surround channels will not be added to the bass redirection (the surround channels of a Pro Logic program are band limited and bass is considered as leakage).

#### 5.2 PCM scaling

PCM scaling is needed for every decoding mode (AC3, Pro Logic, MPEG, PCM). It is applied at the end of the filtering steps before PCM output, allowing maximum effective word width for most of the signal processing before.

Master volume (PCM\_SCALE register) and balances (BAL\_LR and BAL\_SUR registers) are implemented for PCM scaling.

#### 5.3 Output quantization

For optimal results for 16/18/20-bit DACs, a quantization with rounding is applied together with the PCM scaling. The sample value is multiplied by a rounding factor and rounded to 24 bits. The result is then left shifted (4/6/8)

for PCM output.

The output precision is selectable from the 16bits/word to 24 bits/word by configuring the field PREC in the register PCMCONF.

#### 5.4 Interface and output formats

The decoded audio data are output in serial PCM format.

The interface consists of the following signals

| PCM data, output,                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------|

| Bit clock (or serial clock), output,                                                                                   |

| Word clock (or Left/Right channel select clock), output,                                                               |

| PCM clock, input or output (see <crossref><blueht>Clocks <blueht>on page 11 for details).</blueht></blueht></crossref> |

|                                                                                                                        |

**LJ**

#### 26/90

Downloaded from Elcodis.com electronic components distributor

#### 5.4.1 Output precision and format selection

Output precision is selectable from 16 bits/word to 24 bits/word by setting the output precision select, in the PC-MCONF (16-, 18-, 20- and 24-bit mode) register.

In 16-bit mode, data may be output either with the most significant bit first or least significant bit first. This is configured by the contents of the field ORD in the PCMCONF register.

When PCMCONF.PREC is more than 16 bits, 32 bits are output for each channel. In this configuration, the field FOR of register PCMCONF is used to select Sony or I<sup>2</sup>S- compatible format. The field DIF of PCMCONF is used to position the 18, 20 or 24 bits either at the beginning or at the end of each 32-bit frame.

|      |          | 16 SC      | CLK cycles | 6          |                  |        |                         |                     |           |            |        |                                    |

|------|----------|------------|------------|------------|------------------|--------|-------------------------|---------------------|-----------|------------|--------|------------------------------------|

| LRCL | ĸ        |            |            |            | 16 SCLK cycl     | es     |                         |                     |           |            |        |                                    |

| PCM_ | OUT[2:0] | M<br>S     |            | L M<br>S S |                  | L<br>S | PCMCONF.OR              | 2D = 0,             | , PCMC    | ONF.PREC   | C is   | 16 bits mode                       |

| PCM_ | OUT[2:0] | L<br>S     |            | M L<br>S S |                  | M<br>S | PCMCONF.OR              | D = 1,              | PCMC      | ONF.PREC   | ) is   | 16 bits mode                       |

|      |          |            | 32 S       | CLK o      | cycles           |        |                         |                     |           |            |        |                                    |

| LRCL | ĸ        |            |            |            |                  |        | 32                      | SCLK                | ( cycles  | i          |        |                                    |

| PCM_ | OUT[2:0] | M<br>S 18, | 20 or 24   | bits       | L 0              |        | M<br>S 18, 20 or 2      | 4 bits              | L<br>S    | 0          |        | PCMCONF.FOR = 1<br>PCMCONF.DIF = 1 |

| PCM_ | OUT[2:0] | C          | ) N<br>S   | 1<br>; 18  | , 20 or 24 bits  | L<br>S | 0                       | SMS 1               | l 8, 20 o | or 24 bits | L<br>S | PCMCONF.FOR = 0<br>PCMCONF.DIF = 0 |

| PCM_ | OUT[2:0] | 0 M<br>S   | 18, 20 o   | r 24 b     | oits L C         |        | 0 <mark>M</mark> 18, 20 | or 24               | bits      | S 0        |        | PCMCONF.FOR = 0<br>PCMCONF.DIF = 1 |

| PCM_ | OUT[2:0] | MS         | BB S       |            | s, 20 or 24 bits | L<br>S | MSB                     | M<br>S <sup>1</sup> | 18, 20 o  | or 24 bits | L<br>S | PCMCONF.FOR = 1<br>PCMCONF.DIF = 0 |

#### Figure 15. Output formats

| M CONF.PEC    | PCM<br>CONF.ORD | PCM<br>CONF.FOR | PCM<br>CONF.DIF | DATA IN SAMPLE<br>MEMORY DATA<br>[23:0] | DATA SENT ON THE<br>PCM SERIAL OUTPUT<br>(LEFT BIT FIRST) |

|---------------|-----------------|-----------------|-----------------|-----------------------------------------|-----------------------------------------------------------|

| 0:16-bit mode | 1               | NA              | NA              | {d23-d8}-{8*0}                          | {d8-d23}: 16 bits                                         |

| 0:16-bit mode | 0               | NA              | NA              | {d23-d8}-{8*0}                          | {d23-d8}: 16 bits                                         |

| 1:18-bit mode | NA              | 0               | 0               | {d23-d6}-{6*0}                          | {13*0}{0}{d23-d6}: 32 bits                                |

| 1:18-bit mode | NA              | 0               | 1               | {d23-d6}-{6*0}                          | {0}{d23-d6}{13*0}: 32 bits                                |

| 1:18-bit mode | NA              | 1               | 0               | {d23-d6}-{6*0}                          | {14*d23}{d26*d6}: 32 bits                                 |

| 1:18-bit mode | NA              | 1               | 1               | {d23-d6}-{6*0}                          | {d23-d6}{14*0}: 32 bits                                   |

| 2:20-bit mode | NA              | 0               | 0               | {d23-d4}-{4*0}                          | {11*0}{0}{d23-d4}: 32 bits                                |

| 2:20-bit mode | NA              | 0               | 1               | {d23-d4}-{4*0}                          | {0}{d23-d4}{11*0}: 32 bits                                |

| 2:20-bit mode | NA              | 1               | 0               | {d23-d4}-{4*0}                          | {12*d23}{d23-d4}: 32 bits                                 |

| 2:20-bit mode | NA              | 1               | 1               | {d23-d4}-{4*0}                          | {d23-d4}{12*0}: 32 bits                                   |

| 3:24-bit mode | NA              | 0               | 0               | {d23-d0}                                | {6*0}{0}{d23-d0}: 32 bits                                 |

| 3:24-bit mode | NA              | 0               | 1               | {d23-d0}                                | {0}{d23-d0}{7*0}: 32 bits                                 |

| 3:24-bit mode | NA              | 1               | 0               | {d23-d0}                                | {8*d23}{d23-d0}: 32 bits                                  |

| 3:24-bit mode | NA              | 1               | 1               | {d23-d0}                                | {d23-d0}{8*0}: 32 bits                                    |

How to read the above table:

The first 4 columns list the possible configurations for output formats on the PCM outputs. The 5th column gives the description of the internal 24-bit decoded, scaled and rounded audio samples as they are stored in memory. These 24 bits are referred to as d23, d22,..., d0, where MSB=d23, LSB=d0. The last column describes the sequence of bits that are output on PCM\_OUT according to the selected format.

Example 1: in 16-bit mode, with PCMCONF.ORD=1: In memory, 24 bits are stored, where only the 16 MSB bits (d23, d22,... to d8) are significant and the 8 remaining bits are 0. This is noted: {d23-d8} {8\*0}. The data are sent LSB first, i.e. d8 is sent first and d23 is sent last. This is noted {d8-d23}. 16 bits only are transmitted per channel.

Example 2: in 20-bit mode (PCMCONF.ORD field is meaningless in this mode), with PCMCONF.FOR=1 and PCMCONF.DIF=0: In memory, 24 bits are stored, where only the 20 MSB (d23 to d4) are significant and the remaining 4 LSB are 0.This is noted: {d23-d4} {4\*0}. 32 bits are transmitted per channel on the PCM outputs: the 12 first transmitted bits are d23, the last bits are d23 to d4, where d23 is transmitted first. This is noted: {12\*d23} {d23-d4}.

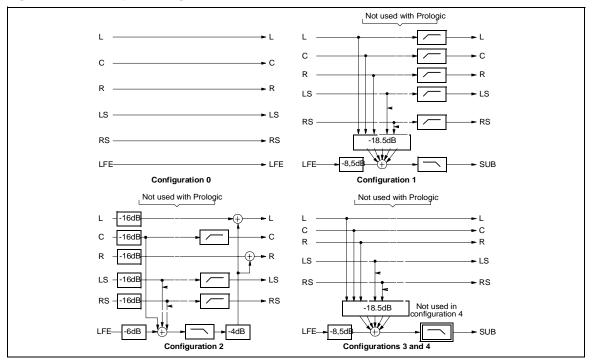

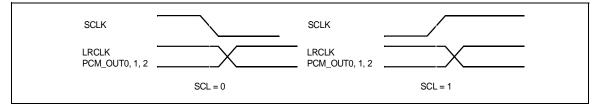

#### 5.4.2 Clocks polarity selection

The polarity of the PCM serial output clock, SCLK and the polarity of the PCM word clock LRCLK are selected by the field SCL and INV respectively, in the PCMCONF register.

#### 5.4.3 I<sup>2</sup>S format compatible outputs

To output I<sup>2</sup>S compatible data, the PCMCONF register must be configured as follows

| PCMCONF.DIF | = 1 | not right padded,        |

|-------------|-----|--------------------------|

| PCMCONF.FOR | = 0 | I <sup>2</sup> S format, |

| PCMCONF.INV | = 0 | do not invert LRCLK,     |

| PCMCONF.SCL | = 0 | do not invert SCLK.      |

#### 5.4.4 Sony format compatible outputs

| PCMCONF.FOR | = 1 | Sony format,  |

|-------------|-----|---------------|

| PCMCONF.INV | = 1 | Invert LRCLK. |

#### Figure 16. SCLK Polarity

#### Figure 17. LRCLK Polarity

#### 6 S/PDIF OUTPUT

The S/PDIF output pad is a TTL output pad with slew rate control. The output DC capability is 4 mA. The voltage drop is 3V. This output must be connected to a TTL driver before the transformer.

The S/PDIF output supports SPDIF and IEC-61937 standards. Several registers must be initialized to configure the SPDIF output:

- The category code must be entered in the IEC958\_CAT register. It is related to the type of application. The category code is specified in the Digital Output Interface standard.

- The status bits that will be transmitted on the SPDIF output, must be programmed in the IEC958\_STATUS register.

- IEC clock setting must be specified in the IEC958\_CONF register.

- The data type dependent information can be specified in the IEC958\_DTDI register.

- The S/PDIF type is selected through the IEC958\_CMD register: the IEC unit can output decoded data (PCM mode), encoded data, or null data.

Note: 1. The SPDIF output handles only 48kHz or 44.1kHz sample rates.

#### 6.1 SPDIF output

When configured in SPDIF mode, the S/PDIF output is used to transmit either the L/R channels (PCMOUT1) or VCR\_L/VCR\_R (PCMOUT0).

The selection is done by choosing the PCM mode and AUX = 1 in the register SPDIF\_CMD and resetting the COM status of SPDIF\_STATUS register.

#### 6.2 IEC-61937 output

When configured in IEC-61937 mode, the S/PDIF output is used to transmit encoded data taken directly from the frame buffer.

The selection is done by choosing the encoded mode (ENC mode) in the register IEC958\_CMD and setting the bit COM in IEC958\_STATUS register.

The decompressed data are output simultaneously on the PCM\_OUT outputs.

Latency in software versions 6 and later

For software versions 6 and later, when choosing to output encoded S/PDIF data, a latency is automatically inserted between S/PDIF output and PCM outputs. The PCM outputs are delayed compared to the SPDIF output.

The latency value is defined by standards and applied when the auto-latency mode is selected.

#### AC3 decoding

Latency = 1/Fs \* (1/3 \* Framesize + 256)

= 1/Fs \* (32 \* Datarate/Fs + 256)

MPEG decoding

Latency = 1/Fs \* (36 \* Datarate/Fs + 96)

where Fs is the sampling frequency in kHz, Framesize is expressed in 16-bit words, Datarate is the bit rate in kbits per second.

The latency insertion can not be disabled however it can be programmed to values different from those required in the standard by selecting the user-programmable-latency mode (by setting the bit 7 of IEC858\_CONF regis-

57

ter). In this case, the latency is specified in the IEC958\_LATENCY register.

Note that there are minimum and maximum values to respect

#### Table 7.

| AC-3                |                           | MPEG               |                      |  |

|---------------------|---------------------------|--------------------|----------------------|--|

| Min. Latency        | Min. Latency Max. Latency |                    | Max. Latency         |  |

| 256<br>samples / Fs | 1536<br>samples / Fs      | 96<br>samples / Fs | 1152<br>samples / Fs |  |

If those limits are not respected, an error interrupt occurs corresponding to error type: LATENCY\_TOO\_BIG, which automatically makes the chip switch to auto\_latency mode.

For software versions prior to 6, the latency is not implemented.

#### 6.3 PCM null data

When configured in muted mode (in the IEC958\_CMD register), the outputs are PCM null data. This can be used to synchronize the external IEC receiver.

#### 7 INTERRUPTS

#### 7.1 Interrupt register

The decoder can signal to the external controller that an interrupt has occurred during the execution. The register INTE enables to select which interrupts will be generated and output on the IRQ output pin.

When an interrupt occurs, the signal IRQ is activated low and the controller can check which interrupt was detected by reading the register INT.

According to the type of interrupt detected, other information can be obtained by reading associated registers (such as stream header, type of error detected, PTS value).

#### 7.2 IRQ Signal

This signal, IRQ, is a three-state line. This signal indicates (by going low) when an interrupt occurs. It returns to high level once the corresponding bit in the interrupt register has been cleared.

#### 7.3 Error concealment

Errors are signaled as interrupts by the audio core. The error list is provided in. Most of the errors are automatically handled by the core, some require that software be changed.

#### AC-3 decoding errors:

Those errors are signaled in the ERROR register but handled directly by the core. Nothing can be done by the software. They signal that something wrong happened during the decoding. The core soft mutes the frame and continues to decode.

#### MPEG decoding errors:

Those errors are also signaled in the ERROR register but handled directly by the core. Nothing can be done by the software. They signal that something wrong happened during the decoding. The core soft mutes the frame and continues to decode. Only one error in this category indicates a programming error: if triggering the

**\$7**

MPEG\_EXT\_CRC\_ERROR, the bit MC\_OFF must be set. This indicates that the decoder tries to decode more than 2 channels whereas the incoming stream contains only 2 channels.

Packet and audio synchronization errors:

Those errors are handled internally, and usually indicate that the incoming bitstream is incorrect or incorrectly input to the chip. In those cases, the decoder resets the corresponding parsing stage (packet or audio parser) then searches for the next correct frame.

Miscellaneous errors:

- LATENCY\_TOO\_BIG error indicates a problem of latency programming which is superior to the maximum authorized value.

Change the latency value or switch to auto-latency mode to solve the problem. Other miscellaneous errors are internally handled.

#### 8 AUDIO/VIDEO SYNCHRONIZATION

#### 8.1 Presentation time stamp detection

#### 8.1.0.1 PTS Signal

This signal, PTS, is used to signal the detection of a Presentation Time Stamp in a stream, for audio/video synchronization. When a PTS is detected, the signal PTS goes low during one LRCLK period. It is generated while the PCM are output, so to enable the use of an external counter to synchronize the STA310 with a video decoder.

The signal is activated, even if PTS interrupt is not enabled.

#### 8.1.1 PTS interrupt

When enabled through the INTE register, the interrupt <u>PTS</u> is generated when a PTS is detected. The interrupt is signalled on the IRQ output, which goes low. The IRQ signal is de-activated once the PTS bit has been cleared in INT register by reading the PTS Most Significant Bit.

#### 8.1.2 PTS interrupt and signal relative timings

The IRQ configured as PTS interrupt is output before the PTS signal. The PTS signal is activated at last one period of LRCLK after the IRQ signal.

#### 8.2 Frames skip capability

When the audio decoder is late compared to the video decoder, the decoder is able to skip frames. Writing 1 in the SKIP\_FRAME register makes the decoder ignore the next incoming frame. Once skipping the frame, it continues to decode the stream, and the SKIP\_FRAME register is automatically reset.

#### 8.3 Frames repeat capability

When the audio decoder is ahead of the video decoder, the decoder can repeat frames. Writing 1 in the REPEAT\_FRAME register makes the decoder repeat the current frame. Once repeating the frame, the chip plays the next incoming frame, and the REPEAT\_FRAME register is reset.

#### 9 REGISTER MANUAL

#### 9.1 Introduction

The STA310 device contains 256 registers.

Two types of registers exist:

- From address 0x00 to 0x3F, the registers are real registers that can be initialized after reset.

- From address 0x40 to 0x100, they are memory locations. This means that the registers located at the address 0x40 to 0x100 can have different meanings and usage according to the mode in which the device operates.

Be careful that they can not be hardware reset: they contain undefined values at reset and require to be initialized after each hardware reset.

In this document, only the user registers are described.

The undocumented registers are reserved. These registers must never be accessed (neither in Read nor in Write mode).

The Read only registers must never be written

#### 9.2 Register map by function

| Code | Description                                                                                                                                                                                                                                                                                                    |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| (a)  | Register modification is ALWAYS taken into account by the audio decoder.<br>Any change to these registers is taken into account immediately.                                                                                                                                                                   |  |  |

| (b)  | Register modification is taken into account AFTER EVERY DECODED DATA BLOCK or JUST AFTER<br>RESET (soft or hard).<br>The decoded block is related to the granularity of the computation in the audio decoder software.<br>A block is 256 samples in Dolby Digital, 96 samples in MPEG, 80 samples in LPCM/PCM. |  |  |

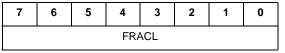

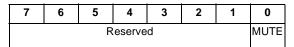

| (f)  | Register modification is taken into account AFTER EVERY DATA FRAME.<br>A frame is: 1152 samples in MPEG I/II, 1536 samples in Dolby Digital, 384 samples in MPEG-1 layer 1, 80 samples in LPCM/PCM.                                                                                                            |  |  |