February 2000

# DS75451/2/3 **Series Dual Peripheral Drivers General Description**

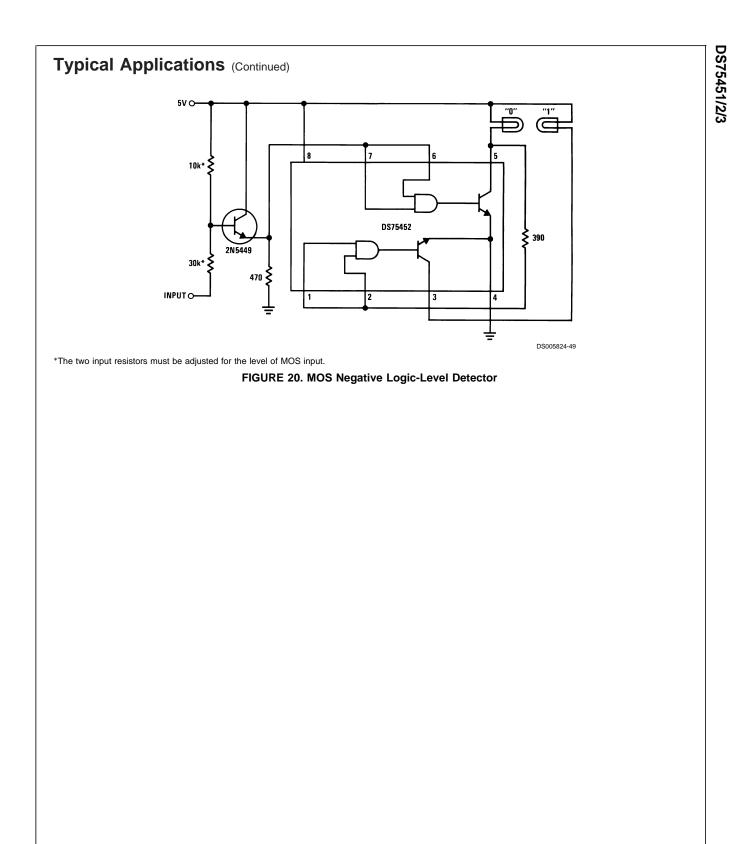

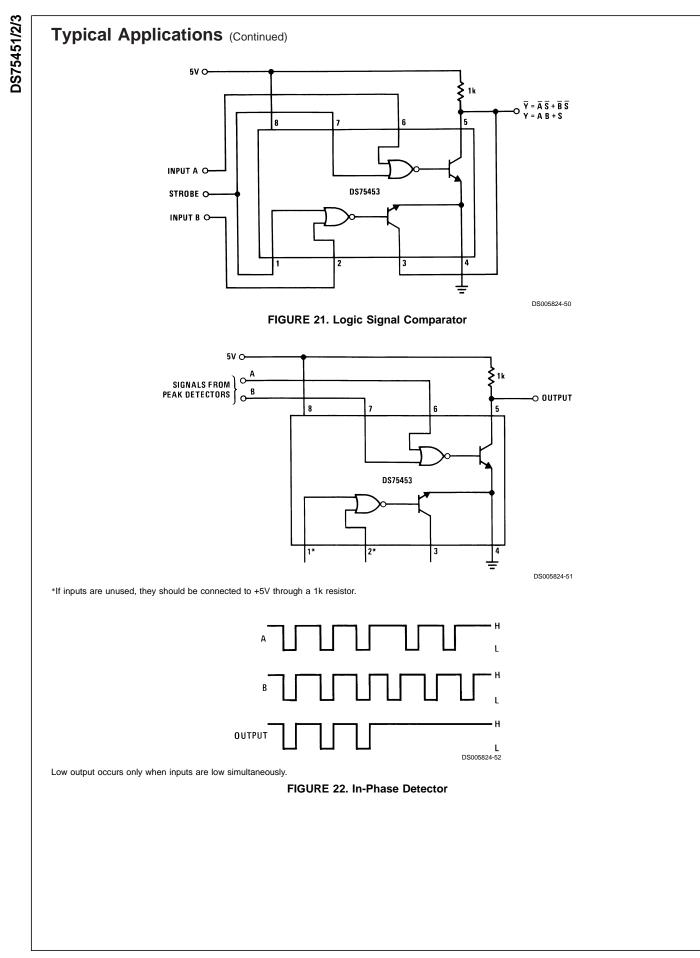

The DS7545X series of dual peripheral drivers is a family of versatile devices designed for use in systems that use TTL logic. Typical applications include high speed logic buffers, power drivers, relay drivers, lamp drivers, MOS drivers, bus drivers and memory drivers.

The DS75451, DS75452 and DS75453 are dual peripheral AND, NAND and NOR drivers, respectively, (positive logic) with the output of the logic gates internally connected to the bases of the NPN output transistors.

## Features

- 300 mA output current capability

- High voltage outputs

- No output latch-up at 20V

- High speed switching

- Choice of logic function

- TTL compatible diode-clamped inputs

- Standard supply voltages

- Replaces TI "A" and "B" series

DS005824-2

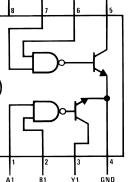

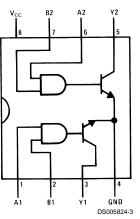

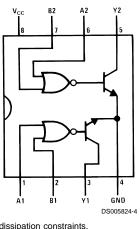

Connection Diagrams (Dual-In-Line and Metal Can Packages)

**Top View**

\*See (Note 5) and Appendix E regarding S.O. package power dissipation constraints. Order Number DS75452M or DS75452N

**Top View** Order Number DS75451M or DS75451N

\*See (Note 5) and Appendix E regarding S.O. package power dissipation constraints.

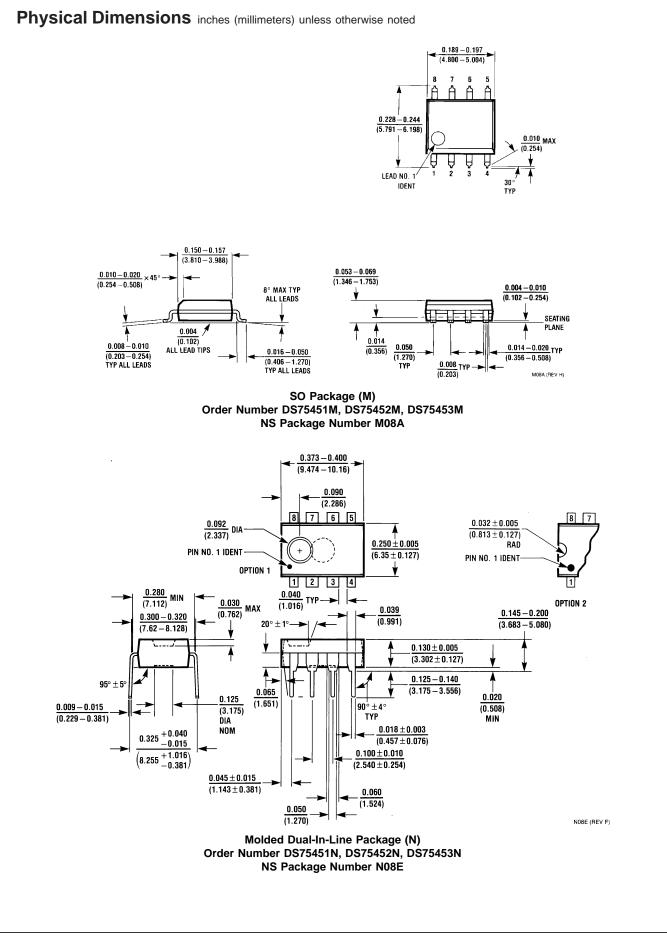

**Top View** Order Number DS75453M or DS75453N See NS Package Numbers M08A\* or N08E

© 2001 National Semiconductor Corporation DS005824

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage, (V <sub>CC</sub> ) (Note 2) | 7.0V   |

|---------------------------------------------|--------|

| Input Voltage                               | 5.5V   |

| Inter-Emitter Voltage (Note 3)              | 5.5V   |

| Output Voltage (Note 4)                     | 30V    |

| Output Current (Note 5)                     | 300 mA |

| Maximum Power (Note 5)                      |        |

| Dissipation <sup>†</sup> at 25°C            |        |

| Molded DIP Package                   | 957 mW          |

|--------------------------------------|-----------------|

| SO Package                           | 632 mW          |

| Storage Temperature Range            | –65°C to +150°C |

| Lead Temperature (Soldering, 4 sec.) | 260°C           |

# **Operating Conditions**

|                                                                | Min           | Max           | Units     |

|----------------------------------------------------------------|---------------|---------------|-----------|

| Supply Voltage, (V <sub>CC</sub> )                             | 4.75          | 5.25          | V         |

| Temperature, (T <sub>A</sub> )                                 | 0             | +70           | °C        |

| <sup>†</sup> Derate molded package 7.7 mW/°C mW/°C above 25°C. | above 25°C, o | derate SO pac | kage 7.56 |

## **Electrical Characteristics**

(Notes 6, 7)

| Sumbol           | Parameter                                 |                                               |                          | Conditions               |                  | Min | Tun  | Max  | Units |

|------------------|-------------------------------------------|-----------------------------------------------|--------------------------|--------------------------|------------------|-----|------|------|-------|

| Symbol           |                                           |                                               |                          | Conditions               |                  |     | Тур  | wax  |       |

| V <sub>IH</sub>  | High-Level Input Voltage                  | (Figure 7)                                    |                          |                          |                  | 2   |      |      | V     |

| VIL              | Low-Level Input Voltage                   |                                               |                          |                          |                  |     |      | 0.8  | V     |

| VI               | Input Clamp Voltage                       | $V_{CC} = Min$                                | , $I_1 = -12 \text{ mA}$ |                          |                  |     |      | -1.5 | V     |

| V <sub>OL</sub>  | Low-Level Output Voltage                  | V <sub>CC</sub> =                             | $V_{IL} = 0.8V$          | I <sub>OL</sub> = 100 mA | DS75451, DS75453 |     | 0.25 | 0.4  | V     |

|                  |                                           | Min,                                          |                          | I <sub>OL</sub> = 300 mA | DS75451, DS75453 |     | 0.5  | 0.7  | V     |

|                  |                                           | (Figure 7)                                    | $V_{IH} = 2V$            | I <sub>OL</sub> = 100 mA | DS75452          |     | 0.25 | 0.4  | V     |

|                  |                                           |                                               |                          | I <sub>OL</sub> = 300 mA | DS75452          |     | 0.5  | 0.7  | V     |

| I <sub>он</sub>  | High-Level Output Current                 | V <sub>CC</sub> =<br>Min.                     | V <sub>OH</sub> = 30V    | $V_{IH} = 2V$            | DS75451, DS75453 |     |      | 100  | μA    |

|                  |                                           | ( <i>Figure 7</i> )                           |                          | $V_{IL} = 0.8V$          | DS75452          |     |      | 100  | μA    |

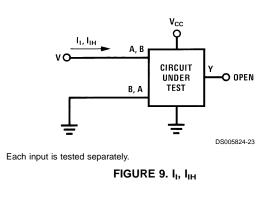

| l <sub>l</sub>   | Input Current at Maximum<br>Input Voltage | $V_{CC} = Max, V_1 = 5.5V, (Figure 9)$        |                          |                          |                  |     | 1    | mA   |       |

| I <sub>IH</sub>  | High-Level Input Current                  | V <sub>CC</sub> = Max                         | $k_{1} = 2.4 V_{1} (R)$  | -igure 9 )               |                  |     |      | 40   | μA    |

| $I_{IL}$         | Low-Level Input Current                   | V <sub>CC</sub> = Max                         | $k_{1} = 0.4 V_{1} (R)$  | -igure 8)                |                  |     | -1   | -1.6 | mA    |

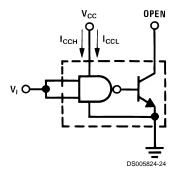

| I <sub>CCH</sub> | Supply Current, Outputs                   | V <sub>CC</sub> = V <sub>I</sub> = 5V DS75451 |                          |                          | 7                | 11  | mA   |      |       |

|                  | High                                      | Max,<br>( <i>Figure</i>                       | Max, $V_1 = 0V$ DS75452  |                          | DS75452          |     | 11   | 14   | mA    |

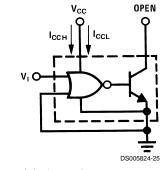

|                  |                                           | 10)                                           | $V_I = 5V$               |                          | DS75453          |     | 8    | 11   | mA    |

| I <sub>CCL</sub> | Supply Current, Outputs                   | V <sub>CC</sub> =                             |                          |                          | DS75451          |     | 52   | 65   | mA    |

|                  | Low                                       | Max,<br>( <i>Figure</i>                       | $V_1 = 5V$               |                          | DS75452          |     | 56   | 71   | mA    |

|                  |                                           | ( <i>r igure</i><br>10)                       | $V_1 = 0V$               |                          | DS75453          |     | 54   | 68   | mA    |

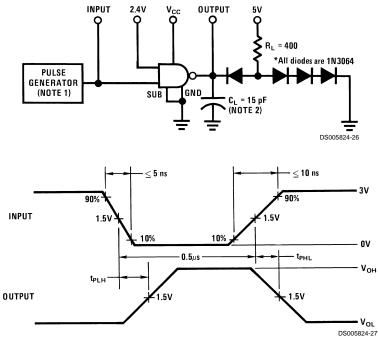

## **Switching Characteristics**

$(V_{CC} = 5V, T_A = 25^{\circ}C)$

| Symbol           | Parameter                                    | Conditions                                                                                 |            | Min                  | Тур | Max | Units |

|------------------|----------------------------------------------|--------------------------------------------------------------------------------------------|------------|----------------------|-----|-----|-------|

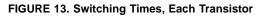

| t <sub>PLH</sub> | Propagation Delay Time, Low-to-High          | $C_{L} = 15 \text{ pF}, R_{L} = 50\Omega,$                                                 | DS75451    |                      | 18  | 25  | ns    |

|                  | Level Output                                 | I <sub>O</sub> ≈ 200 mA, ( <i>Figure 14</i> )                                              | DS75452    |                      | 26  | 35  | ns    |

|                  |                                              |                                                                                            | DS75453    |                      | 18  | 25  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time, High-to-Low          | $C_{L} = 15 \text{ pF}, R_{L} = 50\Omega,$                                                 | DS75451    |                      | 18  | 25  | ns    |

|                  | Level Output                                 | I <sub>O</sub> ≈ 200 mA, ( <i>Figure 14</i> )                                              | DS75452    |                      | 24  | 35  | ns    |

|                  |                                              |                                                                                            | DS75453    |                      | 16  | 25  | ns    |

| t <sub>TLH</sub> | Transition Time, Low-to-High Level<br>Output | $C_L = 15 \text{ pF}, R_L = 50\Omega, I_O \approx 200 \text{ mA},$<br>( <i>Figure 14</i> ) |            |                      | 5   | 8   | ns    |

| t <sub>THL</sub> | Transition Time, High-to-Low Level<br>Output | $C_L$ = 15 pF, $R_L$ = 50 $\Omega$ , $I_O \approx$ 200 mA, (Figure 14 )                    |            |                      | 7   | 12  | ns    |

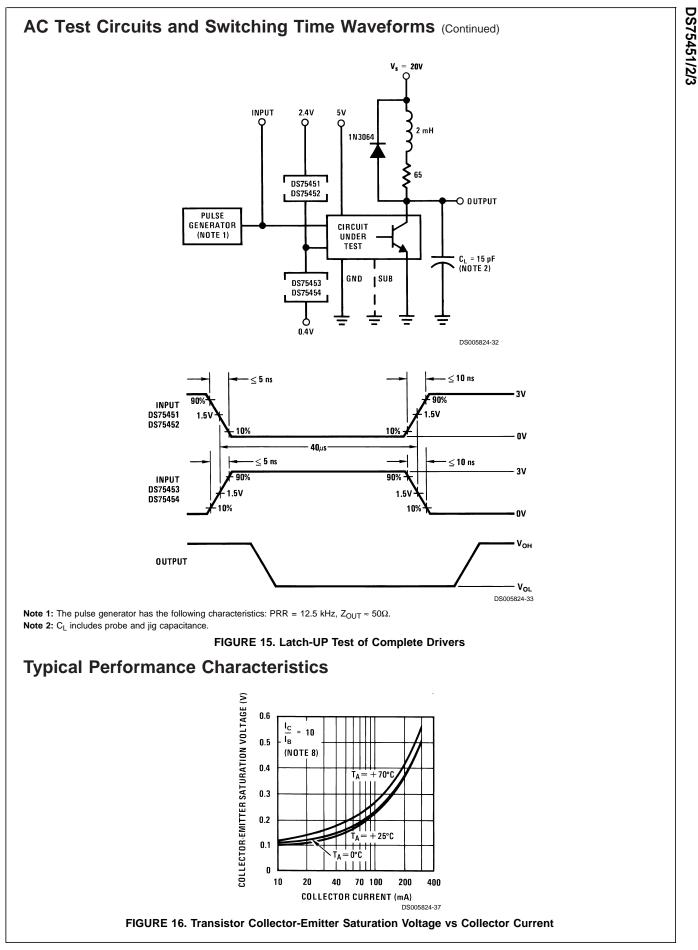

| V <sub>OH</sub>  | High-Level Output Voltage after<br>Switching | $V_{\rm S}$ = 20V, $I_{\rm O}$ $\approx$ 300 mA, (F                                        | Figure 15) | V <sub>S</sub> – 6.5 |     |     | mV    |

## Switching Characteristics (Continued)

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Voltage values are with respect to network ground terminal unless otherwise specified.

Note 3: The voltage between two emitters of a multiple-emitter transistor.

Note 4: The maximum voltage which should be applied to any output when it is in the "OFF" state.

Note 5: Both halves of these dual circuits may conduct rated current simultaneously; however, power dissipation averaged over a short time interval must fall within the continuous dissipation rating.

Note 6: Unless otherwise specified min/max limits apply across 0°C to +70°C range. All typicals are given for  $V_{CC}$  = +5V and  $T_A$  = 25°C.

Note 7: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as max or min on absolute value basis.

## **Truth Tables** (H = high level, L = low level)

### DS75451

| Α | В | Y             |

|---|---|---------------|

| L | L | L (ON State)  |

| L | Н | L (ON State)  |

| Н | L | L (ON State)  |

| Н | Н | H (OFF State) |

#### DS75452

| Α | В | Y             |

|---|---|---------------|

| L | L | H (OFF State) |

| L | Н | H (OFF State) |

| н | L | H (OFF State) |

| н | Н | L (ON State)  |

#### DS75453

| Α | В | Y             |  |

|---|---|---------------|--|

| L | L | L (ON State)  |  |

| L | Н | H (OFF State) |  |

| н | L | H (OFF State) |  |

| н | Н | H (OFF State) |  |

# DS75451/2/3

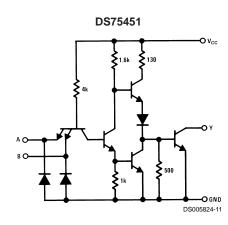

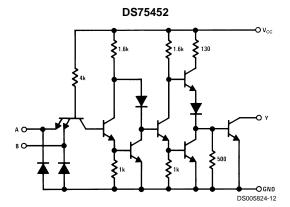

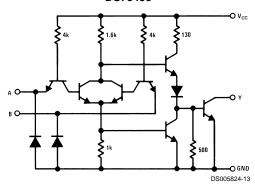

# Schematic Diagrams

Resistor values shown are nominal.

Resistor values shown are nominal.

DS75453

Resistor values shown are nominal.

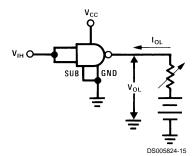

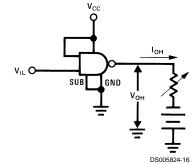

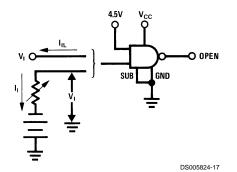

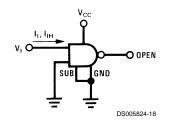

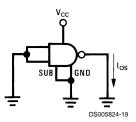

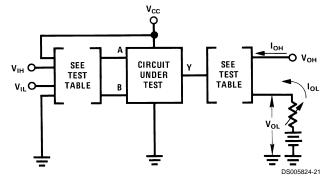

## **DC Test Circuits**

Both inputs is tested simultaneously.

FIGURE 1.  $V_{IH}$ ,  $V_{OL}$

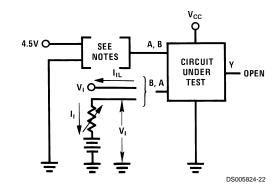

Each input is tested separately.

Each input is tested separately.

FIGURE 4. I<sub>I</sub>, I<sub>IH</sub>

FIGURE 5. Ios

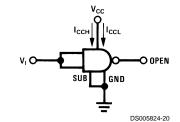

Both gates are tested simultaneously.

FIGURE 6. I<sub>CCH</sub>, I<sub>CCL</sub>

## DC Test Circuits (Continued)

| Circuit | Input<br>Under  | Other           | Output          |                 |

|---------|-----------------|-----------------|-----------------|-----------------|

| Circuit | Test            | Input           | Apply           | Measure         |

| DS75451 | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>он</sub> | I <sub>OL</sub> |

|         | V <sub>IL</sub> | V <sub>cc</sub> | I <sub>OL</sub> | V <sub>OL</sub> |

| DS75452 | V <sub>IH</sub> | V <sub>IH</sub> | I <sub>OL</sub> | V <sub>OL</sub> |

|         | V <sub>IL</sub> | V <sub>cc</sub> | V <sub>он</sub> | I <sub>он</sub> |

| DS75453 | V <sub>IH</sub> | Gnd             | V <sub>он</sub> | I <sub>он</sub> |

|         | VIL             | VIL             | I <sub>OL</sub> | V <sub>он</sub> |

FIGURE 7.  $V_{IH}$ ,  $V_{IL}$ ,  $I_{OH}$ ,  $V_{OL}$

**Note A:** Each input is tested separately. **Note B:** When testing DS75453 input not under test is grounded. For all other circuits it is at 4.5V.

Both gates are tested simultaneously.

FIGURE 10.  $I_{\rm CCH},\,I_{\rm CCL}$  for AND, NAND Circuits

Both gates are tested simultaneously.

FIGURE 11.  $I_{CCH}$ ,  $I_{CCL}$  for OR, NOR Circuits

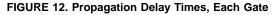

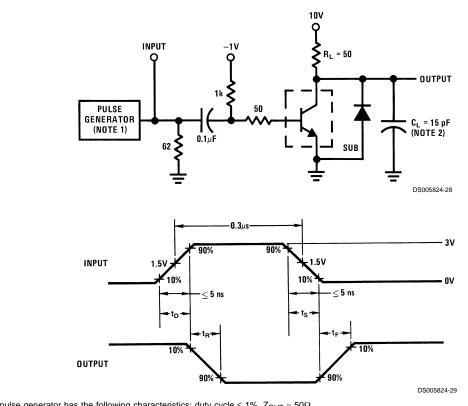

**Note 1:** The pulse generator has the following characteristics: PRR = 1 MHz,  $Z_{OUT} \approx 50\Omega$ . **Note 2:**  $C_L$  includes probe and jig capacitance.

**Note 1:** The pulse generator has the following characteristics: duty cycle  $\leq$  1%, Z<sub>OUT</sub>  $\approx$  50 $\Omega$ . **Note 2:** C<sub>L</sub> includes probe and jig capacitance.

DS75451/2/3

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas Email: support@nsc.com

National Semiconductor Europe

www.national.com

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com

Deutsch

Tel: +49 (0) 69 9508 6208 English

Tel: +44 (0) 870 24 0 2171 Français

Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: ap.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

## Notes