LTC 1340

Varactor Driver

**OBSOLETE:** FOR INFORMATION PURPOSES ONLY Contact Linear Technology for Potential Replacement

#### FEATURES

- Generates 5V Varactor Drive from a 3V Supply

- Wide Supply Voltage Range: 2.7V to 6V

- Requires Only Three External Components

- Micropower Operation: 400µA at 3V Supply

- Shutdown Mode Drops Supply Current Below 1µA

- Low Output Noise: 15µV<sub>RMS</sub>

- Amplifier Gain: 2.3

- Up to 500kHz Signal Bandwidth

- MS8 and SO-8 Packages

- Very Low Input Bias Current: 10nA Max

- Amplifier Offset Maintains Phase Detector in Linear Region

#### **APPLICATIONS**

- 5V Varactor Drive from a Single Li-Ion Cell

- 5V Varactor Drive from Three NiCd/NiMH Cells

- Cellular Telephones

- Portable RF Equipment

- Radio Modems

- Wireless Data Transmission

T, LTC and LT are registered trademarks of Linear Technology Corporation.

## DESCRIPTION

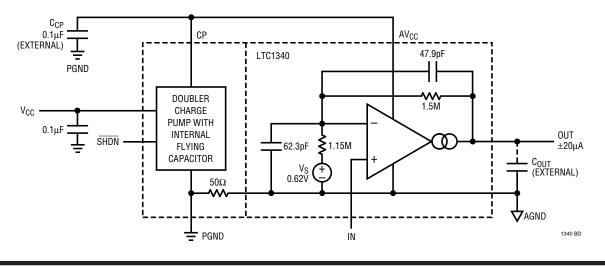

The LTC<sup>®</sup>1340 is a varactor diode driver designed to generate 5V varactor drive from a single 3V or higher voltage supply. It includes a low noise amplifier with an internal gain of 2.3 and a self-contained charge pump to generate output voltages above the input supply. The amplifier input stage includes a built-in offset voltage that allows the output voltage to swing to ground without requiring OV on the input. This feature maintains the phase detector within its linear range of operation. The LTC1340 requires only three external surface mount capacitors to implement a complete varactor driver module.

Low Noise, Voltage-Boosted

The LTC1340 features output referred noise of  $15\mu V_{RMS}$ , minimizing frequency deviation in PLL frequency synthesizer systems. Supply current is 400µA typically with a 3V supply, and drops to 1µA in shutdown, maximizing operating life in battery-powered systems. Amplifier bandwidth is user-adjustable from 10kHz up to 500kHz and the output typically sinks or sources 20µA, allowing fast output signal changes with a typical varactor load. The amplifier input features rail-to-rail input common mode range, allowing it to interface with the output of virtually any phase detector circuit.

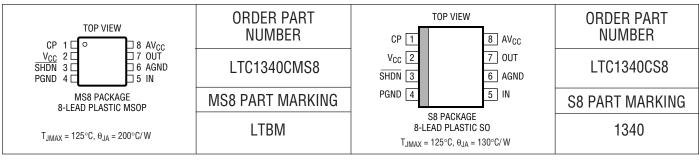

The LTC1340 is available in MS8 and SO-8 packages.

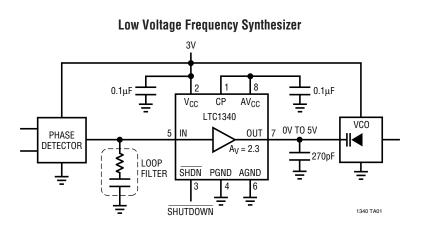

## TYPICAL APPLICATION

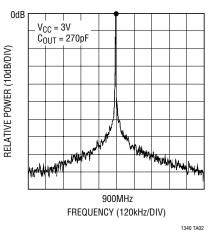

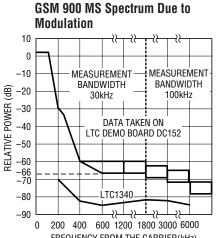

#### Spectral Plot of VCO Output Driven by LTC1340 Resolution Bandwidth = 300Hz

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> )                    | . 7V |

|------------------------------------------------------|------|

| Input Voltage (AV <sub>CC</sub> )                    | 14V  |

| Input Voltage (SHDN, IN)0.3V to V <sub>CC</sub> + C  | ).3V |

| Output Voltage (CP, OUT)0.3V to AV <sub>CC</sub> + C |      |

| Output Short-Circuit Duration Indefi                 | nite |

Commercial Temperature Range ...... 0°C to 70°C Extended Commercial Operating Temperature Range (Note 1) ..... -40°C to 85°C Storage Temperature Range ...... -65°C to 150°C Lead Temperature (Soldering, 10 sec.)...... 300°C

## PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

#### **ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted. (Note 1)

| SYMBOL           | PARAMETER                    | CONDITIONS                                                                                                                                                                                        |   | MIN                         | ТҮР        | MAX             | UNITS             |

|------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------|------------|-----------------|-------------------|

| V <sub>CC</sub>  | Input Supply Voltage         |                                                                                                                                                                                                   | • | 2.7                         |            | 6               | V                 |

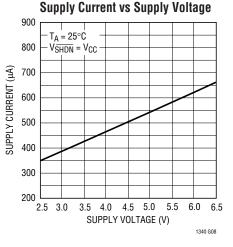

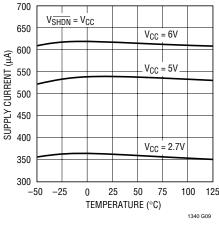

| I <sub>CC</sub>  | Supply Current               | $I_{OUT} = 0, 2.7V \le V_{CC} \le 6V$<br>Shutdown, 2.7V \le V_{CC} \le 6V                                                                                                                         | • |                             | 500<br>1   | 900<br>10       | μΑ<br>μΑ          |

| V <sub>OL</sub>  | Low Output Voltage Swing     | $V_{CC} = 2.7V, 6V,  I_{OUT}  = 0\mu A$<br>$V_{CC} = 2.7V, 6V,  I_{OUT}  = 14\mu A$                                                                                                               | • |                             |            | 0.25<br>0.6     | V<br>V            |

| V <sub>OH</sub>  | High Output Voltage Swing    | $ \begin{array}{ c c c c c } V_{CC} = 2.7V, \  I_{0UT}  = 0\mu A \\ V_{CC} = 6V, \  I_{0UT}  = 0\mu A \\ V_{CC} = 2.7V, \  I_{0UT}  = 14\mu A \\ V_{CC} = 6V, \  I_{0UT}  = 14\mu A \end{array} $ | • | 4.6<br>10.5<br>4.25<br>9.75 |            |                 | V<br>V<br>V<br>V  |

| I <sub>OUT</sub> | Output Sink/Source Current   | $\begin{array}{c} 0.6V \leq V_{OUT} \leq 4.25V, \ V_{CC} = 2.7V \\ 0.6V \leq V_{OUT} \leq 9.75V, \ V_{CC} = 6V \end{array}$                                                                       | • | ±14<br>±14                  | ±20<br>±20 | ±35<br>±35      | μΑ<br>μΑ          |

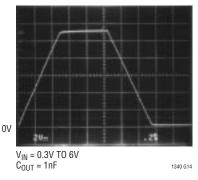

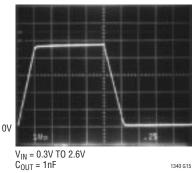

| t <sub>OUT</sub> | Output Transition Time       | $C_{OUT} = 1 nF, \Delta V_{OUT} = \pm 4 V$                                                                                                                                                        | • |                             | 200        | 285             | μs                |

| VIN              | Input Voltage Range          |                                                                                                                                                                                                   | • | 0                           |            | V <sub>CC</sub> | V                 |

| I <sub>B</sub>   | Input Bias Current           | $0.1V \le V_{IN} \le V_{CC}$                                                                                                                                                                      | • |                             | ±0.01      | ±1<br>±10       | nA<br>nA          |

| V <sub>OS</sub>  | Input Offset Voltage         |                                                                                                                                                                                                   | • | 0.15                        | 0.35       | 0.60            | V                 |

| Av               | Amplifier Gain               | $V_{IN} = 1V, AV_{CC} = 5V$                                                                                                                                                                       | • | 2.1                         | 2.3        | 2.5             | V/V               |

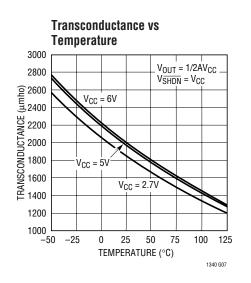

| g <sub>m</sub>   | Amplifier Transconductance   | $V_{OUT} = 2.5V, AV_{CC} = 5V$<br>$V_{OUT} = 2.5V, AV_{CC} = 5V$                                                                                                                                  | • | 1200<br>800                 | 1800       | 2300<br>3200    | µmho<br>µmho      |

| R <sub>OUT</sub> | Output Impedance             | $V_{OUT} = 1/2AV_{CC}$                                                                                                                                                                            |   |                             | 1          |                 | MΩ                |

| e <sub>n</sub>   | Output Noise Voltage         | 1kHz to 100kHz, C <sub>OUT</sub> = 1nF                                                                                                                                                            |   |                             | 15         | 25              | μV <sub>RMS</sub> |

| BW               | –3dB Signal Bandwidth        | C <sub>OUT</sub> = 1nF                                                                                                                                                                            |   |                             | 125        |                 | kHz               |

| PSRR             | Power Supply Rejection Ratio | $AV_{CC} = 4V$ to $6V$ , $C_{OUT} = 1$ nF                                                                                                                                                         | • | 60                          | 90         |                 | dB                |

| ISHDN            | Shutdown Logic Input Current | $0.1V \le V_{\overline{SHDN}} \le V_{CC}$                                                                                                                                                         |   |                             | ±0.01      | ±1              | μA                |

2

#### **ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ , unless otherwise noted. (Note 1)

| SYMBOL              | PARAMETER                                   | CONDITIONS                                                           | MIN | ТҮР | MAX | UNITS         |

|---------------------|---------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|---------------|

| t <sub>START</sub>  | Charge Pump Start-Up Time                   | $C_{CP} = 0.1 \mu F, V_{CC} = 2.7 V, I_{OUT} = 0$                    |     | 1.2 | 5   | ms            |

| V <sub>RIPPLE</sub> | Charge Pump Output Ripple at C <sub>P</sub> | $C_{CP} = C_{VCC} = 0.1 \mu F, V_{CC} = 2.7 V, I_{OUT} = 0$ (Note 2) |     | 200 |     | $\mu V_{P-P}$ |

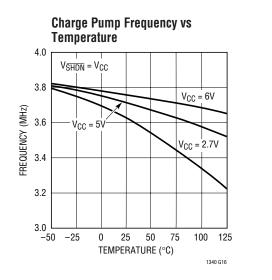

| f <sub>CP</sub>     | Charge Pump Frequency                       | (Note 3)                                                             | 2.5 | 4   |     | MHz           |

The  ${\ensuremath{\bullet}}$  denotes specifications which apply over the specified temperature range.

**Note 1:** C grade device specifications are guaranteed over the 0°C to 70°C temperature range. In addition, C grade device specifications are assured over the -40°C to 85°C temperature range by design or correlation, but are not production tested.

**Note 2:** The charge pump output ripple is not tested but is correlated with a PCB ground plane and high quality, low ESR, low ESL metalized polyester  $0.1\mu$ F capacitors.

**Note 3:** The internal oscillator typically runs at 2MHz, but the charge pump refreshes the output on both phases of the clock, resulting in an effective 4MHz operating frequency.

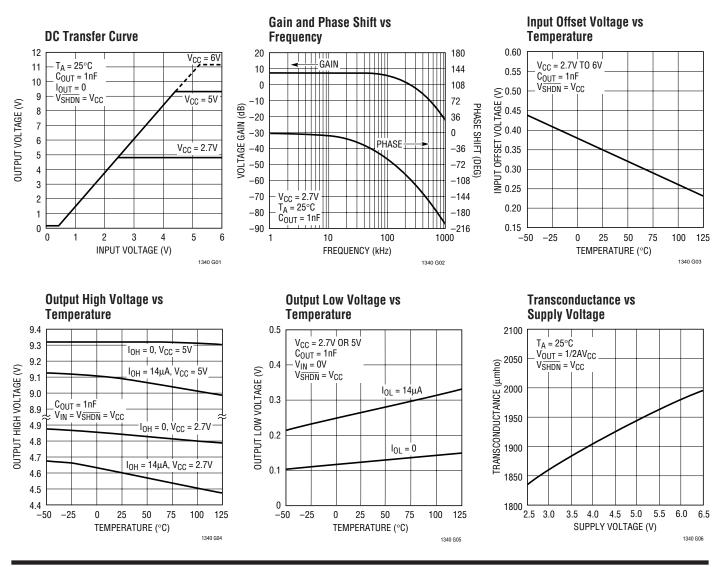

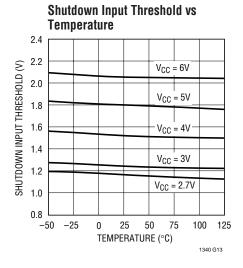

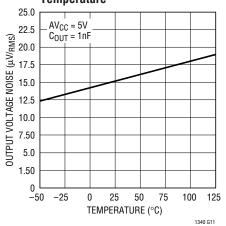

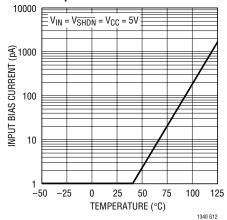

### **TYPICAL PERFORMANCE CHARACTERISTICS**

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Supply Current vs Temperature

D 200 400 600 1200 1800 3000 6000 FREQUENCY FROM THE CARRIER(kHz) 1340 610

Output Voltage Noise vs Temperature

Input Bias Current vs Temperature

Rail-to-Rail Step Response at V<sub>CC</sub> = 6V

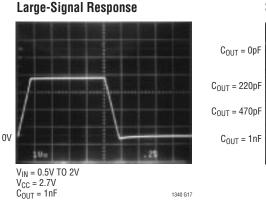

Rail-to-Rail Step Response at  $V_{CC} = 2.7V$

### TYPICAL PERFORMANCE CHARACTERISTICS

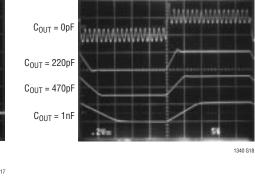

Small-Signal Response

### PIN FUNCTIONS

**CP (Pin 1):** Charge Pump Output. This is the output of the internal charge pump. The voltage at CP is nominally twice the  $V_{CC}$  input voltage. Connect CP to an external  $0.1 \mu F$  filter capacitor and  $AV_{CC}$ .

$V_{CC}$  (Pin 2): Supply Input. This is the input supply to the charge pump.  $V_{CC}$  can range from 2.7V to 6V and requires a 0.1µF bypass capacitor to PGND.

**SHDN** (Pin 3) Shutdown. If SHDN is high (>V<sub>CC</sub> – 0.5V), the LTC1340 operates normally. If SHDN is pulled low (<0.5V), the LTC1340 enters shutdown mode and the supply current drops to less than 1 $\mu$ A typically. In shutdown, the charge pump output voltage collapses and the OUT pin enters a high impedance state. If SHDN returns high, the charge pump output requires 1.2ms typically to resume full voltage.

**PGND (Pin 4):** Power Ground. This is the charge pump ground. Connect PGND to the system power supply return.

**IN (Pin 5):** Signal Input. The internal amplifier amplifies the signal input at this pin typically by 2.3 to the OUT pin. IN accepts signals from GND to  $V_{CC}$  without phase reversal or unusual behavior, allowing a direct connection to the output of virtually any phase detector or loop filter powered from  $V_{CC}$ .

**AGND (Pin 6):** Signal Ground. Connect AGND to the ground plane in close proximity to the VCO ground. There is an internal parasitic resistance of  $50\Omega$  between AGND and PGND.

**OUT (Pin 7):** Driver Output. OUT is the output of the internal  $g_m$  amplifier and the internal feedback network. It swings from GND to AV<sub>CC</sub>, and drives a varactor load directly. The OUT pin requires an external capacitor ( $\geq$  220pF) to AGND to ensure stability. OUT typically sinks or sources 20 $\mu$ A.

$AV_{CC}$  (Pin 8): Amplifier Supply. LTC recommends a direct connection from  $AV_{CC}$  to CP and also recommends a 0.1µF filter capacitor from CP to PGND.

## **BLOCK DIAGRAM**

## APPLICATIONS INFORMATION

#### Overview

The LTC1340 is a monolithic IC that combines a charge pump and a low noise amplifier to provide a 0V to 5V swing to drive a varactor diode-based PLL system from a single 3V supply. Traditional PLL frequency synthesizers used in cellular phones and other portable RF systems use varactor diodes as the voltage variable element in the VCO. Typical varactor diodes require at least 4V of control voltage swing to obtain their full range of capacitance adjustment. Newer battery-powered systems, operating from low voltage power supplies, have trouble providing this bias voltage without an additional step-up circuit.

The LTC1340 design provides a 5V signal swing suitable for biasing such a varactor diode when powered from a 3V or higher voltage supply. The internal op amp and feedback network with built-in offset provide a gain of 2.3 so that a 0.35V to 2.5V swing at the noninverting input provides a 0V to 5V swing at the output. The onboard charge pump provides the boosted voltage necessary to drive the varactor and requires only a single  $0.1\mu$ F output filter capacitor to complete the boost circuit. The amplifier requires one capacitor (typically 1nF) at its output to set amplifier noise bandwidth and to ensure amplifier stability. The performance characteristics of the LTC1340 are designed to meet the requirements of GSM and similar cellular phone transceivers without requiring additional circuitry. The LTC1340's high level of functional integration allows it to replace several power supply and regulator components in a typical PLL synthesizer. This results in significant space and complexity savings.

#### **Charge Pump**

The LTC1340 features a self-contained doubling charge pump with internal flying capacitors. The charge pump refreshes the output on each phase of the internal 2MHz clock, giving an effective 4MHz switching frequency. An external 0.1 $\mu$ F capacitor at the CP pin acts as a charge reservoir and provides filtering to minimize clock feedthrough to the amplifier section. The CP pin can be connected directly to the amplifier power supply at AV<sub>CC</sub>. In addition, it can be filtered with an RC or LC network prior to its connection to AV<sub>CC</sub>. The LTC1340 minimizes interaction between the charge pump and the amplifier through careful internal shielding.

#### Amplifier

The LTC1340 includes an internal  $g_m$  amplifier with an onchip feedback network to amplify the input signal to the gained output level. The amplifier requires an external capacitor from its output to AGND to provide closed-loop stability, noise bandwidth limiting and to further reduce charge pump feedthrough. The –3dB signal bandwidth of the amplifier is given by the following equation:

$BW_{-3dB} = g_m/(2\pi)(C_{OUT})(A_V)$

### **APPLICATIONS INFORMATION**

Amplifier transconductance is typically  $1800\mu$ mho. With a 1nF external capacitor at the amplifier output, the bandwidth is 125kHz. The amplifier transconductance varies with temperature and process. The minimum recommended C<sub>OUT</sub> is 220pF with a typical bandwidth of 566kHz.

The slew rate of the amplifier is:

$SR = I_{OUT}/C_{OUT}$

The amplifier typically sinks or sources  $20\mu$ A, allowing it to slew a 1nF output capacitance at 20V/ms, or 5V in 250 $\mu$ s.

The on-chip amplifier feedback network is set for a DC gain of 2.3 with an input offset of 0.35V as shown in the typical curves. The amplifier allows a rail-to-rail input swing with a 3V supply and provides a 5V swing at the output. The output swings to within millivolts of the AV<sub>CC</sub> voltage and to about 100mV above AGND. The input stage of the amplifier is powered from AV<sub>CC</sub> and accepts full GND to V<sub>CC</sub> rail-to-rail input signals without exceeding the input common mode range. The output noise of the amplifier is typically 15 $\mu$ V<sub>RMS</sub> at frequencies between 1kHz and 100kHz.

There are two feedthrough signals at the amplifier OUT pin from the charge pump, the main component at 4MHz and the second harmonic signal at 8MHz. The 4MHz feedthrough is typically below  $50\mu$ V with C<sub>OUT</sub> equal to 1nF and C<sub>CP</sub> equal to  $0.1\mu$ F. The feedthrough signal decreases in amplitude when larger C<sub>OUT</sub> is used. Most systems should require no additional filtering. Additional filtering to reduce feedthrough noise is possible by inserting a resistor or a ferrite bead between OUT and  $C_{OUT}$ .

#### Hookup

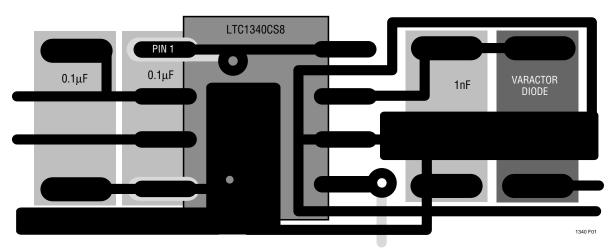

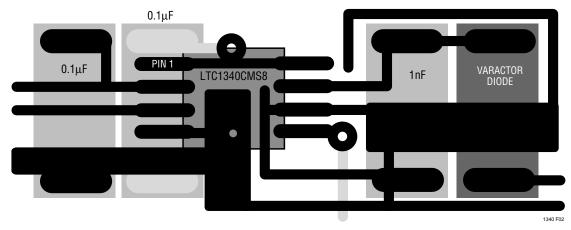

The two sections of the LTC1340 are carefully shielded from each other inside the chip, but care must also be taken in the external hookup to minimize noise at the amplifier output. The two halves of the chip should only meet electrically where the CP and AV<sub>CC</sub> pins connect together and at the common point of AGND and PGND. Separate PGND and AGND as much as possible. AGND is the amplifier ground. Connect it to a ground plane and as close to the VCO ground as possible. Bypass  $V_{CC}$  and CP to PGND with a 0.1µF capacitor. Select high quality, low ESR and low ESL surface mount ceramic capacitors for both the CP and the VCC bypass capacitors. Poor grade capacitors will result in unacceptable ripple amplitude or ringing characteristics. Connect both terminals of the bypass capacitors as close to the chip as possible to minimize charge pump output ripple amplitude and ground currents in the rest of the system. Keep IN and OUT away from V<sub>CC</sub>, CP and AV<sub>CC</sub> as much as possible. Crosstalk from  $V_{CC}$ , CP and AV<sub>CC</sub> PCB traces to IN and OUT PCB traces can be minimized by routing AGND PCB traces as shield as shown in Figures 1 and 2. Connect the 1nF output capacitor close to the varactor diode and return it to the AGND plane. The SHDN and IN pins, should not be allowed to go below PGND potential as the ESD diode forms an NPN and bleeds the charge pump output.

Figure 1. Suggested Surface Mount PCB Layout for LTC1340CS8

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

# **APPLICATIONS INFORMATION**

PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted. **MS8** Package 8-Lead Plastic MSOP (LTC DWG # 05-08-1660) 0.118 ± 0.004\*  $(3.00 \pm 0.10)$  $0.040\pm0.006$  $0.006 \pm 0.004$  $(1.02 \pm 0.15)$  $(0.15 \pm 0.10)$ 0.007  $0^{\circ} - 6^{\circ} TYP$ (0.18)0.118 ± 0.004\*\* SEATING  $0.192 \pm 0.004$ PLANE (3.00 ± 0.10)  $(4.88 \pm 0.10)$  $0.021\pm0.004$ 0.012  $(0.53 \pm 0.01)$ (0.30)0.025 (0.65) TYP \* DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE \*\* DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. MSOP08 0596 INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE **S8** Package 8-Lead Plastic Small Outline (Narrow 0.150) 0.189 - 0.197\* (LTC DWG # 05-08-1610)  $(\overline{4.801 - 5.004})$ 0.010 - 0.020 × 45° 0.053 - 0.069  $(\overline{0.254 - 0.508})$ (1.346 - 1.752) 0.004 - 0.010 0.008 - 0.010 (0.101 - 0.254)0°- 8° TYF  $(\overline{0.203 - 0.254})$ 0.228 - 0.244 (5.791 - 6.197) 0.150 - 0.157\*\* 0.016 - 0.050  $(\overline{3.810 - 3.988})$ 0.014 - 0.019 0.050 0.406 - 1.270 $(\overline{0.355 - 0.483})$ (1.270) BSC \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE 2 \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD SO8 0695 FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

### **RELATED PARTS**

| PART NUMBER                           | DESCRIPTION              | COMMENTS                                                           |

|---------------------------------------|--------------------------|--------------------------------------------------------------------|

| LTC1261, LTC1429,<br>LTC1550, LTC1551 | GaAs FET Bias Generators | Regulated negative voltage generator from a single positive supply |