#### **General Description**

The DS3231 is a low-cost, extremely accurate I<sup>2</sup>C realtime clock (RTC) with an integrated temperaturecompensated crystal oscillator (TCXO) and crystal. The device incorporates a battery input, and maintains accurate timekeeping when main power to the device is interrupted. The integration of the crystal resonator enhances the long-term accuracy of the device as well as reduces the piece-part count in a manufacturing line. The DS3231 is available in commercial and industrial temperature ranges, and is offered in a 16-pin, 300-mil SO package.

The RTC maintains seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with an AM/PM indicator. Two programmable time-of-day alarms and a programmable square-wave output are provided. Address and data are transferred serially through an I<sup>2</sup>C bidirectional bus.

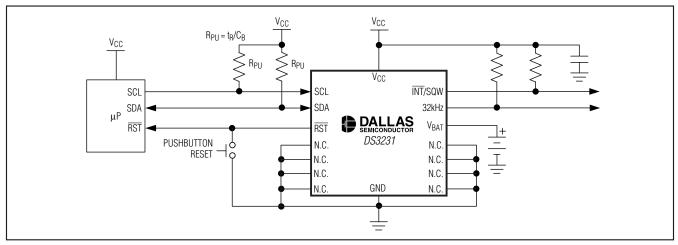

A precision temperature-compensated voltage reference and comparator circuit monitors the status of V<sub>CC</sub> to detect power failures, to provide a reset output, and to automatically switch to the backup supply when necessary. Additionally, the  $\overline{\text{RST}}$  pin is monitored as a pushbutton input for generating a  $\mu$ P reset.

#### **Applications**

Utility Power Meters

Servers Telematics

GPS

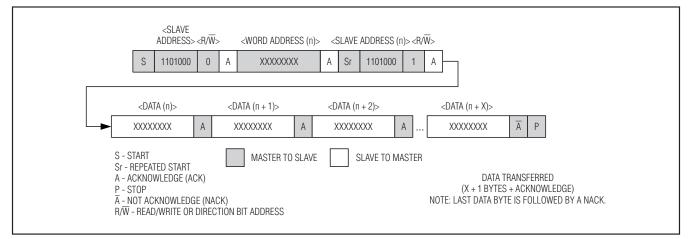

Pin Configuration appears at end of data sheet.

#### Features

- Accuracy ±2ppm from 0°C to +40°C

- Accuracy ±3.5ppm from -40°C to +85°C

- Battery Backup Input for Continuous Timekeeping

- Operating Temperature Ranges Commercial: 0°C to +70°C Industrial: -40°C to +85°C

- Low-Power Consumption

- Real-Time Clock Counts Seconds, Minutes, Hours, Day, Date, Month, and Year with Leap Year Compensation Valid Up to 2100

- Two Time-of-Day Alarms

- Programmable Square-Wave Output

- ◆ Fast (400kHz) I<sup>2</sup>C Interface

- ♦ 3.3V Operation

- Digital Temp Sensor Output: ±3°C Accuracy

- Register for Aging Trim

- ♦ RST Output/Pushbutton Reset Debounce Input

- Underwriters Laboratories (UL) Recognized

#### **Ordering Information**

| PART      | TEMP RANGE     | PIN-PACKAGE |

|-----------|----------------|-------------|

| DS3231S#  | 0°C to +70°C   | 16 SO       |

| DS3231SN# | -40°C to +85°C | 16 SO       |

#Denotes a RoHS-compliant device that may include lead that is exempt under RoHS requirements. The lead finish is JESD97 category e3, and is compatible with both lead-based and leadfree soldering processes. A "#" anywhere on the top mark denotes a RoHS-compliant device.

#### **Typical Operating Circuit**

### BALLAS ANALY

Maxim Integrated Products 1

DS3231

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on V <sub>CC</sub> , V <sub>BAT</sub> , 32kHz, SCL, SDA, <del>RST</del> , |

|-----------------------------------------------------------------------------------------|

| INT/SQW Relative to Ground0.3V to +6.0V                                                 |

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) (Note 1)73°C/W                 |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) (Note 1)23°C/W                    |

| Operating Temperature Range                                                             |

| (noncondensing)40°C to +85°C                                                            |

| Junction Temperature+125°C                                                              |

| Storage Temperature Range                   | 40°C to +85°C      |

|---------------------------------------------|--------------------|

| Lead Temperature (soldering, 10s)           | +260°C             |

| Soldering Temperature (reflow, 2 times max) |                    |

| Lead(Pb)-free                               | +260°C             |

| Containing lead(Pb)                         | +240°C             |

| (See the Handling, PC Board Layout, and     | Assembly section.) |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

$(T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$  (Notes 2, 3)

| PARAMETER              | SYMBOL          | CONDITIONS | MIN                      | ТҮР | MAX                      | UNITS |

|------------------------|-----------------|------------|--------------------------|-----|--------------------------|-------|

|                        | Vcc             |            | 2.3                      | 3.3 | 5.5                      | V     |

| Supply Voltage         | VBAT            |            | 2.3                      | 3.0 | 5.5                      | V     |

| Logic 1 Input SDA, SCL | V <sub>IH</sub> |            | 0.7 x<br>V <sub>CC</sub> |     | V <sub>CC</sub> +<br>0.3 | V     |

| Logic 0 Input SDA, SCL | VIL             |            | -0.3                     |     | 0.3 x<br>V <sub>CC</sub> | V     |

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = 2.3V to 5.5V, V<sub>CC</sub> = Active Supply (see Table 1), T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.) (Typical values are at V<sub>CC</sub> = 3.3V,  $V_{BAT} = 3.0V$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Notes 2, 3)

| PARAMETER                                                    | SYMBOL          | CONDITIONS                                                        |                       |      | ТҮР   | MAX  | UNITS |

|--------------------------------------------------------------|-----------------|-------------------------------------------------------------------|-----------------------|------|-------|------|-------|

| Active Supply Current                                        | laat            | (Nietes 4 E)                                                      |                       |      | 200   |      |       |

| Active Supply Current                                        | ICCA            | (Notes 4, 5)                                                      | $V_{CC} = 5.5V$       |      |       | 300  | μA    |

| Standby Supply Current                                       | Iccs            | I <sup>2</sup> C bus inactive, 32kHz<br>output on, SQW output off | $V_{\rm CC} = 3.63 V$ |      |       | 110  | μA    |

| Standby Suppry Surrent                                       | 1005            | (Note 5)                                                          | $V_{CC} = 5.5V$       |      |       | 170  | μπ    |

| Temperature Conversion Current                               |                 | I <sup>2</sup> C bus inactive, 32kHz                              | $V_{CC} = 3.63V$      |      |       | 575  | μA    |

| Temperature Conversion Current                               | ICCSCONV        | output on, SQW output off                                         | $V_{CC} = 5.5V$       |      |       | 650  | μΑ    |

| Power-Fail Voltage                                           | $V_{PF}$        |                                                                   |                       | 2.45 | 2.575 | 2.70 | V     |

| Logic 0 Output, 32kHz,<br>INT/SQW, SDA                       | V <sub>OL</sub> | I <sub>OL</sub> = 3mA                                             |                       |      |       | 0.4  | V     |

| Logic 0 Output, RST                                          | VOL             | I <sub>OL</sub> = 1mA                                             |                       |      |       | 0.4  | V     |

| Output Leakage Current 32kHz,<br>INT/SQW, SDA                | ILO             | Output high impedance                                             |                       | -1   | 0     | +1   | μA    |

| Input Leakage SCL                                            | ILI             |                                                                   |                       | -1   |       | +1   | μA    |

| RST Pin I/O Leakage                                          | IOL             | RST high impedance (Note                                          | 6)                    | -200 |       | +10  | μA    |

| V <sub>BAT</sub> Leakage Current<br>(V <sub>CC</sub> Active) | IBATLKG         |                                                                   |                       |      | 25    | 100  | nA    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{CC}$  = 2.3V to 5.5V,  $V_{CC}$  = Active Supply (see Table 1),  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Typical values are at  $V_{CC}$  = 3.3V,  $V_{BAT}$  = 3.0V, and  $T_A$  = +25°C, unless otherwise noted.) (Notes 2, 3)

| PARAMETER                                           | SYMBOL            | CONDITIC                                   | CONDITIONS     |    | ТҮР    | MAX  | UNITS |  |

|-----------------------------------------------------|-------------------|--------------------------------------------|----------------|----|--------|------|-------|--|

| Output Frequency                                    | fout              | $V_{CC} = 3.3V \text{ or } V_{BAT} = 3.3'$ | V              |    | 32.768 |      | kHz   |  |

| Frequency Stability vs.                             | Δf/fout           | $V_{CC} = 3.3V$ or<br>$V_{BAT} = 3.3V$ ,   | 0°C to +40°C   |    |        | ±2   | nnm   |  |

| Temperature (Commercial)                            |                   | aging offset = 00h                         | >40°C to +70°C |    |        | ±3.5 | ppm   |  |

|                                                     |                   | $V_{CC} = 3.3 V \text{ or}$                | -40°C to <0°C  |    |        | ±3.5 |       |  |

| Frequency Stability vs.<br>Temperature (Industrial) | ∆f/fout           | $V_{BAT} = 3.3V,$                          | 0°C to +40°C   |    |        | ±2   | ppm   |  |

|                                                     |                   | aging offset = 00h                         | >40°C to +85°C |    |        | ±3.5 |       |  |

| Frequency Stability vs. Voltage                     | Δf/V              |                                            |                |    | 1      |      | ppm/V |  |

|                                                     |                   |                                            | -40°C          |    | 0.7    |      |       |  |

| Trim Register Frequency                             |                   | Constitued at                              | +25°C          |    | 0.1    |      | 1     |  |

| Sensitivity per LSB                                 | ∆f/LSB            | Specified at:                              | +70°C          |    | 0.4    |      | ppm   |  |

|                                                     |                   |                                            | +85°C          |    | 0.8    |      |       |  |

| Temperature Accuracy                                | Temp              | $V_{CC} = 3.3V$ or $V_{BAT} = 3.3V$        |                | -3 |        | +3   | °C    |  |

| Crystal Aging                                       | A 6/6 -           | After reflow,                              | First year     |    | ±1.0   |      |       |  |

| Crystal Aging                                       | Δf/f <sub>O</sub> | not production tested                      | 0-10 years     |    | ±5.0   |      | _ ppm |  |

#### **ELECTRICAL CHARACTERISTICS**

(VCC = 0V, VBAT = 2.3V to 5.5V, TA = TMIN to TMAX, unless otherwise noted.) (Note 2)

| PARAMETER                      | SYMBOL  | CONDITIONS                                                                                     |                          | MIN | ТҮР  | MAX | UNITS |

|--------------------------------|---------|------------------------------------------------------------------------------------------------|--------------------------|-----|------|-----|-------|

| Active Battery Current         |         | $\overline{\text{EOSC}} = 0$ , BBSQW = 0,                                                      | $V_{BAT} = 3.63V$        |     |      | 70  | μA    |

|                                | IBATA   | SCL = 400kHz (Note 5)                                                                          | $V_{BAT} = 5.5V$         |     |      | 150 | μΑ    |

| Timekeeping Battery Current    |         | $\overline{\text{EOSC}} = 0$ , BBSQW = 0,<br>EN32kHz = 1,                                      | $V_{BAT} = 3.63V$        |     | 0.84 | 3.0 | μA    |

| Timekeeping Ballery Current    | IBATT   | SCL = SDA = 0V or<br>SCL = SDA = V <sub>BAT</sub> (Note 5)                                     | V <sub>BAT</sub> = 5.5V  |     | 1.0  | 3.5 | μΑ    |

| Temperature Conversion Current | IBATTC  | $\overline{\text{EOSC}} = 0$ , BBSQW = 0,<br>SCL = SDA = 0V or<br>SCL = SDA = V <sub>BAT</sub> | V <sub>BAT</sub> = 3.63V |     |      | 575 |       |

|                                |         |                                                                                                | $V_{BAT} = 5.5V$         |     |      | 650 | μA    |

| Data-Retention Current         | IBATTDR | $\overline{\text{EOSC}} = 1$ , SCL = SDA = 0V,                                                 | +25°C                    |     |      | 100 | nA    |

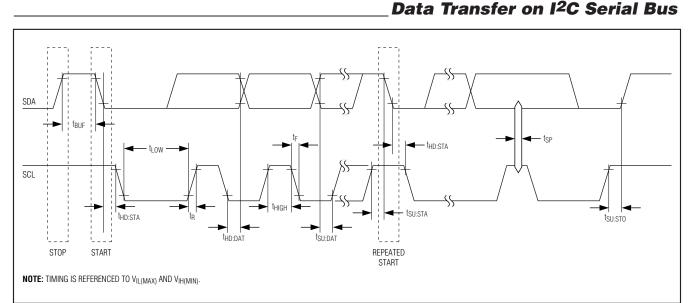

#### AC ELECTRICAL CHARACTERISTICS

**DS3231**

(V<sub>CC</sub> = V<sub>CC(MIN)</sub> to V<sub>CC(MAX)</sub> or V<sub>BAT</sub> = V<sub>BAT(MIN)</sub> to V<sub>BAT(MAX)</sub>, V<sub>BAT</sub> > V<sub>CC</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.) (Note 2)

| PARAMETER                                                            | SYMBOL              | CONDITIONS    | MIN TY | 'P MAX | UNITS |  |

|----------------------------------------------------------------------|---------------------|---------------|--------|--------|-------|--|

|                                                                      | f                   | Fast mode     | 100    | 400    |       |  |

| SCL Clock Frequency                                                  | fSCL                | Standard mode | 0      | 100    | - kHz |  |

| Bus Free Time Between STOP                                           | tour                | Fast mode     | 1.3    |        |       |  |

| and START Conditions                                                 | tBUF                | Standard mode | 4.7    |        | μs    |  |

| Hold Time (Repeated) START                                           | tup 071             | Fast mode     | 0.6    |        |       |  |

| Condition (Note 7)                                                   | <sup>t</sup> HD:STA | Standard mode | 4.0    |        | μs    |  |

| Low Period of SCL Clock                                              | t. ou               | Fast mode     | 1.3    |        |       |  |

| LOW FEILING OF SCE CLOCK                                             | tlow                | Standard mode | 4.7    |        | - µs  |  |

| High Deried of SCL Clock                                             | t                   | Fast mode     | 0.6    |        |       |  |

| High Period of SCL Clock                                             | thigh               | Standard mode | 4.0    |        | μs    |  |

| Data Hald Time (Natas 8, 0)                                          | tup p               | Fast mode     | 0      | 0.9    |       |  |

| Data Hold Time (Notes 8, 9)                                          | <sup>t</sup> HD:DAT | Standard mode | 0      | 0.9    | μs    |  |

| Data Satup Tima (Nata 10)                                            | tourner             | Fast mode     | 100    |        | 20    |  |

| Data Setup Time (Note 10)                                            | tsu:dat             | Standard mode | 250    |        | - ns  |  |

|                                                                      | tsu:sta             | Fast mode     | 0.6    |        |       |  |

| START Setup Time                                                     |                     | Standard mode | 4.7    |        | μs    |  |

| Rise Time of Both SDA and SCL                                        | to                  | Fast mode     | 20 +   | 300    | 20    |  |

| Signals (Note 11)                                                    | tR                  | Standard mode | 0.1CB  | 1000   | - ns  |  |

| Fall Time of Both SDA and SCL                                        | +                   | Fast mode     | 20 +   | 300    |       |  |

| Signals (Note 11)                                                    | tF                  | Standard mode | 0.1CB  | 300    | ns    |  |

| Setup Time for STOP Condition                                        | touro               | Fast mode     | 0.6    |        |       |  |

| Setup Time for STOP Condition                                        | tsu:sto             | Standard mode | 4.7    |        | μs    |  |

| Capacitive Load for Each Bus<br>Line                                 | CB                  | (Note 11)     |        | 400    | pF    |  |

| Capacitance for SDA, SCL                                             | CI/O                |               | 1      | 0      | рF    |  |

| Pulse Width of Spikes That Must<br>Be Suppressed by the Input Filter | t <sub>SP</sub>     |               | 3      | 0      | ns    |  |

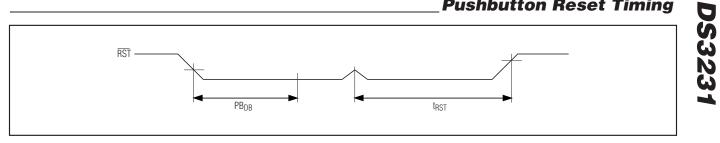

| Pushbutton Debounce                                                  | PB <sub>DB</sub>    |               | 25     | i0     | ms    |  |

| Reset Active Time                                                    | trst                |               | 25     | 0      | ms    |  |

| Oscillator Stop Flag (OSF) Delay                                     | tosf                | (Note 12)     | 10     | 0      | ms    |  |

| Temperature Conversion Time                                          | tCONV               |               | 12     | 25 200 | ms    |  |

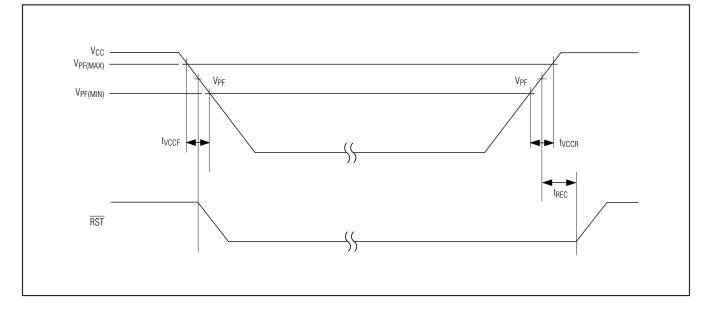

#### **POWER-SWITCH CHARACTERISTICS**

$(T_A = T_{MIN} \text{ to } T_{MAX})$

| PARAMETER                                                                  | SYMBOL | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|----------------------------------------------------------------------------|--------|------------|-----|-----|-----|-------|

| V <sub>CC</sub> Fall Time; V <sub>PF(MAX)</sub> to<br>V <sub>PF(MIN)</sub> | tvccf  |            | 300 |     |     | μs    |

| V <sub>CC</sub> Rise Time; V <sub>PF(MIN)</sub> to<br>V <sub>PF(MAX)</sub> | tvccr  |            | 0   |     |     | μs    |

| Recovery at Power-Up                                                       | trec   | (Note 13)  |     | 250 | 300 | ms    |

#### **Pushbutton Reset Timing**

#### **Power-Switch Timing**

DS3231

#### WARNING: Negative undershoots below -0.3V while the part is in battery-backed mode may cause loss of data.

- Note 2: Limits at -40°C are guaranteed by design and not production tested.

- **Note 3:** All voltages are referenced to ground.

- **Note 4:** I<sub>CCA</sub>—SCL clocking at max frequency = 400kHz.

- Note 5: Current is the averaged input current, which includes the temperature conversion current.

- **Note 6:** The  $\overline{\text{RST}}$  pin has an internal 50k $\Omega$  (nominal) pullup resistor to V<sub>CC</sub>.

- Note 7: After this period, the first clock pulse is generated.

- **Note 8:** A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 9: The maximum t<sub>HD:DAT</sub> needs only to be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- **Note 10:** A fast-mode device can be used in a standard-mode system, but the requirement  $t_{SU:DAT} \ge 250$ ns must then be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line  $t_{R(MAX)} + t_{SU:DAT} = 1000 + 250 = 1250$ ns before the SCL line is released.

- Note 11: CB-total capacitance of one bus line in pF.

- Note 12: The parameter  $t_{OSF}$  is the period of time the oscillator must be stopped for the OSF flag to be set over the voltage range of  $0.0V \le V_{CC} \le V_{CC(MAX)}$  and  $2.3V \le V_{BAT} \le 3.4V$ .

- **Note 13:** This delay applies only if the oscillator is enabled and running. If the EOSC bit is a 1, t<sub>REC</sub> is bypassed and RST immediately goes high. The state of RST does not affect the I<sup>2</sup>C interface, RTC, or TCXO.

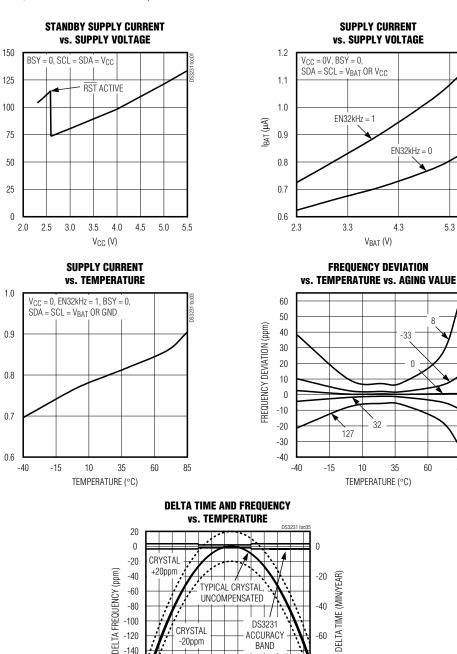

#### **Typical Operating Characteristics**

5.3

33

60

85

CRYSTAL

-20ppm

-40 -30 -20 -10 0 10 20 30 40 50 60 70 80 TEMPERATURE (°C)

ACCURACY

BAND

-60

-80

-100

-120

-140 -160

-180 -200

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

Iccs (µA)

IBAT (µA)

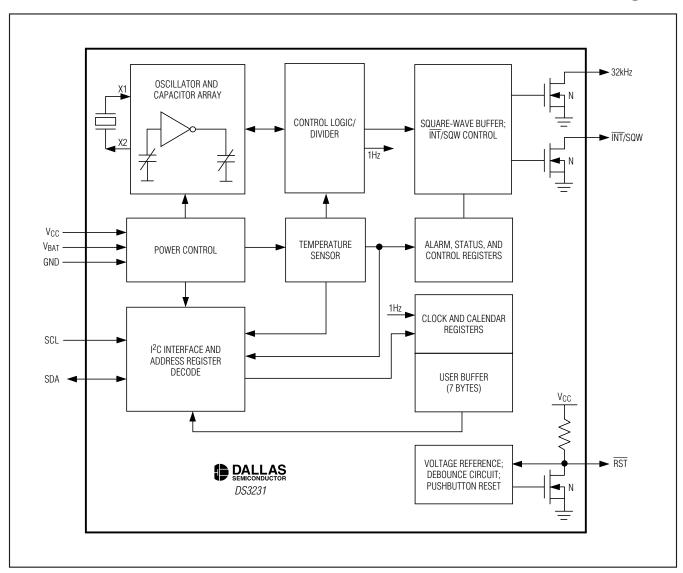

Block Diagram

**DS3231**

#### **Pin Description**

|      | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN  | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1    | 32kHz           | 32kHz Output. This open-drain pin requires an external pullup resistor. When enabled, the output operates on either power supply. It may be left open if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2    | V <sub>CC</sub> | DC Power Pin for Primary Power Supply. This pin should be decoupled using a $0.1\mu$ F to $1.0\mu$ F capacitor. If not used, connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3    | ĪNT/SQW         | Active-Low Interrupt or Square-Wave Output. This open-drain pin requires an external pullup resistor connected to a supply at 5.5V or less. This multifunction pin is determined by the state of the INTCN bit in the Control Register (0Eh). When INTCN is set to logic 0, this pin outputs a square wave and its frequency is determined by RS2 and RS1 bits. When INTCN is set to logic 1, then a match between the timekeeping registers and either of the alarm registers activates the INT/SQW pin (if the alarm is enabled). Because the INTCN bit is set to logic 1 when power is first applied, the pin defaults to an interrupt output with alarms disabled. The pullup voltage can be up to 5.5V, regardless of the voltage on V <sub>CC</sub> . If not used, this pin can be left unconnected.       |

| 4    | RST             | Active-Low Reset. This pin is an open-drain input/output. It indicates the status of V <sub>CC</sub> relative to the V <sub>PF</sub> specification. As V <sub>CC</sub> falls below V <sub>PF</sub> , the $\overline{\text{RST}}$ pin is driven low. When V <sub>CC</sub> exceeds V <sub>PF</sub> , for t <sub>RST</sub> , the $\overline{\text{RST}}$ pin is pulled high by the internal pullup resistor. The active-low, open-drain output is combined with a debounced pushbutton input function. This pin can be activated by a pushbutton reset request. It has an internal 50k $\Omega$ nominal value pullup resistor to V <sub>CC</sub> . No external pullup resistors should be connected. If the oscillator is disabled, t <sub>REC</sub> is bypassed and $\overline{\text{RST}}$ immediately goes high. |

| 5–12 | N.C.            | No Connection. Must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13   | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14   | VBAT            | Backup Power-Supply Input. When using the device with the $V_{BAT}$ input as the primary power source, this pin should be decoupled using a $0.1\mu$ F to $1.0\mu$ F low-leakage capacitor. When using the device with the $V_{BAT}$ input as the backup power source, the capacitor is not required. If $V_{BAT}$ is not used, connect to ground. The device is UL recognized to ensure against reverse charging when used with a primary lithium battery. Go to <u>www.maxim-ic.com/qa/info/ul</u> .                                                                                                                                                                                                                                                                                                           |

| 15   | SDA             | Serial Data Input/Output. This pin is the data input/output for the $I^2C$ serial interface. This open-drain pin requires an external pullup resistor. The pullup voltage can be up to 5.5V, regardless of the voltage on V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16   | SCL             | Serial Clock Input. This pin is the clock input for the $I^2C$ serial interface and is used to synchronize data movement on the serial interface. Up to 5.5V can be used for this pin, regardless of the voltage on V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **Detailed Description**

The DS3231 is a serial RTC driven by a temperaturecompensated 32kHz crystal oscillator. The TCXO provides a stable and accurate reference clock, and maintains the RTC to within ±2 minutes per year accuracy from -40°C to +85°C. The TCXO frequency output is available at the 32kHz pin. The RTC is a low-power clock/calendar with two programmable time-of-day alarms and a programmable square-wave output. The INT/SQW provides either an interrupt signal due to alarm conditions or a square-wave output. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The

clock operates in either the 24-hour or 12-hour format with an  $\overline{AM}/PM$  indicator. The internal registers are accessible though an I<sup>2</sup>C bus interface.

A temperature-compensated voltage reference and comparator circuit monitors the level of V<sub>CC</sub> to detect power failures and to automatically switch to the backup supply when necessary. The RST pin provides an external pushbutton function and acts as an indicator of a power-fail event.

#### **Operation**

The block diagram shows the main elements of the DS3231. The eight blocks can be grouped into four functional groups: TCXO, power control, pushbutton function, and RTC. Their operations are described separately in the following sections.

#### 32kHz TCXO

The temperature sensor, oscillator, and control logic form the TCXO. The controller reads the output of the on-chip temperature sensor and uses a lookup table to determine the capacitance required, adds the aging correction in AGE register, and then sets the capacitance selection registers. New values, including changes to the AGE register, are loaded only when a change in the temperature value occurs, or when a user-initiated temperature conversion is completed. Temperature conversion occurs on initial application of V<sub>CC</sub> and once every 64 seconds afterwards.

#### **Power Control**

This function is provided by a temperature-compensated voltage reference and a comparator circuit that monitors the V<sub>CC</sub> level. When V<sub>CC</sub> is greater than V<sub>PF</sub>, the part is powered by V<sub>CC</sub>. When V<sub>CC</sub> is less than V<sub>PF</sub> but greater than V<sub>BAT</sub>, the DS3231 is powered by V<sub>CC</sub>. If V<sub>CC</sub> is less than V<sub>PF</sub> and is less than V<sub>BAT</sub>, the device is powered by V<sub>BAT</sub>. See Table 1.

#### **Table 1. Power Control**

| SUPPLY CONDITION                                                       | ACTIVE SUPPLY    |

|------------------------------------------------------------------------|------------------|

| V <sub>CC</sub> < V <sub>PF</sub> , V <sub>CC</sub> < V <sub>BAT</sub> | V <sub>BAT</sub> |

| $V_{CC} < V_{PF}, V_{CC} > V_{BAT}$                                    | V <sub>CC</sub>  |

| V <sub>CC</sub> > V <sub>PF</sub> , V <sub>CC</sub> < V <sub>BAT</sub> | V <sub>CC</sub>  |

| V <sub>CC</sub> > V <sub>PF</sub> , V <sub>CC</sub> > V <sub>BAT</sub> | V <sub>CC</sub>  |

To preserve the battery, the first time V<sub>BAT</sub> is applied to the device, the oscillator will not start up until V<sub>CC</sub> exceeds V<sub>PF</sub>, or until a valid I<sup>2</sup>C address is written to the part. Typical oscillator startup time is less than one second. Approximately 2 seconds after V<sub>CC</sub> is applied, or a valid I<sup>2</sup>C address is written, the device makes a temperature measurement and applies the calculated correction to the oscillator. Once the oscillator is running, it continues to run as long as a valid power source is available (V<sub>CC</sub> or V<sub>BAT</sub>), and the device continues to measure the temperature and correct the oscillator frequency every 64 seconds.

On the first application of power (V<sub>CC</sub>) or when a valid I<sup>2</sup>C address is written to the part (V<sub>BAT</sub>), the time and date registers are reset to 01/01/00 01 00:00:00 (MM/DD/YY DOW HH:MM:SS).

#### **VBAT Operation**

There are several modes of operation that affect the amount of  $V_{BAT}$  current that is drawn. While the device is powered by  $V_{BAT}$  and the serial interface is active,

active battery current, IBATA, is drawn. When the serial interface is inactive, timekeeping current (IBATT), which includes the averaged temperature conversion current, IBATTC, is used (refer to Application Note 3644: *Power Considerations for Accurate Real-Time Clocks* for details). Temperature conversion current, IBATTC, is specified since the system must be able to support the periodic higher current pulse and still maintain a valid voltage level. Data retention current, IBATTDR, is the current drawn by the part when the oscillator is stopped (EOSC = 1). This mode can be used to minimize battery requirements for times when maintaining time and date information is not necessary, e.g., while the end system is waiting to be shipped to a customer.

#### **Pushbutton Reset Function**

The DS3231 provides for a pushbutton switch to be connected to the RST output pin. When the DS3231 is not in a reset cycle, it continuously monitors the RST signal for a low going edge. If an edge transition is detected, the DS3231 debounces the switch by pulling the RST low. After the internal timer has expired (PB<sub>DB</sub>), the DS3231 continues to monitor the RST line. If the line is still low, the DS3231 continuously monitors the line looking for a rising edge. Upon detecting release, the DS3231 forces the RST pin low and holds it low for t<sub>RST</sub>.

RST is also used to indicate a power-fail condition. When V<sub>CC</sub> is lower than V<sub>PF</sub>, an internal power-fail signal is generated, which forces the RST pin low. When V<sub>CC</sub> returns to a level above V<sub>PF</sub>, the RST pin is held low for approximately 250ms (t<sub>REC</sub>) to allow the power supply to stabilize. If the oscillator is not running (see the *Power Control* section) when V<sub>CC</sub> is applied, t<sub>REC</sub> is bypassed and RST immediately goes high. Assertion of the RST output, whether by pushbutton or power-fail detection, does not affect the internal operation of the DS3231.

#### **Real-Time Clock**

With the clock source from the TCXO, the RTC provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with an AM/PM indicator.

The clock provides two programmable time-of-day alarms and a programmable square-wave output. The  $\overline{INT}/SQW$  pin either generates an interrupt due to alarm condition or outputs a square-wave signal and the selection is controlled by the bit INTCN.

| ADDRESS | BIT 7<br>MSB | BIT 6 | BIT 5            | BIT 4     | BIT 3        | BIT 2 | BIT 1 | BIT 0<br>LSB    | FUNCTION              | RANGE                 |

|---------|--------------|-------|------------------|-----------|--------------|-------|-------|-----------------|-----------------------|-----------------------|

| 00h     | 0            |       | 10 Second        | 0 Seconds |              | Secor | nds   |                 | Seconds               | 00–59                 |

| 01h     | 0            |       | 10 Minutes       | 5         |              | Minut | tes   |                 | Minutes               | 00–59                 |

| 02h     | 0            | 12/24 | AM/PM<br>20 Hour | 10 Hour   |              | Ηοι   | ır    |                 | Hours                 | 1–12 + AM/PM<br>00–23 |

| 03h     | 0            | 0     | 0                | 0         | 0            |       | Day   |                 | Day                   | 1–7                   |

| 04h     | 0            | 0     | 10               | Date      |              | Dat   | е     |                 | Date                  | 01–31                 |

| 05h     | Century      | 0     | 0                | 10 Month  |              | Mon   | th    |                 | Month/<br>Century     | 01–12 +<br>Century    |

| 06h     |              | 10    | Year             |           | 10 Year Year |       |       | Year            | 00–99                 |                       |

| 07h     | A1M1         |       | 10 Second        | S         |              | Secor | nds   |                 | Alarm 1 Seconds       | 00–59                 |

| 08h     | A1M2         |       | 10 Minutes       | 3         |              | Minut | tes   |                 | Alarm 1 Minutes       | 00–59                 |

| 09h     | A1M3         | 12/24 | AM/PM<br>20 Hour | 10 Hour   | Hour         |       | our   |                 | Alarm 1 Hours         | 1–12 + AM/PM<br>00–23 |

|         |              |       |                  |           |              | Dav   | y     |                 | Alarm 1 Day           | 1–7                   |

| 0Ah     | A1M4         | DY/DT | 101              | 10 Date   |              | Dat   | е     |                 | Alarm 1 Date          | 1–31                  |

| 0Bh     | A2M2         |       | 10 Minutes       | 6         | Minutes      |       |       | Alarm 2 Minutes | 00–59                 |                       |

| 0Ch     | A2M3         | 12/24 | AM/PM<br>20 Hour | 10 Hour   |              | Hour  |       | Alarm 2 Hours   | 1–12 + AM/PM<br>00–23 |                       |

|         |              |       |                  |           |              | Day   | y     |                 | Alarm 2 Day           | 1–7                   |

| 0Dh     | A2M4         | DY/DT | 101              | Date      | Date         |       |       | Alarm 2 Date    | 1–31                  |                       |

| 0Eh     | EOSC         | BBSQW | CONV             | RS2       | RS1          | INTCN | A2IE  | A1IE            | Control               |                       |

| 0Fh     | OSF          | 0     | 0                | 0         | EN32kHz      | BSY   | A2F   | A1F             | Control/Status        |                       |

| 10h     | SIGN         | DATA  | DATA             | DATA      | DATA         | DATA  | DATA  | DATA            | Aging Offset          |                       |

| 11h     | SIGN         | DATA  | DATA             | DATA      | DATA         | DATA  | DATA  | DATA            | MSB of Temp           |                       |

| 12h     | DATA         | DATA  | 0                | 0         | 0            | 0     | 0     | 0               | LSB of Temp           |                       |

#### **Figure 1. Timekeeping Registers**

Note: Unless otherwise specified, the registers' state is not defined when power is first applied.

Address Map

Figure 1 shows the address map for the DS3231 timekeeping registers. During a multibyte access, when the address pointer reaches the end of the register space (12h), it wraps around to location 00h. On an I<sup>2</sup>C START or address pointer incrementing to location 00h, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to reread the registers in case the main registers update during a read.

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C interface is accessible whenever either V<sub>CC</sub> or V<sub>BAT</sub> is at a valid level. If a microcontroller connected to the DS3231 resets because of a loss of V<sub>CC</sub> or other

DALLAS /////

event, it is possible that the microcontroller and DS3231 I<sup>2</sup>C communications could become unsynchronized, e.g., the microcontroller resets while reading data from the DS3231. When the microcontroller resets, the DS3231 I<sup>2</sup>C interface may be placed into a known state by toggling SCL until SDA is observed to be at a high level. At that point the microcontroller should pull SDA low while SCL is high, generating a START condition.

#### **Clock and Calendar**

The time and calendar information is obtained by reading the appropriate register bytes. Figure 1 illustrates the RTC registers. The time and calendar data are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in

#### Alarms

the binary-coded decimal (BCD) format. The DS3231 can be run in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12- or 24-hour mode select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic-high being PM. In the 24-hour mode, bit 5 is the 20-hour bit (20-23 hours). The century bit (bit 7 of the month register) is toggled when the years register overflows from 99 to 00.

The day-of-week register increments at midnight. Values that correspond to the day of week are userdefined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation.

When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers on any START and when the register pointer rolls over to zero. The time information is read from these secondary registers, while the clock continues to run. This eliminates the need to reread the registers in case the main registers update during a read.

The countdown chain is reset whenever the seconds register is written. Write transfers occur on the acknowledge from the DS3231. Once the countdown chain is reset, to avoid rollover issues the remaining time and date registers must be written within 1 second. The 1Hz square-wave output, if enabled, transitions high 500ms after the seconds data transfer, provided the oscillator is already running.

The DS3231 contains two time-of-day/date alarms. Alarm 1 can be set by writing to registers 07h to 0Ah. Alarm 2 can be set by writing to registers 0Bh to 0Dh. The alarms can be programmed (by the alarm enable and INTCN bits of the control register) to activate the INT/SQW output on an alarm match condition. Bit 7 of each of the time-of-dav/date alarm registers are mask bits (Table 2). When all the mask bits for each alarm are logic 0, an alarm only occurs when the values in the timekeeping registers match the corresponding values stored in the time-of-day/date alarm registers. The alarms can also be programmed to repeat every second, minute, hour, day, or date. Table 2 shows the possible settings. Configurations not listed in the table will result in illogical operation.

The DY/DT bits (bit 6 of the alarm day/date registers) control whether the alarm value stored in bits 0 to 5 of that register reflects the day of the week or the date of the month. If DY/DT is written to logic 0, the alarm will be the result of a match with date of the month. If DY/DT is written to logic 1, the alarm will be the result of a match with day of the week.

When the RTC register values match alarm register settings, the corresponding Alarm Flag 'A1F' or 'A2F' bit is set to logic 1. If the corresponding Alarm Interrupt Enable 'A1IE' or 'A2IE' is also set to logic 1 and the INTCN bit is set to logic 1, the alarm condition will activate the INT/SQW signal. The match is tested on the once-per-second update of the time and date registers.

| DY/DT       | ALARM                              | A 1 REGISTER | R MASK BITS         | (BIT 7)         |                                                                                       |

|-------------|------------------------------------|--------------|---------------------|-----------------|---------------------------------------------------------------------------------------|

| DY/DI       | A1M4                               | A1M3         | A1M2                | A1M1            | ALARM RATE                                                                            |

| Х           | 1                                  | 1            | 1                   | 1               | Alarm once per second                                                                 |

| Х           | 1                                  | 1            | 1                   | 0               | Alarm when seconds match                                                              |

| Х           | 1                                  | 1            | 0                   | 0               | Alarm when minutes and seconds match                                                  |

| Х           | 1                                  | 0            | 0                   | 0               | Alarm when hours, minutes, and seconds match                                          |

| 0           | 0                                  | 0            | 0                   | 0               | Alarm when date, hours, minutes, and seconds match                                    |

| 1           | 0                                  | 0            | 0                   | 0               | Alarm when day, hours, minutes, and seconds match                                     |

|             |                                    |              |                     |                 |                                                                                       |

|             | ALARM 2 REGISTER MASK BITS (BIT 7) |              |                     |                 |                                                                                       |

| DY/DT       |                                    |              |                     |                 |                                                                                       |

| וט,דט       | A2M4                               | A2           | M3                  | A2M2            |                                                                                       |

| X           | <b>A2M4</b>                        | A2           | <b>M3</b>           | <b>A2M2</b>     | Alarm once per minute (00 seconds of every minute)                                    |

|             | A2M4 1 1                           | A2           | <b>M3</b><br>1<br>1 | <b>A2M2</b> 1 0 | Alarm once per minute (00 seconds of every minute)           Alarm when minutes match |

| X           | A2M4 1 1 1 1 1                     | A2           | 1                   | 1               |                                                                                       |

| X<br>X<br>X | A2M4 1 1 1 0                       |              | 1<br>1<br>)         | 1<br>0          | Alarm when minutes match                                                              |

#### Table 2. Alarm Mask Bits

12

#### **Control Register (0Eh)**

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | EOSC  | BBSQW | CONV  | RS2   | RS1   | INTCN | A2IE  | A1IE  |

| POR:  | 0     | 0     | 0     | 1     | 1     | 1     | 0     | 0     |

#### **Special-Purpose Registers**

The DS3231 has two additional registers (control and status) that control the real-time clock, alarms, and square-wave output.

#### **Cont**rol Register (0Eh)

**Bit 7: Enable Oscillator (EOSC).** When set to logic 0, the oscillator is started. When set to logic 1, the oscillator is stopped when the DS3231 switches to V<sub>BAT</sub>. This bit is clear (logic 0) when power is first applied. When the DS3231 is powered by V<sub>CC</sub>, the oscillator is always on regardless of the status of the EOSC bit. When EOSC is disabled, all register data is static.

Bit 6: Battery-Backed Square-Wave Enable (BBSQW). When set to logic 1 with INTCN = 0 and V<sub>CC</sub> < V<sub>PF</sub>, this bit enables the square wave. When BBSQW is logic 0, the INT/SQW pin goes high impedance when V<sub>CC</sub> < V<sub>PF</sub>. This bit is disabled (logic 0) when power is first applied.

**Bit 5: Convert Temperature (CONV).** Setting this bit to 1 forces the temperature sensor to convert the temperature into digital code and execute the TCXO algorithm to update the capacitance array to the oscillator. This can only happen when a conversion is not already in progress. The user should check the status bit BSY before forcing the controller to start a new TCXO execution. A user-initiated temperature conversion does not affect the internal 64-second update cycle.

A user-initiated temperature conversion does not affect the BSY bit for approximately 2ms. The CONV bit remains at a 1 from the time it is written until the conversion is finished, at which time both CONV and BSY go to 0. The CONV bit should be used when monitoring the status of a user-initiated conversion.

**Bits 4 and 3: Rate Select (RS2 and RS1).** These bits control the frequency of the square-wave output when the square wave has been enabled. The following table

shows the square-wave frequencies that can be selected with the RS bits. These bits are both set to logic 1 (8.192kHz) when power is first applied.

#### SQUARE-WAVE OUTPUT FREQUENCY

| RS2 | RS1 | SQUARE-WAVE OUTPUT<br>FREQUENCY |

|-----|-----|---------------------------------|

| 0   | 0   | 1Hz                             |

| 0   | 1   | 1.024kHz                        |

| 1   | 0   | 4.096kHz                        |

| 1   | 1   | 8.192kHz                        |

**Bit 2: Interrupt Control (INTCN).** This bit controls the INT/SQW signal. When the INTCN bit is set to logic 0, a square wave is output on the INT/SQW pin. When the INTCN bit is set to logic 1, then a match between the timekeeping registers and either of the alarm registers activates the INT/SQW output (if the alarm is also enabled). The corresponding alarm flag is always set regardless of the state of the INTCN bit. The INTCN bit is set to logic 1 when power is first applied.

**Bit 1: Alarm 2 Interrupt Enable (A2IE).** When set to logic 1, this bit permits the alarm 2 flag (A2F) bit in the status register to assert  $\overline{INT}/SQW$  (when INTCN = 1). When the A2IE bit is set to logic 0 or INTCN is set to logic 0, the A2F bit does not initiate an interrupt signal. The A2IE bit is disabled (logic 0) when power is first applied.

**Bit 0: Alarm 1 Interrupt Enable (A1IE).** When set to logic 1, this bit permits the alarm 1 flag (A1F) bit in the status register to assert  $\overline{INT}/SQW$  (when INTCN = 1). When the A1IE bit is set to logic 0 or INTCN is set to logic 0, the A1F bit does not initiate the  $\overline{INT}/SQW$  signal. The A1IE bit is disabled (logic 0) when power is first applied.

**Status Register (0Fh)**

BIT 2 BIT 6 BIT 5 BIT 4 BIT 1 BIT 0 BIT 7 BIT 3 OSF EN32kHz A2F NAME: 0 0 0 BSY A1F POR: 0 0 1 0 1 Х Х Х

#### Status Register (0Fh)

**Bit 7: Oscillator Stop Flag (OSF).** A logic 1 in this bit indicates that the oscillator either is stopped or was stopped for some period and may be used to judge the validity of the timekeeping data. This bit is set to logic 1 any time that the oscillator stops. The following are examples of conditions that can cause the OSF bit to be set:

- 1) The first time power is applied.

- 2) The voltages present on both V<sub>CC</sub> and V<sub>BAT</sub> are insufficient to support oscillation.

- 3) The  $\overline{\text{EOSC}}$  bit is turned off in battery-backed mode.

- 4) External influences on the crystal (i.e., noise, leakage, etc.).

This bit remains at logic 1 until written to logic 0.

**Bit 3: Enable 32kHz Output (EN32kHz).** This bit controls the status of the 32kHz pin. When set to logic 1, the 32kHz pin is enabled and outputs a 32.768kHz squarewave signal. When set to logic 0, the 32kHz pin goes to a high-impedance state. The initial power-up state of this bit is logic 1, and a 32.768kHz square-wave signal appears at the 32kHz pin after a power source is applied to the DS3231 (if the oscillator is running).

**Bit 2: Busy (BSY).** This bit indicates the device is busy executing TCXO functions. It goes to logic 1 when the conversion signal to the temperature sensor is asserted and then is cleared when the device is in the 1-minute idle state.

**Bit 1: Alarm 2 Flag (A2F).** A logic 1 in the alarm 2 flag bit indicates that the time matched the alarm 2 registers. If the A2IE bit is logic 1 and the INTCN bit is set to logic 1, the INT/SQW pin is also asserted. A2F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1 leaves the value unchanged.

Bit 0: Alarm 1 Flag (A1F). A logic 1 in the alarm 1 flag bit indicates that the time matched the alarm 1 regis-

ters. If the A1<u>IE bit is logic 1 and the INTCN bit is set to logic 1, the INT/SQW pin is also asserted. A1F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1 leaves the value unchanged.</u>

#### **Aging Offset**

The aging offset register takes a user-provided value to add to or subtract from the codes in the capacitance array registers. The code is encoded in two's complement, with bit 7 representing the sign bit. One LSB represents one small capacitor to be switched in or out of the capacitance array at the crystal pins. The aging offset register capacitance value is added or subtracted from the capacitance value that the device calculates for each temperature compensation. The offset register is added to the capacitance array during a normal temperature conversion, if the temperature changes from the previous conversion, or during a manual user conversion (setting the CONV bit). To see the effects of the aging register on the 32kHz output frequency immediately, a manual conversion should be started after each aging register change.

Positive aging values add capacitance to the array, slowing the oscillator frequency. Negative values remove capacitance from the array, increasing the oscillator frequency.

The change in ppm per LSB is different at different temperatures. The frequency vs. temperature curve is shifted by the values used in this register. At  $+25^{\circ}$ C, one LSB typically provides about 0.1ppm change in frequency.

Use of the aging register is not needed to achieve the accuracy as defined in the EC tables, but could be used to help compensate for aging at a given temperature. See the *Typical Operating Characteristics* section for a graph showing the effect of the register on accuracy over temperature.

#### Aging Offset (10h)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | Sign  | Data  |

| POR:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

14

#### Temperature Register (Upper Byte) (11h)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | Sign  | Data  |

| POR:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Temperature Register (Lower Byte) (12h)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | Data  | Data  | 0     | 0     | 0     | 0     | 0     | 0     |

| POR:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### \_Temperature Registers (11h–12h)

Temperature is represented as a 10-bit code with a resolution of 0.25°C and is accessible at location 11h and 12h. The temperature is encoded in two's complement format. The upper 8 bits, the integer portion, are at location 11h and the lower 2 bits, the fractional portion, are in the upper nibble at location 12h. For example, 00011001 01b = +25.25°C. Upon power reset, the registers are set to a default temperature of 0°C and the controller starts a temperature conversion. The temperature is read on initial application of V<sub>CC</sub> or I<sup>2</sup>C access on V<sub>BAT</sub> and once every 64 seconds afterwards. The temperature registers are updated after each user-initiated conversion and on every 64-second conversion. The temperature registers are read-only.

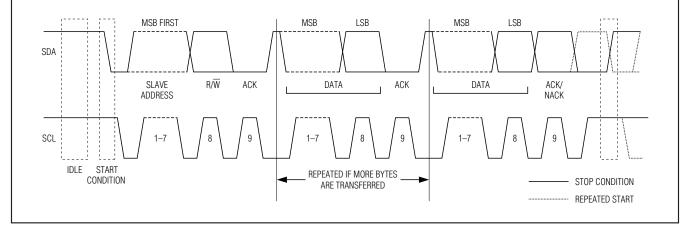

#### I<sup>2</sup>C Serial Data Bus

The DS3231 supports a bidirectional I<sup>2</sup>C bus and data transmission protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data is defined as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are slaves. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DS3231 operates as a slave on the I<sup>2</sup>C bus. Connections to the bus are made through the SCL input and open-drain SDA I/O lines. Within the bus specifications, a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. The DS3231 works in both modes.

The following bus protocol has been defined (Figure 2):

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is high. Changes in the data

line while the clock line is high are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

**Bus not busy:** Both data and clock lines remain high.

**START data transfer:** A change in the state of the data line from high to low, while the clock line is high, defines a START condition.

**STOP data transfer:** A change in the state of the data line from low to high, while the clock line is high, defines a STOP condition.

**Data valid:** The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the high period of the clock signal. The data on the line must be changed during the low period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between the START and the STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse, which is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the

**DS3231**

Figure 2. I<sup>2</sup>C Data Transfer Overview

slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line high to enable the master to generate the STOP condition.

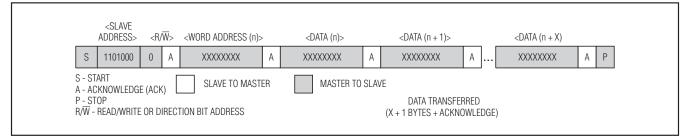

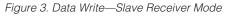

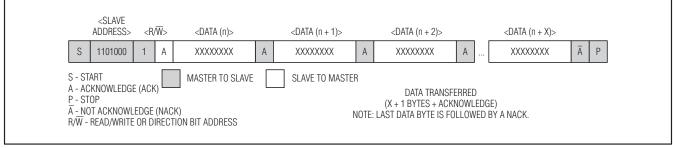

Figures 3 and 4 detail how data transfer is accomplished on the  $I^2C$  bus. Depending upon the state of the R/W bit, two types of data transfer are possible:

Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is

the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first.

**Data transfer from a slave transmitter to a master receiver.** The first byte (the slave address) is transmitted by the master. The slave then returns an acknowledge bit. Next follows a number of data bytes transmitted by the slave to the master. The

Figure 4. Data Read—Slave Transmitter Mode

Figure 5. Data Write/Read (Write Pointer, Then Read)—Slave Receive and Transmit

master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a not acknowledge is returned.

The master device generates all the serial clock pulses es and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released. Data is transferred with the most significant bit (MSB) first.

The DS3231 can operate in the following two modes:

Slave receiver mode (DS3231 write mode): Serial data and clock are received through SDA and SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit. The slave address byte is the first byte received after the master generates the START condition. The slave address byte contains the 7-bit DS3231 address, which is 1101000, followed by the direction bit (R/W), which is 0 for a write. After receiving and decoding the slave address byte, the DS3231 outputs an acknowledge on SDA. After the DS3231 acknowledges the slave address + write bit, the master transmits a word address to the DS3231. This sets the register pointer on the DS3231, with the DS3231

acknowledging the transfer. The master may then transmit zero or more bytes of data, with the DS3231 acknowledging each byte received. The register pointer increments after each data byte is transferred. The master generates a STOP condition to terminate the data write.

Slave transmitter mode (DS3231 read mode): The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. Serial data is transmitted on SDA by the DS3231 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit. The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit DS3231 address, which is 1101000, followed by the direction bit (R/W), which is 1 for a read. After receiving and decoding the slave address byte, the DS3231 outputs an acknowledge on SDA. The DS3231 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode, the first address that is read is the last one stored in the register pointer. The DS3231 must receive a not acknowledge to end a read.

# **DS3231**

#### Handling, PC Board Layout, \_\_\_\_\_and Assembly

The DS3231 package contains a quartz tuning-fork crystal. Pick-and-place equipment can be used, but precautions should be taken to ensure that excessive shocks are avoided. Ultrasonic cleaning should be avoided to prevent damage to the crystal.

Avoid running signal traces under the package, unless a ground plane is placed between the package and the signal line. All N.C. (no connect) pins must be connected to ground.

Moisture-sensitive packages are shipped from the factory dry packed. Handling instructions listed on the package label must be followed to prevent damage during reflow. Refer to the IPC/JEDEC J-STD-020 standard for moisture-sensitive device (MSD) classifications and reflow profiles. Exposure to reflow is limited to 2 times maximum.

#### \_\_Chip Information

SUBSTRATE CONNECTED TO GROUND PROCESS: CMOS

#### **Package Information**

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND           |

|---------|---------|----------------|----------------|

| TYPE    | CODE    | NO.            | PATTERN NO.    |

| 16 SO   | W16#H2  | <u>21-0042</u> | <u>90-0107</u> |

#### **Revision History**

| REVISION<br>NUMBER            | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                   | PAGES<br>CHANGED |

|-------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                             | 1/05             | Initial release.                                                                                                                                                                                                              | _                |

|                               |                  | Changed Digital Temp Sensor Output from $\pm 2^{\circ}$ C to $\pm 3^{\circ}$ C.                                                                                                                                               | 1, 3             |

|                               | 0/05             | Updated Typical Operating Circuit.                                                                                                                                                                                            | 1                |

| 1 2/05                        | 2/05             | Changed $T_A = -40^{\circ}C$ to $+85^{\circ}C$ to $T_A = T_{MIN}$ to $T_{MAX}$ .                                                                                                                                              | 2, 3, 4          |

| Updated <i>Block Diagram.</i> |                  | Updated Block Diagram.                                                                                                                                                                                                        | 8                |

|                               |                  | Added "UL Recognized" to <i>Features</i> ; added lead-free packages and removed S from top mark info in <i>Ordering Information</i> table; added ground connections to the N.C. pin in the <i>Typical Operating Circuit</i> . | 1                |

| 2                             |                  | Added "noncondensing" to operating temperature range; changed $V_{\text{PF}}$ MIN from 2.35V to 2.45V.                                                                                                                        | 2                |

|                               |                  | Added aging offset specification.                                                                                                                                                                                             | 3                |

|                               |                  | Relabeled TOC4.                                                                                                                                                                                                               | 7                |

|                               |                  | Added arrow showing input on X1 in the Block Diagram.                                                                                                                                                                         | 8                |

|                               | 6/05             | Updated pin descriptions for V <sub>CC</sub> and V <sub>BAT</sub> .                                                                                                                                                           | 9                |

|                               | 0/05             | Added the <i>I</i> <sup>2</sup> <i>C</i> Interface section.                                                                                                                                                                   | 10               |

|                               |                  | Figure 1: Added sign bit to aging and temperature registers; added MSB and LSB.                                                                                                                                               | 11               |

|                               |                  | Corrected title for rate select bits frequency table.                                                                                                                                                                         | 13               |

|                               |                  | Added note that frequency stability over temperature spec is with aging offset register = 00h; changed bit 7 from Data to Sign (Crystal Aging Offset Register).                                                               | 14               |

|                               |                  | Changed bit 7 from Data to Sign (Temperature Register); correct pin definitions in $l^2C$<br>Serial Data Bus section.                                                                                                         | 15               |

|                               |                  | Modified the <i>Handing, PC Board Layout, and Assembly</i> section to refer to J-STD-020 for reflow profiles for lead-free and leaded packages.                                                                               | 17               |

| 3                             | 11/05            | Changed lead-free packages to RoHS-compliant packages.                                                                                                                                                                        | 1                |

|                               |                  | Changed RST and UL bullets in <i>Features</i> .                                                                                                                                                                               | 1                |

|                               |                  | Changed EC condition "V <sub>CC</sub> > V <sub>BAT</sub> " to "V <sub>CC</sub> = Active Supply (see Table 1)."                                                                                                                | 2, 3             |

|                               |                  | Modified Note 12 to correct t <sub>REC</sub> operation.                                                                                                                                                                       | 6                |

|                               |                  | Added various conditions text to TOCs 1, 2, and 3.                                                                                                                                                                            | 7                |

|                               | 10/22            | Added text to pin descriptions for 32kHz, V <sub>CC</sub> , and <del>RST</del> .                                                                                                                                              | 9                |

| 4                             | 10/06            | Table 1: Changed column heading "Powered By" to "Active Supply"; changed "applied" to "exceeds V <sub>PF</sub> " in the <i>Power Control</i> section.                                                                         | 10               |

|                               |                  | Indicated BBSQW applies to both SQW and interrupts; simplified temp convert description (bit 5); added "output" to INT/SQW (bit 2).                                                                                           | 13               |

|                               |                  | Changed the <i>Crystal Aging</i> section to the <i>Aging Offset</i> section; changed "this bit indicates" to "this bit controls" for the enable 32kHz output bit.                                                             | 14               |

|                               |                  | Added Warning note to EC table notes; updated Note 12.                                                                                                                                                                        | 6                |

|                               |                  | Updated the Typical Operating Characteristics graphs.                                                                                                                                                                         | 7                |

| 5                             | 4/08             | In the <i>Power Control</i> section, added information about the POR state of the time and date registers; in the <i>Real-Time Clock</i> section, added to the description of the RST function.                               | 10               |

|                               | 1                | In Figure 1, corrected the months date range for 04h from 00-31 to 01-31.                                                                                                                                                     |                  |

#### **Revision History (continued)**