# Single Bus LVDS Transceiver

#### **Features**

- Bus LVDS Signaling (BLVDS)

- Designed for Double Termination Applications

- · Balanced Output Impedance

- · Light Bus Loading: 5pF typical

- Glitch-free power up/down (Driver Disabled)

- Operates from a 3.3V supply

- High Signaling Rate Capability: >100Mbps

- Driver:

- $-\pm 250$ mV Differential Swing into a  $27\Omega$  load

- Propagation Delay of 1.5ns typ.

- Low Voltage TTL (LVTTL) Inputs are 5V Tolerant

- Receiver

- Accepts ±50mV (min.) Differential Swing with up to 2.0V ground potential difference

- Propagation Delay of 3.3ns typical

- Low Voltage TTL (LVTTL) Outputs

- Open, Short, and Terminated Fail Safe

- Bus terminal ESD exceeds 10kV

- Industrial Temperature Operation (-40°C to +85°C)

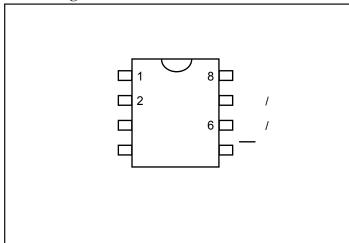

- Packaging (Pb-free & Green available):

- 8-lead SOIC (W)

- 8-lead MSOP (U)

### **Description**

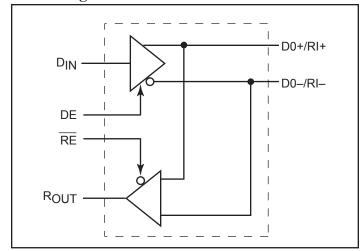

The PI90LVB010 is a differential line driver and receiver (transceiver) that is similar to the IEEE1596.3 SCI and ANSI/TIA/EIA-644LVDS standards, the difference is that the driver output current is higher. This modification enables true half-duplex operation with more than one LVDS driver or with two line transmission resistors over a  $50\Omega$  differential transmission line. To minimize bus loading, the driver outputs and receiver inputs are internally connected. The logic interface provides maximum flexibility resulting from four separate lines that are provided:  $D_{IN}$ , DE,  $\overline{RE}$ , and  $R_{OUT}$ .

This device also feature flow-through which allows easy PCB routing for short stubs between the bus pins and the connector. The driver has 10mA drive capability, allowing it to drive heavily loaded backplanes, with impedance as low as  $27\Omega$ .

The driver translates between TTL levels (single-ended) to Low Voltage Differential Signaling levels. This allows for high-speed operation, while consuming minimal power with reduced EMI. In addition the differential signaling provides common mode noise rejection of  $\pm 1$ V.

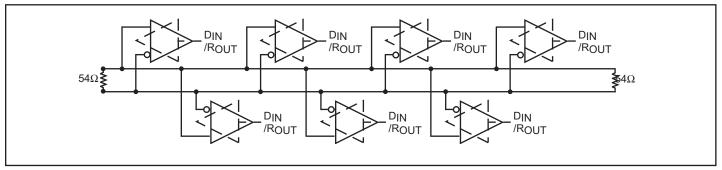

#### **Block Diagram**

#### **Pin Configuration**

08-0295 1 PS8662B 11/11/08

# **Absolute Maximum Ratings**(1,2)

| 6.0V                   |

|------------------------|

| V to $(V_{CC} + 0.3V)$ |

| V to $(V_{CC} + 0.3V)$ |

| V to $(V_{CC} + 0.3V)$ |

| 0.3V to +3.9V          |

| Continuous             |

| >10kV                  |

|                        |

| 1025mW                 |

| 8.2mW/°C               |

|                        |

| Storage Temperature Range       | 65°C to +150°C |

|---------------------------------|----------------|

| Lead Temperature Range (Solderi | ng, 4s)+260°C  |

# **Recommended Operating Conditions**

|                                   | Min. | Max. | Units |

|-----------------------------------|------|------|-------|

| Supply Voltage (V <sub>CC</sub> ) | 3.0  | 3.6  | V     |

| Receiver Input Voltage            | 0.0  | 2.9  | V     |

| Operating Free-Air Temperature    | -40  | +85  | °C    |

#### Note:

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Functional Mode**

| Mode Select    | DE | RE |

|----------------|----|----|

| Driver Mode    | Н  | Н  |

| Receiver Mode  | L  | L  |

| 3-State Mode   | L  | Н  |

| Loop Back Mode | Н  | L  |

## **Transmitter Mode**

| Inputs |             | Out | puts |

|--------|-------------|-----|------|

| DE     | DI          | DO+ | DO-  |

| Н      | L           | L   | Н    |

| Н      | Н           | Н   | L    |

| Н      | 2 > & > 0.8 | X   | X    |

| L      | X           | Z   | Z    |

| Н      | Open        | L   | Н    |

### **Receiver Mode**

|    | Outputs                 |   |

|----|-------------------------|---|

| RE | <b>RE</b> (RE+) - (RI-) |   |

| L  | L (< -100mV)            | L |

| L  | H (> + 100mV)           | Н |

| L  | 100 mV > & > -100 mV    | ? |

| Н  | X                       | Z |

#### Notes:

1. H = High, L = Low, Z = High Impedance, X = High or Low

### **Pin Description**

| Pin<br>Name      | Pin# | Inputs/ Description Outputs |                                              |

|------------------|------|-----------------------------|----------------------------------------------|

| $D_{IN}$         | 2    | I                           | TTL Driver Input                             |

| DO±<br>RI±       | 6, 7 | I/O                         | LVDS Driver Outputs/<br>LVDS Receiver Inputs |

| R <sub>OUT</sub> | 3    | О                           | TTL Receiver Outputs                         |

| RE               | 5    | I                           | Receiver Enable TTL Input (Active Low)       |

| DE               | 1    | I                           | Driver Enable TTL Input<br>(Active High)     |

| GND              | 4    | NA                          | Ground                                       |

| V <sub>CC</sub>  | 8    | NA Power Supply             |                                              |

**DC Electrical Characteristics** $^{(2,3)}$  (T<sub>A</sub> =  $-40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. V<sub>CC</sub> =  $3.3V \pm 0.3V$ )

| Symbol                   | Parameter                        | Test Condition                                         |                 | Pin                | Min. | Тур. | Max.     | Units |

|--------------------------|----------------------------------|--------------------------------------------------------|-----------------|--------------------|------|------|----------|-------|

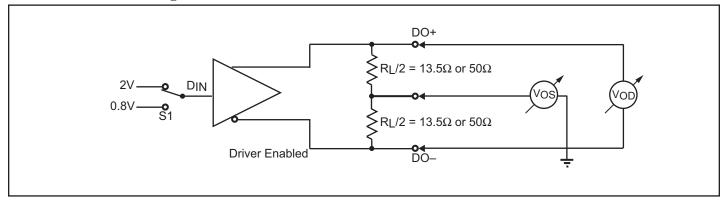

| V <sub>OD</sub>          | Output Differential Voltage      |                                                        |                 |                    | 140  | 250  | 360      |       |

| $\Delta V_{\mathrm{OD}}$ | V <sub>OD</sub> Magnitude Change |                                                        |                 |                    |      | 3    | 30       | mV    |

| Vos                      | Offset Voltage                   | $R_L = 27\Omega$ , See figure                          | 1               | DO+/RI+<br>DO-/RI- | 1    | 1.25 | 1.65     | V     |

| $\Delta V_{OS}$          | Offset Magnitude Change          |                                                        |                 | DO-/KI-            |      | 5    | 50       | mV    |

| I <sub>OSD</sub>         | Output Short Circuit Current     | $V_{O} = 0V$ , DE = $V_{CC}$                           |                 |                    |      | -12  | -20      | mA    |

|                          |                                  | $V_{\rm ID} = +100 \rm mV$                             |                 |                    | 2.8  | 3    |          |       |

|                          |                                  | Inputs Open                                            | ]               |                    | 2.8  | 3    |          |       |

| $V_{OH}$                 | Voltage Output High              | Inputs Shorted                                         | $I_{OH} = -400$ | R <sub>OUT</sub>   | 2.8  | 3    |          | V     |

|                          |                                  | Inputs Terminated, $R_L = 27\Omega$                    |                 |                    | 2.8  | 3    |          | ·     |

| $V_{OL}$                 | Voltage Output Low               | $I_{OL} = 2.0 \text{mA}, V_{ID} = -1$                  | 100mV           |                    |      | 0.1  | 0.4      |       |

| I <sub>OS</sub>          | Output Short Circuit Curretn     | $V_{OUT} = 0V, V_{ID} = 100$                           | )V              |                    | -5   | -35  | -85      | mA    |

| $V_{TH}$                 | Input Threshold High             | DE = 0V                                                |                 |                    |      |      | 100      | V     |

| $V_{TL}$                 | Input Threshold Low              |                                                        |                 | DO+/RI+            | -100 |      |          | mV    |

| I                        | In most Comment                  | $DE = 0V, V_{IN} = 2.4V \text{ or } 0V$                |                 | DO-/RI-            | -20  | ±1   | 20       | 4     |

| $I_{IN}$                 | Input Current                    | $V_{CC} = 0V, V_{IN} = 2.4V \text{ or } 0V$            |                 |                    | -20  | ±1   | 20       | μA    |

| $V_{IH}$                 | Minimum Input High Voltage       |                                                        |                 | IN, DE, RE         | 2.0  |      | $V_{CC}$ | V     |

| $V_{\rm IL}$             | Minimum Input Low Voltage        |                                                        |                 |                    | GND  |      | 0.8      | V     |

| I <sub>IH</sub>          | Input High Current               | $V_{IN} = V_{CC}$ or 2.4V                              |                 |                    |      | ±1   | 10       | 4     |

| $I_{IL}$                 | Input Low Current                | $V_{IN} = GND \text{ or } 0.4V$                        |                 |                    |      | ±1   | 10       | μΑ    |

| $V_{CL}$                 | Input Diode Clamp Voltage        | $I_{CLAMP} = -18mA$                                    |                 |                    | -1.5 | -0.8 |          | V     |

| I <sub>CCD</sub>         |                                  | $DE = \overline{RE} = V_{CC}, R_L =$                   | - 27Ω           | V <sub>CC</sub>    |      | 13   | 20       |       |

| I <sub>CCR</sub>         | Downer Committee Comment         | $DE = \overline{RE} = 0V$                              |                 |                    |      | 5    | 8        | A     |

| I <sub>CCZ</sub>         | Power Supply Current             | $DE = 0V, \overline{RE} = V_{CC}$                      |                 |                    |      | 3    | 7.5      | mA    |

| I <sub>CC</sub>          | ]                                | $DE = V_{CC}$ , $\overline{RE}$ - 0V, $R_L = 27\Omega$ |                 |                    |      | 16   | 22       |       |

| Соитрит                  | Bus Pin Capacitance              |                                                        |                 | DO+/RI+<br>DO-/RI- |      | 5    |          | pF    |

#### Notes:

- 1. "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

- All currents into device pins are positive, all currents out of device pins are negative. All voltages are referenced to ground except: V<sub>OD</sub>, V<sub>ID</sub>, V<sub>TH</sub>, and V<sub>TL</sub>, unless otherwise specified.

- 3. All typicals are given for  $V_{CC} = +3.3 \text{V}$  or 5.0V and  $T_A = +25 ^{\circ}\text{C}$  unless otherwise stated.

- 4. ESD Rating: HBM  $(15k\Omega, 100pF) > 2.0kV$  EAT  $(0\Omega, 200pF) > 300V$ .

- 5.  $C_L$  includes probe and jig capacitance.

- 6. Generator waveforms for all tests unless otherwise specified: f = 1 MHz,  $ZO = 50\Omega$ ,  $t_r$ ,  $t_f \le 6.0 ns$  (0% 100%) on control pins and  $\le 1.0 ns$  for  $R_I$  inputs.

- The PI90LVB010 is a current mode device and only functions with datasheet specification when a resistive load is appplied between the driver outputs.

- 8. For receiver disable delays, the switch is set to  $V_{CC}$  for  $t_{PZL}$ , and  $t_{PLZ}$  and to GND for  $t_{PZH}$  and  $t_{PHZ}$ .

08-0295 3 PS8662B 11/11/08

# **AC Electrical Characteristics** $(T_A = -40$ °C to +85°C, $V_{CC} = 3.3$ V $\pm 0.3$ V)

| Symbol             | Paramter                                                  | Test Conditions                    | Min. | Тур. | Max. | Units |

|--------------------|-----------------------------------------------------------|------------------------------------|------|------|------|-------|

| Differential D     | river Timing Requirement                                  |                                    |      |      |      |       |

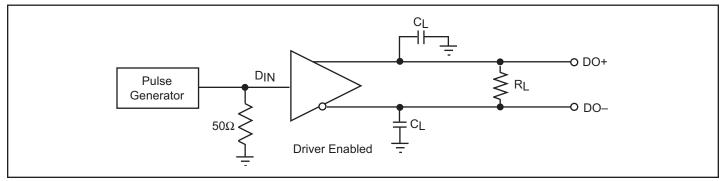

| t <sub>PHLD</sub>  | Differenital Propagation Delay High to Low                |                                    | 0.7  | 1.5  | 2.7  |       |

| t <sub>PLHD</sub>  | Differential Propagation Delay Low to High                | $R_{\rm L} = 27\Omega$             | 0.7  | 1.5  | 2.7  | ]     |

| $t_{SKD}$          | Differential Skew   t <sub>PHLD</sub> - t <sub>PLHD</sub> | Figures 2 & 3                      |      | 0.2  | 1.0  | ]     |

| t <sub>TLH</sub>   | Transition Time Low to High                               | $C_L = 10 pF$                      |      | 0.3  | 0.9  | ]     |

| $t_{\mathrm{THL}}$ | Transition Time High to Low                               |                                    |      | 0.3  | 0.9  | ns    |

| $t_{PHZ}$          | Disable Time High to Z                                    |                                    | 0.5  | 2.6  | 3.3  | ]     |

| $t_{PLZ}$          | Disable Time Low to Z                                     | $R_L = 27\Omega$ Figures 4 & 5     | 0.5  | 2.6  | 3.3  | ]     |

| t <sub>PZH</sub>   | Enable Time Z to High                                     | $C_{L} = 10 \text{pF}$             | 0.5  | 2.6  | 3.3  | ]     |

| $t_{PZL}$          | Enable Time Z to Low                                      |                                    | 0.5  | 2.6  | 3.3  | ]     |

| Differential R     | eceicer Timing Requirements                               |                                    |      | ·    |      |       |

| t <sub>PHLD</sub>  | Differential Propagation Delay High to Low                |                                    | 1.3  | 2.1  | 3.2  | ]     |

| $t_{PLHD}$         | Differenital Propagation Delay Low to High                |                                    | 1.3  | 2.1  | 3.2  | ]     |

| $t_{SKD}$          | Differential Skew   t <sub>PHLD</sub> - t <sub>PLHD</sub> | Figures 6 & 7 $C_L = 10 \text{pF}$ |      | 0.5  | 2.0  |       |

| $t_{R}$            | Rise Time                                                 |                                    |      | 0.8  | 1.4  |       |

| $t_{\mathrm{F}}$   | Fall Time                                                 |                                    |      | 1.8  | 1.4  | ns    |

| t <sub>PHZ</sub>   | Disable Time High to Z                                    |                                    | 1.5  | 4.0  | 6.0  | 1     |

| $t_{PLZ}$          | Disable Time Low to Z                                     | $R_L = 500\Omega$                  | 5.0  | 4.0  | 7.0  | 1     |

| t <sub>PZH</sub>   | Enable Time Z to High                                     | Figures 8 & 9 $C_L = 10 pF^{(8)}$  | 0.5  | 2.5  | 7.0  |       |

| t <sub>PZL</sub>   | Enable Time Z to Low                                      | <b></b>                            | 0.5  | 2.5  | 6.0  | ]     |

# **Test Circuits and Timing Waveforms**

Figure 1. Differential Driver DC Test Circuit

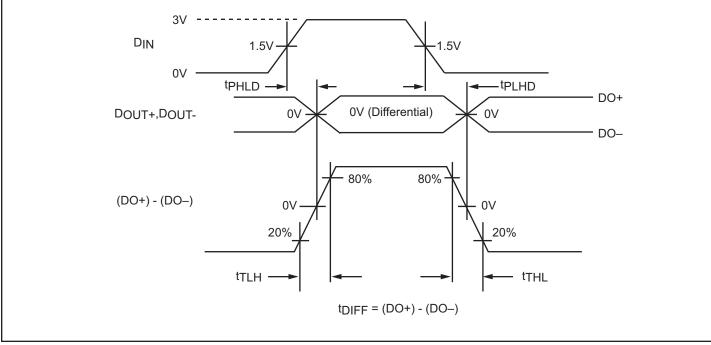

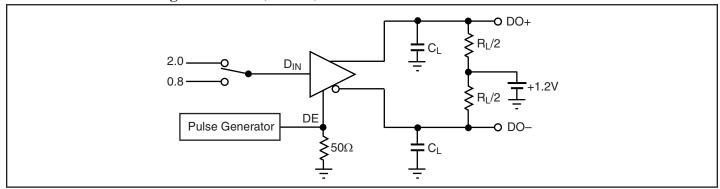

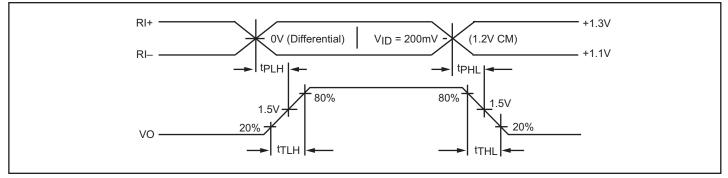

Figure 2. Differential Driver Propagation Delay and Transition Time Test Circuit

Figure 3. Driver Propagation Delay and Transition Time Waveforms

08-0295 5 PS8662B 11/11/08

# Test Circuits and Timing Waveforms (continued)

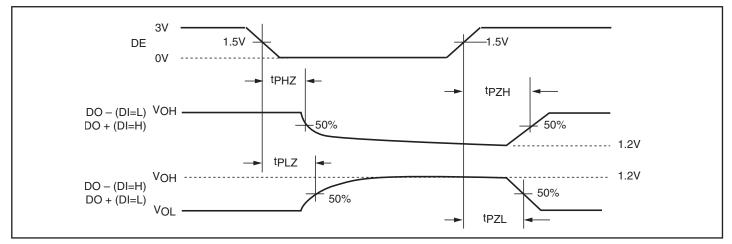

Figure 4. Driver Three-State Delay Test Circuit

Figure 5. Driver Three-State Delay Waveforms

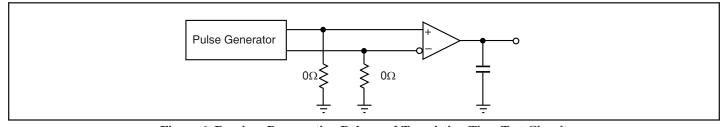

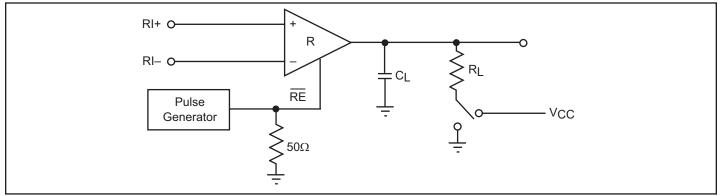

Figure 6. Receiver Propagation Delay and Transistion Time Test Circuit

Figure 7. Receiver Propagation Delay and Transistion Time Waveforms

08-0295 6 PS8662B 11/11/08

# Test Circuits and Timing Waveforms (continued)

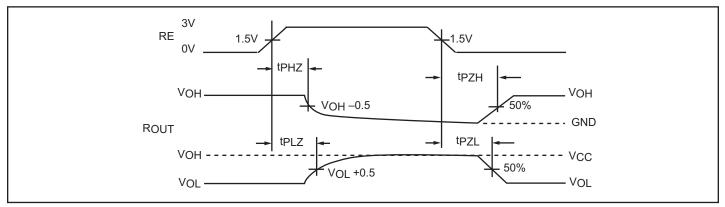

Figure 8. Receiver Three-State Delay Test Circuit

Figure 9. Receiver Three-State Delay Waveforms

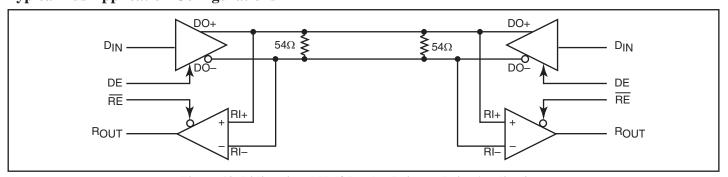

# **Typical Bus Application Configurations**

Figure 10. Bidirectional Half-Duplex Point-to-Point Applications

Figure 11. Multipoint Bus Applications

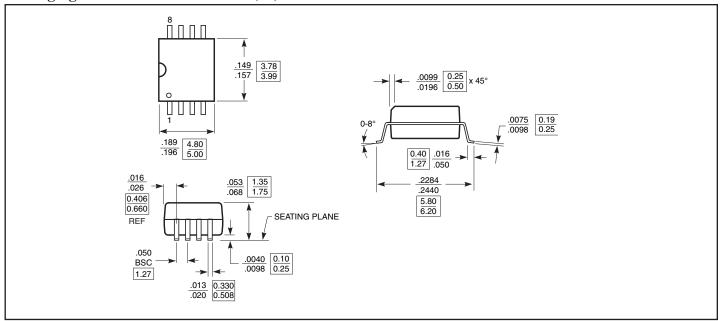

# Packaging Mechanical: 8-Pin SOIC (W)

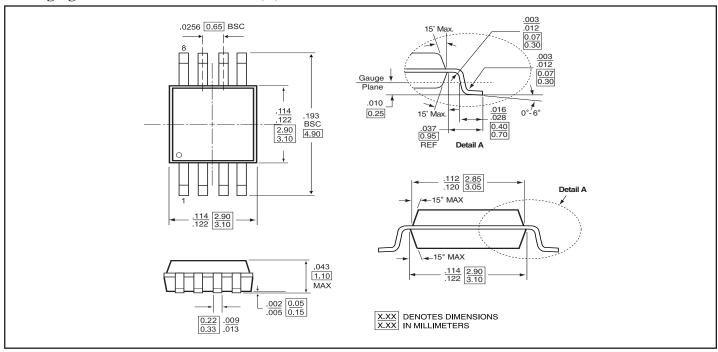

# Packaging Mechanical: 8-Pin MSOP (U)

# **Ordering Information**

| Ordering Code | Package Code | Package Description          |

|---------------|--------------|------------------------------|

| PI90LVB010WE  | W            | Pb-free & Green, 8-pin, SOIC |

| PI90LVB010UE  | U            | Pb-free & Green, 8-pin MSOP  |

#### **Notes:**

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/