# 250 kSPS, 12-Bit Impedance Converter, Network Analyzer

AD5934

#### **FEATURES**

Programmable output peak-to-peak excitation voltage to a maximum frequency of 100 kHz

Programmable frequency sweep capability with serial  $I^2C$  interface

Frequency resolution of 27 bits (<0.1 Hz)

Impedance measurement range from 1 k $\Omega$  to 10 M $\Omega$

Capable of measuring 100  $\Omega$  to 1  $k\Omega$  with additional circuitry Phase measurement capability

System accuracy of 0.5%

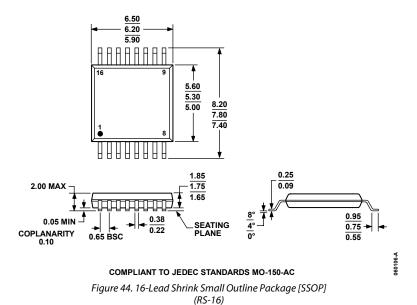

2.7 V to 5.5 V power supply operation Temperature range: -40°C to +125°C 16-lead SSOP package

## **APPLICATIONS**

Electrochemical analysis

Bioelectrical impedance analysis

Impedance spectroscopy

Complex impedance measurement

Corrosion monitoring and protection equipment

Biomedical and automotive sensors

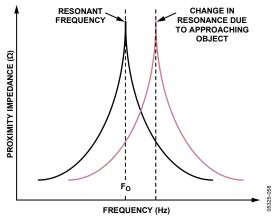

Proximity sensing

Nondestructive testing

Material property analysis

Fuel/battery cell condition monitoring

#### **GENERAL DESCRIPTION**

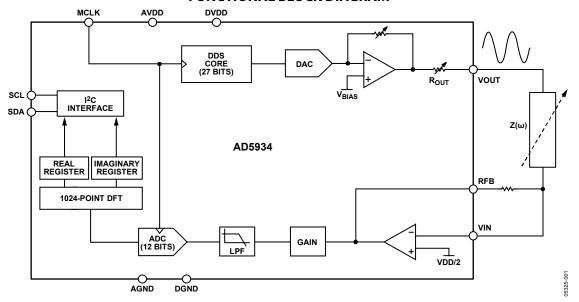

The AD5934 is a high precision impedance converter system solution that combines an on-board frequency generator with a 12-bit, 250 kSPS, analog-to-digital converter (ADC). The frequency generator allows an external complex impedance to be excited with a known frequency. The response signal from the impedance is sampled by the on-board ADC and a discrete Fourier transform (DFT) is processed by an on-board DSP engine. The DFT algorithm returns a real (R) and imaginary (I) data-word at each output frequency.

Once calibrated, the magnitude of the impedance and relative phase of the impedance at each frequency point along the sweep is easily calculated using the following two equations:

$$Magnitude = \sqrt{R^2 + I^2}$$

$$Phase = \tan^{-1}(I/R)$$

A similar device, available from Analog Devices, Inc., is the AD5933, which is a 2.7 V to 5.5 V, 1 MSPS, 12-bit impedance converter, with an internal temperature sensor, available in a 16-lead SSOP.

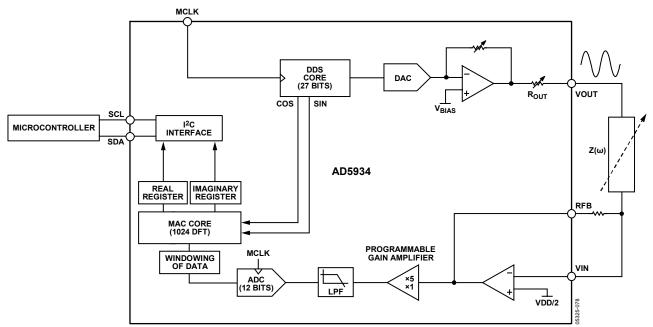

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Rev. A Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2005–2008 Analog Devices, Inc. All rights reserved.

## **TABLE OF CONTENTS**

| Features                                                  | I    |

|-----------------------------------------------------------|------|

| Applications                                              | 1    |

| General Description                                       | 1    |

| Functional Block Diagram                                  | 1    |

| Revision History                                          | 3    |

| Specifications                                            | 4    |

| I <sup>2</sup> C Serial Interface Timing Characteristics  | 6    |

| Absolute Maximum Ratings                                  | 7    |

| ESD Caution                                               | 7    |

| Pin Configuration and Function Descriptions               | 8    |

| Typical Performance Characteristics                       | 9    |

| Teminology                                                | . 11 |

| System Description                                        | . 12 |

| Transmit Stage                                            | . 13 |

| Frequency Sweep Command Sequence                          | . 14 |

| Receive Stage                                             | . 14 |

| DFT Operation                                             | . 14 |

| Impedance Calculation                                     | . 15 |

| Magnitude Calculation                                     | . 15 |

| Gain Factor Calculation                                   | . 15 |

| Impedance Calculation Using Gain Factor                   | . 15 |

| Gain Factor Variation with Frequency                      | . 15 |

| 2-Point Calibration                                       | . 16 |

| 2-Point Gain Factor Calculation                           | . 16 |

| Gain Factor Setup Configuration                           | . 16 |

| Gain Factor Recalculation                                 | . 16 |

| Gain Factor Temperature Variation                         |      |

| Impedance Error                                           | . 17 |

| Measuring the Phase Across an Impedance                   | . 19 |

| Performing a Frequency Sweep                              | . 21 |

| Register Map                                              | . 22 |

| Control Register (Register Address 0x80, Register Address |      |

| 0x81)                                                     | . 22 |

| Start Frequency Register (Register Address 0x82, Register Address 0x83, Register Address 0x84)                                         | . 23 |

|----------------------------------------------------------------------------------------------------------------------------------------|------|

| Frequency Increment Register (Register Address 0x85, Register Address 0x86, Register Address 0x87)                                     | . 23 |

| Number of Increments Register (Register Address 0x88, Register Address 0x89)                                                           | . 24 |

| Number of Settling Time Cycles Register (Register Address 0x8A, Register Address 0x8B)                                                 |      |

| Status Register (Register Address 0x8F)                                                                                                | . 24 |

| Real and Imaginary Data Registers (16 Bits—Register Address 0x94, Register Address 0x95, Register Address 0x96, Register Address 0x97) |      |

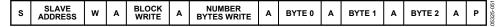

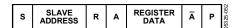

| Serial Bus Interface                                                                                                                   | . 26 |

| General I <sup>2</sup> C Timing                                                                                                        | . 26 |

| Writing/Reading to the AD5934                                                                                                          | . 27 |

| Block Write                                                                                                                            | . 27 |

| Read Operations                                                                                                                        | . 28 |

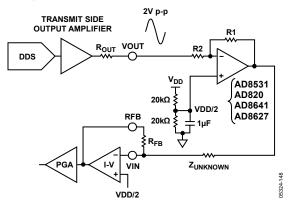

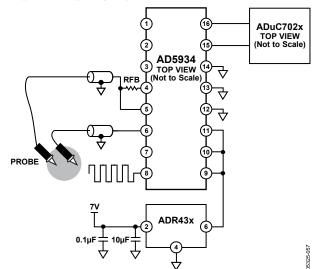

| Typical Applications                                                                                                                   | . 29 |

| Measuring Small Impedances                                                                                                             | . 29 |

| Biomedical: Noninvasive Blood impedance Measurement                                                                                    | . 30 |

| Sensor/Complex Impedance Measurement                                                                                                   | . 31 |

| Electro-Impedance Spectroscopy                                                                                                         | . 31 |

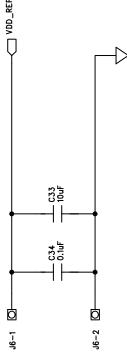

| Choosing a Reference for the AD5934                                                                                                    | . 32 |

| Layout and Configuration                                                                                                               | . 33 |

| Power Supply Bypassing and Grounding                                                                                                   | . 33 |

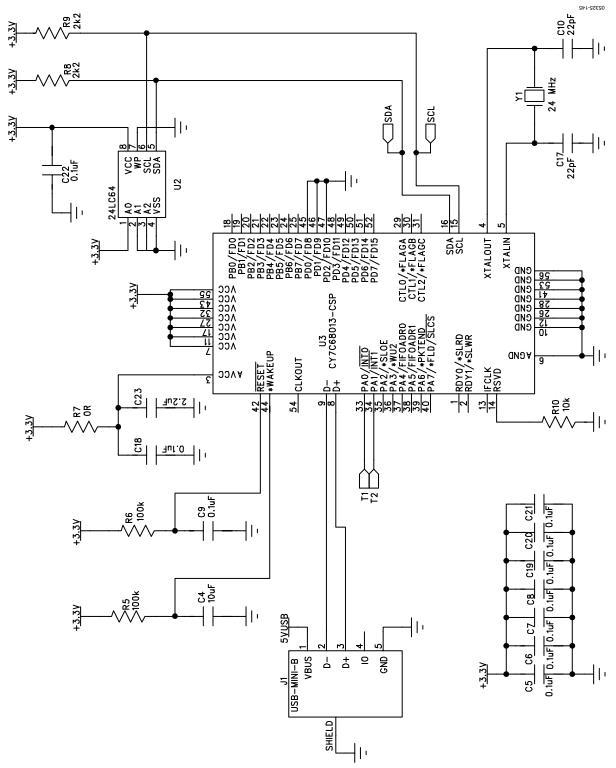

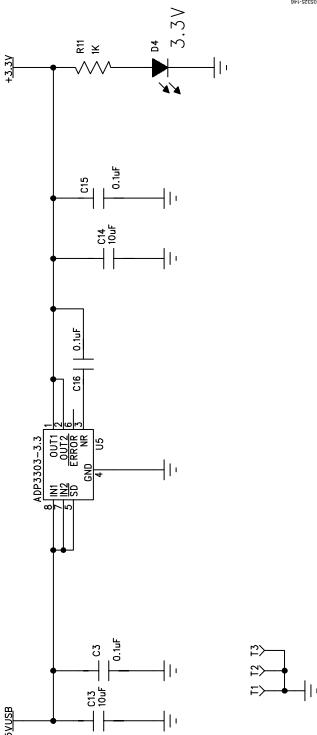

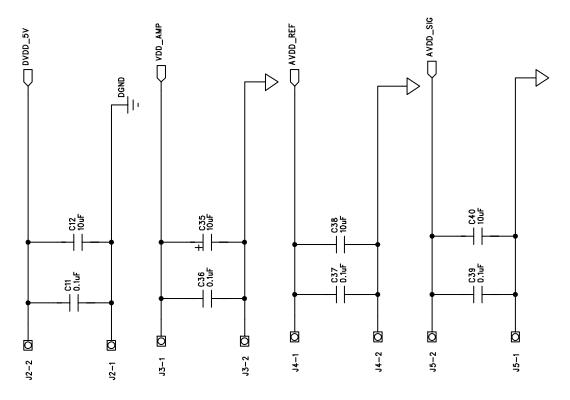

| Evaluation Board                                                                                                                       | . 34 |

| Using the AD5934 Evaluation Board                                                                                                      | . 34 |

| Prototyping Area                                                                                                                       | . 34 |

| Crystal Oscillator (XO) vs. External Clock                                                                                             | . 34 |

| Schematics                                                                                                                             | . 35 |

| Bill Of Materials                                                                                                                      | . 39 |

| Outline Dimensions                                                                                                                     | . 40 |

| Ondoning Cuido                                                                                                                         | 40   |

## **REVISION HISTORY**

| 5/8—Rev. 0 to Rev. A                                          |   |

|---------------------------------------------------------------|---|

| Changes to Layout                                             | l |

| Changes to Features Section, General Description Section, and |   |

| Figure 1                                                      |   |

| Deleted Table 1; Renumbered Sequentially1                     | L |

| Changes to Table 14                                           |   |

| Changes to Table 26                                           | į |

| Changes to Figure 3 and Table 4                               | ; |

| Changes to System Description Section and Figure 1412         | 2 |

| Changes to Figure 16                                          | , |

| Changes to Frequency Sweep Command Sequence Section and       |   |

| Receive Stage Section14                                       | Ŀ |

| Changes to Gain Factor Calculation Section and Impedance      |   |

| Calculation Using Gain Factor Section                         | , |

| Changes to Figure 2016                                        | į |

| Changes to Impedance Error Section17                          | 7 |

| Added Measuring the Phase Across an Impedance Section19       | ) |

| Added Figure 28 and Figure 29: Renumbered Sequentially20      | ) |

| Added Table 6; Renumbered Sequentially                     | . 20 |

|------------------------------------------------------------|------|

| Deleted Table 8                                            | .19  |

| Deleted Table 10 and Table 11                              | .20  |

| Changes to Table 9                                         | .22  |

| Deleted Table 14, Table 16, and Table 17                   | .22  |

| Changes to Status Register (Register Address 0x8F) Section | .24  |

| Added Measuring Small Impedances Section, Figure 37, and   |      |

| Table 16                                                   | .29  |

| Changes to Table 17                                        | .32  |

| Added Evaluation Board Section                             | .34  |

| Added Figure 40                                            | .35  |

| Added Figure 41                                            | .36  |

| Added Figure 42                                            | .37  |

| Added Figure 43                                            | .38  |

| Added Table 18                                             |      |

| Changes to Ordering Guide                                  | .40  |

| <del>-</del>                                               |      |

6/05—Revision 0: Initial Version

## **SPECIFICATIONS**

VDD = 3.3 V, MCLK = 16.776 MHz, 2 V p-p output excitation voltage @ 30 kHz, 200 k $\Omega$  connected between Pin 5 and Pin 6; feedback resistor = 200 k $\Omega$  connected between Pin 4 and Pin 5; PGA gain = ×1, unless otherwise noted.

Table 1.

|                                           | Y Version <sup>1</sup> |       |        |        |                                                                                                   |

|-------------------------------------------|------------------------|-------|--------|--------|---------------------------------------------------------------------------------------------------|

| Parameter                                 | Min                    | Тур   | Max    | Unit   | Test Conditions/Comments                                                                          |

| SYSTEM                                    |                        |       |        |        |                                                                                                   |

| Impedance Range                           | 1 k                    |       | 10 M   | Ω      | $100\Omega$ to $1k\Omega$ requires extra buffer circuitry, see Measuring Small Impedances section |

| Total System Accuracy                     |                        | 0.5   |        | %      | 2 V p-p output excitation voltage at 30 kHz, 200 k $\Omega$ connected between Pin 5 and Pin 6     |

| System Impedance Error Drift              |                        | 30    |        | ppm/°C |                                                                                                   |

| TRANSMIT STAGE                            |                        |       |        |        |                                                                                                   |

| Output Frequency Range <sup>2</sup>       | 1                      |       | 100    | kHz    |                                                                                                   |

| Output Frequency Resolution               |                        | 0.1   |        | Hz     | <0.1 Hz resolution achievable using direct digital synthesis (DDS) techniques                     |

| MCLK Frequency                            |                        |       | 16.776 | MHz    | Maximum system clock frequency                                                                    |

| TRANSMIT OUTPUT VOLTAGE                   |                        |       |        |        |                                                                                                   |

| Range 1                                   |                        |       |        |        |                                                                                                   |

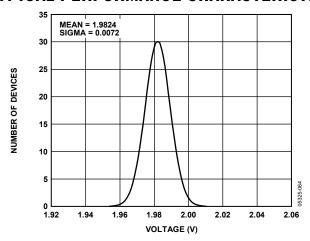

| AC Output Excitation Voltage <sup>3</sup> |                        | 1.98  |        | V p-p  | Refer to Figure 4 for output voltage distribution                                                 |

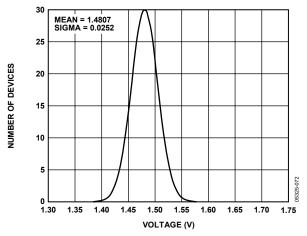

| DC Bias <sup>4</sup>                      |                        | 1.48  |        | V      | DC bias of the ac excitation signal; see Figure 5                                                 |

| DC Output Impedance                       |                        | 200   |        | Ω      | T <sub>A</sub> = 25°C                                                                             |

| Short-Circuit Current to Ground at VOUT   |                        | ±5.8  |        | mA     | T <sub>A</sub> = 25°C                                                                             |

| Range 2                                   |                        |       |        |        |                                                                                                   |

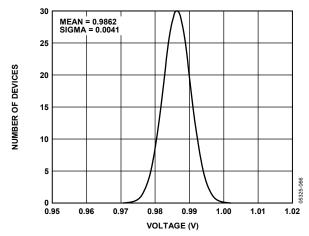

| AC Output Excitation Voltage <sup>3</sup> |                        | 0.97  |        | V p-p  | See Figure 6                                                                                      |

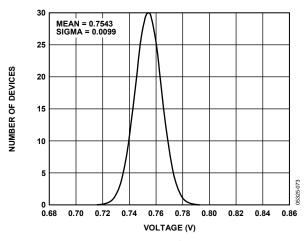

| DC Bias <sup>4</sup>                      |                        | 0.76  |        | V      | DC bias of output excitation signal; see Figure 7                                                 |

| DC Output Impedance                       |                        | 2.4   |        | kΩ     |                                                                                                   |

| Short-Circuit Current to Ground at VOUT   |                        | ±0.25 |        | mA     |                                                                                                   |

| Range 3                                   |                        |       |        |        |                                                                                                   |

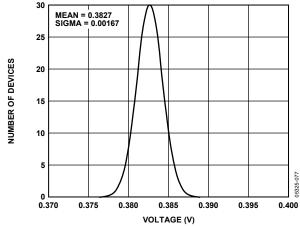

| AC Output Excitation Voltage <sup>3</sup> |                        | 0.383 |        | V p-p  | See Figure 8                                                                                      |

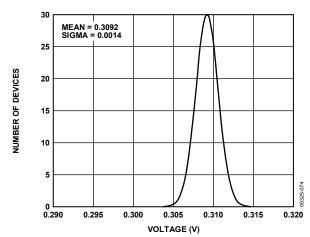

| DC Bias <sup>4</sup>                      |                        | 0.31  |        | V      | DC bias of output excitation signal; see Figure 9                                                 |

| DC Output Impedance                       |                        | 1     |        | kΩ     |                                                                                                   |

| Short-Circuit Current to Ground at VOUT   |                        | ±0.20 |        | mA     |                                                                                                   |

| Range 4                                   |                        |       |        |        |                                                                                                   |

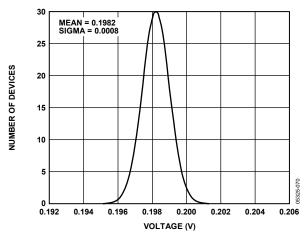

| AC Output Excitation Voltage <sup>3</sup> |                        | 0.198 |        | V p-p  | See Figure 10                                                                                     |

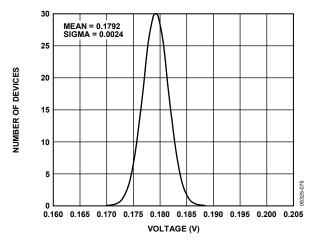

| DC Bias <sup>4</sup>                      |                        | 0.173 |        | V      | DC bias of output excitation signal; see Figure 11                                                |

| DC Output Impedance                       |                        | 600   |        | Ω      |                                                                                                   |

| Short-Circuit Current to Ground at VOUT   |                        | ±0.15 |        | mA     |                                                                                                   |

| SYSTEM AC CHARACTERISTICS                 |                        |       |        |        |                                                                                                   |

| Signal-to-Noise Ratio                     |                        | 60    |        | dB     |                                                                                                   |

| Total Harmonic Distortion                 |                        | -52   |        | dB     |                                                                                                   |

| Spurious-Free Dynamic Range               |                        |       |        |        |                                                                                                   |

| Wide Band (0 MHz to 1 MHz)                |                        | -56   |        | dB     |                                                                                                   |

| Narrow Band (±5 kHz)                      |                        | -85   |        | dB     |                                                                                                   |

|                                       | 1         | Y Version <sup>1</sup> |                  |      |                                                                                                             |  |

|---------------------------------------|-----------|------------------------|------------------|------|-------------------------------------------------------------------------------------------------------------|--|

| Parameter                             | Min       | Тур                    | Max              | Unit | Test Conditions/Comments                                                                                    |  |

| RECEIVE STAGE                         |           |                        |                  |      |                                                                                                             |  |

| Input Leakage Current                 |           | 1                      |                  | nA   | To VIN pin                                                                                                  |  |

| Input Capacitance <sup>5</sup>        |           | 0.01                   |                  | pF   | Pin capacitance between VOUT and GND                                                                        |  |

| Feedback Capacitance, C <sub>FB</sub> |           | 3                      |                  | pF   | Feedback capacitance around current-to-<br>voltage amplifier; appears in parallel with<br>feedback resistor |  |

| ANALOG-TO-DIGITAL CONVERTER⁵          |           |                        |                  |      |                                                                                                             |  |

| Resolution                            |           | 12                     |                  | Bits |                                                                                                             |  |

| Sampling Rate                         |           | 250                    |                  | kSPS | ADC throughput rate                                                                                         |  |

| LOGIC INPUTS                          |           |                        |                  |      |                                                                                                             |  |

| Input High Voltage, V <sub>IH</sub>   | 0.7 × VDD |                        |                  |      |                                                                                                             |  |

| Input Low Voltage, V <sub>IL</sub>    |           |                        | $0.3 \times VDD$ |      |                                                                                                             |  |

| Input Current <sup>6</sup>            |           |                        | 1                | μΑ   | $T_A = 25^{\circ}$                                                                                          |  |

| Input Capacitance                     |           |                        | 7                | pF   | $T_A = 25$ °C                                                                                               |  |

| POWER REQUIREMENTS                    |           |                        |                  |      |                                                                                                             |  |

| VDD                                   | 2.7       |                        | 5.5              | V    |                                                                                                             |  |

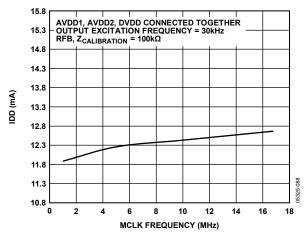

| I <sub>DD</sub> , Normal Mode         |           | 10                     | 15               | mA   | VDD = 3.3 V                                                                                                 |  |

|                                       |           | 17                     | 25               | mA   | VDD = 5.5 V                                                                                                 |  |

| I <sub>DD</sub> , Standby Mode        |           | 7                      |                  | mA   | VDD = 3.3 V; see the Control Register section                                                               |  |

|                                       |           | 9                      |                  | mA   | VDD = 5.5 V                                                                                                 |  |

| I <sub>DD</sub> , Power-Down Mode     |           | 0.7                    | 5                | μΑ   | VDD = 3.3 V                                                                                                 |  |

|                                       |           | 1                      | 8                | μΑ   | VDD = 5.5 V                                                                                                 |  |

$<sup>^{1}</sup>$  Temperature range for Y version =  $-40^{\circ}$ C to  $+125^{\circ}$ C, typical at  $+25^{\circ}$ C.

<sup>&</sup>lt;sup>2</sup> The lower limit of the output excitation frequency can be lowered by scaling the clock supplied to the AD5934.

<sup>3</sup> The peak-to-peak value of the ac output excitation voltage scales with supply voltage according to the following formula. VDD is the supply voltage. Output Excitation Voltage (V p-p) =  $[2/3.3] \times VDD$

<sup>&</sup>lt;sup>4</sup> The dc bias value of the output excitation voltage scales with supply voltage according to the following formula. VDD is the supply voltage. Output Excitation Voltage (V p-p) =  $[2/3.3] \times VDD$

<sup>&</sup>lt;sup>5</sup> Guaranteed by design or characterization, not production tested. Input capacitance at the VOUT pin is equal to pin capacitance divided by open-loop gain of currentto-voltage amplifier.

<sup>&</sup>lt;sup>6</sup> The accumulation of the currents into Pin 8, Pin 15, and Pin 16.

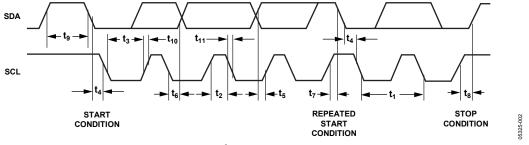

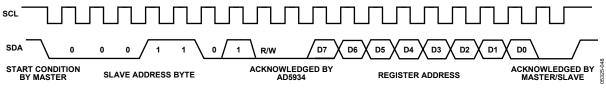

## I<sup>2</sup>C SERIAL INTERFACE TIMING CHARACTERISTICS

VDD = 2.7 V to 5.5 V; all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted (see Figure 2).

Table 2.

| Parameter <sup>1</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Description                                                                |  |

|------------------------|----------------------------------------------|---------|----------------------------------------------------------------------------|--|

| f <sub>SCL</sub>       | 400                                          | kHz max | SCL clock frequency                                                        |  |

| $t_1$                  | 2.5                                          | μs min  | SCL cycle time                                                             |  |

| $t_2$                  | 0.6                                          | μs min  | t <sub>HIGH</sub> , SCL high time                                          |  |

| $t_3$                  | 1.3                                          | μs min  | t <sub>LOW</sub> , SCL low time                                            |  |

| t <sub>4</sub>         | 0.6                                          | μs min  | t <sub>HD, STA</sub> , start/repeated start condition hold time            |  |

| <b>t</b> <sub>5</sub>  | 100                                          | ns min  | t <sub>SU, DAT</sub> , data setup time                                     |  |

| $t_6^2$                | 0.9                                          | μs max  | t <sub>HD, DAT</sub> , data hold time                                      |  |

|                        | 0                                            | μs min  | t <sub>HD, DAT</sub> , data hold time                                      |  |

| <b>t</b> <sub>7</sub>  | 0.6                                          | μs min  | t <sub>SU, STA</sub> , setup time for repeated start                       |  |

| t <sub>8</sub>         | 0.6                                          | μs min  | t <sub>SU, STO</sub> , stop condition setup time                           |  |

| t <sub>9</sub>         | 1.3                                          | μs min  | t <sub>BUF</sub> , bus free time between a stop and a start condition      |  |

| t <sub>10</sub>        | 300                                          | ns max  | t <sub>R</sub> , rise time of SDA when transmitting                        |  |

|                        | 0                                            | ns min  | t <sub>R</sub> , rise time of SCL and SDA when receiving (CMOS compatible) |  |

| t <sub>11</sub>        | 300                                          | ns max  | t <sub>F</sub> , fall time of SCL and SDA when transmitting                |  |

|                        | 0                                            | ns min  | t <sub>F</sub> , fall time of SDA when receiving (CMOS compatible)         |  |

|                        | 250                                          | ns max  | t <sub>F</sub> , fall time of SDA when receiving                           |  |

|                        | $20 + 0.1  C_b^3$                            | ns min  | t <sub>F</sub> , fall time of SCL and SDA when transmitting                |  |

| Сь                     | 400                                          | pF max  | Capacitive load for each bus line                                          |  |

$^3$  C<sub>b</sub> is the total capacitance of one bus line in pF. Note that  $t_R$  and  $t_F$  are measured between 0.3 VDD and 0.7 VDD.

Figure 2. I<sup>2</sup>C Interface Timing Diagram

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not production tested. <sup>2</sup> A master device must provide a hold time of at least 300 ns for the SDA signal (referred to V<sub>IH MIN</sub> of the SCL signal) to bridge the undefined falling edge of SCL.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

#### Table 3.

|                                     | I                     |  |

|-------------------------------------|-----------------------|--|

| Parameter                           | Rating                |  |

| DVDD to GND                         | −0.3 V to +7.0 V      |  |

| AVDD1 to GND                        | −0.3 V to +7.0 V      |  |

| AVDD2 to GND                        | −0.3 V to +7.0 V      |  |

| SDA/SCL to GND                      | -0.3 V to VDD + 0.3 V |  |

| VOUT to GND                         | -0.3 V to VDD + 0.3 V |  |

| VIN to GND                          | −0.3 V to VDD + 0.3 V |  |

| MCLK to GND                         | -0.3 V to VDD + 0.3 V |  |

| Operating Temperatures              |                       |  |

| Extended Industrial Range (Y Grade) | -40°C to +125°C       |  |

| Storage Temperature Range           | −65°C to +160°C       |  |

| Maximum Junction Temperature        | 150°C                 |  |

| SSOP Package, Thermal Impedance     |                       |  |

| $	heta_{JA}$                        | 139°C/W               |  |

| hetaJC                              | 136°C/W               |  |

| Reflow Soldering (Pb-Free)          |                       |  |

| Peak Temperature                    | 260°C                 |  |

| Time at Peak Temperature            | 10 sec to 40 sec      |  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

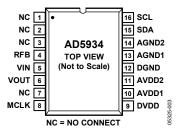

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### NOTES:

- LIT IS RECOMMENDED TO TIE ALL SUPPLY CONNECTIONS (PIN 9, PIN 10, AND PIN 11) AND RUN FROM A SINGLE SUPPLY BETWEEN 2.7V AND 5.5V.

- 2.17 IS ALSO RECOMMENDED TO CONNECT ALL GROUND SIGNALS TOGETHER (PIN 12, PIN 13, AND PIN 14).

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.   | Mnemonic | Description                                                                                                                              |

|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 3, 7 | NC       | No Connect.                                                                                                                              |

| 4         | RFB      | External Feedback Resistor. Connect from Pin 4 to Pin 5. This pin sets the gain of the current-to-voltage amplifier on the receive side. |

| 5         | VIN      | Input to Receive Transimpedance Amplifier. VIN presents a virtual earth voltage of VDD/2.                                                |

| 6         | VOUT     | Excitation Voltage Signal Output.                                                                                                        |

| 8         | MCLK     | The master clock for the system is supplied by the user.                                                                                 |

| 9         | DVDD     | Digital Supply Voltage.                                                                                                                  |

| 10        | AVDD1    | Analog Supply Voltage 1.                                                                                                                 |

| 11        | AVDD2    | Analog Supply Voltage 2.                                                                                                                 |

| 12        | DGND     | Digital Ground.                                                                                                                          |

| 13        | AGND1    | Analog Ground 1.                                                                                                                         |

| 14        | AGND2    | Analog Ground 2.                                                                                                                         |

| 15        | SDA      | I <sup>2</sup> C® Data Input.                                                                                                            |

| 16        | SCL      | I <sup>2</sup> C Clock Input.                                                                                                            |

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 4. Range 1 Output Excitation Voltage Distribution, VDD = 3.3 V

Figure 5. Range 1 DC Bias Distribution, VDD = 3.3 V

Figure 6. Range 2 Output Excitation Voltage Distribution, VDD = 3.3 V

Figure 7. Range 2 DC Bias Distribution, VDD = 3.3 V

Figure 8. Range 3 Output Excitation Voltage Distribution, VDD = 3.3 V

Figure 9. Range 3 DC Bias Distribution, VDD = 3.3 V

Figure 10. Range 4 Output Excitation Voltage Distribution, VDD = 3.3 V

Figure 11. Range 4 DC Bias Distribution, VDD = 3.3 V

Figure 12. Typical Supply Current (IDD) vs. MCLK Frequency

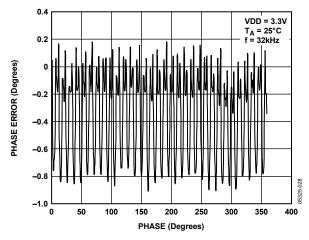

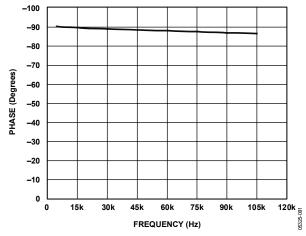

Figure 13. Typical Phase Error

## **TEMINOLOGY**

## **Total System Accuracy**

The AD5934 can accurately measure a range of impedance values to less than 0.5% of the correct impedance value for supply voltages between 2.7 V to 5.5 V.

## Spurious-Free Dynamic Range (SFDR)

Along with the frequency of interest, harmonics of the fundamental frequency and images of these frequencies are present at the output of a DDS device. The spurious-free dynamic range refers to the largest spur or harmonic present in the band of interest. The wideband SFDR gives the magnitude of the largest harmonic or spur relative to the magnitude of the fundamental frequency in the 0 Hz to Nyquist bandwidth. The narrow-band SFDR gives the attenuation of the largest spur or harmonic in a bandwidth of  $\pm 200~\rm kHz$ , about the fundamental frequency.

## Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured output signal to the rms sum of all other spectral components below the Nyquist frequency. The value for SNR is expressed in decibels.

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of harmonics to the fundamental, where V1 is the rms amplitude of the fundamental, and V2, V3, V4, V5, and V6 are the rms amplitudes of the second through the sixth harmonics. THD is defined as

$$THD(dB) = 20 \log \frac{\sqrt{V2^2 + V3^2 + V4^2 + V5^2 + V6^2}}{V1}$$

## SYSTEM DESCRIPTION

Figure 14. Block Overview

The AD5934 is a high precision, impedance converter system solution that combines an on-board frequency generator with a 12-bit, 250 kSPS ADC. The frequency generator allows an external complex impedance to be excited with a known frequency. The response signal from the impedance is sampled by the on-board ADC and DFT processed by an on-board DSP engine. The DFT algorithm returns both a real (R) and imaginary (I) data-word at each frequency point along the sweep. The impedance magnitude and phase is easily calculated using the following equations:

$$Magnitude = \sqrt{R^2 + I^2}$$

$$Phase = tan^{-1}(I/R)$$

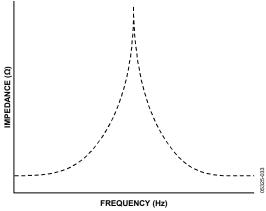

To characterize an impedance profile  $Z(\omega)$ , generally a frequency sweep is required such as that shown in Figure 15.

Figure 15. Impedance vs. Frequency Profile

The AD5934 permits the user to perform a frequency sweep with a user-defined start frequency, frequency resolution, and number of points in the sweep. In addition, the device allows the user to program the peak-to-peak value of the output sinusoidal signal as an excitation to the external unknown impedance connected between the VOUT and VIN pins.

Table 5 gives the four possible output peak-to-peak voltages and the corresponding dc bias levels for each range for 3.3 V. These values are ratiometric with VDD. So for a 5 V supply:

Output Excitation Voltage for Range

$$1 = 1.98 \times \frac{5.0}{3.3} = 3 \text{ V p} - \text{p}$$

Output DC Bias Voltage for Range

$$1 = 1.48 \times \frac{5.0}{3.3} = 2.24 \text{ V p} - \text{p}$$

Table 5. Voltage Levels Respective Bias Levels for 3.3 V

| 1 1 2 1 2 1 1 2 1 2 1 2 1 2 1 2 1 2 1 2       |                                        |                      |  |  |  |  |

|-----------------------------------------------|----------------------------------------|----------------------|--|--|--|--|

| Range Output Excitation No. Voltage Amplitude |                                        | Output DC Bias Level |  |  |  |  |

| 1                                             | 1.98 V p-p                             | 1.48 V               |  |  |  |  |

| 2                                             | 1.98 V p-p<br>0.99 V p-p<br>383 mV p-p | 0.74 V               |  |  |  |  |

| 3                                             | 383 mV p-p                             | 0.31 V               |  |  |  |  |

| 4                                             | 198 mV p-p                             | 0.179 V              |  |  |  |  |

The excitation signal for the transmit stage is provided on-chip using DDS techniques that permit subhertz resolution. The receive stage receives the input signal current from the unknown impedance, performs signal processing, and digitizes the result. The clock for the DDS is generated from an external reference clock that is provided by the user at MCLK.

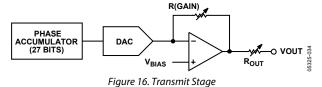

#### TRANSMIT STAGE

As shown in Figure 16, the transmit stage of the AD5934 is made up of a 27-bit phase accumulator DDS core that provides the output excitation signal at a particular frequency. The input to the phase accumulator is taken from the contents of the start frequency register (see Register Address 0x82, Register Address 0x83, and Register Address 0x84). Although the phase accumulator offers 27 bits of resolution, the start frequency register has the three most significant bits (MSBs) set to 0 internally; therefore, the user has the ability to program only the lower 24 bits of the start frequency register.

The AD5934 offers a frequency resolution programmable by the user down to 0.1 Hz. The frequency resolution is programmed via a 24-bit word loaded serially over the  $\rm I^2C$  interface to the frequency increment register.

The frequency sweep is fully described by the programming of three parameters: the start frequency, the frequency increment, and the number of increments.

## **Start Frequency**

This is a 24-bit word that is programmed to the on-board RAM at Register Address 0x82, Register Address 0x83, and Register Address 0x84 (see the Register Map section). The required code loaded to the start frequency register is the result of the formula shown in Equation 1, based on the master clock frequency and the required start frequency output from the DDS.

*Start Frequency Code* =

$$\left(\frac{Required\ Output\ Start\ Frequency}{\frac{MCLK}{16}}\right) \times 2^{27} \tag{1}$$

For example, if the user requires the sweep to begin at 30 kHz and has a 16 MHz clock signal connected to MCLK, the code that needs to be programmed is given by

Start Frequency Code =

$$\left( \frac{30 \text{ kHz}}{\left( \frac{16 \text{ MHz}}{16} \right)} \right) \times 2^{27} = 0 \times 3 \text{D}70 \text{A}3$$

The user programs the value of 0x3D to Register Address 0x82, the value 0x70 to Register Address 0x83, and the value 0xA3 to Register Address 0x84.

#### Frequency Increment

This is a 24-bit word that is programmed to the on-board RAM at Register Address 0x85, Register Address 0x86, and Register Address 0x87 (see the Register Map section). The required code loaded to the frequency increment register is the result of the formula shown in Equation 2, based on the master clock frequency and the required increment frequency output from the DDS.

Frequency Increment Code =

$$\left(\frac{Required\ Frequency\ Increment}{\frac{MCLK}{16}}\right) \times 2^{27}$$

(2)

For example, if the user requires the sweep to have a resolution of 10 Hz and has a 16 MHz clock signal connected to MCLK, the code that needs to be programmed is given by

Frequency Increment Code =

$$\left(\frac{10 \text{ Hz}}{\left(\frac{16 \text{ MHz}}{16}\right)}\right) = 0 \times 00053 \text{E}$$

The user programs the value 0x00 to Register Address 0x85, the value 0x05 to Register Address 0x86, and the value 0x3E to Register Address 0x87.

## **Number of Increments**

This is a 9-bit word that represents the number of frequency points in the sweep. The number is programmed to the on-board RAM at Register Address 0x88 and Register Address 0x89 (see the Register Map section). The maximum number of points that can be programmed is 511.

For example, if the sweep needs 150 points, the user programs the value 0x00 to Register Address 0x88 and the value 0x96 to Register Address 0x89.

Once the three parameter values are programmed, the sweep is initiated by issuing a start frequency sweep command to the control register at Register Address 0x80 and Register Address 0x81 (see the Register Map section). Bit D2 in the status register (Register Address 0x8F) indicates the completion of the frequency measurement for each sweep point. Incrementing to the next frequency sweep point is under the control of the user. The measured result is stored in the two register groups that follow: 0x94, 0x95 (real data) and 0x96, 0x97 (imaginary data) that should be read before issuing an increment frequency command to the control register to move to the next sweep point. There is the facility to repeat the current frequency point measurement by issuing a repeat frequency command to the control register. This has the benefit of allowing the user to average successive readings. When the frequency sweep has completed all frequency points, Bit D3 in the status register is set, indicating the completion of the sweep. Once this bit is set, further increments are disabled.

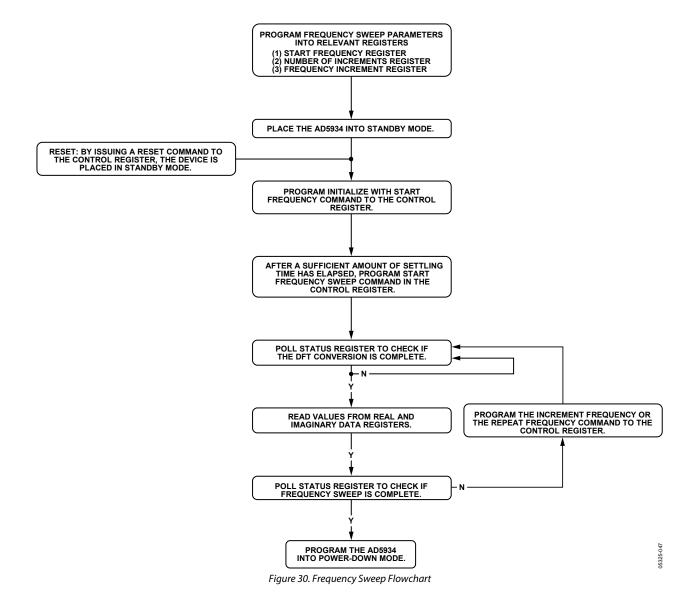

## FREQUENCY SWEEP COMMAND SEQUENCE

The following sequence must be followed to implement a frequency sweep:

- Enter standby mode. Prior to issuing a start frequency sweep command, the device must be placed in standby mode by issuing an enter standby mode command to the control register (Register Address 0x80 and Register Address 0x81). In this mode, the VOUT and VIN pins are connected internally to ground so there is no dc bias across the external impedance or between the impedance and ground.

- Enter initialize mode. In general, high Q complex circuits

require a long time to reach steady state. To facilitate the

measurement of such impedances, this mode allows the user

full control of the settling time requirement before entering

start frequency sweep mode where the impedance

measurement takes place.

- An initialize with start frequency command to the control register enters initialize mode. In this mode, the impedance is excited with the programmed start frequency but no measurement takes place. The user times out the required settling time before issuing a start frequency sweep command to the control register to enter the start frequency sweep mode.

- 3. Enter start frequency sweep mode. The user enters this mode by issuing a start frequency sweep command to the control register. In this mode, the ADC starts measuring after the programmed number of settling time cycles elapses. The user can program an integer number of output frequency cycles (settling time cycles) to Register Address 0x8A and Register Address 0x8B before beginning the measurement at each frequency point (see Figure 30).

The DDS output signal is passed through a programmable gain stage to generate the four ranges of peak-to-peak output excitation signals listed in Table 5. The peak-to-peak output excitation voltage is selected by setting Bit D10 and Bit D9 in the control register (see the Control Register section) and is made available at the VOUT pin.

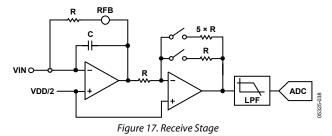

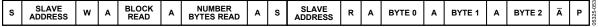

## **RECEIVE STAGE**

The receive stage comprises a current-to-voltage amplifier, followed by a programmable gain amplifier (PGA), antialiasing filter, and ADC. The receive stage schematic is shown in Figure 17. The unknown impedance is connected between the VOUT and VIN pins. The first stage current-to-voltage amplifier configuration means that a voltage present at the VIN pin is a virtual ground with a dc value set at VDD/2. The signal current that is developed across the unknown impedance flows into the VIN pin and develops a voltage signal at the output of the current-to-voltage converter. The gain of the current-to voltage amplifier is determined by a user-selectable feedback resistor connected between Pin 4 (RFB) and Pin 5 (VIN). It is important for the user to choose a feedback resistance value which, in conjunction with the selected gain of the PGA stage, maintains the signal within the linear range of the ADC (0 V to VDD).

The PGA allows the user to gain the output of the current-to-voltage amplifier by a factor of 5 or 1 depending upon the status of Bit D8 in the control register (see the Register Map section Register Address 0x80). The signal is then low-pass filtered and presented to the input of the 12-bit, 250 kSPS ADC.

The digital data from the ADC is passed directly to the DSP core of the AD5934 that performs a DFT on the sampled data.

## **DFT OPERATION**

A DFT is calculated for each frequency point in the sweep. The AD5934 DFT algorithm is represented by

$$X(f) = \sum_{n=0}^{1023} (x(n)(\cos(n) - j\sin(n)))$$

where:

X(f) is the power in the signal at the Frequency Point f. x(n) is the ADC output.

cos(n) and sin(n) are the sampled test vectors provided by the DDS core at the Frequency f.

The multiplication is accumulated over 1024 samples for each frequency point. The result is stored in two 16-bit registers representing the real and imaginary components of the result. The data is stored in two complement format.

## IMPEDANCE CALCULATION

## **MAGNITUDE CALCULATION**

The first step in the impedance calculation for each frequency point is to calculate the magnitude of the DFT at that point.

The DFT magnitude is given by

$$Magnitude = \sqrt{R^2 + I^2}$$

where:

*R* is the real number stored at Register Address 0x94 and Register Address 0x95.

*I* is the imaginary number stored at Register Address 0x96 and Register Address 0x97.

For example, assume the results in the real data and imaginary data registers are as follows at a frequency point:

Real Data Register = 0x038B = 907 decimal

Imaginary Data Register = 0x0204 = 516 decimal

$$Magnitude = \sqrt{(907^2 + 516^2)} = 1043.506$$

To convert this number into impedance, it must be multiplied by a scaling factor called the gain factor. The gain factor is calculated during the calibration of the system with a known impedance connected between the VOUT and VIN pins.

Once the gain factor is calculated, it can be used in the calculation of any unknown impedance between the VOUT and VIN pins.

## **GAIN FACTOR CALCULATION**

An example of a gain factor calculation follows, with these assumptions:

Output excitation voltage = 2 V p-p

Calibration impedance value,  $Z_{CALIBRATION} = 200 \text{ k}\Omega$

PGA gain =  $\times 1$

Current-to-voltage amplifier gain resistor = 200  $k\Omega$

Calibration frequency = 30 kHz

The typical contents of the real data and imaginary data registers after a frequency point conversion would then be

Real Data Register = 0xF064 = -3996 decimal

Imaginary Data Register = 0x227E = +8830 decimal

$$Magnitude = \sqrt{(-3996)^2 + (8830)^2} = 9692.106$$

Gain Factor =

$$\left(\frac{Admittance}{Code}\right) = \frac{\left(\frac{1}{Impedance}\right)}{Magnitude}$$

Gain Factor =

$$\left(\frac{1}{200 \text{ k}\Omega}\right)$$

= 515.819×10<sup>-12</sup>

## IMPEDANCE CALCULATION USING GAIN FACTOR

The next example illustrates how the calculated gain factor derived previously is used to measure an unknown impedance. For this example, assume that the unknown impedance is 510 k $\Omega$ .

After measuring the unknown impedance at a frequency of 30 kHz, assume that the real data and imaginary data registers contain the following data:

Real Data Register = 0xFA3F = -1473 decimal

$Imaginary\ Data\ Register = 0x0DB3 = +3507\ decimal$

Magnitude =

$$\sqrt{((-1473)^2 + (3507)^2)}$$

= 3802.863

The measured impedance at the frequency point is then given by

$$Impedance = \frac{1}{Gain\ Factor \times Magnitude}$$

$$= \frac{1}{515.819273 \times 10^{-12} \times 3802.863} \Omega = 509.791 \text{ k}\Omega$$

## **GAIN FACTOR VARIATION WITH FREQUENCY**

Because the AD5934 has a finite frequency response, the gain factor also shows a variation with frequency. This variation in gain factor results in an error in the impedance calculation over a frequency range. Figure 18 shows an impedance profile based on a single-point gain factor calculation. To minimize this error, the frequency sweep should be limited to as small a frequency range as possible.

Figure 18. Impedance Profile Using a Single-Point Gain Factor Calculation

#### 2-POINT CALIBRATION

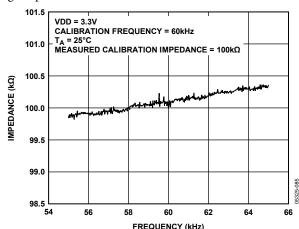

Alternatively, it is possible to minimize this error by assuming that the frequency variation is linear and adjusting the gain factor with a 2-point calibration. Figure 19 shows an impedance profile based on a 2-point gain factor calculation.

Figure 19. Impedance Profile Using a 2-Point Gain Factor Calculation

## 2-POINT GAIN FACTOR CALCULATION

This is an example of a 2-point gain factor calculation assuming the following:

Output excitation voltage = 2 V p-p Calibration impedance value,  $Z_{UNKNOWN}$  = 100.0 k $\Omega$  PGA gain = ×1 Supply voltage = 3.3 V Current-to-voltage amplifier gain resistor = 100 k $\Omega$  Calibration frequencies = 55 kHz and 65 kHz

Typical values of the gain factor calculated at the two calibration frequencies read

Gain factor calculated at 55 kHz is  $1.031224 \times 10^{-9}$ . Gain factor calculated at 65 kHz is  $1.035682 \times 10^{-9}$ . Difference in gain factor ( $\Delta$ GF) is  $1.035682 \times 10^{-9} - 1.031224 \times 10^{-9} = 4.458000 \times 10^{-12}$ . Frequency span of sweep ( $\Delta$ F) is 10 kHz.

Therefore, the gain factor required at 60 kHz is given by

$$\left(\frac{4.458000E-12}{10 \text{ kHz}} \times 5 \text{ kHz}\right) + 1.031224 \times 10^{-9}$$

The required gain factor is  $1.033453 \times 10^{-9}$ .

The impedance is calculated as previously described in the Impedance Calculation section.

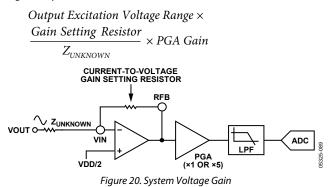

## **GAIN FACTOR SETUP CONFIGURATION**

When calculating the gain factor, it is important that the receive stage is operating in its linear region. This requires careful selection of the excitation signal range, current-to-voltage gain resistor and PGA gain. The gain through the system shown in Figure 20 is given by

For this example, assume the following system settings:

$VDD = 3.3 \ V$ Gain setting resistor = 200 kΩ  $Z_{UNKNOWN} = 200 \ k\Omega$ PGA setting = ×1

The peak-to-peak voltage presented to the ADC input is 2 V p-p. However, had the user chosen a PGA gain of  $\times$ 5, the voltage would saturate the ADC.

#### **GAIN FACTOR RECALCULATION**

The gain factor must be recalculated for a change in any of the following parameters:

- Current-to-voltage gain setting resistor

- Output excitation voltage

- PGA gain

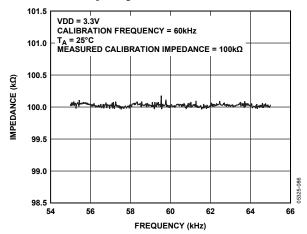

#### **GAIN FACTOR TEMPERATURE VARIATION**

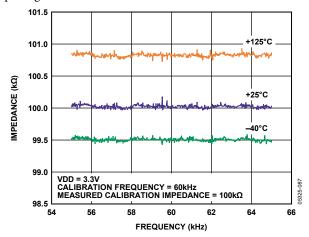

The typical impedance error variation with temperature is in the order of 30 ppm/°C. Figure 21 shows an impedance profile with a variation in temperature for 100 k $\Omega$  impedance using a 2-point gain factor calibration.

Figure 21. Impedance Profile Variation with Temperature Using a 2-Point Gain Factor Calibration

#### **IMPEDANCE ERROR**

Minimizing the impedance range under test optimizes the AD5934 measurement performance. Following are the examples of the AD5934 performance when operating in the six different impedance ranges. The gain factor is calculated with a precision resistor in each case. Note that  $R_{\rm OUT}$  was measured to be 200  $\Omega$  for 2 V p-p.  $R_{\rm OUT}$  was calibrated out in the gain factor calculations. In Figure 22 to Figure 26, the 10 kHz excitation frequency was generated using a 4 MHz clock.

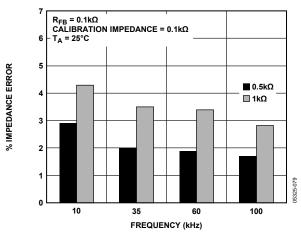

## Impedance Range 1 (0.1 $k\Omega$ to 1 $k\Omega$ )

The following conditions were used to conduct the tests shown in Figure 22:

Output excitation voltage = 2 V p-p Calibration impedance value,  $Z_{CALIBRATION}$  = 100  $\Omega$  PGA gain =  $\times 1$  Supply voltage = 3.3 V Current-to-voltage amplifier gain resistor = 100  $\Omega$

Figure 22. Impedance Range 1 Typical % Impedance Error over Frequency

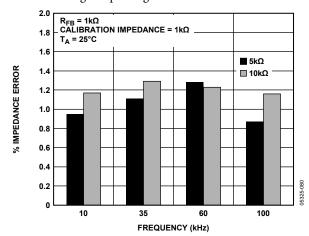

## Impedance Range 2 (1 $k\Omega$ to 10 $k\Omega$ )

The following conditions were used to conduct the tests shown in Figure 23:

Output excitation voltage = 2 V p-p Calibration impedance value,  $Z_{\text{CALIBRATION}} = 1 \text{ k}\Omega$  PGA gain =  $\times 1$  Supply voltage = 3.3 V Current-to-voltage amplifier gain resistor =  $1 \text{ k}\Omega$

Figure 23. Impedance Range 2 Typical % Impedance Error over Frequency

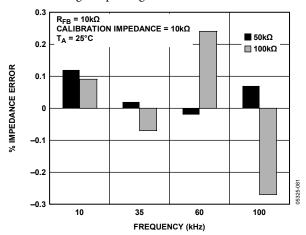

## Impedance Range 3 (10 k $\Omega$ to 100 k $\Omega$ )

The following conditions were used to conduct the tests shown in Figure 24:

Output excitation voltage = 2 V p-p

Calibration impedance value,  $Z_{CALIBRATION} = 10 \text{ k}\Omega$

$PGA gain = \times 1$

Supply voltage = 3.3 V

Current-to-voltage amplifier gain resistor =  $10 \text{ k}\Omega$

Figure 24. Impedance Range 3 Typical % Impedance Error over Frequency

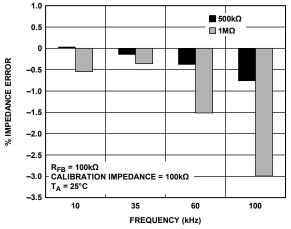

## Impedance Range 4 (100 k $\Omega$ to 1 M $\Omega$ )

The following conditions were used to conduct the tests shown in Figure 25:

Output excitation voltage = 2 V p-p

Calibration impedance value,  $Z_{\text{CALIBRATION}} = 100 \text{ k}\Omega$

PGA gain =  $\times 1$

Supply voltage = 3.3 V

Current-to-voltage amplifier gain resistor = 100 k $\Omega$

Figure 25. Impedance Range 4 Typical % Impedance Error over Frequency

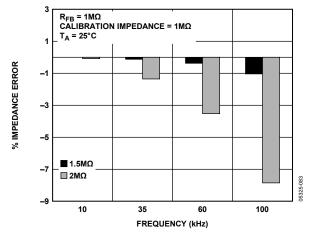

#### Impedance Range 5 (1 M $\Omega$ to 2 M $\Omega$ )

The following conditions were used to conduct the tests shown in Figure 26:

Output excitation voltage = 2 V p-p

Calibration impedance value,  $Z_{CALIBRATION} = 100 \text{ k}\Omega$

$PGA gain = \times 1$

Supply voltage = 3.3 V

Current-to-voltage amplifier gain resistor =  $100 \text{ k}\Omega$

Figure 26. Impedance Range 5 Typical % Impedance Error over Frequency

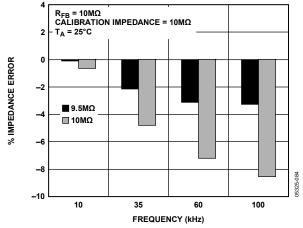

## Impedance Range 6 (9 M $\Omega$ to 10 M $\Omega$ )

The following conditions were used to conduct the tests shown in Figure 27:

Output excitation voltage = 2 V p-p

Calibration impedance value,  $Z_{CALIBRATION} = 9 M\Omega$

$PGA gain = \times 1$

Supply voltage = 3.3 V

Current-to-voltage amplifier gain resistor = 9 M $\Omega$

Figure 27. Impedance Range 6 Typical % Impedance Error over Frequency

#### **MEASURING THE PHASE ACROSS AN IMPEDANCE**

The AD5934 returns a complex output code made up of a separate real and imaginary components. The real component is stored at Register Address 0x94 and Register Address 0x95, and the imaginary component is stored at Register Address 0x96 and Register Address 0x97 after each sweep measurement. These correspond to the real and imaginary components of the DFT and not the resistive and reactive components of the impedance under test.

For example, it is a common misconception to assume that if a user was analyzing a series RC circuit that the real value stored in Register Address 0x94 and Register Address 0x95 and the imaginary value stored in Register Address 0x96 and Register Address 0x97 would correspond to the resistance and capacitive reactance, respectfully. However, this is incorrect because the magnitude of the impedance (|Z|) can be calculated by calculating the magnitude of the real and imaginary components of the DFT given by the following formula:

$$Magnitude = \sqrt{R^2 + I^2}$$

After each measurement, multiply it by the calibration term and invert the product. Therefore, the magnitude of the impedance is given by the following formula:

$$Impedance = \frac{1}{Gain \ Factor \times Magnitude}$$

Where the gain factor is given by

$$Gain\ Factor = \left(\frac{Admittance}{Code}\right) = \frac{\left(\frac{1}{Impedance}\right)}{Magnitude}$$

The user must calibrate the AD5934 system for a known impedance range to determine the gain factor before any valid measurement can take place. Therefore, the user must know the impedance limits of the complex impedance ( $Z_{\text{UNKNOWN}}$ ) for the sweep frequency range of interest. The gain factor is simply determined by placing a known impedance between the input/output of the AD5934 and measuring the resulting magnitude of the code. The AD5934 system gain settings need to be chosen to place the excitation signal in the linear region of the on-board ADC.

Because the AD5934 returns a complex output code made up of real and imaginary components, the user is also able to calculate the phase of the response signal through the signal path of the AD5934. The phase is given by the following formula:

$$Phase (rads) = tan^{-1}(I/R)$$

(3)

The phase measured by Equation 3 accounts for the phase shift introduced to the DDS output signal as it passes through the internal amplifiers on the transmit and receive side of the AD5934, along with the low-pass filter, and also the impedance connected between the VOUT and VIN pins of the AD5934.

The parameters of interest for many users are the magnitude of the impedance ( $|Z_{UNKNOWN}|$ ) and the impedance phase ( $Z\emptyset$ ). The measurement of the impedance phase ( $Z\emptyset$ ) is a 2-step process.

The first step involves calculating the AD5934 system phase. The AD5934 system phase can be calculated by placing a resistor across the VOUT and VIN pins of the AD5934 and calculating the phase (using Equation 3) after each measurement point in the sweep. By placing a resistor across the VOUT and VIN pins, there is no additional phase lead or lag introduced to the AD5934 signal path, and the resulting phase is due entirely to the internal poles of the AD5934, that is, the system phase.

Once the system phase is calibrated using a resistor, the second step involves calculating the phase of any unknown impedance can be calculated by inserting the unknown impedance between the VIN and VOUT terminals of the AD5934 and recalculating the new phase (including the phase due to the impedance) using the same formula. The phase of the unknown impedance ( $Z\emptyset$ ) is given by

$$Z\emptyset = (\Phi unknown - \nabla system)$$

where

*∇system* is the phase of the system with a calibration resistor connected between VIN and VOUT.

Φ*unknown* is the phase of the system with the unknown impedance connected between VIN and VOUT. ZØ is the phase due to the impedance, that is, the impedance phase.

Note that it is possible to calculate the gain factor and to calibrate the system phase using the same real and imaginary component values when a resistor is connected between the VOUT and VIN pins of the AD5934, for example, measuring the impedance phase  $(Z\emptyset)$  of a capacitor.

The excitation signal current leads the excitation signal voltage across a capacitor by -90 degrees. Therefore, an approximate -90 degrees phase difference between the system phase responses measured with a resistor and the system phase responses measured with a capacitive impedance exists.

As previously outlined, if the user wants to determine the phase angle of the capacitive impedance ( $Z\emptyset$ ), the user first must determine the system phase response ( $\nabla$ system) and subtract this from the phase calculated with the capacitor connected between VOUT and VIN ( $\Phi$ unknown).

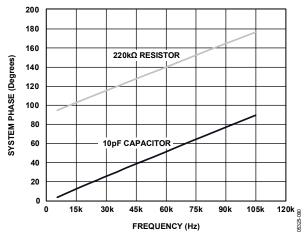

Figure 28 shows the AD5934 system phase response calculated using a 220 k $\Omega$  calibration resistor (R<sub>FB</sub> = 220 k $\Omega$ , PGA = ×1) and the repeated phase measurement with a 10 pF capacitive impedance.

One important point to note about the phase formula used to plot Figure 28 is that it uses the arctangent function that returns a phase angle in radians and, therefore, it is necessary to convert from radians to degrees.

Figure 28. System Phase Response vs. Capacitive Phase

The phase difference (that is,  $Z\emptyset$ ) between the phase response of a capacitor and the system phase response using a resistor is the impedance phase of the capacitor ( $Z\emptyset$ ) and is shown in Figure 29.

Figure 29. Phase Response of a Capacitor

In addition, when using the real and imaginary values to interpret the phase at each measurement point, care should be taken when using the arctangent formula. The arctangent function only returns the correct standard phase angle when the sign of the real and imaginary values are positive, that is, when the coordinates lie in the first quadrant. The standard angle is taken counterclockwise from the positive real x-axis. If the sign of the real component is positive and the sign of the imaginary

component is negative, that is, the data lies in the second quadrant, the arctangent formula returns a negative angle, and it is necessary to add an additional 180° to calculate the correct standard angle. Likewise, when the real and imaginary components are both negative, that is, when data lies in the third quadrant, the arctangent formula returns a positive angle, and it is necessary to add an additional 180° to calculate the correct standard phase. When the real component is positive and the imaginary component is negative, that is, the data lies in the fourth quadrant, the arctangent formula returns a negative angle, and it is necessary to add an additional 360° to calculate the correct standard phase.

Therefore, the correct standard phase angle is dependent upon the sign of the real and imaginary components, which is summarized in Table 6.

Table 6. Phase Angle

| Real     | Imaginary | Quadrant | Phase Angle                                                                |

|----------|-----------|----------|----------------------------------------------------------------------------|

| Positive | Positive  | First    | $\tan^{-1}(I/R) \times \frac{180^{\circ}}{\pi}$                            |

| Positive | Negative  | Second   | $180^{\circ} + \left(\tan^{-1}(I/R) \times \frac{180^{\circ}}{\pi}\right)$ |

| Negative | Negative  | Third    | $180^{\circ} + \left(\tan^{-1}(I/R) \times \frac{180^{\circ}}{\pi}\right)$ |

| Positive | Negative  | Fourth   | $360^{\circ} + \left(\tan^{-1}(I/R) \times \frac{180^{\circ}}{\pi}\right)$ |

Once the magnitude of the impedance (|Z|) and the impedance phase angle ( $Z\emptyset$ , in radians) are correctly calculated, it is possible to determine the magnitude of the real (resistive) and imaginary (reactive) components of the impedance ( $Z_{\text{UNKNOWN}}$ ) by the vector projection of the impedance magnitude onto the real and imaginary impedance axis using the following formulas:

The real component is given by

$$|Z_{REAL}| = |Z| \times \cos(Z\emptyset)$$

The imaginary component is given by

$$|Z_{IMAG}| = |Z| \times \sin(Z\emptyset)$$

## PERFORMING A FREQUENCY SWEEP

## **REGISTER MAP**

Table 7.

| Register Name                  | Register Address | Bits       | Function   |

|--------------------------------|------------------|------------|------------|

| Control                        | 0x80             | D15 to D8  | Read/write |

|                                | 0x81             | D7 to D0   | Read/write |

| Start Frequency                | 0x82             | D23 to D16 | Read/write |

|                                | 0x83             | D15 to D8  | Read/write |

|                                | 0x84             | D7 to D0   | Read/write |

| Frequency Increment            | 0x85             | D23 to D16 | Read/write |

|                                | 0x86             | D15 to D8  | Read/write |

|                                | 0x87             | D7 to D0   | Read/write |

| Number of Increments           | 0x88             | D15 to D8  | Read/write |

|                                | 0x89             | D7 to D0   | Read/write |

| Number of Settling Time Cycles | 0x8A             | D15 to D8  | Read/write |

|                                | 0x8B             | D7 to D0   | Read/write |

| Status                         | 0x8F             | D7 to D0   | Read only  |

| Real Data                      | 0x94             | D15 to D8  | Read only  |

|                                | 0x95             | D7 to D0   | Read only  |

| Imaginary Data                 | 0x96             | D15 to D8  | Read only  |

|                                | 0x97             | D7 to D0   | Read only  |

## CONTROL REGISTER (REGISTER ADDRESS 0x80, REGISTER ADDRESS 0x81)

The AD5934 contains a 16-bit control register (Register Address 0x80 and Register Address 0x81) that sets the control modes. The default value of the control register upon reset is as follows: D15 to D0 is reset to 0xA000 upon power-up.

The four MSBs of the control register are decoded to provide control functions, such as performing a frequency sweep, powering down the part, and controlling various other functions defined in the control register map.

The user can choose to write only to Register Address 0x80 and to not alter the contents of Register Address 0x81. Note that the control register should not be written to as part of a block write command. The control register also allows the user to program the excitation voltage and set the system clock. A reset command to the control register does not reset any programmed values associated with the sweep (that is, start frequency, number of increments, frequency increment). After a reset command, an initialize with start frequency command must be issued to the control register to restart the frequency sweep sequence (see Figure 30).

Table 8. D10 to D9 Control Register Map

| D10 | D9 | Range No. | Output Voltage Range |

|-----|----|-----------|----------------------|

| 0   | 0  | 1         | 2.0 V p-p typical    |

| 0   | 1  | 3         | 200 mV p-p typical   |

| 1   | 0  | 4         | 400 mV p-p typical   |

| 1   | 1  | 2         | 1.0 V p-p typical    |

Table 9. D11 and D8 to D0 Control Register Map

| Bits | Description                               |  |  |  |  |  |

|------|-------------------------------------------|--|--|--|--|--|

| D11  | No operation                              |  |  |  |  |  |

| D8   | PGA gain; $0 = \times 5$ , $1 = \times 1$ |  |  |  |  |  |

| D7   | Reserved; set to 0                        |  |  |  |  |  |

| D6   | Reserved; set to 0                        |  |  |  |  |  |

| D5   | Reserved; set to 0                        |  |  |  |  |  |

| D4   | Reset                                     |  |  |  |  |  |

| D3   | External system clock; set to 1           |  |  |  |  |  |

|      | Internal system clock; set to 0           |  |  |  |  |  |

| D2   | Reserved; set to 0                        |  |  |  |  |  |

| D1   | Reserved; set to 0                        |  |  |  |  |  |

| D0   | Reserved; set to 0                        |  |  |  |  |  |

|      |                                           |  |  |  |  |  |

Table 10. D15 to D12 Control Register Map

| Table 10. D13 to D12 Control Register Map |     |     |     |                                 |  |  |  |  |

|-------------------------------------------|-----|-----|-----|---------------------------------|--|--|--|--|

| D15                                       | D14 | D13 | D12 | Description                     |  |  |  |  |

| 0                                         | 0   | 0   | 0   | No operation                    |  |  |  |  |

| 0                                         | 0   | 0   | 1   | Initialize with start frequency |  |  |  |  |

| 0                                         | 0   | 1   | 0   | Start frequency sweep           |  |  |  |  |

| 0                                         | 0   | 1   | 1   | Increment frequency             |  |  |  |  |

| 0                                         | 1   | 0   | 0   | Repeat frequency                |  |  |  |  |

| 1                                         | 0   | 0   | 0   | No operation                    |  |  |  |  |

| 1                                         | 0   | 0   | 1   | No operation                    |  |  |  |  |

| 1                                         | 0   | 1   | 0   | Power-down mode                 |  |  |  |  |

| 1                                         | 0   | 1   | 1   | Standby mode                    |  |  |  |  |

| 1                                         | 1   | 0   | 0   | No operation                    |  |  |  |  |

| 1                                         | 1   | 0   | 1   | No operation                    |  |  |  |  |

## **Control Register Decode**

## **Initialize with Start Frequency**

This command enables the DDS to output the programmed start frequency for an indefinite time. Initially, it is used to excite the unknown impedance. When the output unknown impedance has settled after a time determined by the user, the user must initiate a start frequency sweep command to begin the frequency sweep.

## **Start Frequency Sweep**

In this mode, the ADC starts measuring after the programmed number of settling time cycles has elapsed. The user has the ability to program an integer number of output frequency cycles (settling time cycles) to Register Address 0x8A and Register Address 0x8B before the commencement of the measurement at each frequency point (see Figure 30).

## **Increment Frequency**

The increment frequency command is used to step to the next frequency point in the sweep. This usually happens after data from the previous step is transferred and verified by the DSP. When the AD5934 receives this command, it waits for the programmed number of settling time cycles before beginning the ADC conversion process.

## Repeat Frequency

There is the facility to repeat the current frequency point measurement by issuing a repeat frequency command to the control register. This command allows users to average successive readings.

#### Power-Down Mode

The default state at power-up of the AD5934 is power-down mode. The control register contains the code 1010,0000,0000,0000 (0xA000). In this mode, both the output and input pins, VOUT and VIN, are connected internally to GND.

## **Standby Mode**

This mode powers up the part for general operation. In standby mode, the VIN and VOUT pins are internally connected to GND.

#### Reset

A reset command allows the user to interrupt a sweep. The start frequency, number of increments, and frequency increment register contents are not overwritten. An initialize with start frequency command is required to restart the frequency sweep command sequence.

#### **Output Voltage Range**

The output voltage range allows the user to program the excitation voltage range at VOUT.

#### **PGA Gain**

The PGA gain allows the user to amplify the response signal into the ADC by a multiplication factor of  $\times 5$  or  $\times 1$ .

# START FREQUENCY REGISTER (REGISTER ADDRESS 0x82, REGISTER ADDRESS 0x83, REGISTER ADDRESS 0x84)

The start frequency register contains the 24-bit digital representation of the frequency from where the subsequent frequency sweep is initiated. For example, if the user requires the sweep to start from a frequency of 30 kHz using a 16.0 MHz clock, the user must program the value 0x3D to Register Address 0x82, the value 0x70 to Register Address 0x83, and the value 0xA3 to Register Address 0x84. Doing this ensures the output frequency starts at 30 kHz.

The start frequency code is

Start Frequency Code =

$$\left(\frac{30 \text{ kHz}}{\left(\frac{16 \text{ MHz}}{16}\right)}\right) \times 2^{27} \equiv 0 \times 3 \text{ D} 70 \text{A} 3$$

The default value of the start frequency register upon reset is as follows: D23 to D0 are not reset at power-up. After the reset command, the contents of this register are not reset.

# FREQUENCY INCREMENT REGISTER (REGISTER ADDRESS 0x85, REGISTER ADDRESS 0x86, REGISTER ADDRESS 0x87)

The frequency increment register contains a 24-bit representation of the frequency increment between consecutive frequency points along the sweep. For example, if the user requires an increment step of 30 Hz using a 16.0 MHz clock, the user must program the value 0x00 to Register Address 0x85, the value 0x0F to Register Address 0x86, and the value 0xBA to Register Address 0x87.

The formula for calculating the frequency increment is given by

Frequency Increment Code =

$$\left(\frac{10 \text{ Hz}}{\left(\frac{16 \text{ MHz}}{16}\right)}\right) \times 2^{27} \equiv 0 \times 00053 \text{E}$$

The user programs the value 0x00 to Register Address 0x85, the value 0x05 to Register Address 0x86, and the value 0x3E to Register Address 0x87.

The default value of the frequency increment register upon reset is as follows: D23 to D0 are not reset at power-up. After the reset command, the contents of this register are not reset.

## NUMBER OF INCREMENTS REGISTER (REGISTER ADDRESS 0x88, REGISTER ADDRESS 0x89)

The default value of the number of increments register upon reset is as follows: D8 to D0 are not reset at power-up. After a reset command, the contents of this register are not reset.

Table 11. Number of Increments Register

| Reg Addr | Bits      | Description          | Function         | Format                                             |

|----------|-----------|----------------------|------------------|----------------------------------------------------|

| 0x88     | D15 to D9 | Don't care           | Read or write    | Integer<br>number                                  |

|          | D8        | Number of increments | Read or<br>write | stored<br>in binary<br>format                      |

| 0x89     | D7 to D0  | Number of increments | Read or<br>write | Integer<br>number<br>stored<br>in binary<br>format |

This register determines the number of frequency points in the frequency sweep. The number of frequency points is represented by a 9-bit word, D8 to D0. D15 to D9 are don't care bits. This register in conjunction with the start frequency register and the frequency increment register determine the frequency sweep range for the sweep operation. The maximum number of increments that can be programmed is 511.

# NUMBER OF SETTLING TIME CYCLES REGISTER (REGISTER ADDRESS 0x8A, REGISTER ADDRESS 0x8B)

The default value of the number of settling time cycles register upon reset is as follows: D10 to D0 are not reset at power-up. After a reset command, the contents of this register are not reset.