July 1995

#### DP8390D/NS32490D NIC Network Interface Controller

#### **General Description**

The DP8390D/NS32490D Network Interface Controller (NIC) is a microCMOS VLSI device designed to ease interfacing with CSMA/CD type local area networks including Ethernet, Thin Ethernet (Cheapernet) and StarLAN. The NIC implements all Media Access Control (MAC) layer functions for transmission and reception of packets in accordance with the IEEE 802.3 Standard. Unique dual DMA channels and an internal FIFO provide a simple yet efficient packet management design. To minimize system parts count and cost, all bus arbitration and memory support logic are integrated into the NIC.

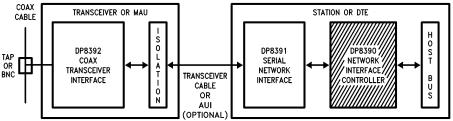

The NIC is the heart of a three chip set that implements the complete IEEE 802.3 protocol and node electronics as shown below. The others include the DP8391 Serial Network Interface (SNI) and the DP8392 Coaxial Transceiver Interface (CTI).

#### **Features**

- Compatible with IEEE 802.3/Ethernet II/Thin Ethernet/ StarLAN

- Interfaces with 8-, 16- and 32-bit microprocessor systems

- Implements simple, versatile buffer management

- Requires single 5V supply

- Utilizes low power microCMOS process

- Includes

- Two 16-bit DMA channels

- 16-byte internal FIFO with programmable threshold

- Network statistics storage

- Supports physical, multicast, and broadcast address filtering

- Provides 3 levels of loopback

- Utilizes independent system and network clocks

#### **Table of Contents**

- 1.0 SYSTEM DIAGRAM

- 2.0 BLOCK DIAGRAM

- 3.0 FUNCTIONAL DESCRIPTION

- 4.0 TRANSMIT/RECEIVE PACKET ENCAPSULATION/ DECAPSULATION

- **5.0 PIN DESCRIPTIONS**

- 6.0 DIRECT MEMORY ACCESS CONTROL (DMA)

- 7.0 PACKET RECEPTION

- 8.0 PACKET TRANSMISSION

- 9.0 REMOTE DMA

- **10.0 INTERNAL REGISTERS**

- 11.0 INITIALIZATION PROCEDURES

- 12.0 LOOPBACK DIAGNOSTICS

- 13.0 BUS ARBITRATION AND TIMING

- 14.0 PRELIMINARY ELECTRICAL CHARACTERISTICS

- 15.0 SWITCHING CHARACTERISTICS

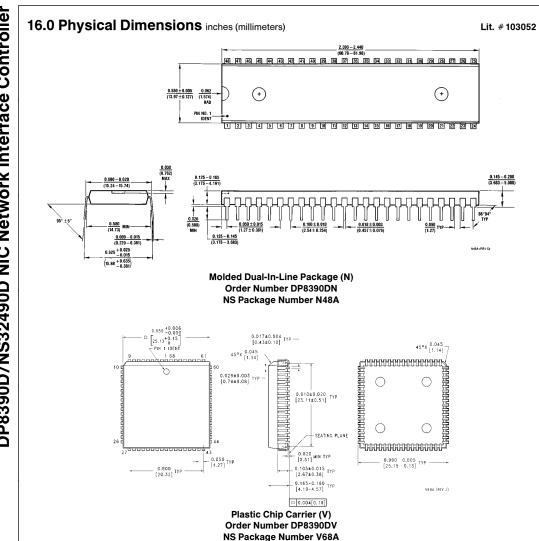

- 16.0 PHYSICAL DIMENSIONS

#### 1.0 System Diagram

#### IEEE 802.3 Compatible Ethernet/Thin Ethernet Local Area Network Chip Set

TL/F/8582-1

RI-STATE® is a registered trademark of National Semiconductor Corporation

1995 National Semiconductor Corporation TL/F/85

RRD-B30M105/Printed in U. S. A.

#### 2.0 Block Diagram COLLISION CRS RECOVERY. BUS ARBITRATION/ IFG TIMING BREQ, BACK **BSCK** HANDSHAKE HANDSHAKE DMA ADDRESS PROTOCOL BUFFER REGISTERS AND COUNTERS ADDRESS COMMAND CONTROL REGISTER ARRAY (PHYS & MULTI) REGISTER ARRAY ₹8 8 HANDSHAKE 16 INTERNAL BUS ADDRESS ੈ 8 OR 16 RECOGNITION RECEIVE BYTE COUNT/ALIGNMENT LOGIC 16 BYTE RECEIVE/ RXC RECEIVE TRANSMÍT MULTIPLEXED ADDRESS/DATA BUS DESERIALIZER LOGIC RXD TRANSMIT SERIALIZER FIFO TXO PREAMBLE / SYNCH LOGIC JAM PATTERN GEN LOGIC CRC GENERATOR CHECKER TL/F/8582-2

FIGURE 1

#### 3.0 Functional Description

(Refer to Figure 1)

#### **RECEIVE DESERIALIZER**

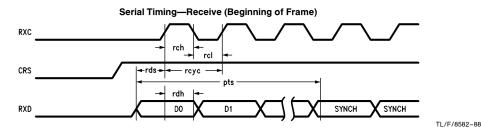

The Receive Deserializer is activated when the input signal Carrier Sense is asserted to allow incoming bits to be shifted into the shift register by the receive clock. The serial receive data is also routed to the CRC generator/checker. The Receive Deserializer includes a synch detector which detects the SFD (Start of Frame Delimiter) to establish where byte boundaries within the serial bit stream are located. After every eight receive clocks, the byte wide data is transferred to the 16-byte FIFO and the Receive Byte Count is incremented. The first six bytes after the SFD are checked for valid comparison by the Address Recognition Logic. If the Address Recognition Logic does not recognize the packet, the FIFO is cleared.

#### CRC GENERATOR/CHECKER

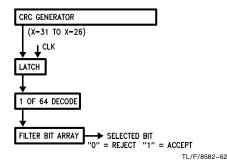

During transmission, the CRC logic generates a local CRC field for the transmitted bit sequence. The CRC encodes all fields after the synch byte. The CRC is shifted out MSB first following the last transmit byte. During reception the CRC logic generates a CRC field from the incoming packet. This local CRC is serially compared to the incoming CRC appended to the end of the packet by the transmitting node. If the local and received CRC match, a specific pattern will be generated and decoded to indicate no data errors. Transmission errors result in a different pattern and are detected, resulting in rejection of a packet.

#### TRANSMIT SERIALIZER

The Transmit Serializer reads parallel data from the FIFO and serializes it for transmission. The serializer is clocked by

the transmit clock generated by the Serial Network Interface (DP8391). The serial data is also shifted into the CRC generator/checker. At the beginning of each transmission, the Preamble and Synch Generator append 62 bits of 1,0 preamble and a 1,1 synch pattern. After the last data byte of the packet has been serialized the 32-bit FCS field is shifted directly out of the CRC generator. In the event of a collision the Preamble and Synch generator is used to generate a 32-bit JAM pattern of all 1's

#### ADDRESS RECOGNITION LOGIC

The address recognition logic compares the Destination Address Field (first 6 bytes of the received packet) to the Physical address registers stored in the Address Register Array. If any one of the six bytes does not match the pre-programmed physical address, the Protocol Control Logic rejects the packet. All multicast destination addresses are filtered using a hashing technique. (See register description.) If the multicast address indexes a bit that has been set in the filter bit array of the Multicast Address Register Array the packet is accepted, otherwise it is rejected by the Protocol Control Logic. Each destination address is also checked for all 1's which is the reserved broadcast address.

#### FIFO AND FIFO CONTROL LOGIC

The NIC features a 16-byte FIFO. During transmission the DMA writes data into the FIFO and the Transmit Serializer reads data from the FIFO and transmits it. During reception the Receive Deserializer writes data into the FIFO and the DMA reads data from the FIFO. The FIFO control logic is used to count the number of bytes in the FIFO shat after a preset level, the DMA can begin a bus access and write/read data to/from the FIFO before a FIFO underflow//overflow occurs.

#### 3.0 Functional Description (Continued)

Because the NIC must buffer the Address field of each incoming packet to determine whether the packet matches its Physical Address Registers or maps to one of its Multicast Registers, the first local DMA transfer does not occur until 8 bytes have accumulated in the FIFO.

To assure that there is no overwriting of data in the FIFO, the FIFO logic flags a FIFO overrun as the 13th byte is written into the FIFO; this effectively shortens the FIFO to 13 bytes. In addition, the FIFO logic operates differently in Byte Mode than in Word Mode. In Byte Mode, a threshold is indicated when the n  $\pm$  1 byte has entered the FIFO; thus, with an 8-byte threshold, the NIC issues Bus Request (BREQ) when the 9th byte has entered the FIFO. For Word Mode, BREQ is not generated until the n  $\pm$  2 bytes have entered the FIFO. Thus, with a 4 word threshold (equivalent to an 8-byte threshold), BREQ is issued when the 10th byte has entered the FIFO.

#### PROTOCOL PLA

The protocol PLA is responsible for implementing the IEEE 802.3 protocol, including collision recovery with random backoff. The Protocol PLA also formats packets during transmission and strips preamble and synch during reception

#### **DMA AND BUFFER CONTROL LOGIC**

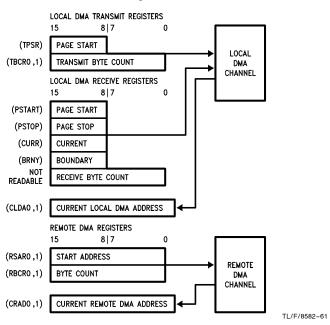

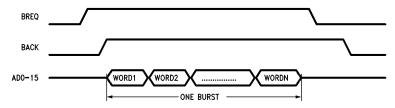

The DMA and Buffer Control Logic is used to control two 16-bit DMA channels. During reception, the Local DMA stores packets in a receive buffer ring, located in buffer memory. During transmission the Local DMA uses programmed pointer and length registers to transfer a packet from local buffer memory to the FIFO. A second DMA channel is used as a slave DMA to transfer data between the local buffer memory and the host system. The Local DMA and Remote DMA are internally arbitrated, with the Local DMA channel having highest priority. Both DMA channels use a common external bus clock to generate all required bus timing. External arbitration is performed with a standard bus request, bus acknowledge handshake protocol.

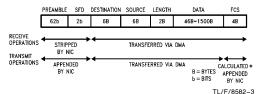

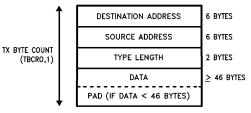

# 4.0 Transmit/Receive Packet Encapsulation/Decapsulation

A standard IEEE 802.3 packet consists of the following fields: preamble, Start of Frame Delimiter (SFD), destination address, source address, length, data, and Frame Check Sequence (FCS). The typical format is shown in *Figure 2*. The packets are Manchester encoded and decoded by the DP8391 SNI and transferred serially to the NIC using NRZ data with a clock. All fields are of fixed length except for the data field. The NIC generates and appends the preamble, SFD and FCS field during transmission. The Preamble and SFD fields are stripped during reception. (The CRC is passed through to buffer memory during reception.)

#### PREAMBLE AND START OF FRAME DELIMITER (SFD)

The Manchester encoded alternating 1,0 preamble field is used by the SNI (DP8391) to acquire bit synchronization with an incoming packet. When transmitted each packet contains 62 bits of alternating 1,0 preamble. Some of this preamble will be lost as the packet travels through the network. The preamble field is stripped by the NIC. Byte alignment is performed with the Start of Frame Delimiter (SFD) pattern which consists of two consecutive 1's. The NIC does not treat the SFD pattern as a byte, it detects only the

two bit pattern. This allows any preceding preamble within the SFD to be used for phase locking.

#### **DESTINATION ADDRESS**

The destination address indicates the destination of the packet on the network and is used to filter unwanted packets from reaching a node. There are three types of address formats supported by the NIC: physical, multicast, and broadcast. The physical address is a unique address that corresponds only to a single node. All physical addresses have an MSB of "0". These addresses are compared to the internally stored physical address registers. Each bit in the destination address must match in order for the NIC to accept the packet. Multicast addresses begin with an MSB of "1". The DP8390D filters multicast addresses using a standard hashing algorithm that maps all multicast addresses into a 6-bit value. This 6-bit value indexes a 64-bit array that filters the value. If the address consists of all 1's it is a broadcast address, indicating that the packet is intended for all nodes. A promiscuous mode allows reception of all packets: the destination address is not required to match any filters. Physical, broadcast, multicast, and promiscuous address modes can be selected.

#### SOURCE ADDRESS

The source address is the physical address of the node that sent the packet. Source addresses cannot be multicast or broadcast addresses. This field is simply passed to buffer memory.

#### LENGTH FIELD

The 2-byte length field indicates the number of bytes that are contained in the data field of the packet. This field is not interpreted by the NIC.

#### **DATA FIELD**

The data field consists of anywhere from 46 to 1500 bytes. Messages longer than 1500 bytes need to be broken into multiple packets. Messages shorter than 46 bytes will require appending a pad to bring the data field to the minimum length of 46 bytes. If the data field is padded, the number of valid data bytes is indicated in the length field. The NIC does not strip or append pad bytes for short packets, or check for oversize packets.

#### FCS FIELD

The Frame Check Sequence (FCS) is a 32-bit CRC field calculated and appended to a packet during transmission to allow detection of errors when a packet is received. During reception, error free packets result in a specific pattern in the CRC generator. Packets with improper CRC will be rejected. The AUTODIN II (X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X5 + X4 + X2 + X1 + 1) polynomial is used for the CRC calculations.

FIGURE 2

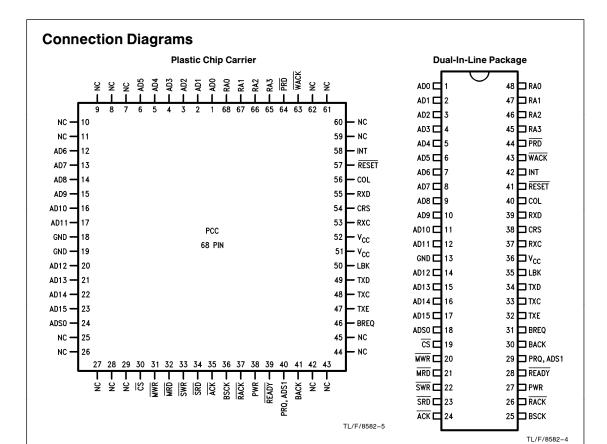

Order Number DP8390DN or DP8390DV See NS Package Number N48A or V68A

#### 5.0 Pin Descriptions

#### **BUS INTERFACE PINS**

| Symbol   | DIP Pin No    | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

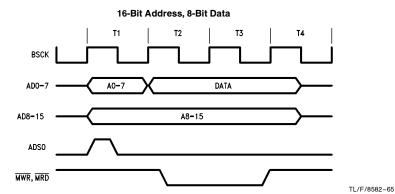

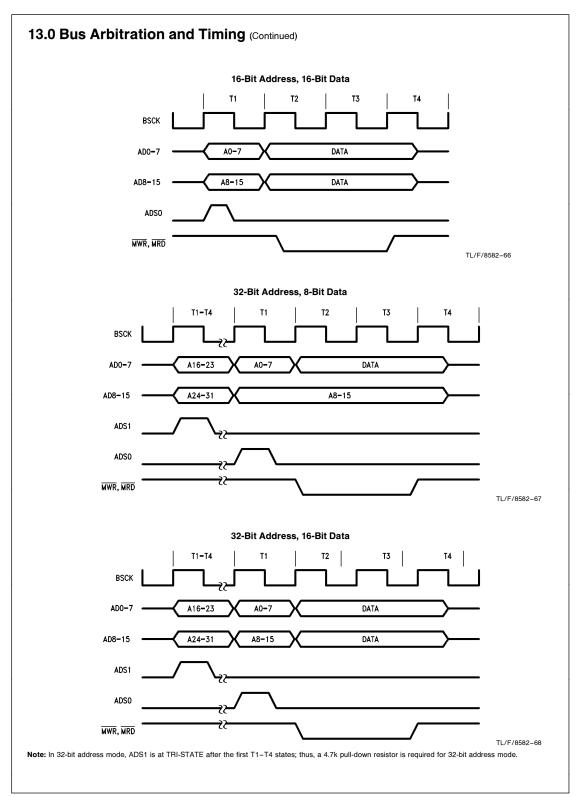

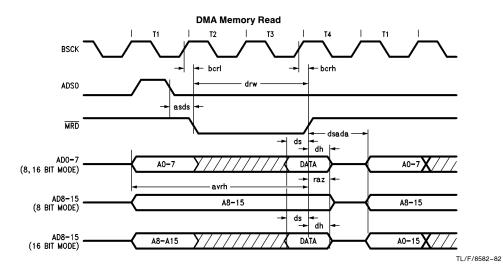

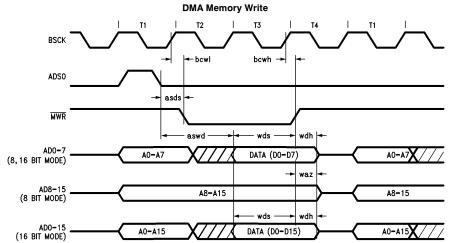

| AD0-AD15 | 1–12<br>14–17 | I/O,Z    | MULTIPLEXED ADDRESS/DATA BUS:  Register Access, with DMA inactive, CS low and ACK returned from NIC, pins AD0-AD7 are used to read/write register data. AD8-AD15 float during I/O transfers. SRD, SWR pins are used to select direction of transfer.  Bus Master with BACK input asserted. During t1 of memory cycle AD0-AD15 contain address. During t2, t3, t4 AD0-AD15 contain data (word transfer mode). During t2, t3, t4 AD0-AD7 contain data, AD8-AD15 contain address (byte transfer mode). Direction of transfer is indicated by NIC on MWR, MRD lines. |

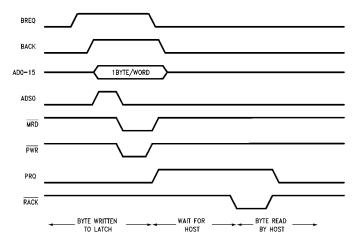

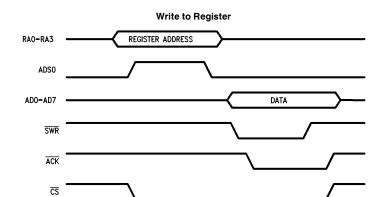

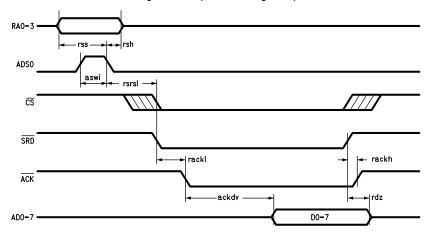

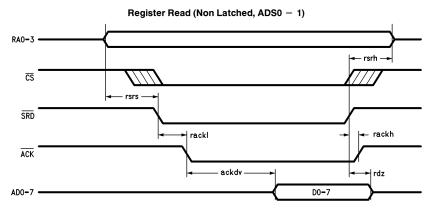

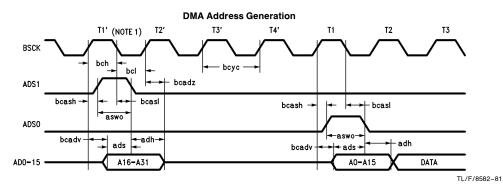

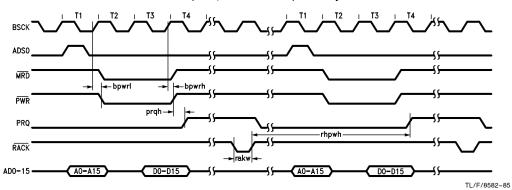

| ADS0     | 18            | I/O,Z    | ADDRESS STROBE 0 Input with DMA inactive and CS low, latches RA0–RA3 inputs on falling edge. If high, data present on RA0–RA3 will flow through latch. Output when Bus Master, latches address bits (A0–A15) to external memory during DMA transfers.                                                                                                                                                                                                                                                                                                            |

# 5.0 Pin Descriptions (Continued)

BUS INTERFACE PINS (Continued)

| Symbol    | DIP Pin No | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

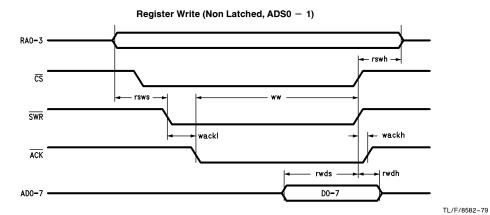

| <u>CS</u> | 19         | I        | <b>CHIP SELECT:</b> Chip Select places controller in slave mode for $\mu P$ access to internal registers. Must be valid through data portion of bus cycle. RA0–RA3 are used to select the internal register. $\overline{SWR}$ and $\overline{SRD}$ select direction of data transfer.                                                                                                                                                                                                                                                                                                                    |

| MWR       | 20         | O,Z      | MASTER WRITE STROBE: Strobe for DMA transfers, active low during write cycles (t2, t3, tw) to buffer memory. Rising edge coincides with the presence of valid output data. TRI-STATE® until BACK asserted.                                                                                                                                                                                                                                                                                                                                                                                               |

| MRD       | 21         | O,Z      | MASTER READ STROBE: Strobe for DMA transfers, active during read cycles (t2, t3, tw) to buffer memory. Input data must be valid on rising edge of MRD. TRI-STATE until BACK asserted.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SWR       | 22         | I        | <b>SLAVE WRITE STROBE:</b> Strobe from CPU to write an internal register selected by RA0–RA3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SRD       | 23         | I        | <b>SLAVE READ STROBE:</b> Strobe from CPU to read an internal register selected by RA0-RA3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ĀCK       | 24         | 0        | ACKNOWLEDGE: Active low when NIC grants access to CPU. Used to insert WAIT states to CPU until NIC is synchronized for a register read or write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RA0-RA3   | 45–48      | I        | <b>REGISTER ADDRESS:</b> These four pins are used to select a register to be read or written. The state of these inputs is ignored when the NIC is not in slave mode (CS high).                                                                                                                                                                                                                                                                                                                                                                                                                          |

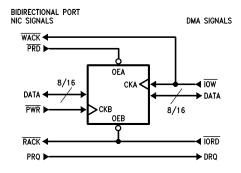

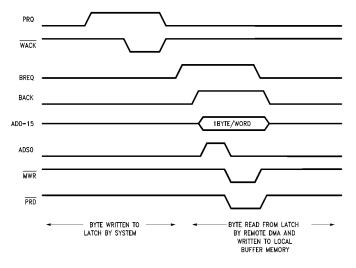

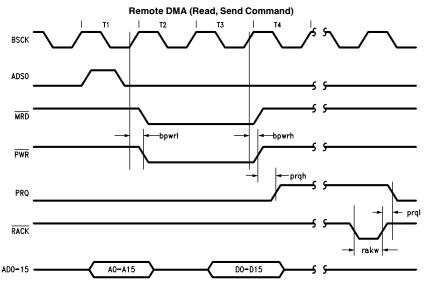

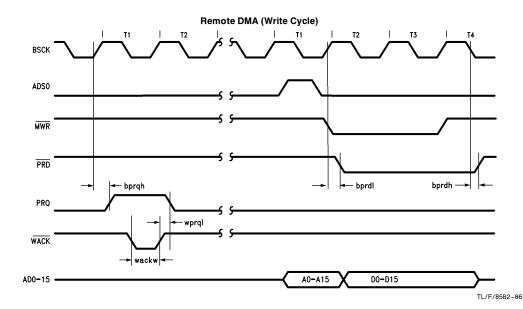

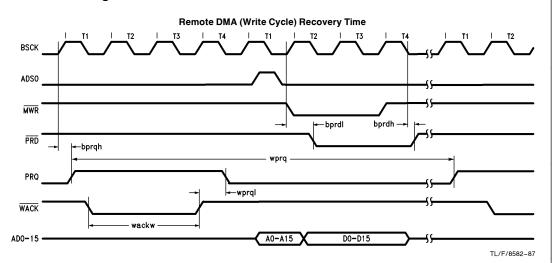

| PRD       | 44         | 0        | <b>PORT READ:</b> Enables data from external latch onto local bus during a memory write cycle to local memory (remote write operation). This allows asynchronous transfer of data from the system memory to local memory.                                                                                                                                                                                                                                                                                                                                                                                |

| WACK      | 43         | I        | WRITE ACKNOWLEDGE: Issued from system to NIC to indicate that data has been written to the external latch. The NIC will begin a write cycle to place the data in local memory.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| INT       | 42         | 0        | INTERRUPT: Indicates that the NIC requires CPU attention after reception transmission or completion of DMA transfers. The interrupt is cleared by writing to the ISR. All interrupts are maskable.                                                                                                                                                                                                                                                                                                                                                                                                       |

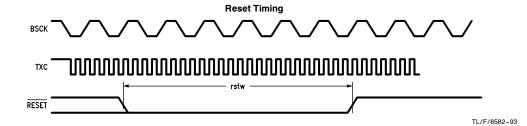

| RESET     | 41         | I        | RESET: Reset is active low and places the NIC in a reset mode immediately, no packets are transmitted or received by the NIC until STA bit is set. Affects Command Register, Interrupt Mask Register, Data Configuration Register and Transmit Configuration Register. The NIC will execute reset within 10 BUSK cycles.                                                                                                                                                                                                                                                                                 |

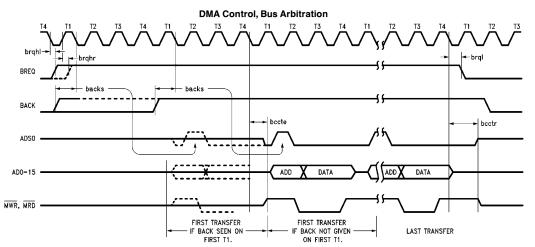

| BREQ      | 31         | 0        | BUS REQUEST: Bus Request is an active high signal used to request the bus for DMA transfers. This signal is automatically generated when the FIFO needs servicing.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BACK      | 30         | I        | BUS ACKNOWLEDGE: Bus Acknowledge is an active high signal indicating that the CPU has granted the bus to the NIC. If immediate bus access is desired, BREQ should be tied to BACK. Tying BACK to V <sub>CC</sub> will result in a deadlock.                                                                                                                                                                                                                                                                                                                                                              |

| PRQ, ADS1 | 29         | O,Z      | PORT REQUEST/ADDRESS STROBE 1  32-BIT MODE: If LAS is set in the Data Configuration Register, this line is programmed as ADS1. It is used to strobe addresses A16-A31 into external latches. (A16-A31 are the fixed addresses stored in RSAR0, RSAR1.) ADS1 will remain at TRI-STATE until BACK is received.  16-BIT MODE: If LAS is not set in the Data Configuration Register, this line is programmed as PRQ and is used for Remote DMA Transfers. In this mode PRQ will be a standard logic output.  NOTE: This line will power up as TRI-STATE until the Data Configuration Register is programmed. |

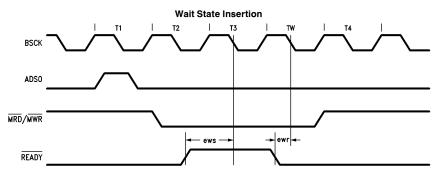

| READY     | 28         | I        | READY: This pin is set high to insert wait states during a DMA transfer. The NIC will sample this signal at t3 during DMA transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### 5.0 Pin Descriptions (Continued)

BUS INTERFACE PINS (Continued)

| Symbol          | DIP Pin No     | Function | Description                                                                                                                                                                                                                                                             |

|-----------------|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWR             | 27             | 0        | PORT WRITE: Strobe used to latch data from the NIC into external latch for transfer to host memory during Remote Read transfers. The rising edge of PWR coincides with the presence of valid data on the local bus.                                                     |

| RACK            | 26             | I        | READ ACKNOWLEDGE: Indicates that the system DMA or host CPU has read the data placed in the external latch by the NIC. The NIC will begin a read cycle to update the latch.                                                                                             |

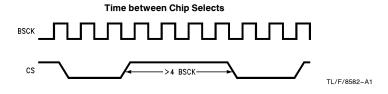

| BSCK            | 25             | I        | This clock is used to establish the period of the DMA memory cycle. Four clock cycles (t1, t2, t3, t4) are used per DMA cycle. DMA transfers can be extended by one BSCK increments using the READY input.                                                              |

| NETWORK         | ( INTERFACE PI | NS       |                                                                                                                                                                                                                                                                         |

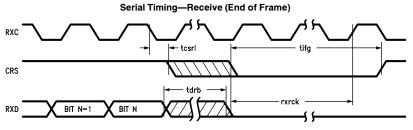

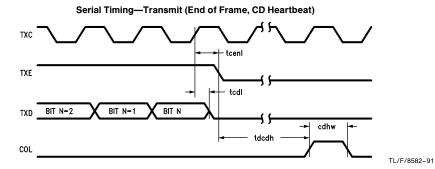

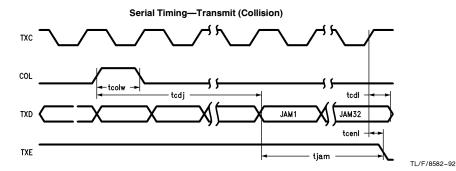

| COL             | 40             | I        | COLLISION DETECT: This line becomes active when a collision has been detected on the coaxial cable. During transmission this line is monitored after preamble and synch have been transmitted. At the end of each transmission this line is monitored for CD heartbeat. |

| RXD             | 39             | I        | RECEIVE DATA: Serial NRZ data received from the ENDEC, clocked into the NIC on the rising edge of RXC.                                                                                                                                                                  |

| CRS             | 38             | I        | CARRIER SENSE: This signal is provided by the ENDEC and indicates that carrier is present. This signal is active high.                                                                                                                                                  |

| RXC             | 37             | I        | RECEIVE CLOCK: Re-synchronized clock from the ENDEC used to clock data from the ENDEC into the NIC.                                                                                                                                                                     |

| LBK             | 35             | 0        | LOOPBACK: This output is set high when the NIC is programmed to perform a loopback through the StarLAN ENDEC.                                                                                                                                                           |

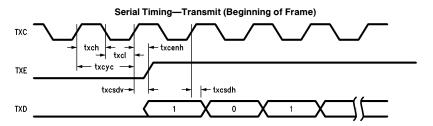

| TXD             | 34             | 0        | TRANSMIT DATA: Serial NRZ Data output to the ENDEC. The data is valid on the rising edge of TXC.                                                                                                                                                                        |

| TXC             | 33             | I        | TRANSMIT CLOCK: This clock is used to provide timing for internal operation and to shift bits out of the transmit serializer. TXC is nominally a 1 MHz clock provided by the ENDEC.                                                                                     |

| TXE             | 32             | 0        | TRANSMIT ENABLE: This output becomes active when the first bit of the packet is valid on TXD and goes low after the last bit of the packet is clocked out of TXD. This signal connects directly to the ENDEC. This signal is active high.                               |

| POWER           |                |          |                                                                                                                                                                                                                                                                         |

| V <sub>CC</sub> | 36             |          | +5V DC is required. It is suggested that a decoupling capacitor be connected                                                                                                                                                                                            |

| GND             | 13             |          | between these pins. It is essential to provide a path to ground for the GND pin with the lowest possible impedance.                                                                                                                                                     |

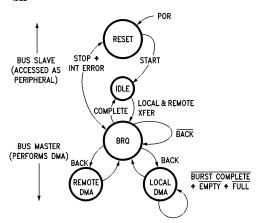

#### 6.0 Direct Memory Access Control (DMA)

The DMA capabilities of the NIC greatly simplify use of the DP8390D in typical configurations. The local DMA channel transfers data between the FIFO and memory. On transmission, the packet is DMA'd from memory to the FIFO in bursts. Should a collision occur (up to 15 times), the packet is retransmitted with no processor intervention. On reception, packets are DMAed from the FIFO to the receive buffer ring (as explained below).

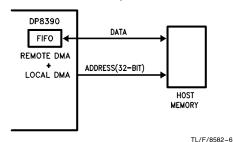

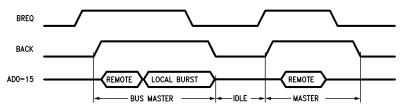

A remote DMA channel is also provided on the NIC to accomplish transfers between a buffer memory and system memory. The two DMA channels can alternatively be combined to form a single 32-bit address with 8- or 16-bit data.

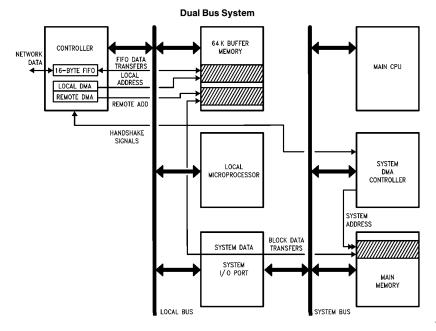

#### **DUAL DMA CONFIGURATION**

An example configuration using both the local and remote DMA channels is shown below. Network activity is isolated

on a local bus, where the NIC's local DMA channel performs burst transfers between the buffer memory and the NIC's FIFO. The Remote DMA transfers data between the buffer memory and the host memory via a bidirectional I/O port. The Remote DMA provides local addressing capability and is used as a slave DMA by the host. Host side addressing must be provided by a host DMA or the CPU. The NIC allows Local and Remote DMA operations to be interleaved.

#### SINGLE CHANNEL DMA OPERATION

If desirable, the two DMA channels can be combined to provide a 32-bit DMA address. The upper 16 bits of the 32-bit address are static and are used to point to a 64k byte (or 32k word) page of memory where packets are to be received and transmitted.

# 6.0 Direct Memory Access Control (DMA) (Continued)

TL/F/8582-55

#### 32-Bit DMA Operation

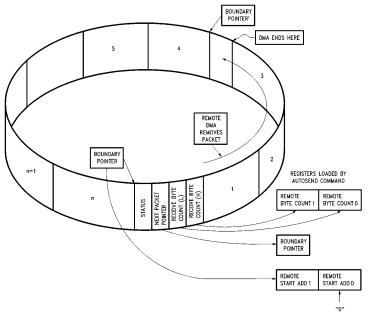

# 7.0 Packet Reception

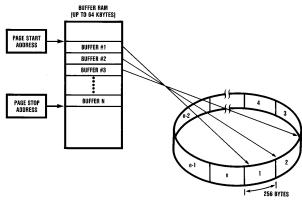

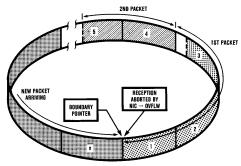

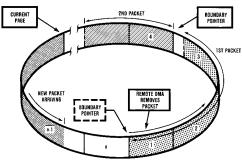

The Local DMA receive channel uses a Buffer Ring Structure comprised of a series of contiguous fixed length 256 byte (128 word) buffers for storage of received packets. The location of the Receive Buffer Ring is programmed in two registers, a Page Start and a Page Stop Register. Ethernet packets consist of a distribution of shorter link control packets and longer data packets, the 256 byte buffer length provides a good compromise between short packets and longer packets to most efficiently use memory. In addition these buffers provide memory resources for storage of back-to-back packets in loaded networks. The assignment of buffers

TL/F/8582-7

#### NIC Receive Buffer Ring

7

for storing packets is controlled by Buffer Management Logic in the NIC. The Buffer Management Logic provides three basic functions: linking receive buffers for long packets, recovery of buffers when a packet is rejected, and recirculation of buffer pages that have been read by the host.

At initialization, a portion of the 64k byte (or 32k word) address space is reserved for the receive buffer ring. Two eight bit registers, the Page Start Address Register (PSTART) and the Page Stop Address Register (PSTOP) define the physical boundaries of where the buffers reside. The NIC treats the list of buffers as a logical ring; whenever the DMA address reaches the Page Stop Address, the DMA is reset to the Page Start Address.

#### INITIALIZATION OF THE BUFFER RING

Two static registers and two working registers control the operation of the Buffer Ring. These are the Page Start Register, Page Stop Register (both described previously), the Current Page Register and the Boundary Pointer Register. The Current Page Register points to the first buffer used to store a packet and is used to restore the DMA for writing status to the Buffer Ring or for restoring the DMA address in the event of a Runt packet, a CRC, or Frame Alignment error. The Boundary Register points to the first packet in the Ring not yet read by the host. If the local DMA address ever reaches the Boundary, reception is aborted. The Boundary Pointer is also used to initialize the Remote DMA for removing a packet and is advanced when a packet is removed. A simple analogy to remember the function of these registers is that the Current Page Register acts as a Write Pointer and the Boundary Pointer acts as a Read Pointer.

Note 1: At initialization, the Page Start Register value should be loaded into both the Current Page Register and the Boundary Pointer Register.

Note 2: The Page Start Register must not be initialized to 00H.

# Receive Buffer Ring At Initialization 4 CURRENT PAGE REGISTER PAGE START REGISTER REGISTER 2 2 286 BYTES

TL/F/8582-30

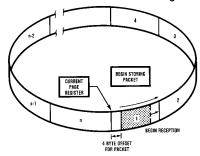

#### **BEGINNING OF RECEPTION**

When the first packet begins arriving the NIC begins storing the packet at the location pointed to by the Current Page

Register. An offset of 4 bytes is saved in this first buffer to allow room for storing receive status corresponding to this packet.

#### **Received Packet Enters Buffer Pages**

TL/F/8582-31

#### **LINKING RECEIVE BUFFER PAGES**

If the length of the packet exhausts the first 256 byte buffer, the DMA performs a forward link to the next buffer to store the remainder of the packet. For a maximal length packet the buffer logic will link six buffers to store the entire packet. Buffers cannot be skipped when linking, a packet will always be stored in contiguous buffers. Before the next buffer can be linked, the Buffer Management Logic performs two comparisons. The first comparison tests for equality between the DMA address of the next buffer and the contents of the Page Stop Register. If the buffer address equals the Page Stop Register, the buffer management logic will restore the DMA to the first buffer in the Receive Buffer Ring value programmed in the Page Start Address Register. The second comparison tests for equality between the DMA address of the next buffer address and the contents of the Boundary Pointer Register. If the two values are equal the reception is aborted. The Boundary Pointer Register can be used to protect against overwriting any area in the receive buffer ring that has not yet been read. When linking buffers, buffer management will never cross this pointer, effectively avoiding any overwrites. If the buffer address does not match either the Boundary Pointer or Page Stop Address, the link to the next buffer is performed.

#### **Linking Buffers**

Before the DMA can enter the next contiguous 256 byte buffer, the address is checked for equality to PSTOP and to the Boundary Pointer. If neither are reached, the DMA is allowed to use the next buffer.

#### **Linking Receive Buffer Pages**

- 1) Check for = to PSTOP

- 2) Check for = to Boundary

TL/F/8582-32

#### **Received Packet Aborted if It Hits Boundary Pointer**

TL/F/8582-8

#### **Buffer Ring Overflow**

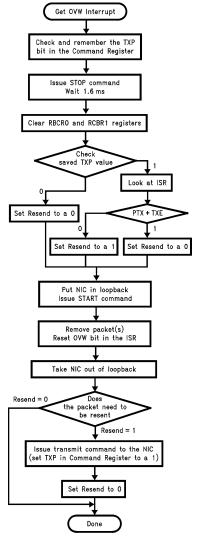

If the Buffer Ring has been filled and the DMA reaches the Boundary Pointer Address, reception of the incoming packet will be aborted by the NIC. Thus, the packets previously received and still contained in the Ring will not be destroyed

In a heavily loaded network environment the local DMA may be disabled, preventing the NIC from buffering packets from the network. To guarantee this will not happen, a software reset must be issued during all Receive Buffer Ring overflows (indicated by the OVW bit in the Interrupt Status Register). The following procedure is required to recover from a Receiver Buffer Ring Overflow.

If this routine is not adhered to, the NIC may act in an unpredictable manner. It should also be noted that it is not permissible to service an overflow interrupt by continuing to empty packets from the receive buffer without implementing the prescribed overflow routine. A flow chart of the NIC's overflow routine can be found at the right.

Note: It is necessary to define a variable in the driver, which will be called "Resend".

- Read and store the value of the TXP bit in the NIC's Command Register.

- Issue the STOP command to the NIC. This is accomplished be setting the STP bit in the NIC's Command Register. Writing 21H to the Command Register will stop the NIC.

- Note: If the STP is set when a transmission is in progress, the RST bit may not be set. In this case, the NIC is guaranteed to be reset after the longest packet time (1500 bytes = 1.2 ms). For the DP8390D (but not for the DP8390B), the NIC will be reset within 2 microseconds after the STP bit is set and Loopback mode 1 is programmed.

- 3. Wait for at least 1.6 ms. Since the NIC will complete any transmission or reception that is in progress, it is necessary to time out for the maximum possible duration of an Ethernet transmission or reception. By waiting 1.6 ms this is achieved with some guard band added. Previously, it was recommended that the RST bit of the Interrupt Status Register be polled to insure that the pending transmission or reception is completed. This bit is not a reliable indicator and subsequently should be ignored.

- Clear the NIC's Remote Byte Count registers (RBCR0 and RBCR1).

TL/F/8582-95

#### **Overflow Routine Flow Chart**

Read the stored value of the TXP bit from step 1, above.If this value is a 0, set the "Resend" variable to a 0 and jump to step 6.

If this value is a 1, read the NIC's Interrupt Status Register. If either the Packet Transmitted bit (PTX) or Transmit Error bit (TXE) is set to a 1, set the "Resend" variable to a 0 and jump to step 6. If neither of these bits is set, place a 1 in the "Resend" variable and jump to step

This step determines if there was a transmission in progress when the stop command was issued in step 2. If there was a transmission in progress, the NIC's ISR is read to determine whether or not the packet was recognized by the NIC. If neither the PTX nor TXE bit was set,

then the packet will essentially be lost and re-transmitted only after a time-out takes place in the upper level software. By determining that the packet was lost at the driver level, a transmit command can be reissued to the NIC once the overflow routine is completed (as in step 11). Also, it is possible for the NIC to defer indefinitely, when it is stopped on a busy network. Step 5 also alleviates this problem. Step 5 is essential and should not be omitted from the overflow routine, in order for the NIC to operate correctly.

- Place the NIC in either mode 1 or mode 2 loopback. This

can be accomplished by setting bits D2 and D1, of the

Transmit Configuration Register, to "0,1" or "1,0", respectively.

- Issue the START command to the NIC. This can be accomplished by writing 22H to the Command Register. This is necessary to activate the NIC's Remote DMA channel.

- Remove one or more packets from the receive buffer ring.

- Reset the overwrite warning (OVW, overflow) bit in the Interrupt Status Register.

- 10. Take the NIC out of loopback. This is done by writing the Transmit Configuration Register with the value it contains during normal operation. (Bits D2 and D1 should both be programmed to 0.)

- 11. If the "Resend" variable is set to a 1, reset the "Resend" variable and reissue the transmit command. This is done by writing a value of 26H to the Command Register. If the "Resend" variable is 0, nothing needs to be done.

Note: If Remote DMA is not being used, the NIC does not need to be started before packets can be removed from the receive buffer ring. Hence, step 8 could be done before step 7.

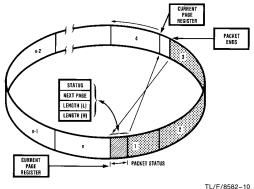

#### **END OF PACKET OPERATIONS**

At the end of the packet the NIC determines whether the received packet is to be accepted or rejected. It either branches to a routine to store the Buffer Header or to another routine that recovers the buffers used to store the packet.

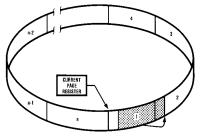

#### SUCCESSFUL RECEPTION

If the packet is successfully received as shown, the DMA is restored to the first buffer used to store the packet (pointed

#### Termination of Received Packet—Packet Accepted

to by the Current Page Register). The DMA then stores the Receive Status, a Pointer to where the next packet will be stored (Buffer 4) and the number of received bytes. Note that the remaining bytes in the last buffer are discarded and reception of the next packet begins on the next empty 256-byte buffer boundary. The Current Page Register is then initialized to the next available buffer in the Buffer Ring. (The location of the next buffer had been previously calculated and temporarily stored in an internal scratchpad register.)

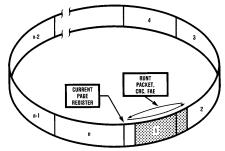

#### BUFFER RECOVERY FOR REJECTED PACKETS

If the packet is a runt packet or contains CRC or Frame Alignment errors, it is rejected. The buffer management logic resets the DMA back to the first buffer page used to store the packet (pointed to by CURR), recovering all buffers that had been used to store the rejected packet. This operation will not be performed if the NIC is programmed to accept either runt packets or packets with CRC or Frame Alignment errors. The received CRC is always stored in buffer memory after the last byte of received data for the packet.

#### Termination of Received Packet—Packet Rejected

TL/F/8582-13

#### **Error Recovery**

If the packet is rejected as shown, the DMA is restored by the NIC by reprogramming the DMA starting address pointed to by the Current Page Register.

#### REMOVING PACKETS FROM THE RING

Packets are removed from the ring using the Remote DMA or an external device. When using the Remote DMA the Send Packet command can be used. This programs the Remote DMA to automatically remove the received packet pointed to by the Boundary Pointer. At the end of the transfer, the NIC moves the Boundary Pointer, freeing additional buffers for reception. The Boundary Pointer can also be moved manually by programming the Boundary Register. Care should be taken to keep the Boundary Pointer at least one buffer behind the Current Page Pointer.

The following is a suggested method for maintaining the Receive Buffer Ring pointers.

- At initialization, set up a software variable (next\_pkt) to indicate where the next packet will be read. At the beginning of each Remote Read DMA operation, the value of next\_pkt will be loaded into RSAR0 and RSAR1.

- 2. When initializing the NIC set: BNDRY = PSTART CURR = PSTART + 1 next\_pkt = PSTART + 1

After a packet is DMAed from the Receive Buffer Ring, the Next Page Pointer (second byte in NIC buffer header) is used to update BNDRY and next\_pkt.

```

next_pkt = Next Page Pointer

BNDRY = Next Page Pointer - 1

If BNDRY < PSTART then BNDRY = PSTOP - 1

```

Note the size of the Receive Buffer Ring is reduced by one 256-byte buffer; this will not, however, impede the operation

In StarLAN applications using bus clock frequencies greater than 4 MHz, the NIC does not update the buffer header information properly because of the disparity between the network and bus clock speeds. The lower byte count is copied twice into the third and fourth locations of the buffer header and the upper byte count is not written. The upper byte count, however, can be calculated from the current next page pointer (second byte in the buffer header) and the previous next page pointer (stored in memory by the CPU). The following routine calculates the upper byte count and allows StarLAN applications to be insensitive to bus clock speeds. Next\_pkt is defined similarly as above.

#### 1st Received Packet Removed By Remote DMA

TL/F/8582-57

$upper\ byte\ count\ =\ next\ page\ pointer\ -\ next\underline{\hspace{0.4cm}} pkt\ -\ 1$

$$\label{eq:count} \begin{split} &\text{if (upper byte count)} < 0 \text{ then} \\ &\text{upper byte count} = & (\text{PSTOP} - \text{next\_pkt}) \ + \\ &\text{(next page pointer} - \text{PSTART}) - 1 \end{split}$$

if (lower byte count) > 0 fch then

upper byte count = upper byte count + 1

#### STORAGE FORMAT FOR RECEIVED PACKETS

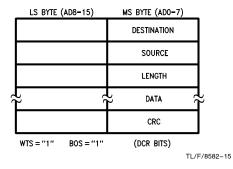

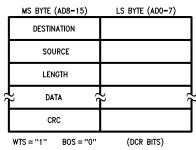

The following diagrams describe the format for how received packets are placed into memory by the local DMA channel. These modes are selected in the Data Configuration Register.

#### Storage Format

| AD15         | AD8   | AD7     | ADO     |

|--------------|-------|---------|---------|

| Next Pa      | acket | Receive |         |

| Pointer      |       | Status  |         |

| Receive      |       | Receive |         |

| Byte Count 1 |       | Byte C  | Count 0 |

| Byte 2       |       | Ву      | te 1    |

BOS = 0, WTS = 1 in Data Configuration Register.

This format used with Series 32000 808X type processors.

| AD15         | AD8 | AD7          | AD0  |

|--------------|-----|--------------|------|

| Next Packet  |     | Receive      |      |

| Pointer      |     | Status       |      |

| Receive      |     | Receive      |      |

| Byte Count 0 |     | Byte Count 1 |      |

| Byte         | 1   | Ву           | te 2 |

BOS = 1, WTS = 1 in Data Configuration Register.

This format used with 68000 type processors.

Note: The Receive Byte Count ordering remains the same for BOS=0 or 1.

| AD7 |                         | AD0 |

|-----|-------------------------|-----|

|     | Receive Status          |     |

|     | Next Packet<br>Pointer  |     |

|     | Receive Byte<br>Count 0 |     |

|     | Receive Byte<br>Count 1 |     |

|     | Byte 0                  |     |

|     | Byte 1                  |     |

BOS = 0, WTS = 0 in Data Configuration Register.

This format used with general 8-bit CPUs.

#### 8.0 Packet Transmission

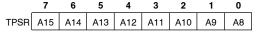

The Local DMA is also used during transmission of a packet. Three registers control the DMA transfer during transmission, a Transmit Page Start Address Register (TPSR) and the Transmit Byte Count Registers (TBCR0,1). When the NIC receives a command to transmit the packet pointed to by these registers, buffer memory data will be moved into the FIFO as required during transmission. The NIC will generate and append the preamble, synch and CRC fields.

#### TRANSMIT PACKET ASSEMBLY

The NIC requires a contiguous assembled packet with the format shown. The transmit byte count includes the Destination Address, Source Address, Length Field and Data. It does not include preamble and CRC. When transmitting data smaller than 46 bytes, the packet must be padded to a minimum size of 64 bytes. The programmer is responsible for adding and stripping pad bytes.

#### **General Transmit Packet Format**

TL/F/8582-58

#### 8.0 Packet Transmission (Continued)

#### TRANSMISSION

Prior to transmission, the TPSR (Transmit Page Start Register) and TBCR0, TBCR1 (Transmit Byte Count Registers) must be initialized. To initiate transmission of the packet the TXP bit in the Command Register is set. The Transmit Status Register (TSR) is cleared and the NIC begins to prefetch transmit data from memory (unless the NIC is currently receiving). If the interframe gap has timed out the NIC will begin transmission.

#### CONDITIONS REQUIRED TO BEGIN TRANSMISSION

In order to transmit a packet, the following three conditions must be met:

- 1. The Interframe Gap Timer has timed out the first 6.4  $\mu s$  of the Interframe Gap (See appendix for Interframe Gap Flowchart)

- 2. At least one byte has entered the FIFO. (This indicates that the burst transfer has been started)

- 3. If the NIC had collided, the backoff timer has expired.

In typical systems the NIC has already prefetched the first burst of bytes before the 6.4  $\mu s$  timer expires. The time during which NIC transmits preamble can also be used to load the FIFO.

Note: If carrier sense is asserted before a byte has been loaded into the FIFO, the NIC will become a receiver.

#### **COLLISION RECOVERY**

During transmission, the Buffer Management logic monitors the transmit circuitry to determine if a collision has occurred. If a collision is detected, the Buffer Management logic will reset the FIFO and restore the Transmit DMA pointers for retransmission of the packet. The COL bit will be set in the TSR and the NCR (Number of Collisions Register) will be incremented. If 15 retransmissions each result in a collision the transmission will be aborted and the ABT bit in the TSR will be set.

Note: NCR reads as zeroes if excessive collisions are encountered.

#### TRANSMIT PACKET ASSEMBLY FORMAT

The following diagrams describe the format for how packets must be assembled prior to transmission for different byte ordering schemes. The various formats are selected in the Data Configuration Register.

| D15 | ١      | D8 E | 07     | D0 |

|-----|--------|------|--------|----|

|     | DA1    |      | DA0    |    |

|     | DA3    |      | DA2    |    |

|     | DA5    |      | DA4    |    |

|     | SA1    |      | DA0    |    |

|     | SA3    |      | DA2    |    |

|     | SA5    |      | DA4    |    |

|     | T/L1   |      | T/L0   |    |

|     | DATA 1 |      | DATA 0 |    |

${\sf BOS}={\sf 0}, {\sf WTS}={\sf 1}$  in Data Configuration Register.

This format is used with Series 32000, 808X type processors.

| D15    | D8 | D7     | D0 |

|--------|----|--------|----|

| DA0    |    | DA1    |    |

| DA2    |    | DA3    |    |

| DA4    |    | DA5    |    |

| SA0    |    | SA1    |    |

| SA2    |    | SA3    |    |

| SA4    |    | SA5    |    |

| T/L0   |    | T/L1   |    |

| DATA 0 |    | DATA 1 |    |

$BOS = 1, WTS = 1 \ \mbox{in Data Configuration Register.}$  This format is used with 68000 type processors.

| D7 |     | D0 |

|----|-----|----|

|    | DA0 |    |

|    | DA1 |    |

|    | DA2 |    |

|    | DA3 |    |

|    | DA4 |    |

|    | DA5 |    |

|    | SA0 |    |

|    | SA1 |    |

|    | SA2 |    |

|    | SA3 |    |

BOS = 0, WTS = 0 in Data Configuration Register.

This format is used with general 8-bit CPUs.

Note: All examples above will result in a transmission of a packet in order of DA0, DA1, DA2, DA3... bits within each byte will be transmitted least significant bit first.

DA = Destination Address

$\mathsf{SA} \,=\, \mathsf{Source}\,\,\mathsf{Address}$

T/L = Type/Length Field

#### 9.0 Remote DMA

The Remote DMA channel is used to both assemble packets for transmission, and to remove received packets from the Receive Buffer Ring. It may also be used as a general purpose slave DMA channel for moving blocks of data or commands between host memory and local buffer memory. There are three modes of operation, Remote Write, Remote Read, or Send Packet.

Two register pairs are used to control the Remote DMA, a Remote Start Address (RSAR0, RSAR1) and a Remote Byte Count (RBCR0, RBCR1) register pair. The Start Address Register pair points to the beginning of the block to be moved while the Byte Count Register pair is used to indicate the number of bytes to be transferred. Full handshake logic is provided to move data between local buffer memory and a bidirectional I/O port.

#### REMOTE WRITE

A Remote Write transfer is used to move a block of data from the host into local buffer memory. The Remote DMA will read data from the I/O port and sequentially write it to local buffer memory beginning at the Remote Start Address. The DMA Address will be incremented and the Byte Counter will be decremented after each transfer. The DMA is terminated when the Remote Byte Count Register reaches a count of zero.

#### REMOTE READ

A Remote Read transfer is used to move a block of data from local buffer memory to the host. The Remote DMA will sequentially read data from the local buffer memory, beginning at the Remote Start Address, and write data to the I/O port. The DMA Address will be incremented and the Byte Counter will be decremented after each transfer. The DMA is terminated when the Remote Byte Count Register reaches zero.

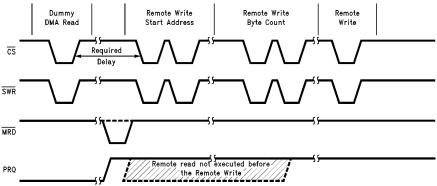

#### **REMOTE DMA WRITE**

#### Setting PRQ Using the Remote Read

Under certain conditions the NIC's bus state machine may issue /MWR and /PRD before PRQ for the first DMA transfer of a Remote Write Command. If this occurs this could cause data corruption, or cause the remote DMA count to be different from the main CPU count causing the system to "lock up".

To prevent this condition when implementing a Remote DMA Write, the Remote DMA Write command should first be preceded by a Remote DMA Read command to insure that the PRQ signal is asserted before the NIC starts its port read cycle. The reason for this is that the state machine that asserts PRQ runs independently of the state machine that controls the DMA signals. The DMA machine assumes that PRQ is asserted, but actually may not be. To remedy this situation, a single Remote Read cycle should be inserted before the actual DMA Write Command is given. This will ensure that PRQ is asserted when the Remote DMA Write is subsequently executed. This single Remote Read cycle is

called a "dummy Remote Read." In order for the dummy Remote Read cycle to operate correctly, the Start Address should be programmed to a known, safe location in the buffer memory space, and the Remote Byte Count should be progammed to a value greater than 1. This will ensure that the master read cycle is performed safely, eliminating the possiblity of data corruption.

#### Remote Write with High Speed Buses

When implementing the Remote DMA Write solution in previous section with high speed buses and CPU's, timing problems may cause the system to hang. Therefore additional considerations are required.

The problem occurs when the system can execute the dummy Remote Read and then start the Remote Write before the NIC has had a chance to execute the Remote Read. If this happens the PRQ signal will not get set, and the Remote Byte Count and Remote Start Address for the Remote Write operation could be corrupted. This is shown by the hatched waveforms in the timing diagram below. The execution of the Remote Read can be delayed by the local DMA operations (particularly during end-of-packet processing).

To ensure the dummy Remote Read does execute, a delay must be inserted between writing the Remote Read Command, and starting to write the Remote Write Start Address. (This time is designated in figure below by the delay arrows.) The recommended method to avoid this problem is, after the Remote Read command is given, to poll both bytes of the Current Remote DMA Address Registers. When the address has incremented, PRQ has been set. Software should recognize this and then start the Remote Write.

An additional caution for high speed systems is that the polling must follow guidelines specified at the end of Section 13. That is, there must be at least 4 bus clocks between chip selects. (For example, when BSCK = 20 MHz, then this time should be 200 ns.)

The general flow for executing a Remote Write is:

Set Remote Byte Count to a value >1 and Remote Start Address to unused RAM (one location before the transmit start address is usually a safe location).

TL/F/8582-96

**Timing Diagram for Dummy Remote Read**

Note: The dashed lines indicate incorrect timing.

- 2. Issue the "dummy" Remote Read command.

- 3. Read the Current Remote DMA Address (CRDA) (both bytes).

- 4. Compare to previous CRDA value if different go to 6.

- 5. Delay and jump to 3.

- 6. Set up for the Remote Write command, by setting the Remote Byte Count and the Remote Start Address (note that if the Remote Byte count in step 1 can be set to the tramsmit byte count plus one, and the Remote Start Address to one less, these will now be incremented to the correct values.)

- 7. Issue the Remote Write command.

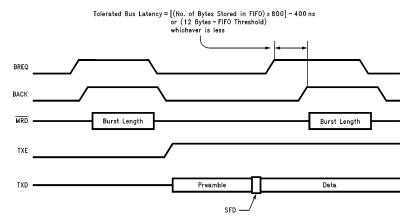

#### **FIFO AND BUS OPERATIONS**

#### Overview

To accommodate the different rates at which data comes from (or goes to) the network and goes to (or comes from) the system memory, the NIC contains a 16-byte FIFO for buffering data between the bus and the media. The FIFO threshold is programmable, allowing filling (or emptying) the FIFO at different rates. When the FIFO has filled to its programmed threshold, the local DMA channel transfers these bytes (or words) into local memory. It is crucial that the local DMA is given access to the bus within a minimum bus latency time; otherwise a FIFO underrun (or overrun) occurs.

To understand FIFO underruns or overruns, there are two causes which produce this condition—

- the bus latency is so long that the FIFO has filled (or emptied) from the network before the local DMA has serviced the FIFO.

- 2) the bus latency or bus data rate has slowed the throughput of the local DMA to point where it is slower than the network data rate (10 Mb/s). This second condition is also dependent upon DMA clock and word width (byte wide or word wide).

The worst case condition ultimately limits the overall bus latency which the NIC can tolerate.

#### FIFO Underrun and Transmit Enable

During transmission, if a FIFO underrun occurs, the Transmit enable (TXE) output may remain high (active). Generally, this will cause a very large packet to be transmitted onto the network. The jabber feature of the transceiver will terminate the transmission, and reset TXE.

To prevent this problem, a properly designed system will not allow FIFO underruns by giving the NIC a bus acknowledge within time shown in the maximum bus latency curves shown and described later.

#### FIFO at the Beginning of Receive

At the beginning of reception, the NIC stores entire Address field of each incoming packet in the FIFO to determine whether the packet matches its Physical Address Registers or maps to one of its Multicast Registers. This causes the FIFO to accumulate 8 bytes. Furthermore, there are some synchronization delays in the DMA PLA. Thus, the actual time that BREQ is asserted from the time the Start of Frame Delimiter (SFD) is detected is 7.8  $\mu s$ . This operation affects the bus latencies at 2 and 4 byte thresholds during the first receive BREQ since the FIFO must be filled to 8 bytes (4 words) before issuing a BREQ.

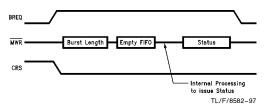

#### FIFO Operation at the End of Receive

When Carrier Sense goes low, the NIC enters its end of packet processing sequence, emptying its FIFO and writing the status information at the beginning of the packet, figure below. This NIC holds onto the bus for the entire sequence. The longest time BREQ may be extended occurs when a packet ends just as the NIC performs its last FIFO burst. The NIC, in this case, performs a programmed burst transfer followed by flushing the remaining bytes in the FIFO, and completes by writing the header information to memory. The following steps occur during this sequence.

- 1) NIC issues BREQ because the FIFO threshold has been reached.

- During the burst, packet ends, resulting in BREQ extended.

- 3) NIC flushes remaining bytes from FIFO.

- 4) NIC performs internal processing to prepare for writing the header.

- 5) NIC writes 4-byte (2-word) header.

- 6) NIC deasserts BREQ.

**End of Packet Processing**

End of Packet Processing (EOPP) times for 10 MHz and 20 MHz have been tabulated in the table below.

#### End of Packet Processing Times for Various FIFO Thresholds, Bus Clocks and Transfer Modes

| Mode | Threshold | Bus Clock | EOPP    |

|------|-----------|-----------|---------|

| Byte | 2 bytes   |           | 7.0 μs  |

|      | 4 bytes   | 10 MHz    | 8.6 μs  |

|      | 8 bytes   |           | 11.0 μs |

| Byte | 2 bytes   |           | 3.6 μs  |

|      | 4 bytes   | 20 MHz    | 4.2 μs  |

|      | 8 bytes   |           | 5.0 μs  |

| Word | 2 bytes   |           | 5.4 μs  |

|      | 4 bytes   | 10 MHz    | 6.2 μs  |

|      | 8 bytes   |           | 7.4 μs  |

| Word | 2 bytes   |           | 3.0 μs  |

|      | 4 bytes   | 20 MHz    | 3.2 μs  |

|      | 8 bytes   |           | 3.6 μs  |

#### **Threshold Detection (Bus Latency)**

To assure that no overwriting of data in the FIFO, the FIFO logic flags a FIFO overrun as the 13th byte is written into the FIFO, effectively shortening the FIFO to 13 bytes. The FIFO logic also operates differently in Byte Mode and in Word Mode. In Byte Mode, a threshold is indicated when the n $\pm$ 1

# Maximum Bus Latency for Byte Mode 3 | State | State

byte has entered the FIFO; thus, with an 8 byte threshold, the NIC issues Bus Request (BREQ) when the 9th byte has entered the FIFO. For Word Mode, BREQ is not generated until the n+2 bytes have entered the FIFO. Thus, with a 4 word threshold (equivalent to 8 byte threshold), BREQ is issued when the 10th byte has entered the FIFO. The two graphs, the figures above, indicate the maximum allowable bus latency for Word and Byte transfer modes.

#### The FIFO at the Beginning of Transmit

Before transmitting, the NIC performs a prefetch from memory to load the FIFO. The number of bytes prefetched is the programmed FIFO threshold. The next BREQ is not issued until after the NIC actually begins trasmitting data, i.e., after SFD. The Transmit Prefetch diagram illustrates this process.

#### SEND PACKET COMMAND

The Remote DMA channel can be automatically initialized to transfer a single packet from the Receive Buffer Ring.

# Maximum Bus Latency for Word Mode 3 2 4 word threshold 2 word threshold 1 word threshold 0 0 5 10 15 20 DMA Clock (MHz)

TL/F/8582-99

TL/F/8582-A0

The CPU begins this transfer by issuing a "Send Packet" Command. The DMA will be initialized to the value of the Boundary Pointer Register and the Remote Byte Count Register pair (RBCR0, RBCR1) will be initialized to the value of the Receive Byte Count fields found in the Buffer Header of each packet. After the data is transferred, the Boundary Pointer is advanced to allow the buffers to be used for new receive packets. The Remote Read will terminate when the Byte Count equals zero. The Remote DMA is then prepared to read the next packet from the Receive Buffer Ring. If the DMA pointer crosses the Page Stop Register, it is reset to the Page Start Address. This allows the Remote DMA to remove packets that have wrapped around to the top of the Receive Buffer Ring.

Note 1: In order for the NIC to correctly execute the Send Packet Command, the upper Remote Byte Count Register (RBCR1) must first be loaded with 0FH.

Note 2: The Send Packet command cannot be used with 68000 type proc-

#### **Transmit Prefetch Timing**

#### Remote DMA Autoinitialization from Buffer Ring

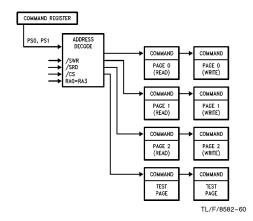

### 10.0 Internal Registers

All registers are 8-bit wide and mapped into two pages which are selected in the Command Register (PS0, PS1). Pins RA0-RA3 are used to address registers within each page. Page 0 registers are those registers which are commonly accessed during NIC operation while page 1 registers are used primarily for initialization. The registers are partitioned to avoid having to perform two write/read cycles to access commonly used registers.

#### 10.1 REGISTER ADDRESS MAPPING

TL/F/8582-59

# 10.2 REGISTER ADDRESS ASSIGNMENTS

Page 0 Address Assignments (PS1 = 0, PS0 = 0)

| RA0-RA3 | RD                                                     | WR                                         |

|---------|--------------------------------------------------------|--------------------------------------------|

| 00H     | Command (CR)                                           | Command (CR)                               |

| 01H     | Current Local DMA<br>Address 0 (CLDA0)                 | Page Start Register<br>(PSTART)            |

| 02H     | Current Local DMA<br>Address 1 (CLDA1)                 | Page Stop Register<br>(PSTOP)              |

| 03H     | Boundary Pointer<br>(BNRY)                             | Boundary Pointer<br>(BNRY)                 |

| 04H     | Transmit Status<br>Register (TSR)                      | Transmit Page Start<br>Address (TPSR)      |

| 05H     | Number of Collisions<br>Register (NCR)                 | Transmit Byte Count<br>Register 0 (TBCR0)  |

| 06H     | FIFO (FIFO)                                            | Transmit Byte Count<br>Register 1 (TBCR1)  |

| 07H     | Interrupt Status<br>Register (ISR)                     | Interrupt Status<br>Register (ISR)         |

| 08H     | Current Remote DMA<br>Address 0 (CRDA0)                | Remote Start Address<br>Register 0 (RSAR0) |

| 09H     | Current Remote DMA<br>Address 1 (CRDA1)                | Remote Start Address<br>Register 1 (RSAR1) |

| 0AH     | Reserved                                               | Remote Byte Count<br>Register 0 (RBCR0)    |

| 0BH     | Reserved                                               | Remote Byte Count<br>Register 1 (RBCR1)    |

| 0CH     | Receive Status<br>Register (RSR)                       | Receive Configuration<br>Register (RCR)    |

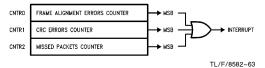

| 0DH     | Tally Counter 0<br>(Frame Alignment<br>Errors) (CNTR0) | Transmit Configuration<br>Register (TCR)   |

| 0EH     | Tally Counter 1<br>(CRC Errors)<br>(CNTR1)             | Data Configuration<br>Register (DCR)       |

| 0FH     | Tally Counter 2<br>(Missed Packet<br>Errors) (CNTR2)   | Interrupt Mask<br>Register (IMR)           |

Page 1 Address Assignments (PS1 = 0, PS0 = 1)

| RA0-RA3 | RD                                     | WR                                     |

|---------|----------------------------------------|----------------------------------------|

| 00H     | Command (CR)                           | Command (CR)                           |

| 01H     | Physical Address<br>Register 0 (PAR0)  | Physical Address<br>Register 0 (PAR0)  |

| 02H     | Physical Address<br>Register 1 (PAR1)  | Physical Address<br>Register 1 (PAR1)  |

| 03H     | Physical Address<br>Register 2 (PAR2)  | Physical Address<br>Register 2 (PAR2)  |

| 04H     | Physical Address<br>Register 3 (PAR3)  | Physical Address<br>Register 3 (PAR3)  |

| 05H     | Physical Address<br>Register 4 (PAR4)  | Physical Address<br>Register 4 (PAR4)  |

| 06H     | Physical Address<br>Register 5 (PAR5)  | Physical Address<br>Register 5 (PAR5)  |

| 07H     | Current Page<br>Register (CURR)        | Current Page<br>Register (CURR)        |

| 08H     | Multicast Address<br>Register 0 (MAR0) | Multicast Address<br>Register 0 (MAR0) |

| 09H     | Multicast Address<br>Register 1 (MAR1) | Multicast Address<br>Register 1 (MAR1) |

| 0AH     | Multicast Address<br>Register 2 (MAR2) | Multicast Address<br>Register 2 (MAR2) |

| 0BH     | Multicast Address<br>Register 3 (MAR3) | Multicast Address<br>Register 3 (MAR3) |

| 0CH     | Multicast Address<br>Register 4 (MAR4) | Multicast Address<br>Register 4 (MAR4) |

| 0DH     | Multicast Address<br>Register 5 (MAR5) | Multicast Address<br>Register 5 (MAR5) |

| 0EH     | Multicast Address<br>Register 6 (MAR6) | Multicast Address<br>Register 6 (MAR6) |

| 0FH     | Multicast Address<br>Register 7 (MAR7) | Multicast Address<br>Register 7 (MAR7) |

# Page 2 Address Assignments (PS1 = 1, PS0 = 0)

| RA0-RA3 | RD                                    | WR                                     |

|---------|---------------------------------------|----------------------------------------|

| 00H     | Command (CR)                          | Command (CR)                           |

| 01H     | Page Start Register<br>(PSTART)       | Current Local DMA<br>Address 0 (CLDA0) |

| 02H     | Page Stop Register (PSTOP)            | Current Local DMA<br>Address 1 (CLDA1) |

| 03H     | Remote Next Packet<br>Pointer         | Remote Next Packet<br>Pointer          |

| 04H     | Transmit Page Start<br>Address (TPSR) | Reserved                               |

| 05H     | Local Next Packet<br>Pointer          | Local Next Packet<br>Pointer           |

| 06H     | Address Counter<br>(Upper)            | Address Counter<br>(Upper)             |

| 07H     | Address Counter (Lower)               | Address Counter (Lower)                |

| RA0-RA3 | RD                                    | WR       |

|---------|---------------------------------------|----------|

| 08H     | Reserved                              | Reserved |

| 09H     | Reserved                              | Reserved |

| 0AH     | Reserved                              | Reserved |

| 0BH     | Reserved                              | Reserved |

| 0CH     | Receive Configuration Register (RCR)  | Reserved |

| 0DH     | Transmit Configuration Register (TCR) | Reserved |

| 0EH     | Data Configuration<br>Register (DCR)  | Reserved |

| 0FH     | Interrupt Mask Register (IMR)         | Reserved |

**Note:** Page 2 registers should only be accessed for diagnostic purposes. They should not be modified during normal operation.

Page 3 should never be modified.

#### 10.3 Register Descriptions

#### COMMAND REGISTER (CR) 00H (READ/WRITE)

The Command Register is used to initiate transmissions, enable or disable Remote DMA operations and to select register pages. To issue a command the microprocessor sets the corresponding bit(s) (RD2, RD1, RD0, TXP). Further commands may be overlapped, but with the following rules: (1) If a transmit command overlaps with a remote DMA operation, bits RD0, RD1, and RD2 must be maintained for the remote DMA command when setting the TXP bit. Note, if a remote DMA command is resued when giving the transmit command, the DMA will complete immediately if the remote byte count register have not been reinitialized. (2) If a remote DMA operation overlaps a transmission, RD0, RD1, and RD2 may be written with the desired values and a "0" written to the TXP bit. Writing a "0" to this bit has no effect. (3) A remote write DMA may not overlap remote read operation or visa versa. Either of these operations must either complete or be aborted before the other operation may start. Bits PS1, PS0, RD2, and STP may be set any time.

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| PS1 | PS0 | RD2 | RD1 | RD0 | TXP | STA | STP |

| Bit        | Symbol        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D0         | STP           | STOP: Software reset command, takes the controller offline, no packets will be received or transmitted. Any reception or transmission in progress will continue to completion before entering the reset state. To exit this state, the STP bit must be reset and the STA bit must be set high. To perform a software reset, this bit should be set high. The software reset has executed only when indicated by the RST bit in the ISR being set to a 1. STP powers up high.  Note: If the NIC has previously been in start mode and the STP is set, both the STP and STA bits will remain set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| D1         | STA           | <b>START:</b> This bit is used to activate the NIC after either power up, or when the NIC has been placed in a reset mode by software command or error. <b>STA powers up low.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| D2         | ТХР           | TRANSMIT PACKET: This bit must be set to initiate transmission of a packet. TXP is internally reset either after the transmission is completed or aborted. This bit should be set only after the Transmit Byte Count and Transmit Page Start registers have been programmed.  Note: Before the transmit command is given, the STA bit must be set and the STP bit reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |