# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# MOS INTEGRATED CIRCUIT $\mu$ PD720133

# **USB2.0 to IDE Bridge**

The  $\mu$ PD720133 is designed to function as a bridge between USB 2.0 and ATA/ATAPI. The  $\mu$ PD720133 complies with the Universal Serial Bus Specification Revision 2.0 full-/high-speed signaling and works up to 480 Mbps. The  $\mu$ PD720133 consists of a CISC processor, an ATA/ATAPI controller, an endpoint controller (EPC), a serial interface engine (SIE), and an USB2.0 transceiver. The USB2.0 protocol and class specific protocols (bulk only protocol) are handled by the USB2.0 transceiver, the SIE and the EPC. The V30MZ CISC processor in the  $\mu$ PD720133 takes care of the activities in the transport layer. The firmware controlling the  $\mu$ PD720133 is located in an embedded ROM.

# FEATURES

- Compliant with Universal Serial Bus Specification Revision 2.0 (Data Rate 12/480 Mbps)

- Compliant with ATA/ATAPI-6 (LBA48, PIO Mode 0-4, Multi Word DMA Mode 0-2, Ultra DMA Mode 0-4)

- · USB2.0 high-speed bus powered device capability

- Certified by USB implementers forum and granted with USB 2.0 high-speed Logo (TID: 40001985)

- · One USB2.0 high-speed transceiver / receiver with full-speed transceiver / receiver

- USB2.0 High-speed or Full-speed packet protocol sequencer (Serial Interface Engine)

- · Automatic chirp assertion and full-/high-speed mode change

- USB Reset, Suspend and Resume signaling detection

- · Supports power control functionality for IDE device as CD-ROM and HDD

- Supports set feature (TEST\_MODE) functionality

- System Clock is generated by 30 MHz X'tal

- 2.5 V and 3.3 V power supply

# ★ ORDERING INFORMATION

| Part Number       | Package                                                                        |

|-------------------|--------------------------------------------------------------------------------|

| μPD720133GB-YEU-A | 64-pin plastic TQFP (fine pitch) (10 $\times$ 10) Lead-free product            |

| μPD720133GB-YEU-Y | 64-pin plastic TQFP (fine pitch) (10 $\times$ 10) High heat-resistance product |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

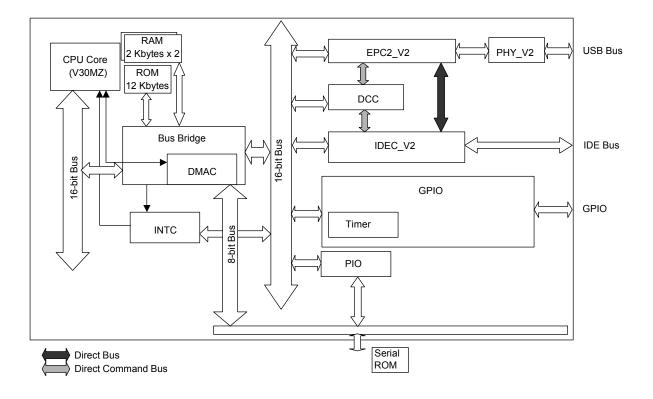

# **BLOCK DIAGRAM**

| V30MZ      | : CISC CPU core                                         |

|------------|---------------------------------------------------------|

| RAM        | : 4-Kbyte work RAM for firmware                         |

| ROM        | : 12-Kbyte ROM for built-in firmware                    |

| PHY_V2     | : USB2.0 transceiver with serial interface engine       |

| EPC2_V2    | : Endpoint controller                                   |

| IDEC_V2    | : IDE controller                                        |

| DCC        | : ATA direct command controller                         |

| Bus Bridge | : Internal / external bus controller and DMA controller |

| INTC       | : Interrupt controller (82C59 like)                     |

| GPIO       | : General purpose 3-bit I/O controller                  |

| PIO        | : Multipurpose 2-bit I/O controller                     |

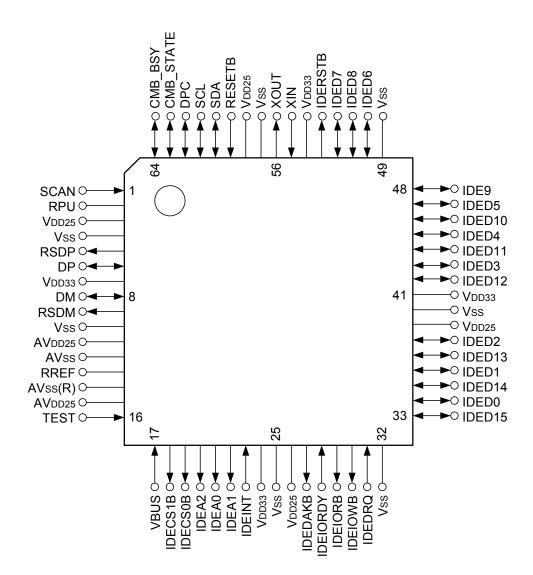

# PIN CONFIGURATION (TOP VIEW)

- 64-pin plastic TQFP (fine pitch) (10 × 10)

- # μPD720133GB-YEU-A

μPD720133GB-YEU-Y

| Pin No | Pin Name         |

|--------|----------|--------|----------|--------|----------|--------|------------------|

| 1      | SCAN     | 17     | VBUS     | 33     | IDED15   | 49     | Vss              |

| 2      | RPU      | 18     | IDECS1B  | 34     | IDED0    | 50     | IDED6            |

| 3      | VDD25    | 19     | IDECS0B  | 35     | IDED14   | 51     | IDED8            |

| 4      | Vss      | 20     | IDEA2    | 36     | IDED1    | 52     | IDED7            |

| 5      | RSDP     | 21     | IDEA0    | 37     | IDED13   | 53     | IDERSTB          |

| 6      | DP       | 22     | IDEA1    | 38     | IDED2    | 54     | Vdd33            |

| 7      | Vdd33    | 23     | IDEINT   | 39     | VDD25    | 55     | XIN              |

| 8      | DM       | 24     | Vdd33    | 40     | Vss      | 56     | XOUT             |

| 9      | RSDM     | 25     | Vss      | 41     | Vdd33    | 57     | Vss              |

| 10     | Vss      | 26     | VDD25    | 42     | IDED12   | 58     | Vdd25            |

| 11     | AVDD25   | 27     | IDEDAKB  | 43     | IDED3    | 59     | RESETB           |

| 12     | AVss     | 28     | IDEIORDY | 44     | IDED11   | 60     | SDA (PIO0)       |

| 13     | RREF     | 29     | IDEIORB  | 45     | IDED4    | 61     | SCL (PIO1)       |

| 14     | AVss(R)  | 30     | IDEIOWB  | 46     | IDED10   | 62     | DPC(GPIO5)       |

| 15     | AVDD25   | 31     | IDEDRQ   | 47     | IDED5    | 63     | CMB_STATE(GPIO6) |

| 16     | TEST     | 32     | Vss      | 48     | IDED9    | 64     | CMB_BSY(GPIO7)   |

**Remark** AVss(R) should be used to connect RREF through 1 % precision reference resistor of 2.43 k $\Omega$ .

# 1. PIN INFORMATION

| Pin Name           | I/O     | Buffer Type              | Active Level | Function                                      |

|--------------------|---------|--------------------------|--------------|-----------------------------------------------|

| XIN                | Ι       | 2.5 V Input              |              | System clock input or oscillator In           |

| XOUT               | 0       | 2.5 V Output             |              | Oscillator out                                |

| RESETB             | I       | 3.3 V Schmitt Input      | Low          | Asynchronous reset signaling                  |

| IDECS(1:0)B        | 0 (I/O) | 5 V tolerant Output      | Low          | IDE host chip select                          |

| IDEA(2:0)          | O (I/O) | 5 V tolerant Output      |              | IDE address bus                               |

| IDEINT             | Ι       | 5 V tolerant Input       | High         | IDE interrupt request from device to host     |

| IDEDAKB            | O (I/O) | 5 V tolerant Output      | Low          | IDE DMA acknowledge                           |

| IDEIORDY           | I       | 5 V tolerant Input       | High         | IDE IO channel ready                          |

| IDEIORB            | O (I/O) | 5 V tolerant Output      | Low          | IDE IO read strobe                            |

| IDEIOWB            | O (I/O) | 5 V tolerant Output      | Low          | IDE IO write strobe                           |

| IDEDRQ             | Ι       | 5 V tolerant Input       | High         | IDE DMA request from device to host           |

| IDED(15:0)         | I/O     | 5 V tolerant I/O         |              | IDE data bus                                  |

| IDERSTB            | O (I/O) | 5 V tolerant Output      | Low          | IDE reset from host to device                 |

| CMB_BSY (GPIO7)    | I/O     | 3.3 V I/O                |              | Combo IDE bus busy                            |

| CMB_STATE (GPIO6)  | I/O     | 3.3 V I/O                |              | Combo IDE bus state                           |

| DPC (GPIO5)        | I/O     | 3.3 V I/O                |              | Power control signaling for IDE device        |

| SDA (PIO0)         | I/O     | 3.3 V I/O                |              | Serial ROM data signaling                     |

| SCL (PIO1)         | I/O     | 3.3 V I/O                |              | Serial ROM clock signaling                    |

| VBUS               | I       | 5 V Schmitt Input Note   |              | VBUS monitoring                               |

| DP                 | I/O     | USB high speed D+ I/O    |              | USB's high speed D+ signal                    |

| DM                 | I/O     | USB high speed D– I/O    |              | USB's high speed D– signal                    |

| RSDP               | 0       | USB full speed D+ Output |              | USB's full speed D+ signal                    |

| RSDM               | 0       | USB full speed D- Output |              | USB's full speed D– signal                    |

| RPU                | А       | USB Pull-up control      |              | USB's 1.5 k $\Omega$ pull-up resistor control |

| RREF               | А       | Analog                   |              | Reference resistor                            |

| SCAN               | I       | 3.3 V Input              |              | Scan mode control                             |

| TEST               | I       | 3.3 V Input              |              | Test mode setting                             |

| AV <sub>DD25</sub> |         |                          |              | 2.5 V VDD for Analog circuit                  |

| VDD25              |         |                          |              | 2.5 V VDD                                     |

| VDD33              |         |                          |              | 3.3 V VDD                                     |

| AVss               |         |                          |              | Vss for Analog circuit                        |

| Vss                |         |                          |              | Vss                                           |

**Note** VBUS pin may be used to monitor for VBUS line even if V<sub>DD33</sub>, V<sub>DD25</sub>, and AV<sub>DD25</sub> are shut off. The System Designer must ensure that the input voltage level for VBUS pin is less than 3.0 V. [that is the absolute maximum rating].

- Remarks 1. "5 V tolerant" means that the buffer is a 3.3 V buffer with 5 V tolerant circuit.

- 2. The signal marked as "(I/O)" in the above table operates as I/O signals during testing. They should be ignored under normal operation.

# 2. FUNCTION INFORMATION

The USB to IDE system can be realized by  $\mu$ PD720133. If the customizations of data such as USB vendor ID and USB product ID are required, an external serial ROM can be used. The  $\mu$ PD720133 also has power circuit to turn on and off the system power supply. The  $\mu$ PD720133 can operate in either bus-powered mode or self-powered mode. If the total power consumption of the USB to IDE system within the USB 2.0 specification of a bus powered device, it will be possible to realize a high-speed capable bus powered system. In addition,  $\mu$ PD720133 has a feature of IDE bus arbitration. This enables system, which has two IDE controllers to control a single IDE device. In this case, another IDE controller also must have a feature of IDE bus arbitration.

The setting of IDE controller in the  $\mu$ PD720133 is controlled by data in serial ROM.

#### 2.1 Data in Serial ROM

The  $\mu$ PD720133 loads some data such as Vendor ID, Product ID and some additional USB related information, etc from serial ROM during  $\mu$ PD720133 initialization.

| Offset (H) | Data Size            | Symbol             | Description                                                       |

|------------|----------------------|--------------------|-------------------------------------------------------------------|

| +00        | 1 Word               | idMark             | Validation Mark of 55AAH                                          |

| +02        | 1 Word               | CheckSum           | Check sum of serial ROM                                           |

| +04        | 1 Word               | Flags              | Control for descriptor overwrite                                  |

| +06        | 1 Byte               | ModeReset          | PWR, CLC, DCC, DV[1:0], DPC Reset bit map field                   |

| +07        | 1 Byte               | ModeSet            | PWR, CLC, DCC, DV[1:0], DPC Set bit map field                     |

| +08        | 1 Word               | idVendor           | idVendor field in Device descriptor                               |

| +0A        | 1 Word               | idProduct          | idProduct field in Device descriptor                              |

| +0C        | 1 Word               | bcdDevice          | bcdDevice field in Device descriptor                              |

| +0E        | 1 Word               | Reserved           | Reserved for future use.                                          |

| +10        | 1 Byte               | MaxPower Bus       | bMaxPower field in Configuration descriptor for Bus powered mode  |

| +11        | 1 Byte               | MaxPower Self      | bMaxPower field in Configuration descriptor for Self powered mode |

| +12        | 1 Byte               | bInterfaceClass    | bInterfaceClass field in Interface descriptor                     |

| +13        | 1 Byte               | bInterfaceSubClass | bInterfaceSubClass field in Interface descriptor                  |

| +14        | 1 Byte               | bInterfaceProtocol | bInterfaceProtocol field in Interface descriptor                  |

| +15        | 1 Byte               | Reserved           | Reserved for future use.                                          |

| +16        | 1Word                | TxModeReset        | IDE transmission type such as Ultra DMA 66 Reset bit map field    |

| +18        | 1Word                | TxModeSet          | IDE transmission type such as Ultra DMA 66 Set bit map field      |

| +1A        | 1Word                | RompatchSW         | ROM Patch information (Patch On or Off) of External Function      |

| +1C        | 4 Bytes              | Reserved           | Reserved for future use.                                          |

| +20        | 32 Bytes             | ManufactureString  | String descriptor for Manufacturer                                |

| +40        | 32 Bytes             | ProductString      | String descriptor for Product                                     |

| +60        | 32 Bytes             | SerialString       | String descriptor for Device serial number                        |

| +80        | $128 \times n$ Bytes | FW Patch           | Firmware patch module for self-powered/bus-powered mode           |

#### Table 2-1. Data in Serial ROM

# 2.2 Pin Setting

Settings of the SCL, SDA and unused pins (TEST and SCAN) are recommended as follows. Please note that the setting of the SCL depends on size of Serial ROM.

| Pin Name | Setting                 |

|----------|-------------------------|

| SCL      | Pull Up <sup>Note</sup> |

| SDA      | Pull Up                 |

| TEST     | Low Clamp               |

| SCAN     | Low Clamp               |

| Table | 2-2. | Pin | Settings |

|-------|------|-----|----------|

|       |      |     | ooungo   |

**Note** If serial ROM size is more than 2 Kbytes, SCL should be pull down.

The settings for any other pins such as the CMB\_BSY and the CMB\_STATE depend on USB2.0 to IDE Bridge system. For example, if two IDE controllers are implemented in the system to control one target IDE device and one of the two IDE controllers is the  $\mu$ PD720133, then both the CMB\_BSY and the CMB\_STATE are used to handshake between the two IDE controller chips. On the other hand, when the system uses the  $\mu$ PD720133 as the only IDE controller to control a target IDE device, then both the CMB\_BSY and the CMB\_STATE should be connected to ground.

#### 2.3 Control Bit in Serial ROM

The following tables show IDE status and control bit in serial ROM.

| No. | Device<br>Power | Internal<br>Clock | ΑΤΑ/ΑΤΑΡΙ                | PWR | CLC | DV1 | DV0 |

|-----|-----------------|-------------------|--------------------------|-----|-----|-----|-----|

| 0   | Bus Powered     | 7.5 MHz           | No device connected      | 1   | 1   | 1   | 1   |

| 1   |                 |                   | ATA                      | 1   | 1   | 1   | 0   |

| 2   |                 |                   | ATAPI                    | 1   | 1   | 0   | 1   |

| 3   |                 |                   | Reserved                 | 1   | 1   | 0   | 0   |

| 4   |                 | 60 MHz            | No device connected      | 1   | 0   | 1   | 1   |

| 5   |                 |                   | ATA                      | 1   | 0   | 1   | 0   |

| 6   |                 |                   | ATAPI                    | 1   | 0   | 0   | 1   |

| 7   |                 |                   | Reserved                 | 1   | 0   | 0   | 0   |

| 8   | Self Powered    | 60 MHz            | No device connected      | 0   | 1   | 1   | 1   |

| 9   |                 |                   | Combo (ATA)              | 0   | 1   | 1   | 0   |

| 10  |                 |                   | Combo (ATAPI)            | 0   | 1   | 0   | 1   |

| 11  |                 |                   | Combo auto device detect | 0   | 1   | 0   | 0   |

| 12  |                 |                   | No device connected      | 0   | 0   | 1   | 1   |

| 13  |                 |                   | ATA                      | 0   | 0   | 1   | 0   |

| 14  |                 |                   | ATAPI                    | 0   | 0   | 0   | 1   |

| 15  |                 |                   | Auto device detect       | 0   | 0   | 0   | 0   |

#### Table 2-3. DV1/DV0, CLC, PWR Setting

**Remarks 1.** Setting of no. 0, 3, 4, 7, 8, and 12 are not allowed.

- **2.** For bus powered setting, some critical considerations such as power consumption for the total system should be observed.

- 3. The slave device function cannot use Auto device detect.

|     | Condition |                |                  | DCC                      | Description                                                               |

|-----|-----------|----------------|------------------|--------------------------|---------------------------------------------------------------------------|

| DV1 | DV0       | Mode           | Target<br>Device | setting in<br>Serial ROM |                                                                           |

| 1   | 0         | ΑΤΑ            | ΑΤΑ              | Reset<br>Set             | Ultra, Multi Word DMA are disabled.<br>Ultra, Multi Word DMA are enabled. |

| 0   | 1         | ATAPI          | ATAPI            | Reset<br>Set             | Ultra DMA are disabled.<br>Ultra, Multi Word DMA are enabled.             |

| 0   | 0         | Auto<br>device | ΑΤΑ              | Reset<br>Set             | Ultra, Multi Word DMA are disabled.<br>Ultra, Multi Word DMA are enabled. |

|     |           | detect         | ATAPI            | Reset<br>Set             | Ultra DMA are disabled.<br>Ultra, Multi Word DMA are enabled.             |

#### Table 2-4. DV1/DV0, DCC Setting

Remark PIO mode 0-4 are always enabled.

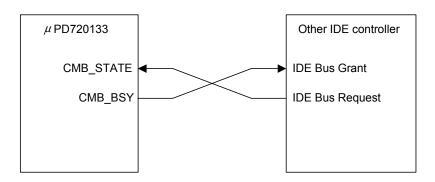

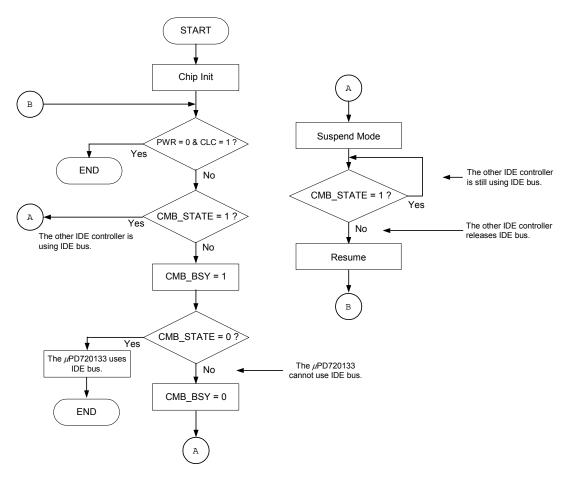

# 2.4 Combo Mode Function

The  $\mu$ PD720133 can be used to realize that two IDE controller chips control one target IDE device in one system. In order to realize IDE bus arbitration between two IDE controller chips, the  $\mu$ PD720133 has the CMB\_BSY and the CMB\_STATE. Combo mode is enabled when PWR = 0 and CLC = 1.

CMB\_BSY and CMB\_STATE are connected to another IDE controller chip as shown below.

Table 2-5. Description of CMB\_BSY and CMB\_STATE

| Pin Name  | Direction | Value                                                         | Description                                        |

|-----------|-----------|---------------------------------------------------------------|----------------------------------------------------|

| CMB_STATE | IN        | 0 Other IDE controller does not require or does not use IDE b |                                                    |

|           |           | 1                                                             | Other IDE controller requires or is using IDE bus. |

| CMB_BSY   | OUT       | 0 The µPD720133 does not require or does not use IDE b        |                                                    |

|           |           | 1                                                             | The $\mu$ PD720133 requires or is using IDE bus.   |

The IDE bus arbitration will be performed in the following sequence. The  $\mu$ PD720133 will check if the other IDE controller is using the IDE bus. If the other IDE controller is not using the IDE bus, the  $\mu$ PD720133 will be able to use the IDE bus. On the other hand, if the other IDE controller is using the IDE bus, the  $\mu$ PD720133 transmits to the suspend mode. And the  $\mu$ PD720133 resumes on condition that the CMB\_STATE becomes low level. After that, the arbitration will restart from the beginning of the sequence.

#### 2.5 Power Control

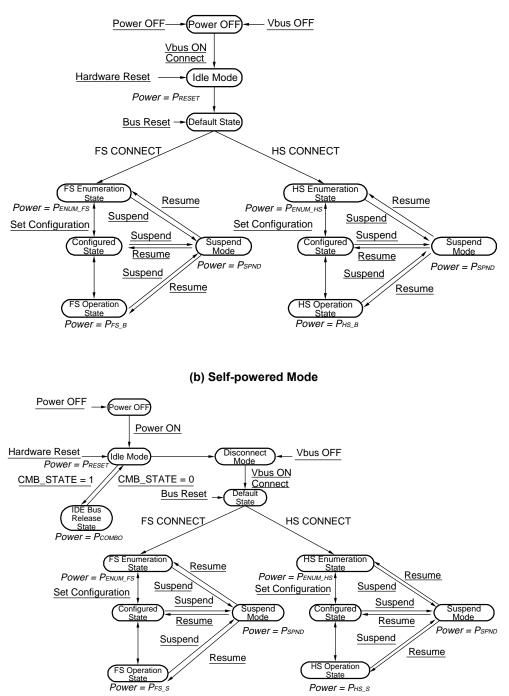

To realize bus-powered or high performance self-powered USB2.0 to IDE Bridge system, the  $\mu$ PD720133 has two internal system clock mode. One is 7.5 MHz for bus-powered mode and another is 60 MHz for self-powered mode. The  $\mu$ PD720133 controls the power state by events as follows. The word with under line indicates event. The Italic word indicates the power state.

#### Figure 2-3. Power State Control

#### (a) Bus-powered Mode

High impedance state

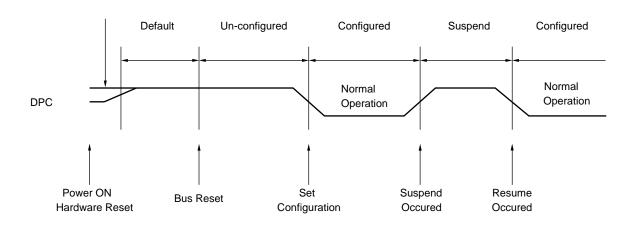

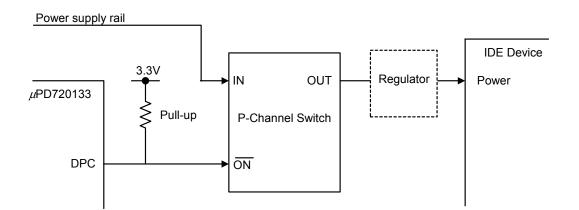

To realize bus-powered USB2.0 to IDE Bridge system,  $\mu$ PD720133 has a DPC pin to control the on and off of the IDE device's power supply according to the USB device states. DPC should be pull-up to 3.3 V because DPC output becomes high impedance state until the  $\mu$ PD720133 is initialized.

Figure 2-4. DPC Pin to Control IDE Device's Power Circuit

The following example is a circuit for controlling the power supplies to IDE device while the  $\mu$ PD720133 is under default and un-configured state. Also, the power supply to IDE device is disabled during suspend state.

Power consumption of total system under default, un-configured, and suspend state can be reduced by DPC pin.

# 3. ELECTRICAL SPECIFICATIONS

- 3.1 Buffer List

- 2.5 V oscillator interface

XIN, XOUT

• 3.3 V input buffer

TEST, SCAN

• 3.3 V schmitt input buffer

RESETB

• 3.3 V IoL = 3 mA bi-directional buffer with input enable (OR-type)

SDA, SCL, DPC (GPIO5), CMB\_STATE (GPIO6), CMB\_BSY (GPIO7)

• 5 V schmitt input buffer

VBUS

5 V IoL = 6 mA bi-directional buffer with input enable (OR-type)

IDED(15:0), IDEINT, IDEIORDY, IDEDRQ, IDECS(1:0)B, IDEA(2:0), IDEDAKB, IDEIORB, IDEIOWB,

IDERSTB

USB interface

DP, DM, RSDP, RSDM, RREF, RPU

**Remark** "5 V" refers to a 3.3 V buffer with 5-V tolerant circuit. Therefore, it is possible to have a 5-V connection for an external bus, but the output level will be only up to 3.3 V, which is the VDD33 voltage.

# 3.2 Terminology

# Terms Used in Absolute Maximum Ratings

| Parameter             | Symbol       | Meaning                                                                                                                                                   |

|-----------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage  | Vdd33, Vdd25 | Indicates voltage range within which damage or reduced reliability will not result when power is applied to a $V_{\text{DD}}$ pin.                        |

| Input voltage         | Vı           | Indicates voltage range within which damage or reduced reliability will not result when power is applied to an input pin.                                 |

| Output voltage        | Vo           | Indicates voltage range within which damage or reduced reliability will not result when power is applied to an output pin.                                |

| Output current        | lo           | Indicates absolute tolerance value for DC current to prevent damage or reduced reliability when a current flows out of or into an output pin.             |

| Operating temperature | Та           | Indicates the ambient temperature range for normal logic operations.                                                                                      |

| Storage temperature   | Tstg         | Indicates the element temperature range within which damage or reduced reliability will not result while no voltage or current are applied to the device. |

# Terms Used in Recommended Operating Range

| Parameter                | Symbol       | Meaning                                                                                                                                                                |

|--------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage     | Vdd33, Vdd25 | Indicates the voltage range for normal logic operations occur when $V_{SS} = 0 V$ .                                                                                    |

| High-level input voltage | Vін          | Indicates the voltage, which is applied to the input pins of the device, is the voltage indicates that the high level states for normal operation of the input buffer. |

|                          |              | * If a voltage that is equal to or greater than the "Min." value is applied, the input voltage is guaranteed as high level voltage.                                    |

| Low-level input voltage  | VIL          | Indicates the voltage, which is applied to the input pins of the device, is the voltage indicates that the low level states for normal operation of the input buffer.  |

|                          |              | * If a voltage that is equal to or lesser than the "Max." value is applied, the input voltage is guaranteed as low level voltage.                                      |

| Hysteresys voltage       | Vн           | Indicates the differential between the positive trigger voltage and the negative trigger voltage.                                                                      |

| Input rise time          | tri          | Indicates allowable input rise time to input pins. Input rise time is transition time from $0.1 \times V_{DD}$ to $0.9 \times V_{DD}$ .                                |

| Input fall time          | tfi          | Indicates allowable input fall time to input pins. Input fall time is transition time from 0.9 $\times$ V_{DD} to 0.1 $\times$ V_{DD}.                                 |

# **Terms Used in DC Characteristics**

| Parameter                        | Symbol | Meaning                                                                                                                                              |

|----------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off-state output leakage current | loz    | Indicates the current that flows from the power supply pins when the rated power supply voltage is applied when a 3-state output has high impedance. |

| Output short circuit current     | los    | Indicates the current that flows when the output pin is shorted (to GND pins) when output is at high-level.                                          |

| Input leakage current            | h      | Indicates the current that flows when the input voltage is supplied to the input pin.                                                                |

| Low-level output current         | lol    | Indicates the current that flows to the output pins when the rated low-level output voltage is being applied.                                        |

| High-level output current        | Іон    | Indicates the current that flows from the output pins when the rated high-level output voltage is being applied.                                     |

#### 3.3 Electrical Specifications

#### **Absolute Maximum Ratings**

| Parameter                     | Symbol | Condition                                                                                                               | Rating       | Unit |

|-------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|--------------|------|

| Power supply voltage          | VDD33  | 3.3 V power supply rail                                                                                                 | -0.5 to +4.6 | V    |

|                               | VDD25  | 2.5 V power supply rail                                                                                                 | -0.5 to +3.6 | V    |

| Input voltage, 5 V buffer     | Vı     | $\begin{array}{l} 3.0 \; V \leq V_{\text{DD33}} \leq 3.6 \; V \\ V_{\text{I}} < V_{\text{DD33}} + 3.0 \; V \end{array}$ | -0.5 to +6.6 | V    |

| Input voltage, 3.3 V buffer   | Vı     | $\begin{array}{l} 3.0 \; V \leq V_{DD33} \leq 3.6 \; V \\ V_{I} < V_{DD33} + 1.0 \; V \end{array}$                      | -0.5 to +4.6 | V    |

| Input voltage, 2.5 V buffer   | Vı     | $\begin{array}{l} 2.3 \ V \leq V_{DD25} \leq 2.7 \ V \\ V_1 < V_{DD25} + 0.9 \ V \end{array}$                           | -0.5 to +3.6 | V    |

| Output voltage, 5 V buffer    | Vo     | $\begin{array}{l} 3.0 \; V \leq V_{\text{DD33}} \leq 3.6 \; V \\ V_0 < V_{\text{DD33}} + 3.0 \; V \end{array}$          | -0.5 to +6.6 | V    |

| Output voltage, 3.3 V buffer  | Vo     | $\begin{array}{l} 3.0 \; V \leq V_{\text{DD33}} \leq 3.6 \; V \\ V_0 < V_{\text{DD33}} + 1.0 \; V \end{array}$          | -0.5 to +4.6 | V    |

| Output voltage, 2.5 V buffer  | Vo     | $\begin{array}{l} 2.3 \ V \leq V_{DD25} \leq 2.7 \ V \\ V_0 < V_{DD25} + 0.9 \ V \end{array}$                           | -0.5 to +3.6 | V    |

| Output current, 5 V buffer    | lo     | IoL = 6 mA                                                                                                              | 20           | mA   |

| Output current, 3.3 V buffer  | lo     | IoL = 6 mA                                                                                                              | 20           | mA   |

|                               |        | lo∟ = 3 mA                                                                                                              | 10           | mA   |

| Operating ambient temperature | TA     |                                                                                                                         | 0 to +70     | °C   |

| Storage temperature           | Tstg   |                                                                                                                         | -65 to +150  | °C   |

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameters. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

The ratings and conditions indicated for DC characteristics and AC characteristics represent the quality assurance range during normal operation.

#### Two Power Supply Rails Limitation

The  $\mu$ PD720133 has two power supply rails (2.5 V, 3.3 V). The system will require the power supply rail to be stable at V<sub>DD</sub> level by a specified time. However, there are difference between the time of V<sub>DD25</sub> and V<sub>DD33</sub> becoming stable. The  $\mu$ PD720133 requires that V<sub>DD25</sub> becomes stable before V<sub>DD33</sub>. Also, it is necessary that V<sub>DD33</sub> be powered within 100 ms after V<sub>DD25</sub> became stable. In any case, the system must ensure that the absolute maximum ratings for V<sub>1</sub> / V<sub>0</sub> are not exceeded. System reset signaling must be asserted after the specified time of which both V<sub>DD25</sub> and V<sub>DD33</sub> become stable.

# **Recommended Operating Ranges**

| Parameter                      | Symbol | Condition             | Min. | Тур. | Max.              | Unit |

|--------------------------------|--------|-----------------------|------|------|-------------------|------|

| Operating voltage              | VDD33  | 3.3 V for VDD33 pins  | 3.0  | 3.3  | 3.6               | V    |

|                                | VDD25  | 2.5 V for VDD25 pins  | 2.3  | 2.5  | 2.7               | V    |

|                                | VDD25  | 2.5 V for AVDD25 pins | 2.3  | 2.5  | 2.7               | V    |

| High-level input voltage       | VIH    |                       |      |      |                   |      |

| 5.0 V high-level input voltage |        |                       | 2.0  |      | 5.5               | V    |

| 3.3 V high-level input voltage |        |                       | 2.0  |      | V <sub>DD33</sub> | V    |

| 2.5 V high-level input voltage |        |                       | 1.7  |      | V <sub>DD25</sub> | V    |

| Low-level input voltage        | VIL    |                       |      |      |                   |      |

| 5.0 V low-level input voltage  |        |                       | 0    |      | 0.8               | V    |

| 3.3 V low-level input voltage  |        |                       | 0    |      | 0.8               | V    |

| 2.5 V low-level input voltage  |        |                       | 0    |      | 0.7               | V    |

| Hysteresis voltage             | Vн     |                       |      |      |                   |      |

| 5 V hysteresis voltage         |        |                       | 0.3  |      | 1.5               | V    |

| 3.3 V hysteresis voltage       |        |                       | 0.2  |      | 1.0               | V    |

| Input rise time                | tri    |                       |      |      |                   |      |

| Normal buffer                  |        |                       | 0    |      | 200               | ns   |

| Schmitt buffer                 |        |                       | 0    |      | 10                | ms   |

| Input fall time                | tri    |                       |      |      |                   |      |

| Normal buffer                  |        |                       | 0    |      | 200               | ns   |

| Schmitt buffer                 |        |                       | 0    |      | 10                | ms   |

# DC Characteristics (VDD33 = 3.0 to 3.6 V, VDD25 = 2.3 to 2.7 V, TA = 0 to +70°C)

# **Control Pin Block**

| Parameter                       | Symbol              | Condition                | Min. | Max. | Unit |

|---------------------------------|---------------------|--------------------------|------|------|------|

| Off-state output current        | loz                 | Vo = Vdd33, Vdd25 or Vss |      | ±10  | μA   |

| Output short circuit current    | los <sup>Note</sup> |                          |      | -250 | mA   |

| Low-level output current        | lol                 |                          |      |      |      |

| 5.0 V low-level output current  |                     | Vol = 0.4 V              | 6.0  |      | mA   |

| 3.3 V low-level output current  |                     | Vol = 0.4 V              | 6.0  |      | mA   |

| 3.3 V low-level output current  |                     | Vol = 0.4 V              | 3.0  |      | mA   |

| High-level output current       | Іон                 |                          |      |      |      |

| 5.0 V high-level output current |                     | Vон = 2.4 V              | -2.0 |      | mA   |

| 3.3 V high-level output current |                     | Vон = 2.4 V              | -6.0 |      | mA   |

| 3.3 V high-level output current |                     | Vон = 2.4 V              | -3.0 |      | mA   |

| Input leakage current           | h                   |                          |      |      |      |

| 3.3 V buffer                    |                     | VI = VDD or VSS          |      | ±10  | μA   |

| 5.0 V buffer                    |                     | VI = VDD or VSS          |      | ±10  | μA   |

**Note** It is specified under the assumption that only one pin on the LSI is short-circuited for not more than one second.

# **USB Interface Block**

| Parameter                                                       | Symbol     | Conditions                                                                              | Min.  | Max.  | Unit |

|-----------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------|-------|-------|------|

| Serial Resistor between DP (DM) and RSDP (RSDM)                 | Rs         |                                                                                         | 38.61 | 39.39 | Ω    |

| Output pin impedance                                            | ZHSDRV     | Includes Rs resistor                                                                    | 40.5  | 49.5  | Ω    |

| Bus pull-up resistor on upstream facing port                    | Rpu        | $1.5 \text{ k}\Omega \pm 5\%$ consists of resistance of transistor and pull-up resistor | 1.485 | 1.515 | Ω    |

| Termination voltage for upstream facing port pull-up            | Vterm      |                                                                                         | 3.0   | 3.6   | V    |

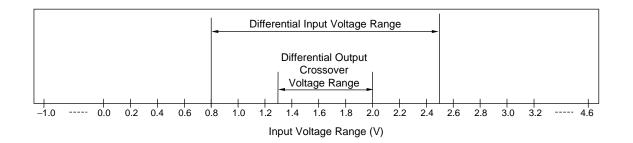

| Input Levels for Full-speed:                                    |            |                                                                                         |       |       |      |

| High-level input voltage (drive)                                | VIH        |                                                                                         | 2.0   |       | V    |

| High-level input voltage (floating)                             | VIHZ       |                                                                                         | 2.7   | 3.6   |      |

| Low-level input voltage                                         | VIL        |                                                                                         |       | 0.8   | V    |

| Differential input sensitivity                                  | VDI        | (D+) – (D–)                                                                             | 0.2   |       | V    |

| Differential common mode range                                  | Vсм        | Includes VDI range                                                                      | 0.8   | 2.5   | V    |

| Output Levels for Full-speed:                                   |            |                                                                                         |       |       |      |

| High-level output voltage                                       | Vон        | R∟ of 14.25 kΩ to Vss                                                                   | 2.8   | 3.6   | V    |

| Low-level output voltage                                        | Vol        | R∟ of 1.425 kΩ to 3.6 V                                                                 | 0.0   | 0.3   | V    |

| SE1                                                             | Vose1      |                                                                                         | 0.8   |       | V    |

| Output signal crossover point voltage                           | VCRS       |                                                                                         | 1.3   | 2.0   | V    |

| Input Levels for High-speed:                                    |            |                                                                                         |       |       |      |

| High-speed squelch detection threshold (differential signal)    | VHSSQ      |                                                                                         | 100   | 150   | mV   |

| High-speed disconnect detection threshold (differential signal) | VHSDSC     |                                                                                         | 525   | 625   | mV   |

| High-speed data signaling common mode voltage range             | Vнscм      |                                                                                         | -50   | +500  | mV   |

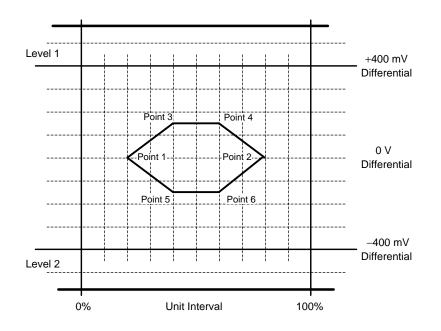

| High-speed differential input signaling level                   | See Figure | <b>3-4</b> .                                                                            |       |       |      |

| Output Levels for High-speed:                                   |            |                                                                                         |       |       |      |

| High-speed idle state                                           | VHSOI      |                                                                                         | -10.0 | +10.0 | mV   |

| High-speed data signaling high                                  | Vнsoн      |                                                                                         | 360   | 440   | mV   |

| High-speed data signaling low                                   | VHSOL      |                                                                                         | -10.0 | +10.0 | mV   |

| Chirp J level (differential signal)                             | VCHIRPJ    |                                                                                         | 700   | 1100  | mV   |

| Chirp K level (differential signal)                             | VCHIRPK    |                                                                                         | -900  | -500  | mV   |

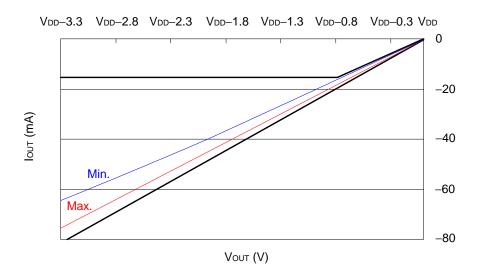

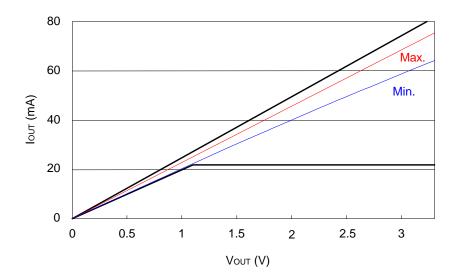

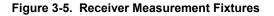

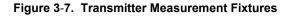

Figure 3-3. Full-speed Buffer VoL/IoL Characteristics for High-speed Capable Transceiver

Figure 3-4. Receiver Sensitivity for Transceiver at DP/DM

#### **Pin Capacitance**

| Parameter          | Symbol | Condition                                    | Min. | Max. | Unit |

|--------------------|--------|----------------------------------------------|------|------|------|

| Input capacitance  | Cin    | V <sub>DD</sub> = 0 V, T <sub>A</sub> = 25°C | 4    | 6    | pF   |

| Output capacitance | Соит   | fc = 1 MHz                                   | 4    | 6    | pF   |

| I/O capacitance    | Сю     | Unmeasured pins returned to 0 V              | 4    | 6    | pF   |

# ★ Power Consumption

# (1) The power consumption when device works as bus-powered mode

| Symbol     | Condition                                              |       | Max.  |                    | Unit |

|------------|--------------------------------------------------------|-------|-------|--------------------|------|

|            |                                                        | Vdd25 | Vdd33 | AV <sub>DD25</sub> |      |

| Penum-bus  | The power consumption during device unconfigured stage |       |       |                    |      |

|            | High-speed operating                                   | 55    | 3     | 10                 | mA   |

|            | Full-speed operating                                   | 25    | 4     | 10                 | mA   |

| Pw-bus     | The power consumption during device configured stage   |       |       |                    |      |

|            | High-speed operating                                   | 100   | 22    | 10                 | mA   |

|            | Full-speed operating                                   | 75    | 13    | 10                 | mA   |

| Pw_spd-bus | The power consumption under suspend state              | 15    | 235   | 5                  | μA   |

# (2) The power consumption when device works as self-powered mode

| Symbol      | Condition                                              |       | Max.  |                    | Unit |

|-------------|--------------------------------------------------------|-------|-------|--------------------|------|

|             |                                                        | Vdd25 | Vdd33 | AV <sub>DD25</sub> |      |

| Penum-self  | The power consumption during device unconfigured stage |       |       |                    |      |

|             | High-speed operating                                   | 90    | 5     | 10                 | mA   |

|             | Full-speed operating                                   | 60    | 5     | 10                 | mA   |

| Pw-self     | The power consumption during device configured stage   |       |       |                    |      |

|             | High-speed operating                                   | 100   | 25    | 10                 | mA   |

|             | Full-speed operating                                   | 75    | 13    | 10                 | mA   |

| Pw_spd-self | The power consumption under suspend state              | 50    | 500   | 15                 | μA   |

| Pw_unp      | The power consumption under unplug state               | 50    | 500   | 15                 | μA   |

| Рw_сом      | The power consumption under combo mode                 | 50    | 500   | 15                 | μA   |

|             | The device is releasing the IDE bus.                   |       |       |                    |      |

# AC Characteristics (VDD33 = 3.0 to 3.6 V, VDD25 = 2.3 to 2.7 V, TA = 0 to +70°C)

# System Clock Ratings

| Parameter        | Symbol        | Condition        | Min.     | Тур. | Max.     | Unit |

|------------------|---------------|------------------|----------|------|----------|------|

| Clock frequency  | fськ          | X'tal            | –500 ppm | 30   | +500 ppm | MHz  |

|                  |               | Oscillator block | –500 ppm | 30   | +500 ppm | MHz  |

| Clock duty cycle | <b>t</b> duty |                  | 45       | 50   | 55       | %    |

**Remarks 1.** Recommended accuracy of clock frequency is  $\pm$  100 ppm.

2. Required accuracy of X'tal or Oscillator block is including initial frequency accuracy, the spread of X'tal capacitor loading, supply voltage, temperature, and aging, etc.

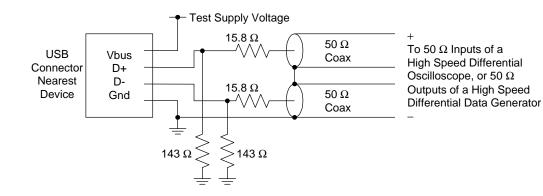

# System Reset signaling

| Parameter         | Symbol       | Conditions | Min. | Max. | Unit |

|-------------------|--------------|------------|------|------|------|

| Reset active time | <b>t</b> rst |            | 2    |      | μs   |

# **USB Interface Block**

|                                                                  |                                      |                          |              |              | (1/2)    |

|------------------------------------------------------------------|--------------------------------------|--------------------------|--------------|--------------|----------|

| Parameter                                                        | Symbol                               | Conditions               | Min.         | Max.         | Unit     |

| Full-speed Source Electrical Characteristic                      | cs                                   |                          |              |              |          |

| Rise time (10% - 90%)                                            | tfr                                  | CL = 50 pF,<br>Rs = 36 Ω | 4            | 20           | ns       |

| Fall time (90% - 10%)                                            | t⊧⊧                                  | CL = 50 pF,<br>Rs = 36 Ω | 4            | 20           | ns       |

| Differential rise and fall time matching                         | <b>t</b> FRFM                        | (tfr/tff)                | 90           | 111.11       | %        |

| Full-speed data rate for device which are<br>high-speed capable  | <b>t</b> fdraths                     | Average bit rate         | 11.9940      | 12.0060      | Mbps     |

| Frame interval                                                   | <b>t</b> FRAME                       |                          | 0.9995       | 1.0005       | ms       |

| Consecutive frame interval jitter                                | <b>t</b> RFI                         | No clock adjustment      |              | 42           | ns       |

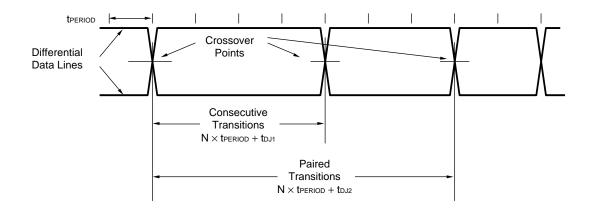

| Source jitter total (including frequency tolerance):             |                                      |                          |              |              |          |

| To next transition<br>For paired transitions                     | t <sub>DJ1</sub><br>t <sub>DJ2</sub> |                          | -3.5<br>-4.0 | +3.5<br>+4.0 | ns<br>ns |

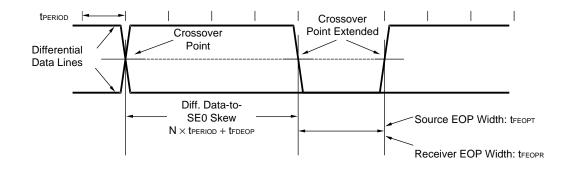

| Source jitter for differential transition to SE0 transition      | <b>t</b> fdeop                       |                          | -2           | +5           | ns       |

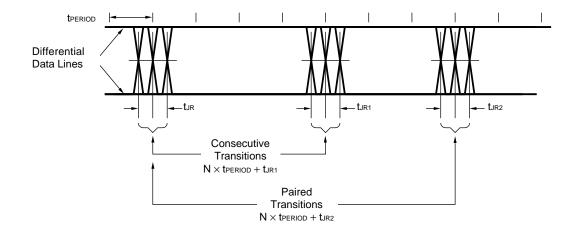

| Receiver jitter:<br>To next transition<br>For paired transitions | tjr1<br>tjr2                         |                          | -18.5<br>-9  | +18.5<br>+9  | ns<br>ns |

| Source SE0 interval of EOP                                       | <b>t</b> feopt                       |                          | 160          | 175          | ns       |

| Receiver SE0 interval of EOP                                     | <b>t</b> feopr                       |                          | 82           |              | ns       |

| Width of SE0 interval during differential transition             | tfst                                 |                          |              | 14           | ns       |

|                                                                                                              |                 |              |          |                 | (2/2         |

|--------------------------------------------------------------------------------------------------------------|-----------------|--------------|----------|-----------------|--------------|

| Parameter                                                                                                    | Symbol          | Conditions   | Min.     | Max.            | Unit         |

| High-speed Source Electrical Characterist                                                                    | ics             |              |          |                 |              |

| Rise time (10% - 90%)                                                                                        | thsr            |              | 500      |                 | ps           |

| Fall time (90% - 10%)                                                                                        | thsp            |              | 500      |                 | ps           |

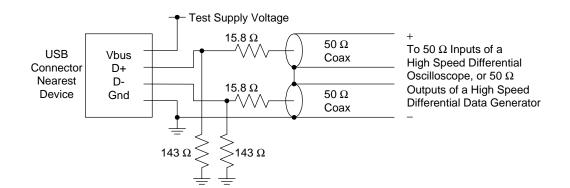

| Driver waveform                                                                                              | See Figure      | 3-6.         |          |                 |              |

| High-speed data rate                                                                                         | <b>t</b> HSDRAT |              | 479.760  | 480.240         | Mbps         |

| Microframe interval                                                                                          | <b>t</b> HSFRAM |              | 124.9375 | 125.0625        | μs           |

| Consecutive microframe interval difference                                                                   | thsrfi          |              |          | 4<br>high-speed | Bit<br>times |

| Data source jitter                                                                                           | See Figure      | <b>3-6</b> . |          |                 |              |

| Receiver jitter tolerance                                                                                    | See Figure      | <b>3-4</b> . |          |                 |              |

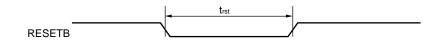

| Device Event Timings                                                                                         |                 |              |          |                 |              |

| Time from internal power good to device<br>pulling D+ beyond V <sub>IHZ</sub> (min.) (signaling<br>attached) | <b>t</b> sigatt |              |          | 100             | ms           |

| Debounce interval provided by USB system software after attach                                               | <b>t</b> attdb  |              |          | 100             | ms           |

| Inter-packet delay for full-speed                                                                            | tipd            |              | 2        |                 | Bit<br>times |

| Inter-packet delay for device response<br>w/detachable cable for full-speed                                  | trspipd1        |              |          | 6.5             | Bit<br>times |

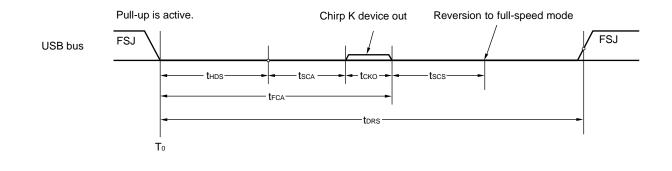

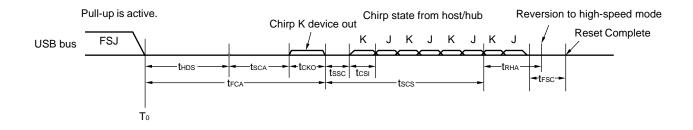

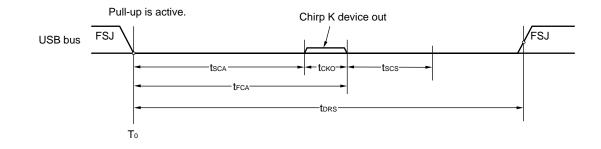

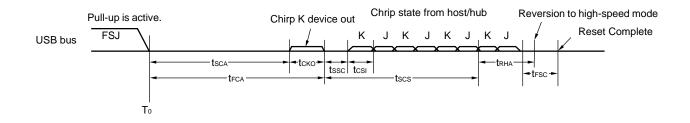

| High-speed detection start time from<br>suspend                                                              | <b>t</b> sca    |              | 2.5      |                 | μs           |

| Sample time for suspend vs reset                                                                             | tcsr            |              | 100      | 875             | μs           |

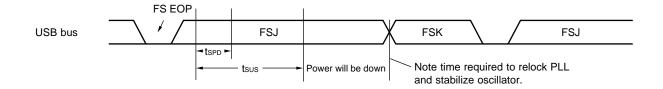

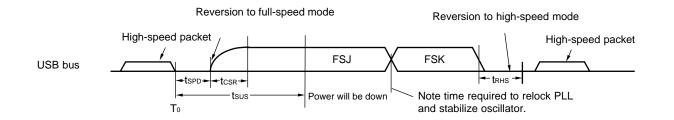

| Time to detect bus suspend state                                                                             | <b>t</b> spd    |              | 3.000    | 3.125           | ms           |

| Power down under suspend                                                                                     | tsus            |              |          | 10              | ms           |

| Reversion time from suspend to high-speed                                                                    | tкнs            |              |          | 1.333           | μs           |

| Drive Chirp K width                                                                                          | tско            |              | 1        |                 | ms           |

| Finish Chirp K assertion                                                                                     | <b>t</b> FCA    |              |          | 7               | ms           |

| Start sequencing Chirp K-J-K-J-K-J                                                                           | tssc            |              |          | 100             | μs           |

| Finish sequencing Chirp K-J                                                                                  | <b>t</b> FSC    |              | -500     | -100            | μs           |

| Detect sequencing Chirp K-J width                                                                            | tcsi            |              | 2.5      |                 | μs           |

| Sample time for sequencing Chirp                                                                             | tscs            |              | 1        | 2.5             | ms           |

| Reversion time to high-speed                                                                                 | <b>t</b> RHA    |              |          | 500             | μs           |

| High-speed detection start time                                                                              | tHDS            |              | 2.5      | 3000            | μs           |

| Reset completed time                                                                                         | <b>t</b> DRS    |              | 10       |                 | ms           |

# IDE Interface Block

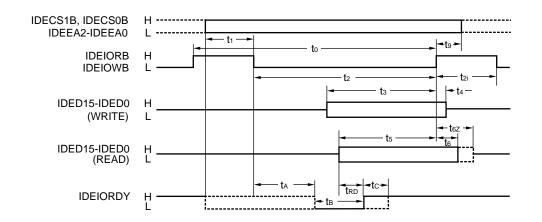

# PIO mode

| Parameter                               | Symbol          | Mode 0 | Mode 1 | Mode 2 | Mode 3 | Mode 4 | Unit |

|-----------------------------------------|-----------------|--------|--------|--------|--------|--------|------|

| Cycle time (min.)                       | to              | 600    | 383    | 240    | 180    | 120    | ns   |

| Address setup time (min.)               | t1              | 70     | 50     | 30     | 30     | 25     | ns   |

| 16 bits DIOR/DIOW pulse width (min.)    | t2              | 165    | 125    | 100    | 80     | 70     | ns   |

| 8 bits DIOR/DIOW pulse width (min.)     |                 | 290    | 290    | 290    | 80     | 70     | ns   |

| DIOR/DIOW recovery time (min.)          | t2i             | _      | -      |        | 70     | 25     | ns   |

| DIOW data setup time (min.)             | tз              | 60     | 45     | 30     | 30     | 20     | ns   |

| DIOW data hold time (min.)              | t4              | 30     | 20     | 15     | 10     | 10     | ns   |

| DIOR data setup time (min.)             | t5              | 50     | 35     | 20     | 20     | 20     | ns   |

| DIOR data hold time (min.)              | t6              | 5      | 5      | 5      | 5      | 5      | ns   |

| DIOR 3-state delay time (max.)          | t <sub>6Z</sub> | 30     | 30     | 30     | 30     | 30     | ns   |

| Address hold time (min.)                | to              | 20     | 15     | 10     | 10     | 10     | ns   |

| IORDY read data valid time (min.) Note  | <b>t</b> RD     | 0      | 0      | 0      | 0      | 0      | ns   |

| IORDY setup time (min.) Note            | tA              | 35     | 35     | 35     | 35     | 35     | ns   |

| IORDY pulse width (max.) Note           | tв              | 1250   | 1250   | 1250   | 1250   | 1250   | ns   |

| IORDY Inactive to Hi-Z time (max.) Note | tc              | 5      | 5      | 5      | 5      | 5      | ns   |

**Note** IORDY is an option in mode 0 - 2. IORDY is essential in modes 3 and 4.

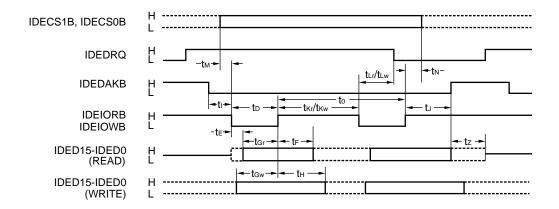

# Multi Word DMA mode

| Parameter                       | Symbol          | Mode 0 | Mode 1 | Mode 2 | Unit |

|---------------------------------|-----------------|--------|--------|--------|------|

| Cycle time (min.)               | to              | 480    | 150    | 120    | ns   |

| DIOR/DIOW pulse width (min.)    | t⊳              | 215    | 80     | 70     | ns   |

| DIOR data access time (max.)    | t⊨              | 150    | 60     | 50     | ns   |

| DIOR data hold time (min.)      | t⊧              | 5      | 5      | 5      | ns   |

| DIOR data setup time (min.)     | t <sub>Gr</sub> | 100    | 30     | 20     | ns   |

| DIOW data setup time (min.)     | t <sub>Gw</sub> | 100    | 30     | 20     | ns   |

| DIOW data hold time (min.)      | t⊦              | 20     | 15     | 10     | ns   |

| DMACK setup time (min.)         | tı              | 0      | 0      | 0      | ns   |

| DMACK hold time (min.)          | tu              | 20     | 5      | 5      | ns   |

| DIOR negate pulse width (min.)  | <b>t</b> ĸr     | 50     | 50     | 25     | ns   |

| DIOW negate pulse width (min.)  | tкw             | 215    | 50     | 25     | ns   |

| DIOR-DMARQ delay time (max.)    | t∟r             | 120    | 40     | 35     | ns   |

| DIOW-DMARQ delay time (max.)    | t∟w             | 40     | 40     | 35     | ns   |

| DMACK 3-state delay time (max.) | tz              | 20     | 25     | 25     | ns   |

| CS setup time (min.)            | tм              | 50     | 30     | 25     | ns   |

| CS hold time (min.)             | t⊳              | 15     | 10     | 10     | ns   |

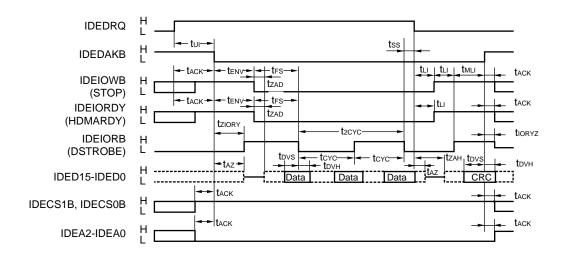

# Ultra DMA mode

| Parameter                                   | Symbol Mo    |      | ode 0 Mode 1 |      | Mode 2 |      | Mode 3 |      | Mode 4 |      | Unit |    |

|---------------------------------------------|--------------|------|--------------|------|--------|------|--------|------|--------|------|------|----|

|                                             |              | Min. | Max.         | Min. | Max.   | Min. | Max.   | Min. | Max.   | Min. | Max. |    |

| Average cycle time for 2 cycles             | t2CYC        | 240  | -            | 160  | -      | 120  | -      | 90   | -      | 60   | -    | ns |

| Minimum cycle time for 2 cycles             | t2CYC        | 235  | -            | 156  | -      | 117  | -      | 86   | -      | 57   | -    | ns |

| Cycle time for 1 cycle                      | tcyc         | 114  | -            | 75   | -      | 55   | -      | 39   | -      | 25   | -    | ns |

| Data setup time on receive side             | tos          | 15   | -            | 10   | -      | 7    | -      | 7    | -      | 5    | -    | ns |

| Data hold time on receive side              | tон          | 5    | -            | 5    | -      | 5    | -      | 5    | -      | 5    | -    | ns |

| Data setup time on transmit side            | tovs         | 70   | -            | 48   | -      | 34   | -      | 20   | -      | 6    | -    | ns |

| Data hold time on transmit side             | tovн         | 6    | -            | 6    | -      | 6    | -      | 6    | -      | 6    | -    | ns |

| First STROBE time                           | t⊧s          | 0    | 230          | 0    | 200    | 0    | 170    | 0    | 130    | 0    | 120  | ns |

| Interlock time with limitation              | t⊔           | 0    | 150          | 0    | 150    | 0    | 150    | 0    | 100    | 0    | 100  | ns |

| Minimum interlock time                      | tmli         | 20   | -            | 20   | -      | 20   | -      | 20   | -      | 20   | -    | ns |

| Interlock time without limitation           | tui          | 0    | -            | 0    | -      | 0    | -      | 0    | -      | 0    | -    | ns |

| Output release time                         | taz          | -    | 10           | -    | 10     | -    | 10     | -    | 10     | -    | 10   | ns |

| Output delay time                           | tzaн         | 20   | -            | 20   | -      | 20   | -      | 20   | -      | 20   | -    | ns |

| Output stabilization time<br>(from release) | tzad         | 0    | -            | 0    | -      | 0    | -      | 0    | -      | 0    | -    | ns |

| Envelope time                               | <b>t</b> env | 20   | 70           | 20   | 70     | 20   | 70     | 20   | 55     | 20   | 55   | ns |

| STROBE DMARDY delay time                    | tsr          | -    | 50           | -    | 30     | -    | 20     | -    | NA     | -    | NA   | ns |

| Last STROBE time                            | trfs         | -    | 75           | -    | 60     | -    | 50     | -    | 60     | -    | 60   | ns |

| Pause time                                  | trp          | 160  | -            | 125  | -      | 100  | -      | 100  | -      | 100  | -    | ns |

| IORDY pull-up time                          | tioryz       | -    | 20           | -    | 20     | -    | 20     | -    | 20     | -    | 20   | ns |

| IORDY wait time                             | tziory       | 0    | -            | 0    | -      | 0    | -      | 0    | -      | 0    | -    | ns |

| DMACK setup/hold time                       | tаск         | 20   | -            | 20   | -      | 20   | -      | 20   | -      | 20   | -    | ns |

| STROBE STOP time                            | tss          | 50   | -            | 50   | -      | 50   | -      | 50   | -      | 50   | -    | ns |

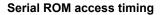

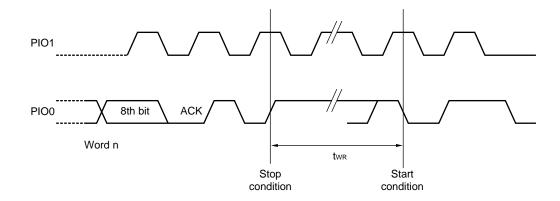

# Serial ROM interface Block

| Parameter                                                     | Symbol       | Conditions | Min. | Max. | Unit |

|---------------------------------------------------------------|--------------|------------|------|------|------|

| Clock frequency                                               | tsc∟         |            |      | 100  | KHz  |

| Clock pulse width low                                         | <b>t</b> LOW |            | 4.7  |      | μs   |

| Clock pulse width high                                        | tніgн        |            | 4.0  |      | μs   |

| Clock Low to data valid                                       | taa          |            | 100  | 4500 | ns   |

| Start hold time                                               | thd.sta      |            | 4.0  |      | μs   |

| Start setup time                                              | tsu.sta      |            | 4.7  |      | μs   |

| Data in hold time                                             | thd.dat      |            | 0    |      | ns   |

| Data in setup time                                            | tsu.dat      |            | 0.2  |      | μs   |

| Data out hold time                                            | tон          |            | 50   |      | ns   |

| Stop setup time                                               | tsu.sto      |            | 4.7  |      | μs   |

| Time the bus must be free before a new transmission can start | tbuf         |            | 10   |      | μs   |

| Write cycle time                                              | twr          |            | 10   |      | ms   |

Figure 3-6. Transmit Waveform for Transceiver at DP/DM

#### **Timing Diagram**

System reset timing

**Remark** After chip RESET, this chip reads the serial ROM first. Do not reset while the serial ROM is read. The read operation is completed in the period, which is calculated with the following expression.

$5 + 0.1197 \times \text{bytes} \text{ (serial ROM size)} + 0.5678 \text{ (ms)}$

Example In the case of 512 bytes: 66.855 ms, in the case of 8 Kbytes: 986.15 ms

# USB power-on and connection events

#### USB differential data jitter for full-speed

# USB differential-to-EOP transition skew and EOP width for full-speed

#### USB receiver jitter tolerance for full-speed

# USB connection sequence on full-speed system bus

# USB connection sequence on high-speed system bus

# USB reset sequence from suspend state on full-speed system bus

## USB reset sequence from suspend state on high-speed system bus

#### USB suspend and resume on full-speed system bus

#### USB suspend and resume on high-speed system bus

# **IDE PIO mode timing**

#### IDE multi word DMA mode timing

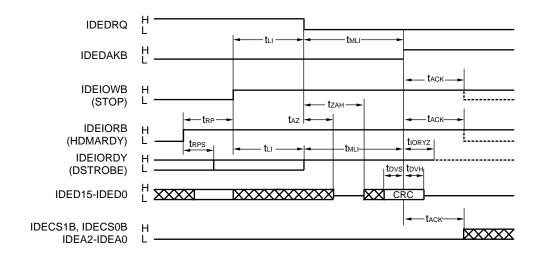

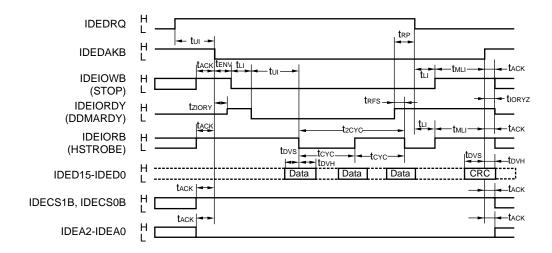

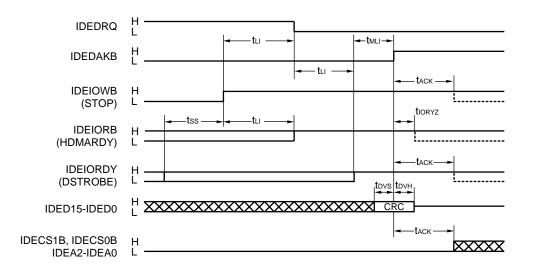

#### IDE ultra DMA mode data-in timing

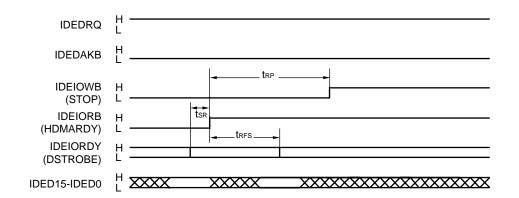

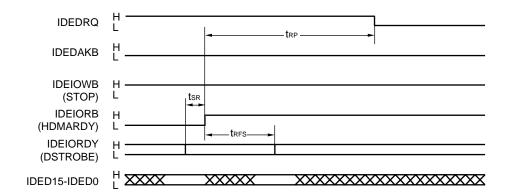

#### IDE ultra DMA mode data-in stop timing

# IDE ultra DMA mode data-in end timing

#### IDE ultra DMA mode data-out timing

NEC

# IDE ultra DMA mode data-out stop timing

# IDE ultra DMA mode data-out end timing

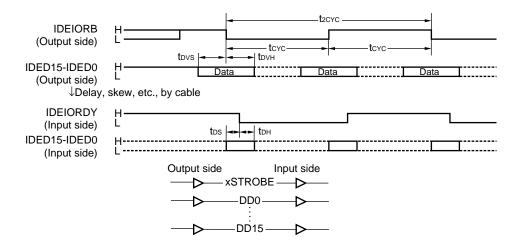

#### IDE ultra DMA mode data skew timing

#### Serial ROM write cycle timing

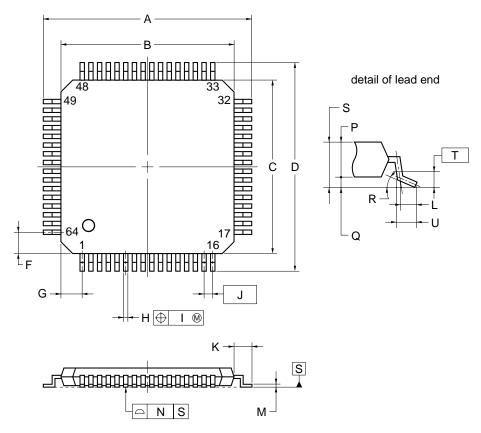

# 4. PACKAGE DRAWING

- μPD720133GB-YEU-A

- µPD720133GB-YEU-Y

# 64-PIN PLASTIC TQFP (FINE PITCH) (10x10)

#### NOTE

Each lead centerline is located within 0.08 mm of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS                          |

|------|--------------------------------------|

| Α    | 12.0±0.2                             |

| В    | 10.0±0.2                             |

| С    | 10.0±0.2                             |

| D    | 12.0±0.2                             |

| F    | 1.25                                 |

| G    | 1.25                                 |

| Н    | $0.22{\pm}0.05$                      |

| I    | 0.08                                 |

| J    | 0.5 (T.P.)                           |

| К    | 1.0±0.2                              |

| L    | 0.5                                  |

| М    | $0.17\substack{+0.03 \\ -0.07}$      |

| N    | 0.08                                 |

| Р    | 1.0                                  |

| Q    | 0.1±0.05                             |

| R    | $3^{\circ + 4^{\circ}}_{-3^{\circ}}$ |

| S    | 1.10±0.10                            |

| Т    | 0.25                                 |

| U    | 0.6±0.15                             |

|      | S64GB-50-YEU-1                       |

# 5. RECOMMENDED SOLDERING CONDITIONS

The  $\mu$ PD720133 should be soldered and mounted under the following recommended conditions.

For soldering methods and conditions other than those recommended below, please contact your NEC Electronics sales representative.

For technical information, please refer to the following website.

Semiconductor Device Mount Manual (http://www.necel.com/pkg/en/mount/index.html)

# **\mu**PD720133GB-YEU-A / $\mu$ PD720133GB-YEU-Y:64-pin plastic TQFP (Fine pitch) (10 × 10)

| Soldering<br>Method | Soldering Conditions                                                                                                                                 |                                                                                                                                                                           |            |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Infrared reflow     | Package peak temperature<br>Time at peak temperature<br>Time at 220°C or higher<br>Preheat time<br>(160 to 180°C)<br>Maximum count<br>Exposure limit | : 260°C<br>: within 10 seconds<br>: within 60 seconds<br>: 60 to 120 seconds<br>: 3 times or less<br>: 3 days <sup>Note</sup> (after that, prebake at 125°C for 10 hours) | IR60-103-3 |  |  |  |

| Partial heating     | g Pin temperature: 300°C max., Time: 3 seconds or less (per pin row)                                                                                 |                                                                                                                                                                           |            |  |  |  |

Note After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.

[MEMO]

38

# NOTES FOR CMOS DEVICES —

#### **1** VOLTAGE APPLICATION WAVEFORM AT INPUT PIN