# DS2141A T1 Controller

#### www.dalsemi.com

# **FEATURES**

- DS1/ISDN-PRI framing transceiver

- Frames to D4, ESF, and SLC-96 formats

- Parallel control port

- Onboard, dual two-frame elastic store slip buffers

- Extracts and inserts robbed-bit signaling

- Programmable output clocks

- Onboard FDL support circuitry

- 5V supply; low-power CMOS

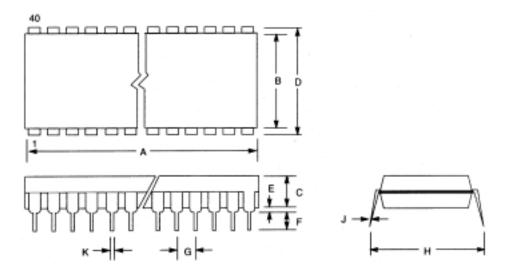

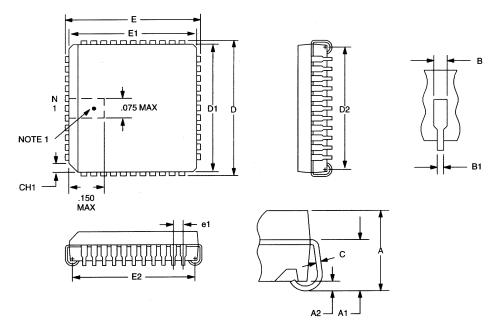

- Available in 40-pin DIP and 44-pin PLCC (DS2141Q)

- Compatible with DS2186 Transmit Line Interface, DS2187 Receive Line Interface, DS2188 Jitter Attenuator, DS2290 T1 Isolation Stik, and DS2291 T1 Long Loop Stik

# **PIN ASSIGNMENT**

| TCLK   TSER   TCHCLK   TPOS   TNEG   AD0   AD1   AD2   AD3   AD4   AD5   AD6   BTS   CS   ALE(AS)   WR(R/W)   RLINK | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | 39 39   38 38   37 36   36 35   34 33   32 31   30 29   28 32   27 26   26 24   23 24 | VDD<br>TSYNC<br>TLINK<br>TLCLK<br>INT1<br>INT2<br>RLOS/LOTC<br>TCHBLK<br>RCHBLK<br>LI CS<br>LI CLK<br>LI SDI<br>SYSCLK<br>RNEG<br>RSYNC<br>RSER<br>RSYNC<br>RSER<br>RCHCLK<br>RCLK |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vss 🗆                                                                                                               | 20                                                                                                    | 21                                                                                    | RLCLK                                                                                                                                                                              |

| 40-Pi                                                                                                               | in DIP (6                                                                                             |                                                                                       | )                                                                                                                                                                                  |

| AD0 7 6 5 4 3<br>AD1 2 8<br>AD2 9<br>AD3 10<br>AD4 11                                                               |                                                                                                       |                                                                                       | RLOS/LOTC<br>RLOS/LOTC<br>RCHBLK<br>RCHBLK<br>LLCS<br>LLCLK<br>LLCLK<br>RNC<br>RNC<br>RNC<br>RNEG<br>RNEG                                                                          |

#### DESCRIPTION

The DS2141A is a comprehensive, software-driven T1 framer. It is meant to act as a slave or coprocessor to a microcontroller or microprocessor. Quick access via the parallel control port allows a single micro to handle many T1 lines. The DS2141A is very flexible and can be configured into numerous orientations via software. The software orientation of the device allows the user to modify their design to conform to future T1 specification changes. The controller contains a set of 62 8-bit internal registers which the user can access. These internal registers are used to configure the device and obtain information from the T1

1 of 39

link. The device fully meets all of the latest T1 specifications including ANSI T1.403-1989, AT&T TR 62411 (12-90), and CCITT G.704 and G.706.

# **1.0 INTRODUCTION**

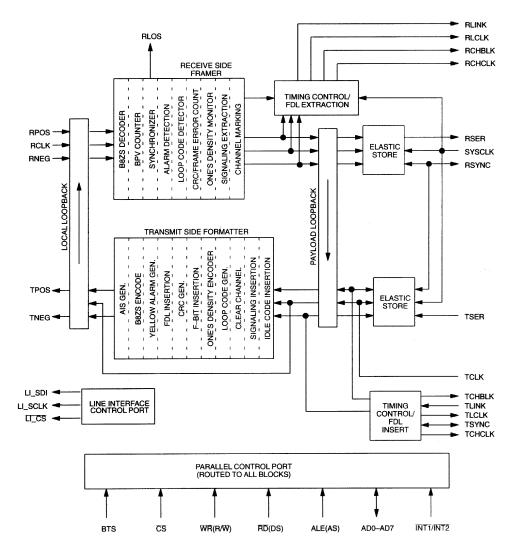

The DS2141A T1 Controller has four main sections: the receive side, the transmit side, the line interface controller, and the parallel control port. See the block diagram below. On the receive side, the device will clock in the serial T1 stream via the RPOS and RNEG pins. The synchronizer will locate the frame and multiframe patterns and establish their respective positions. This information will be used by the rest of the receive side circuitry.

The DS2141A is an "off-line" framer, which means that all of the T1 serial stream that goes into the device will come out of it unchanged. Once the T1 data has been framed to, the robbed-bit signaling data and FDL can be extracted. The 2-frame elastic stores can either be enabled or bypassed.

The transmit side clocks in the unframed T1 stream at TSER and adds in the framing pattern, the robbedbit signaling, and the FDL. The line interface control port will update line interface devices that contain a serial port. The parallel control port contains a multiplexed address and data structure which can be connected to either a microcontroller or microprocessor.

# DS2141A BLOCK DIAGRAM

# **DS2141A FEATURES**

- Parallel control port

- Large error counters

- Onboard dual 2-frame elastic store

- FDL support circuitry

- Robbed-bit signaling extraction and insertion

- Programmable output clocks

- Fully independent transmit and receive sections

- Frame sync generation

- Error-tolerant yellow and blue alarm detection

- Output pin test mode

- Payload loopback capability

- SLC-96 support

- Remote loop up/down code detection

- Loss of transmit clock detection

- Loss of receive clock detection

- 1's density violation detection

|      | -SCRIPTION                                                   | Table | 1                                                                                                      |

|------|--------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------|

| PIN  | SYMBOL                                                       | TYPE  | DESCRIPTION                                                                                            |

| 1    | TCLK                                                         | Ι     | Transmit Clock. 1.544 MHz primary clock.                                                               |

| 2    | TSER                                                         | Ι     | Transmit Serial Data. Transmit NRZ serial data, sampled on the                                         |

|      |                                                              |       | falling edge of TCLK.                                                                                  |

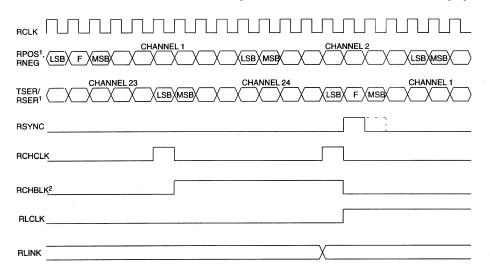

| 3    | TCHCLK                                                       | 0     | Transmit Channel Clock. 192 kHz clock which pulses high during                                         |

|      |                                                              |       | the LSB of each channel. Useful for parallel-to-serial conversion of                                   |

|      |                                                              |       | channel data, locating robbed-bit signaling bits, and for blocking                                     |

|      |                                                              |       | clocks in DDS applications. See Section 13 for timing details.                                         |

| 4    | TPOS                                                         | 0     | Transmit Bipolar Data. Updated on rising edge of TCLK.                                                 |

| 5    | TNEG                                                         |       |                                                                                                        |

| 6-13 | AD0-AD7                                                      | I/O   | Address/Data Bus. An 8-bit multiplexed address/data bus.                                               |

| 14   | BTS                                                          | Ι     | Bus Type Select. Strap high to select Motorola bus timing; strap                                       |

|      |                                                              |       | low to select Intel bus timing. This pin controls the function of                                      |

|      |                                                              |       | $\overline{\text{RD}}$ (DS), ALE(AS), and $\overline{\text{WR}}$ (R/W) pins. If BTS=1, then these pins |

|      |                                                              |       | assume the function listed in parentheses ().                                                          |

| 15   | $\overline{RD}(DS)$                                          | Ι     | Read Input (Data Strobe).                                                                              |

| 16   | CS                                                           | Ι     | Chip Select. Must be low to read or write the port.                                                    |

| 17   | ALE(AS)                                                      | Ι     | Address Latch Enable (Address Strobe). A positive-going edge                                           |

|      |                                                              |       | serves to demultiplex the bus.                                                                         |

| 18   | $\overline{\mathrm{WR}}  (\mathrm{R}/\overline{\mathrm{W}})$ | Ι     | Write Input (Read/Write).                                                                              |

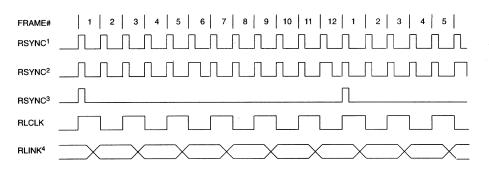

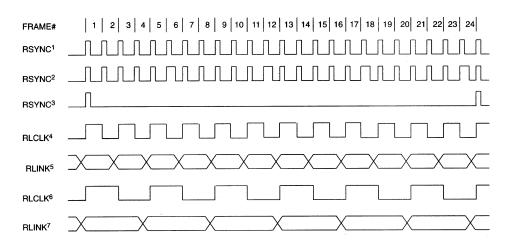

| 19   | RLINK                                                        | 0     | Receive Link Data. Updated with either FDL data (ESF) or Fs-bits                                       |

|      |                                                              |       | (D4) or Z-bits (ZBTSI) one RCLK before the start of a frame. See                                       |

|      |                                                              |       | Section 13 for timing details.                                                                         |

| 20   | VSS                                                          | -     | Signal Ground. 0.0 volts.                                                                              |

| 21   | RLCLK                                                        | 0     | Receive Link Clock. 192 kHz clock which pulses high during the                                         |

|      |                                                              |       | LSB of each channel. Useful for parallel-to-serial conversion of                                       |

|      |                                                              |       | channel data, locating robbed-bit signaling bits, and for blocking                                     |

|      |                                                              |       | clocks in DDS applications. See Section 13 for timing details.                                         |

| 22   | RCLK                                                         | Ι     | Receive Clock. 1.544 MHz primary clock.                                                                |

### **PIN DESCRIPTION** Table 1

| PIN      | SYMBOL           | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

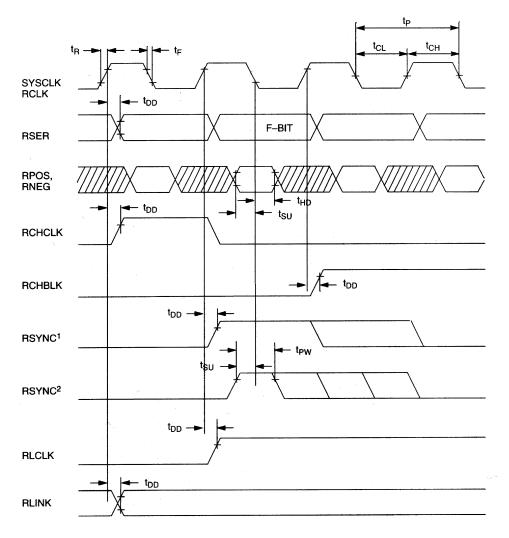

| 23       | RCHCLK           | 0    | <b>Receive Channel Clock.</b> 192 kHz clock which pulses high during the LSB of each channel. Useful for parallel-to-serial conversion of channel data, locating robbed-bit signaling bits, and for blocking clocks in DDS applications. See Section 13 for timing details.                                                                                                                                                                                                   |

| 24       | RSER             | 0    | <b>Receive Serial Data.</b> Received NRZ serial data; updated on rising edges of RCLK.                                                                                                                                                                                                                                                                                                                                                                                        |

| 25       | RSYNC            | I/O  | <b>Receive Sync.</b> An extracted pulse, one RCLK wide, is output at this pin which identifies either frame (RCR2.4=0) or multiframe boundaries (RCR2.4=1). If set to output frame boundaries, then via RCR2.5, RSYNC can also be set to output double-wide pulses on signaling frames. If the elastic store is enabled via the CCR1.2, then this pin can be enabled to be an input via RCR2.3 at which a frame boundary pulse is applied. See Section 13 for timing details. |

| 26<br>27 | RPOS<br>RNEG     | Ι    | <b>Receive Bipolar Data Inputs.</b> Sampled on falling edge of RCLK.<br>Tie together to receive NRZ data and disable bipolar violation<br>monitoring circuitry.                                                                                                                                                                                                                                                                                                               |

| 28       | SYSCLK           | Ι    | <b>System Clock.</b> 1.544 MHz or 2.048 MHz clock. Only used when the elastic store function is enabled via the CCR. Should be tied low in applications that do not use the elastic store.                                                                                                                                                                                                                                                                                    |

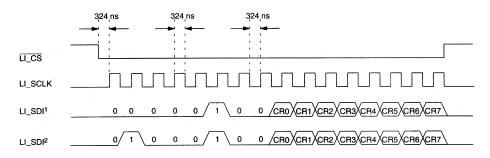

| 29       | LI_SDI           | 0    | <b>Serial Port Data for the Line Interface.</b> Connects directly to the SDI input pin on the line interface.                                                                                                                                                                                                                                                                                                                                                                 |

| 30       | LI_CLK           | 0    | <b>Serial Port Clock for the Line Interface.</b> Connects directly to the SCLK input pin on the line interface.                                                                                                                                                                                                                                                                                                                                                               |

| 31       | LI_CS            | 0    | Serial Port Chip Select for the Line Interface. Connects directly to the $\overline{CS}$ input pin on the line interface.                                                                                                                                                                                                                                                                                                                                                     |

| 32<br>33 | RCHBLK<br>TCHBLK | Ο    | <b>Receive/Transmit Channel Block.</b> A user-programmable output that can be forced high or low during any of the 24 T1 channels. Useful for blocking clocks to a serial UART or LAPD controller in application where not all T1 channels are used such as Fractional T1, 384K bps service, 768K bps, or ISDN-PRI. Also useful for locating individual channels in drop-and-insert applications. See Section 13 for timing details.                                          |

| 34       | RLOS/LOTC        | 0    | <b>Receive Loss of Sync/Loss of Transmit Clock.</b> A dual function output. If CCR1.6=0, then this pin will toggle high when the synchronizer is searching for the T1 frame and multiframe. If CCR1.6=1, then this pin will toggle high when the TCLK pin has not been toggled for 5 ms.                                                                                                                                                                                      |

| 35       | INT2             | 0    | <b>Receive Alarm Interrupt 2.</b> Flags host controller during conditions defined in Status Register 2. Active low, open drain output.                                                                                                                                                                                                                                                                                                                                        |

| 36       | INT1             | Ο    | <b>Receive Alarm Interrupt 1.</b> Flags host controller during alarm conditions defined in Status Register 1. Active low, open drain output.                                                                                                                                                                                                                                                                                                                                  |

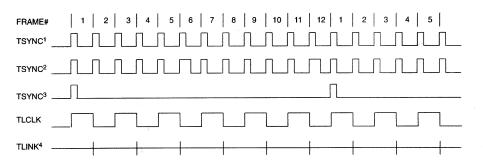

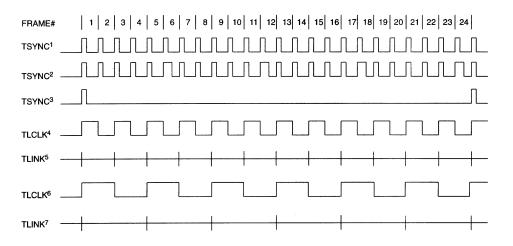

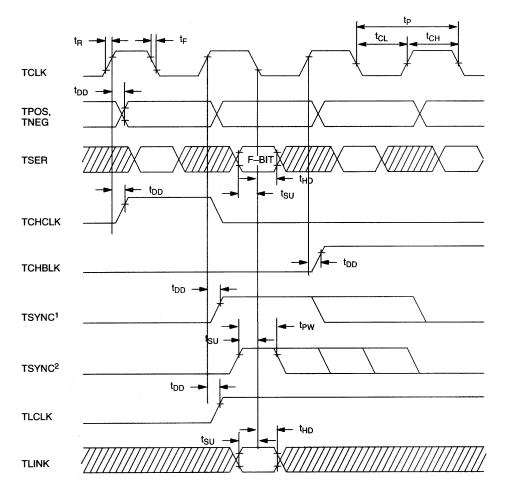

| 37       | TLCLK            | 0    | <b>Transmit Link Clock.</b> 4 kHz or 2 kHz (ZBTSI) demand clock for the TLINK input. See Section 13 for timing details.                                                                                                                                                                                                                                                                                                                                                       |

| PIN | SYMBOL | TYPE | DESCRIPTION                                                               |

|-----|--------|------|---------------------------------------------------------------------------|

| 38  | TLINK  | Ι    | Transmit Link Data. If enabled via TCR1.2, this pin will be               |

|     |        |      | sampled during the F-bit time on the falling edge of TCLK for data        |

|     |        |      | insertion into either the FDL stream (ESF) or the Fs-bit position         |

|     |        |      | (D4) or the Z-bit position (ZBTSI). See Section 13 for timing             |

|     |        |      | details.                                                                  |

| 39  | TSYNC  | I/O  | Transmit Sync. A pulse at this pin will establish either frame or         |

|     |        |      | multiframe boundaries for the DS2141A. Via TCR2.2, the DS2141A            |

|     |        |      | can be programmed to output either a frame or multiframe pulse at         |

|     |        |      | this pin. If this pin is set to output pulses at frame boundaries, it can |

|     |        |      | also be set via TCR2.4 to output double-wide pulses at signaling          |

|     |        |      | frames. See Section 13 for timing details.                                |

| 40  | VDD    | -    | Positive Supply. 5.0 volts.                                               |

# **DS2141A REGISTER MAP**

| ADDRESS | R/W | <b>REGISTER NAME</b>     |

|---------|-----|--------------------------|

| 20      | R/W | Status Register 1        |

| 21      | R/W | Status Register 2        |

| 22      | R/W | Receive Information      |

|         |     | Register                 |

| 23      | R   | Bipolar Violation/ESF    |

|         |     | Error Event Count        |

|         |     | Register 1               |

| 24      | R   | Bipolar Violation/ESF    |

|         |     | Error Event Count        |

|         |     | Register 2               |

| 25      | R   | CRC6 Count Register 1    |

| 26      | R   | CRC6 Count Register 2    |

| 27      | R   | Frame Error Count        |

|         |     | Register                 |

| 28      | R   | Receive FDL Register     |

| 29      | R/W | Receive FDL Match        |

|         |     | Register 1               |

| 2A      | R/W | Receive FDL Match        |

|         |     | Register 2               |

| 2B      | R/W | Receive Control Register |

|         |     | 1                        |

| 2C      | R/W | Receive Control Register |

|         |     | 2                        |

| 2D      | R/W | Receive Mark Register 1  |

| 2E      | R/W | Receive Mark Register 2  |

| 2F      | R/W | Receive Mark Register 3  |

| 30      |     | Not Assigned             |

| 31      |     | Not Assigned             |

| 32      | R/W | Transmit Channel         |

|         |     | Blocking Register 1      |

| 33      | R/W | Transmit Channel         |

|         |     | Blocking Register 2      |

| ADDRESS | R/W | <b>REGISTER NAME</b>     |

|---------|-----|--------------------------|

| 34      | R/W | Transmit Channel         |

|         |     | Blocking Register 3      |

| 35      | R/W | Transmit Control         |

|         |     | Register 1               |

| 36      | R/W | Transmit Control         |

|         |     | Register 2               |

| 37      | R/W | Common Control           |

|         |     | Register 1               |

| 38      | R/W | Common Control           |

|         |     | Register 2               |

| 39      | R/W | Transmit Transparency    |

|         |     | Register 1               |

| 3A      | R/W | Transmit Transparency    |

|         |     | Register 2               |

| 3B      | R/W | Transmit Transparency    |

|         |     | Register 3               |

| 3C      | R/W | Transmit Idle Register 1 |

| 3D      | R/W | Transmit Idle Register 2 |

| 3E      | R/W | Transmit Idle Register 3 |

| 3F      | R/W | Transmit Idle Definition |

|         |     | Register                 |

| 60      | R   | Receive Signaling        |

|         |     | Register 1               |

| 61      | R   | Receive Signaling        |

|         |     | Register 2               |

| 62      | R   | Receive Signaling        |

|         |     | Register 3               |

| 63      | R   | Receive Signaling        |

|         |     | Register 4               |

| 64      | R   | Receive Signaling        |

|         |     | Register 5               |

| ADDRESS | R/W | REGISTER NAME             |

|---------|-----|---------------------------|

| 65      | R   | Receive Signaling         |

|         |     | Register 6                |

| 66      | R   | Receive Signaling         |

|         |     | Register 7                |

| 67      | R   | Receive Signaling         |

|         |     | Register 8                |

| 68      | R   | Receive Signaling         |

|         |     | Register 9                |

| 69      | R   | Receive Signaling         |

|         |     | Register 10               |

| 6A      | R   | Receive Signaling         |

|         |     | Register 11               |

| 6B      | R   | Receive Signaling         |

|         |     | Register 12               |

| 6C      | R/W | Receive Channel           |

|         |     | Blocking Register 1       |

| 6D      | R/W | Receive Channel           |

|         |     | Blocking Register 2       |

| 6E      | R/W | Receive Channel           |

|         |     | Blocking Register 3       |

| 6F      | R/W | Interrupt Mask Register 2 |

| 70      | R/W | Transmit Signaling        |

|         |     | Register 1                |

| 71      | R/W | Transmit Signaling        |

|         |     | Register 2                |

| 72      | R/W | Transmit Signaling        |

|         |     | Register 3                |

| ADDRESS | R/W | <b>REGISTER NAME</b>      |

|---------|-----|---------------------------|

| 73      | R/W | Transmit Signaling        |

|         |     | Register 4                |

| 74      | R/W | Transmit Signaling        |

|         |     | Register 5                |

| 75      | R/W | Transmit Signaling        |

|         |     | Register 6                |

| 76      | R/W | Transmit Signaling        |

|         |     | Register 7                |

| 77      | R/W | Transmit Signaling        |

|         |     | Register 8                |

| 78      | R/W | Transmit Signaling        |

|         |     | Register 9                |

| 79      | R/W | Transmit Signaling        |

|         |     | Register 10               |

| 7A      | R/W | Transmit Signaling        |

|         |     | Register 11               |

| 7B      | R/W | Transmit Signaling        |

|         |     | Register 12               |

| 7C      | R/W | LI Control Register Byte  |

|         |     | 1                         |

| 7D      | R/W | LI Control Register Byte  |

|         |     | 2                         |

| 7E      | R/W | Transmit FDL Register     |

| 7F      | R/W | Interrupt Mask Register 1 |

Note: All values indicated within the Address column are hexadecimal.

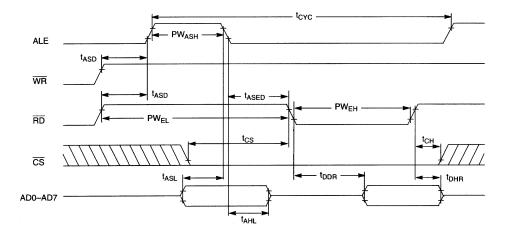

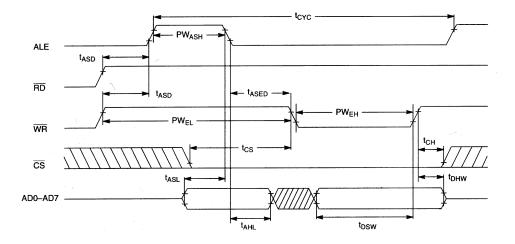

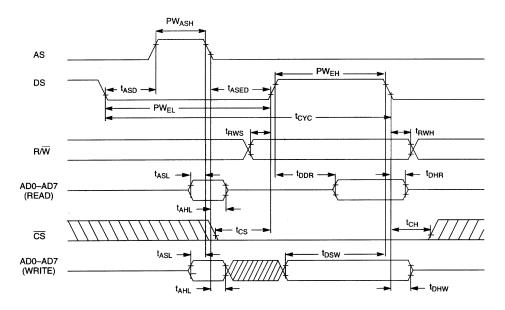

# 2.0 PARALLEL PORT

The DS2141A is controlled via a multiplexed bidirectional address/data bus by an external microcontroller or microprocessor. The DS2141A can operate with either Intel or Motorola bus timing configurations. If the BTS pin is tied low, Intel timing will be selected; if tied high, Motorola timing will be selected. All Motorola bus signals are listed in parentheses (). See the timing diagrams in the AC Electrical Characteristics for more details. The multiplexed bus on the DS2141A saves pins because the address information and data information share the same signal paths. The addresses are presented to the pins in the first portion of the bus cycle and data will be transferred on the pins during second portion of the bus cycle. Addresses must be valid prior to the falling edge of ALE(AS), at which time the DS2141A latches the address from the AD0 to AD7 pins. Valid write data must be present and held stable during the later portion of the DS or  $\overline{WR}$  pulses. In a read cycle, the DS2141A outputs a byte of data during the latter portion of the DS or  $\overline{RD}$  pulses. The read cycle is terminated and the bus returns to a high impedance state as  $\overline{RD}$  transitions high in Intel timing or as DS transitions low in Motorola timing.

# **3.0 CONTROL REGISTERS**

The operation of the DS2141A is configured via a set of six registers. Typically, the control registers are only accessed when the system is first powered up. Once, the DS2141A has been initialized, the control registers will only need to be accessed when there is a change in the system configuration. There are two Receive Control Registers (RCR1 and RCR2), two Transmit Control Registers (TCR1 and TCR2), and two Common Control Registers (CCR1 and CCR2). Each of the six registers is described below.

# RCR1: RECEIVE CONTROL REGISTER 1 (2Bh)

| (MSB) |        |          |                                                                             | <b>、</b>                                                                                                                                                                                                                               |               |               | (LSB)  |  |

|-------|--------|----------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|--------|--|

| -     | ARC    | OOF1     | OOF2                                                                        | SYNCC                                                                                                                                                                                                                                  | SYNCT         | SYNCE         | RESYNC |  |

| SY    | MBOL   | POSITION | NAME ANI                                                                    | D DESCRIPT                                                                                                                                                                                                                             | TION          |               |        |  |

|       | -      | RCR1.7   | Not Assigne                                                                 | d. Should be                                                                                                                                                                                                                           | set to 0 when | n written to. |        |  |

| ł     | ARC    | RCR1.6   | Auto Resyn<br>0=Resync or<br>1=Resync or                                    | n OOF or RCI                                                                                                                                                                                                                           | - event.      |               |        |  |

| C     | OOF1   | RCR1.5   | Out Of Fran<br>0=2/4 frame<br>1=2/5 frame                                   |                                                                                                                                                                                                                                        |               |               |        |  |

| C     | OOF2   | RCR1.4   | 0=follow RC                                                                 | Out Of Frame Select 2.<br>0=follow RCR1.5.<br>1=2/6 frame bits in error.                                                                                                                                                               |               |               |        |  |

| SY    | YNCC . | RCR1.3   | In D4 Framin<br>0=search for<br>1=cross coup<br>In ESF Fram<br>0=search for | Sync Criteria.<br>In D4 Framing Mode.<br>0=search for Ft pattern, then search for Fs pattern.<br>1=cross couple Ft and Fs pattern.<br>In ESF Framing Mode.<br>0=search for FPS pattern only.<br>1=search for FPS and verify with CRC6. |               |               |        |  |

| SY    | YNCT   | RCR1.2   |                                                                             | <b>Sync Time.</b><br>0=qualify 10 bits.<br>1=qualify 24 bits.                                                                                                                                                                          |               |               |        |  |

| SY    | YNCE   | RCR1.1   | Sync Enable<br>0=auto resyn<br>1=auto resyn                                 | ic enabled.                                                                                                                                                                                                                            |               |               |        |  |

| RE    | SYNC   | RCR1.0   | •                                                                           | nen toggled fro<br>red and set ag                                                                                                                                                                                                      |               | •             |        |  |

# RCR2: RECEIVE CONTROL REGISTER 2 (2Ch)

| (MSB) |               |                           |                                                                                                                                                                                                         |                                                                                                                                       |       |      | (LSB)  |  |  |

|-------|---------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------|--------|--|--|

| RCS   | RZBTSI        | RSDW                      | RSM                                                                                                                                                                                                     | RSIO                                                                                                                                  | RD4YM | FSBE | BPVCRS |  |  |

|       | MBOL P        | <b>POSITION</b><br>RCR2.7 | <b>Receive Co</b><br>0=idle code                                                                                                                                                                        | NAME AND DESCRIPTION<br>Receive Code Select.<br>0=idle code (7F Hex).<br>1=digital milliwatt code (1E/0B/0B/1E/9E/8B/8B/9)            |       |      |        |  |  |

| RZ    | RZBTSI RCR2.6 |                           |                                                                                                                                                                                                         | 1=digital milliwatt code (1E/0B/0B/1E/9E/8B/8B/9E Hex).<br><b>Receive Side ZBTSI Enable.</b><br>0=ZBTSI disabled.<br>1=ZBTSI enabled. |       |      |        |  |  |

| R     | SDW           | RCR2.5                    | <b>RSYNC Double-Wide.</b><br>0=do not pulse double-wide in signaling frames.<br>1=do pulse double-wide in signaling frames.<br>(note: this bit must be set to 0 when RCR2.4 = 1 or when<br>RCR2.3 = 1). |                                                                                                                                       |       |      |        |  |  |

| F     | RSM           | RCR2.4                    | <b>RSYNC Mode Select.</b><br>0=frame mode (see the timing in Section 13).<br>1=multiframe mode (see the timing in Section 13).                                                                          |                                                                                                                                       |       |      |        |  |  |

| R     | SIO           | RCR2.3                    | <b>RSYNC I/O Select.</b><br>0=RSYNC is an output.<br>1=RSYNC is an input (only valid if elastic store enabled<br>(note: this bit must be set to 0 when CCR1.2 = 0).                                     |                                                                                                                                       |       |      |        |  |  |

| RI    | D4YM          | RCR2.2                    | <b>Receive Side D4 Yellow Alarm Select.</b><br>0=0 in bit 2 of all channels.<br>1=a 1 in the S-bit position of frame 12.                                                                                |                                                                                                                                       |       |      |        |  |  |

| F     | FSBE RCR2.1   |                           | <b>Fs-Bit Error Report Enable.</b><br>0=do not report bit errors in the Fs-bit position in FECR.<br>1=report bit errors in the Fs-bit position in FECR.                                                 |                                                                                                                                       |       |      |        |  |  |

| BP    | VCRS          | RCR2.0                    | <b>BPVCRS Function Select.</b><br>0=counts bipolar violations.<br>1=counts ESF error events (CRC6 OR 'ed with RLOS).                                                                                    |                                                                                                                                       |       |      |        |  |  |

# TCR1: TRANSMIT CONTROL REGISTER 1 (35h)

| MSB) |       |          |                                                                                                                       |                                                                                                                                     |                                                     |                                       | (LSB) |  |  |

|------|-------|----------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------|-------|--|--|

| ODF  | TFPT  | TCPT     | RBSE                                                                                                                  | GB7S                                                                                                                                | TLINK                                               | TBL                                   | TYEL  |  |  |

| SYI  | MBOL  | POSITION | NAME ANI                                                                                                              | ) DESCRIP                                                                                                                           | ΓΙΟΝ                                                |                                       |       |  |  |

| (    | ODF   | TCR1.7   | -                                                                                                                     | <b>a Format.</b><br>ta at TPOS a<br>at TPOS; TN                                                                                     |                                                     |                                       |       |  |  |

| Т    | Ϋ́FPT | TCR1.6   | 0=Ft or FPS                                                                                                           | <b>Transmit Framing Pass Through.</b><br>0=Ft or FPS bits sourced internally.<br>1=Ft or FPS bits sampled at TSER during F-bit time |                                                     |                                       |       |  |  |

| Т    | ĊĊPŦ  | TCR1.5   | <b>Transmit CRC Pass Through.</b><br>0=source CRC6 bits internally.<br>1=CRC6 bits sampled at TSER during F-bit time. |                                                                                                                                     |                                                     |                                       |       |  |  |

| R    | BSE   | TCR1.4   | 0=no signali<br>1=signaling                                                                                           | is inserted in                                                                                                                      | in any chann<br>all channels (                      | el.<br>the TTR register channel basis |       |  |  |

| G    | B7S   | TCR1.3   | Global Bit 7<br>0=allow the<br>containing at<br>1=force bit 7                                                         | <b>Stuffing.</b><br>TTR register<br>Il zeros are to                                                                                 | s to determine<br>be bit 7 stuff<br>ll zero byte cl | e which chann                         | nels  |  |  |

| TI   | LINK  | TCR1.2   |                                                                                                                       | L or Fs bits f                                                                                                                      | from TFDL re<br>from the TLIN                       | -                                     |       |  |  |

| ]    | ΓBL   | TCR1.1   | <b>Transmit Blue Alarm.</b><br>0=transmit data normally.<br>1=transmit an unframed all 1's code at TPOS and TNEG.     |                                                                                                                                     |                                                     |                                       |       |  |  |

| Т    | YEL   | TCR1.0   | <b>Transmit Yellow Alarm.</b><br>0=do not transmit yellow alarm.<br>1=transmit yellow alarm.                          |                                                                                                                                     |                                                     |                                       |       |  |  |

# TCR2: TRANSMIT CONTROL REGISTER 2 (36h)

| (MSB)        |                                                                                          |         | <u> </u>              |                                                                                                                                         | . /                                              |                |       | (LSB) |  |

|--------------|------------------------------------------------------------------------------------------|---------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------|-------|-------|--|

| TESTM        | TESTI                                                                                    | O TZB1  | TSI T                 | SDW                                                                                                                                     | TSM                                              | TSIO           | TD4YM | B7ZS  |  |

| SYN          | MBOL                                                                                     | POSITIO | N NAI                 | ME ANI                                                                                                                                  | D DESCRIPT                                       | TION           |       |       |  |

| TESTM TCR2.7 |                                                                                          |         |                       | <b>Test Mode Select.</b> Set this bit to a 1 to force all outputs (including I/O pins) either high (TCR2.6 = 1) or low (TCR2.6 = $0$ ). |                                                  |                |       |       |  |

| TE           | TESTIO TCR2.6                                                                            |         |                       |                                                                                                                                         | <b>is.</b><br>output (and I/C<br>output (and I/C | · 1            | 0     |       |  |

| ΤΖ           | ZBTSI TCR2.5 <b>Transmit Side ZBTSI Enable.</b><br>0=ZBTSI disabled.<br>1=ZBTSI enabled. |         | 0=ZBTSI disabled.     |                                                                                                                                         |                                                  |                |       |       |  |

| TS           | SDW                                                                                      | TCR2.4  | 0=de<br>1=de<br>(note | o not pu<br>o pulse c                                                                                                                   |                                                  | n signaling fr | •     | when  |  |

| Т            | CSM                                                                                      | TCR2.3  | 0=fr                  | <b>TSYNC Mode Select.</b><br>0=frame mode (see the timing in Section 13).<br>1=multiframe mode (see the timing in Section 13).          |                                                  |                |       |       |  |

| Т            | SIO                                                                                      | TCR2.2  | 0=T                   | <b>TSYNC I/O Select.</b><br>0=TSYNC is an input.<br>1=TSYNC is an output.                                                               |                                                  |                |       |       |  |

| TĽ           | 04YM                                                                                     | TCR2.1  | 0=0                   | <b>Transmit Side D4 Yellow Alarm Select.</b><br>0=0s in bit 2 of all channels.<br>1=a 1 in the S-bit position of frame 12.              |                                                  |                |       |       |  |

| В            | 57ZS                                                                                     | TCR2.0  | 0=ne                  | <b>Bit 7 Zero Suppression Enable.</b><br>0=no stuffing occurs.<br>1=Bit 7 forced to a 1 in channels with all 0s.                        |                                                  |                |       |       |  |

|              |                                                                                          |         |                       |                                                                                                                                         |                                                  |                |       |       |  |

# CCR1: COMMON CONTROL REGISTER 1 (37h)

| (MSB) |             |          |                                                          |                                                                                                                                          |      |     | (LSB) |  |  |

|-------|-------------|----------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|--|--|

| TESE  | P34F        | RSAO     | -                                                        | SCLKM                                                                                                                                    | RESE | PLB | LLB   |  |  |

| SYN   | MBOL        | POSITION | NAME A                                                   | NAME AND DESCRIPTION                                                                                                                     |      |     |       |  |  |

| Т     | ESE         | CCR1.7   | 0=elastic s                                              | Elastic Store E<br>store is bypassed<br>store is enabled.                                                                                |      |     |       |  |  |

| Р     | P34F CCR1.6 |          |                                                          | Function of Pin 34.<br>0=Receive Loss of Sync (RLOS).<br>1=Loss of Transmit Clock (LOTC).                                                |      |     |       |  |  |

| R     | RSAO CCR1.5 |          |                                                          | <b>Receive Signaling All 1's.</b><br>0=allow robbed signaling bits to appear at RSER.<br>1=force all robbed signaling bits at RSER to 1. |      |     |       |  |  |

|       | -           | CCR1.4   | <b>Not Assigned.</b> Should be set to 0 when written to. |                                                                                                                                          |      |     |       |  |  |

| SC    | CLKM        | CCR1.3   | <b>SYSCLK</b><br>0=if SYSC<br>1=if SYSC                  |                                                                                                                                          |      |     |       |  |  |

| R     | ESE         | CCR1.2   | 0=elastic s                                              | lastic Store Ena<br>store is bypassed<br>store is enabled.                                                                               |      |     |       |  |  |

| I     | PLB         | CCR1.1   | -                                                        | 2 <b>00pback.</b><br>k disabled.<br>k enabled.                                                                                           |      |     |       |  |  |

| Ι     | LLB         | CCR1.0   | -                                                        | <b>pback.</b><br>k disabled.<br>k enabled.                                                                                               |      |     |       |  |  |

# PAYLOAD LOOPBACK

When CCR1.1 is set to a 1, the DS2141A will be forced into Payload LoopBack (PLB). Normally, this loopback is only enabled when ESF framing is being performed. In a PLB situation, the DS2141A will loop the 192 bits of payload data (with BPVs corrected) from the receive section back to the transmit section. The FPS framing pattern, CRC6 calculation, and the FDL bits are not looped back, they are reinserted by the DS2141A. When PLB is enabled, the following will occur:

- 1. Data will be transmitted from the TPOS and TNEG pins synchronous with RCLK instead of TCLK.

- 2. All of the receive side signals will continue to operate normally.

- 3. The TCHCLK and TCHBLK signals are forced low.

- 4. Data at the TSER pin is ignored.

- 5. The TLCLK signal will become synchronous with RCLK instead of TCLK.

# LOCAL LOOPBACK

When CCR1.0 is set to a 1, the DS2141A will enter a Local LoopBack (LLB) mode. This loopback is useful in testing and debugging applications. In LLB, the DS2141A will loop data from the transmit side back to the receive side. This loopback is synonymous with replacing the RCLK input with the TCLK signal, and the RPOS/RNEG inputs with the TPOS/TNEG outputs. When LLB is enabled, the following will occur:

- 1. The TPOS and TNEG pins will transmit an unframed all 1's.

- 2. Data at RPOS and RNEG will be ignored.

- 3. All receive side signals will take on timing synchronous with TCLK instead of RCLK.

| (MSB) |              |          |                                                     |                                                                                 |             |        | (LSB) |  |  |  |

|-------|--------------|----------|-----------------------------------------------------|---------------------------------------------------------------------------------|-------------|--------|-------|--|--|--|

| TFM   | TB8ZS        | TSLC96   | TFDL                                                | RFM                                                                             | RB8ZS       | RSLC96 | RFDL  |  |  |  |

| SYN   | MBOL         | POSITION | NAME ANI                                            | NAME AND DESCRIPTION                                                            |             |        |       |  |  |  |

| Т     | ΓFM          | CCR2.7   | 0=D4 framin                                         | <b>Transmit Frame Mode Select.</b><br>0=D4 framing mode.<br>1=ESF framing mode. |             |        |       |  |  |  |

| TI    | TB8ZS CCR2.6 |          |                                                     | <b>Transmit B8ZS Enable.</b><br>0=B8ZS disabled.<br>1=B8ZS enabled.             |             |        |       |  |  |  |

| TS    | LC96         | CCR2.5   | <b>Transmit SI</b><br>0=SLC-96 d<br>1=SLC-96 er     | isabled.                                                                        | Insertion E | nable. |       |  |  |  |

| T     | FDL          | CCR2.4   | <b>Transmit Z</b><br>0=zero stuffe<br>1=zero stuffe |                                                                                 | Cnable.     |        |       |  |  |  |

| R     | RFM          | CCR2.3   | <b>Receive Fra</b><br>0=D4 framin<br>1=ESF frami    | ig mode.                                                                        | lect.       |        |       |  |  |  |

| RI    | B8ZS         | CCR2.2   | <b>Receive B87</b><br>0=B8ZS disa<br>1=B8ZS ena     | abled.                                                                          |             |        |       |  |  |  |

| RS    | LC96         | CCR2.1   | <b>Receive SLO</b><br>0=SLC-96 d<br>1=SLC-96 er     | isabled.                                                                        |             |        |       |  |  |  |

| R     | FDL          | CCR2.0   | 0=zero destu                                        | o Destuffer 1<br>ffer disabled.<br>ffer enabled.                                |             |        |       |  |  |  |

# CCR1: COMMON CONTROL REGISTER 2 (38h)

# 4.0 STATUS AND INFORMATION REGISTERS

There is a set of three registers that contain information on the current real time status of the DS2141A: Status Register 1 (SR1), Status Register 2 (SR2), and the Receive Information Register (RIR). When a particular event has occurred (or is occurring), the appropriate bit in one of these three registers will be set to a 1. All of the bits in these registers operate in a latched fashion. This means that if an event occurs and a bit is set to a 1 in any of the registers, it will remain set until the user reads that bit. The bit will be cleared when it is read and it will not be set again until the event has occurred again (or in the case of RLOS, if loss of sync is still present).

The user will always precede a read of these registers with a write. The byte written to the register will inform the DS2141A which bits the user wishes to read and have cleared. The user will write a byte to one of these three registers, with a 1 in the bit positions he or she wishes to read and a 0 in the bit positions he or she does not wish to obtain the latest information on. When a 1 is written to a bit location, the read register will be updated with current value and it will be cleared. When a 0 is written to a bit position, the read register will not be updated and the previous value will be held. A write to the status and information registers will be immediately followed by a read of the same register. The read result should be logically AND'ed with the mask byte that was just written and this value should be written back into the same register to insure that the bit does indeed clear. This second write is necessary because the alarms and events in the status registers occur asynchronously in respect to their access via the parallel port. This scheme allows an external microcontroller or microprocessor to individually poll certain bits without disturbing the other bits in the register. This operation is key in controlling the DS2141A with higher-order software languages.

The SR1 and SR2 registers have the unique ability to initiate a hardware interrupt via the INT1 and INT2 pins respectively. Each of the alarms and events in the SR1 and SR2 can be either masked or unmasked from the interrupt pins via the Interrupt Mask Register 1 (IMR1) and Interrupt Mask Register 2 (IMR2) respectively.

#### **RIR: RECEIVE INFORMATION REGISTER (22h)** (MSB) (LSB) COFA 8ZD 16ZD RESF RESE SEFE **B8ZS** FBE **SYMBOL** POSITION NAME AND DESCRIPTION COFA RIR.7 Change of Frame Alignment. Set when the last resync resulted in a change of frame or multiframe alignment. 8ZD RIR.6 Eight Zero Detect. Set when a string of eight consecutive 0s has been received at RPOS and RNEG. 16ZD RIR.5 Sixteen Zero Detect. Set when a string of 16 consecutive 0s has been received at RPOS and RNEG. **Receive Elastic Store Full.** Set when the elastic store buffer RESF RIR.4 fills and a frame is deleted. RESE **Receive Elastic Store Empty.** Set when the elastic store buffer RIR.3 empties and a frame is repeated. SEFE RIR.2 Severely Errored Framing Event. Set when 2 out of 6 framing bits are received in error. RIR.1 **B8ZS Code Word Detect.** Set when a B8ZS code word is B8ZS detected at RPOS and RNEG independent of whether the B8ZS mode is selected or not via CCR2.2. Frame Bit Error. Set when a Ft (D4) or FPS (ESF) framing bit FBE RIR.0 is received in error.

Note: If the transmit elastic store slips, both RIR.4 and RIR.3 will be set.

|                                                                                                           |                 |             |                                                                                         |                                                                                                                                                                               |                                      |               |                        | DS2141A     |  |

|-----------------------------------------------------------------------------------------------------------|-----------------|-------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|------------------------|-------------|--|

|                                                                                                           | R1: STA<br>MSB) | TUS R       | EGISTER 1                                                                               | (20h)                                                                                                                                                                         |                                      |               |                        | (LSB)       |  |

|                                                                                                           | LUP             | LDN         | LOTC                                                                                    | SLIP                                                                                                                                                                          | RBL                                  | RYEL          | RCL                    | RLOS        |  |

|                                                                                                           | SYN             | <b>IBOL</b> | POSITION                                                                                | NAME ANI                                                                                                                                                                      | D DESCRIP                            | ΓΙΟΝ          |                        |             |  |

|                                                                                                           | L               | UP          | SR1.7                                                                                   |                                                                                                                                                                               | de Detected.<br>is being rece        |               | e repeating            | .00001      |  |

|                                                                                                           | L               | DN          | SR1.6                                                                                   | <b>Loop Down Code Detected.</b> Set when the repeating001 loop down code is being received.                                                                                   |                                      |               |                        |             |  |

|                                                                                                           | LO              | DTC         | SR1.5                                                                                   | <b>Loss of Transmit Clock.</b> Set when the TCLK pin has not transitioned for one channel time (or $5.2 \mu$ s). Will force pin-34 high if enabled via CCR1.6. Based on RCLK. |                                      |               |                        |             |  |

|                                                                                                           | S               | LIP         | SR1.4                                                                                   |                                                                                                                                                                               | e <b>Slip Occur</b><br>ed or deleted |               | hen the elastic<br>ta. | c store has |  |

|                                                                                                           | R               | BL          | SR1.3                                                                                   | <b>Receive Blu</b><br>RPOS and R                                                                                                                                              |                                      | t when an all | 1's code is rec        | ceived at   |  |

|                                                                                                           | R               | YEL         | SR1.2 <b>Receive Yellow Alarm.</b> Set when a yellow alarm is received a RPOS and RNEG. |                                                                                                                                                                               |                                      |               |                        |             |  |

|                                                                                                           | R               | CL          | SR1.1                                                                                   | Receive Carrier Loss.Set when 192 consecutive 0s have<br>detected at RPOS and RNEG.                                                                                           |                                      |               |                        |             |  |

| RLOS SR1.0 <b>Receive Loss of Sync.</b> Set when the device is not synchronized to the receive T1 stream. |                 |             |                                                                                         |                                                                                                                                                                               |                                      | vnchronized   |                        |             |  |

### LOOP UP/DOWN CODE DETECTION

Bits SR1.7 and SR1.6 will indicate when either the standard "loop up" or "loop down" codes are being received by the DS2141A. When a loop up code has been received for 5 seconds, the CPE is expected to loop the recovered data (without correcting BPVs) back to the source. The loop down code indicates that the loopback should be discontinued. See the AT&T publication TR 62411 for more details. The DS2141A will detect the loop up/down codes in both framed and unframed circumstances with bit error rates as high as 10-<sup>2</sup>. The loop code detector has a nominal integration period of 48 ms. Hence, after about 48 ms of receiving either code, the proper status bit will be set to a 1. After this initial indication, it is recommended that the software poll the DS2141A every 100 ms to 500 ms until five seconds have elapsed to insure that the code is continuously present. Once five seconds have passed, the line interface should be taken into or out of loopback.

#### SR2: STATUS REGISTER 2 (21h) (MSB) (LSB) RFDL RMF TMF SEC TFDL RMTCH RAF LORC **SYMBOL** POSITION NAME AND DESCRIPTION RMF SR2.7 **Receive Multiframe.** Set on receive multiframe boundaries. TMF SR2.6 **Transmit Multiframe.** Set on transmit multiframe boundaries. SEC SR2.5 One Second Timer. Set on increments of one second based on RCLK; will be set in increments of 999 ms, 999 ms, and 1002 ms every three seconds. RFDL SR2.4 **Receive FDL Buffer Full.** Set when the receive FDL buffer (RFDL) fills to capacity (8-bits). **TFDL** SR2.3 Transmit FDL Buffer Empty. Set when the transmit FDL buffer (TDFL) empties. RMTCH SR2.2 **Receive FDL Match Occurrence.** Set when the RFDL matches either RFDLM1 or RFDLM2. RAF SR2.1 Receive FDL Abort. Set when eight consecutive 1's are received in the FDL. LORC SR2.0 Loss of Receive Clock. Set when the RCLK pin has not transitioned for at least 2 $\mu$ s (3 $\mu$ s $\pm$ 1 $\mu$ s).

# IMR1: INTERRUPT MASK REGISTER 1 (7Fh)

| MSB) | -                  |                    |                                                                               | •                                  |        |     | (LSB) |

|------|--------------------|--------------------|-------------------------------------------------------------------------------|------------------------------------|--------|-----|-------|

| LUP  | LDN                | LOTC               | SLIP                                                                          | RBL                                | RYEL   | RCL | RLOS  |

|      | <b>MBOL</b><br>LUP | POSITION<br>IMR1.7 | Loop Up Co                                                                    | D DESCRIP                          |        |     |       |

| ]    | LDN                | IMR1.6             | 0=interrupt r<br>1=interrupt e<br>Loop Down<br>0=interrupt r<br>1=interrupt e | enabled.<br>Code Detect<br>nasked. | ted.   |     |       |

| L    | LOTC               | IMR1.5             | -                                                                             | <b>nsmit Clock.</b><br>nasked.     |        |     |       |

| S    | SLIP               | IMR1.4             | Elastic Stor<br>0=interrupt r<br>1=interrupt e                                |                                    | rence. |     |       |

| ]    | RBL                | IMR1.3             | <b>Receive Blu</b><br>0=interrupt r<br>1=interrupt e                          | nasked.                            |        |     |       |

| R    | RYEL               | IMR1.2             | <b>Receive Yel</b><br>0=interrupt r<br>1=interrupt e                          | nasked.                            |        |     |       |

| ]    | RCL                | IMR1.1             | <b>Receive Car</b><br>0=interrupt r<br>1=interrupt e                          | nasked.                            |        |     |       |

| R    | RLOS               | IMR1.0             | <b>Receive Los</b><br>0=interrupt r<br>1=interrupt e                          | nasked.                            |        |     |       |

# IMR2: INTERRUPT MASK REGISTER 2 (6Fh)

|     |      | ~~~~     | DEST                                                |           | D) (77.77 | D / | (LSB) |

|-----|------|----------|-----------------------------------------------------|-----------|-----------|-----|-------|

| RMF | TMF  | SEC      | RFDL                                                | TFDL      | RMTCH     | RAF | LORC  |

| SYI | MBOL | POSITION | NAME ANI                                            | D DESCRIP | TION      |     |       |

| F   | RMF  | IMR2.7   | <b>Receive Mu</b><br>0=interrupt r<br>1=interrupt e | nasked.   |           |     |       |

| Т   | ſMF  | IMR2.6   | <b>Transmit</b> M<br>0=interrupt 1<br>1=interrupt e | nasked.   |           |     |       |

| S   | SEC  | IMR2.5   | <b>One Second</b><br>0=interrupt 1<br>1=interrupt e | nasked.   |           |     |       |

| R   | FDL  | IMR2.4   | <b>Receive FD</b><br>0=interrupt r<br>1=interrupt e | nasked.   | 11.       |     |       |

| Т   | FDL  | IMR2.3   | <b>Transmit F</b><br>0=interrupt f<br>1=interrupt e | nasked.   | Cmpty.    |     |       |

| RN  | ИТСН | IMR2.2   | <b>Receive FD</b><br>0=interrupt r<br>1=interrupt e | nasked.   | currence. |     |       |

| I   | RAF  | IMR2.1   | <b>Receive FD</b><br>0=interrupt f<br>1=interrupt e | nasked.   |           |     |       |

| L   | ORC  | IMR2.0   | Loss of Rec<br>0=interrupt 1<br>1=interrupt 6       | nasked.   |           |     |       |

# **5.0 ERROR COUNT REGISTERS**

There is a set of three counters in the DS2141A that record bipolar violations, errors in the CRC6 code words, and frame bit errors. Each of these three counters is automatically updated on 1-second boundaries as determined by the 1-second timer in Status Register 2 (SR2.5). Hence, these registers contain performance data from the previous second. The user can use the interrupt from the 1-second timer to determine when to read these registers. The user has a full second to read the counters before the data is lost.

# BPVCR1: BIPOLAR VIOLATION COUNT REGISTER 1 (23h) BPVCR2: BIPOLAR VIOLATION COUNT REGISTER 2 (24h)

| (MSB) |      |      |      |      |      |     | (LSB) |        |

|-------|------|------|------|------|------|-----|-------|--------|

| BV15  | BV14 | BV13 | BV12 | BV11 | BV10 | BV9 | BV8   | BPVCR1 |

| BV7   | BV6  | BV5  | BV4  | BV3  | BV2  | BV1 | BV0   | BPVCR2 |

#### SYMBOL POSITION NAME AND DESCRIPTION

BV15 BPVCR1.7 MSB of the bipolar violation count.

BV0 BPVCR2.0 LSB of the bipolar violation count.

Bipolar Violation Count Register 1 (BPVCR1) is the most significant word and BPVCR2 is the least significant word of a 16-bit counter that records bipolar violations (BPVs). If the B8ZS mode is set for the receive side via CCR2.2, then B8ZS code words are not counted. This counter increments at all times and is not disabled by loss of sync conditions. The counter saturates at 65,535 and will not roll over. If the DS2141A is programmed to record ESF error events (RCR2.0=1), then the BPVCR will increment for each ESF multiframe that contains either an error in the CRC6 word or an out-of-frame occurrence (loss of sync).

# CRCCR1: CRC6 COUNT REGISTER 1 (25h) CRCCR2: CRC6 COUNT REGISTER 2 (26h)

| ( | (MSB) |      |      |      |      |      |      | (LSB) |        |

|---|-------|------|------|------|------|------|------|-------|--------|

|   | CRC7  | CRC6 | CRC5 | CRC4 | CRC3 | CRC2 | CRC1 | CRC0  | CRCCR1 |

|   | CRC7  | CRC6 | CRC5 | CRC4 | CRC3 | CRC2 | CRC1 | CRC0  | CRCCR2 |

### SYMBOL POSITION NAME AND DESCRIPTION

CRC7 CRCCR1.7 MSB of the CRC6 count.

CRC0 CRCCR2.0 LSB of the CRC6 count.

CRC6 Count Register 1 (CRCCR1) is the most significant word and CRCCR2 is the least significant word of a 16-bit counter that records word errors in the Cyclic Redundancy Check 6 (CRC6) when the DS2141A is operated in the ESF framing mode (CCR2.3 = 1). This counter saturates at 65,535 and will not roll over. The counter is disabled during loss of sync conditions.

|   |                   |            |         |              |               |       |     | DS2141A |

|---|-------------------|------------|---------|--------------|---------------|-------|-----|---------|

| F | FECR: FF<br>(MSB) | RAME ER    | ROR COL | JNT REGIS    | TER (27h      | )     |     | (LSB)   |

|   | FE7               | FE6        | FE5     | FE4          | FE3           | FE2   | FE1 | FE0     |

|   | SYN               | MBOL P     | OSITION | NAME ANI     | ) DESCRIP     | ΓΙΟΝ  |     |         |

|   | Ι                 | FE7 FECR.7 |         | MSB of the l |               |       |     |         |

|   | I                 | FE0        | FECR.0  | LSB of the F | Frame Error c | ount. |     |         |

The Frame Error Count Register (FECR) is a 8-bit counter that records either errors in the framing pattern. The FECR will count individual bit errors in the ESF framing pattern (...001011...) if the device is set into the ESF framing mode (CCR2.3 = 1) and it will count individual bit errors in the Ft framing pattern (...101010...) in the D4 framing mode (CCR2.3 = 0). If RCR2.1=1, then the FECR will also record individual bit errors in the Fs framing pattern (...001110...) when it is in the D4 framing mode. This counter saturates at 255 and will not roll over. The counter is disabled during loss of sync conditions.

# 6.0 FDL/FS EXTRACTION AND INSERTION

The DS2141A has the ability to extract/insert data from/into the Facility Data Link (FDL) in the ESF framing mode and from/into Fs-bit position in the D4 framing mode. Since SLC-96 utilizes the Fs-bit position, this capability can also be used in SLC-96 applications. The operation of the receive and transmit sections will be discussed separately.

# 6.1 Receive Section

In the receive section, the recovered FDL bits or Fs bits are shifted bit-by-bit into the Receive FDL register (RFDL). Since the RFDL is 8 bits in length, it will fill up every 2 ms (8 x 250 µs). The DS2141A will signal an external microcontroller that the buffer has filled via the SR2.4 bit. If enabled via IMR2.4, the INT2 pin will toggle low indicating that the buffer has filled and needs to be read. The user has 2 ms to read this data before it is lost. If the byte in the RFDL matches either of the bytes programmed into the RFDLM1 or RFDLM2 registers, then the SR2.2 bit will be set to a 1 and the INT2 pin will toggled low if enabled via IMR2.2. This feature allows an external microcontroller to ignore the FDL or Fs pattern until an important event occurs.

The DS2141A also contains a 0 destuffer which is controlled via the CCR2.0 bit. In both ANSI T1.403 and TR54016, communications on the FDL follow a subset of a LAPD protocol. The LAPD protocol states that no more than five 1's should be transmitted in a row so that the data does not resemble an opening or closing flag (0111110) or an abort signal (1111111). If enabled via CCR2.0, the DS2141A will automatically look for five 1's in a row, followed by a 0. If it finds such a pattern, it will automatically remove the 0. If the 0 destuffer sees six or more 1's in a row followed by a 0, the 0 is not removed. The CCR2.0 bit should always be set to a 1 when the DS2141A is extracting the FDL. More on how to use the DS2141A in FDL applications is covered in a separate Application Note.

#### **RFDL: RECEIVE FDL REGISTER (28h)** (MSB) (LSB) RFDL7 RFDL6 RFDL5 RFDL4 RFDL3 RFDL2 RFDL1 RFDL0 **SYMBOL** POSITION NAME AND DESCRIPTION RFDL7 RFDL.7 MSB of the Received FDL Code. LSB of the Received FDL Code. RFDL0 RFDL.0

The Receive FDL Register (RFDL) reports the incoming Facility Data Link (FDL) or the incoming Fsbits. The LSB is received first.

# RFDLM1: RECEIVE FDL MATCH REGISTER 1 (29h) RFDLM2: RECEIVE FDL MATCH REGISTER 2 (2Ah)

| (MSB) |         |         |              |             |       |       | (LSB) |

|-------|---------|---------|--------------|-------------|-------|-------|-------|

| RFDL7 | RFDL6   | RFDL5   | RFDL4        | RFDL3       | RFDL2 | RFDL1 | RFDL0 |

| SYN   | 1BOL PO | OSITION | NAME ANI     | D DESCRIP   | ΓΙΟΝ  |       |       |

| RF    | DL7 ]   | RFDL.7  | MSB of the I | FDL Match C | Code. |       |       |

RFDL0 RFDL.0 LSB of the FDL Match Code.

When the byte in the Receive FDL Register matches either of the two Receive FDL Match Registers (RFDLM1/RFDLM2), RSR2.2 will be set to a 1 and the  $\overline{INT2}$  will go active if enabled via IMR2.2.

# 6.2 Transmit Section

The transmit section will shift out either the FDL (in the ESF framing mode) or the Fs-bits (in the D4 framing mode) contained in the Transmit FDL register (TFDL) into the T1 data stream. When a new value is written to the TFDL, it will be multiplexed serially (LSB first) into the proper position in the outgoing T1 data stream. After the full 8 bits have been shifted out, the DS2141A will signal the host microcontroller that the buffer is empty and that more data is needed by setting the SR2.3 bit to a 1. The INT2 will also toggle low if enabled via IMR2.3. The user has 2 ms (1.5 ms in SLC-96 applications) to update the TFDL with a new value. If the TFDL is not updated, the old value in the TFDL will be transmitted once again.