# MPC8308 PowerQUICC II Pro Processor Reference Manual

MPC8308RM Rev. 0 4/2010

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064

Japan

0120 191014 or

+81 3 5437 9125

support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc. Reg. U.S. Pat. & Tm. Off. CoreNet, QorlQ, QUICC Engine, and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. RapidlO is a registered trademark of the RapidlO Trade Association. IEEE 802.3, 802.3u, 802.3x, 802.3z, 802.3ac, and 802.11i are registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE.

| Paragraph<br>Number | Title                                                    | Page<br>Number |

|---------------------|----------------------------------------------------------|----------------|

|                     | <b>About This Book</b>                                   |                |

|                     | Audience                                                 | lvii           |

|                     | Organization                                             | lvii           |

|                     | Suggested Reading                                        | lix            |

|                     | General Information                                      | lix            |

|                     | Related Documentation                                    | lix            |

|                     | Conventions                                              | lx             |

|                     | Signal Conventions                                       | 1x             |

|                     | Acronyms and Abbreviations                               | lxi            |

|                     | Chapter 1                                                |                |

|                     | Overview                                                 |                |

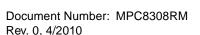

| 1.1                 | MPC8308 Overview                                         |                |

| 1.2                 | MPC8308 Architecture Overview                            |                |

| 1.2.1               | e300 Core                                                | 1-7            |

| 1.2.2               | DDR2 Memory Controller                                   |                |

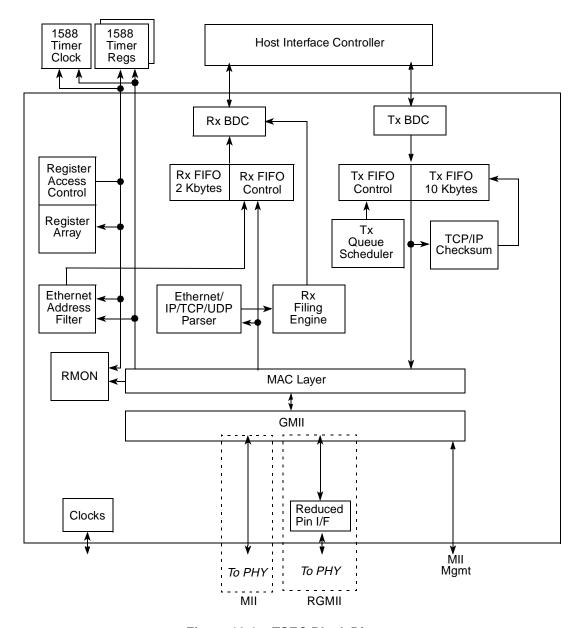

| 1.2.3               | Dual Enhanced Three-Speed Ethernet Controllers           | 1-10           |

| 1.2.4               | SerDes PHY                                               |                |

| 1.2.5               | PCI Express Interface                                    |                |

| 1.2.6               | Universal Serial Bus (USB) 2.0                           |                |

| 1.2.7               | Enhanced Local Bus Controller (eLBC)                     |                |

| 1.2.8               | Integrated Programmable Interrupt Controller (IPIC)      |                |

| 1.2.9               | I <sup>2</sup> C Interface                               |                |

| 1.2.10              | General Purpose DMA Controller                           |                |

| 1.2.11              | Dual Universal Asynchronous Receiver/Transmitter (DUART) |                |

| 1.2.12              | Enhanced Secure Digital Host Controller (eSDHC)          |                |

| 1.2.13              | System Timers                                            | 1-17           |

|                     | Chapter 2                                                |                |

|                     | Signal Descriptions                                      |                |

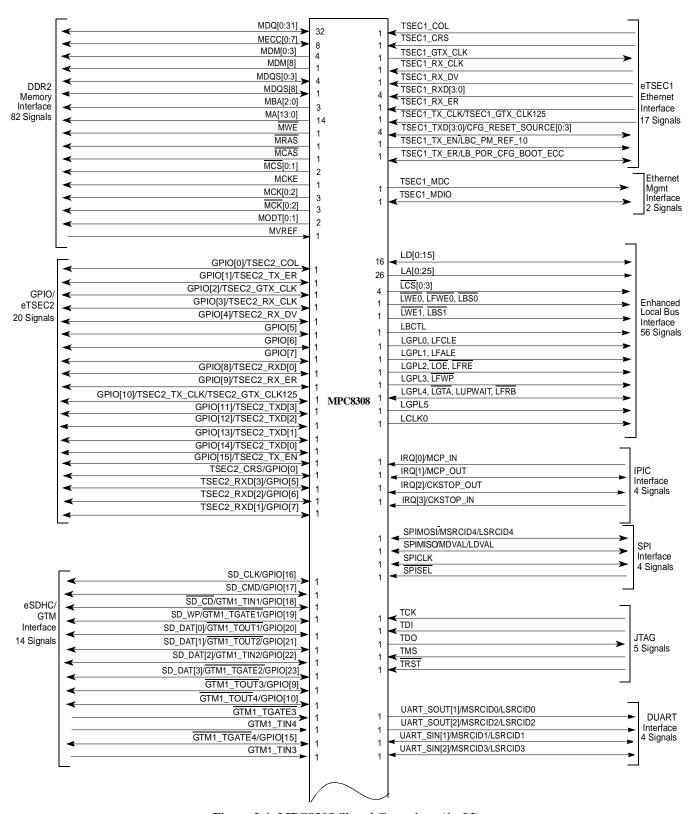

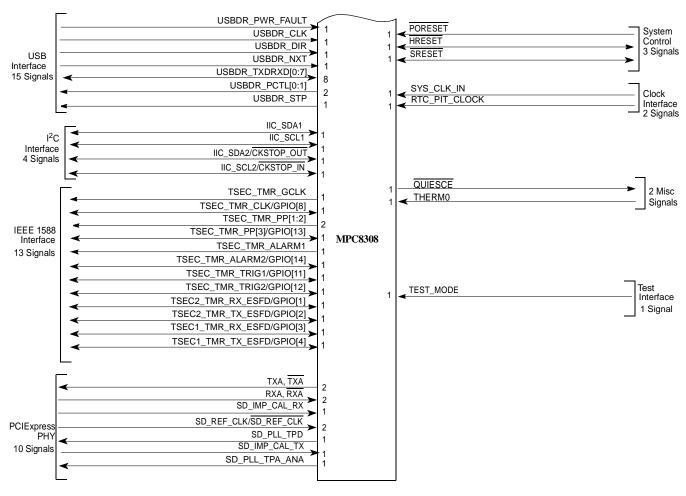

| 2.1                 | Signals Overview                                         | 2-1            |

| 2.2                 | Output Signal States During Reset                        | 2-20           |

|                     | Chapter 3<br>Memory Map                                  |                |

|                     | wichioty wap                                             |                |

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 0

Freescale Semiconductor iii

| Paragraph<br>Number | Title                                                            | Page<br>Number |

|---------------------|------------------------------------------------------------------|----------------|

| 3.1                 | Internal Memory-Mapped Registers                                 | 3-1            |

| 3.2                 | Accessing IMMR Memory from the Local Processor                   | 3-1            |

| 3.3                 | IMMR Address Map                                                 | 3-1            |

|                     | Chapter 4 Reset, Clocking, and Initialization                    |                |

| 4.1                 | External Signals                                                 | 4-1            |

| 4.1.1               | Reset Signals                                                    |                |

| 4.1.2               | Clock Signals                                                    |                |

| 4.2                 | Functional Description                                           |                |

| 4.2.1               | Reset Operations                                                 |                |

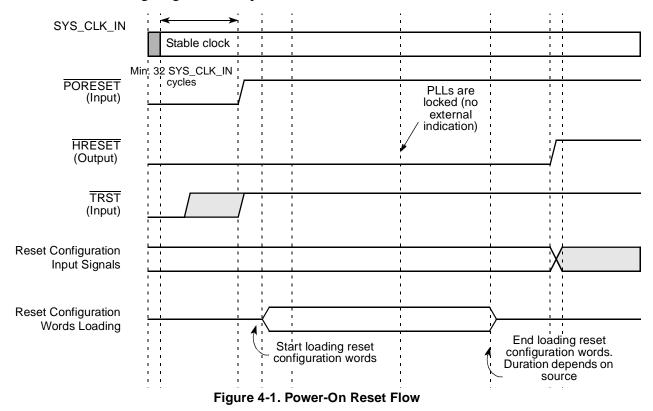

| 4.2.2               | Power-On Reset Flow                                              |                |

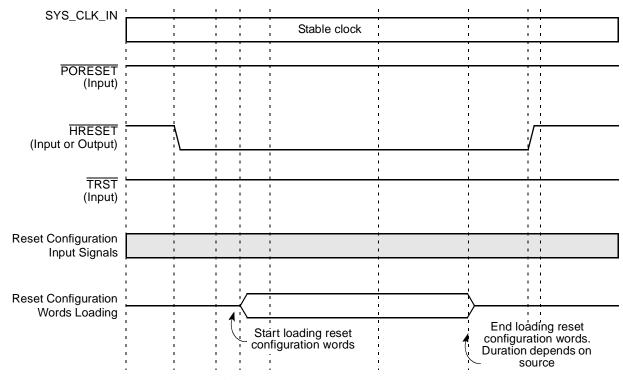

| 4.2.3               | Hard Reset Flow                                                  | 4-6            |

| 4.3                 | Reset Configuration                                              | 4-7            |

| 4.3.1               | Reset Configuration Signals                                      | 4-7            |

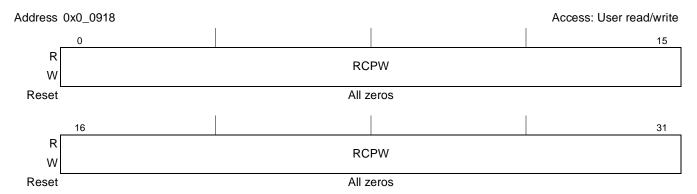

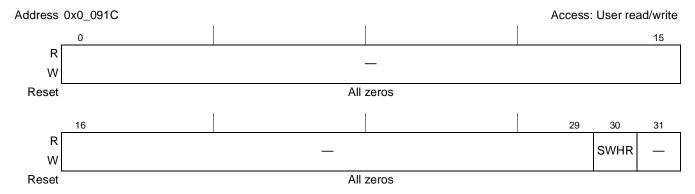

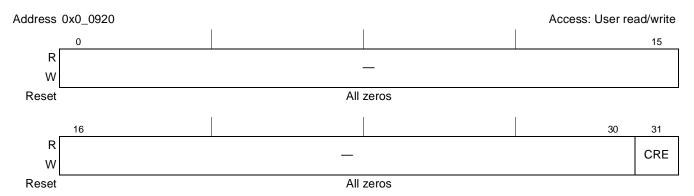

| 4.3.2               | Reset Configuration Words                                        | 4-9            |

| 4.3.3               | Loading the Reset Configuration Words                            | 4-16           |

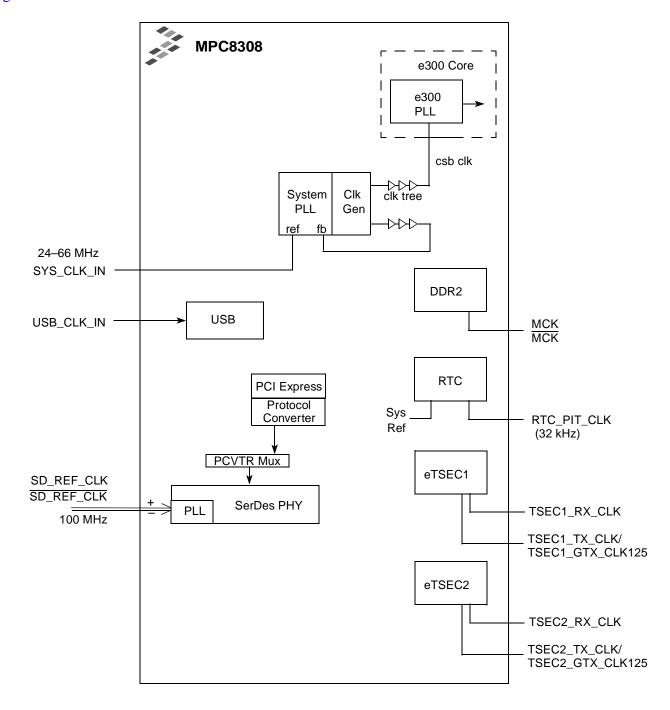

| 4.4                 | Clocking                                                         | 4-22           |

| 4.4.1               | System Clock Domains                                             | 4-24           |

| 4.4.2               | USB Clocking                                                     |                |

| 4.4.3               | Ethernet Clocking                                                | 4-25           |

| 4.5                 | Memory Map/Register Definitions                                  |                |

| 4.5.1               | Reset Configuration Register Descriptions                        |                |

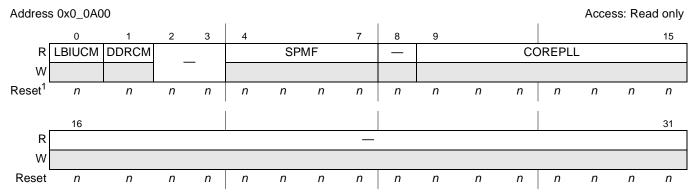

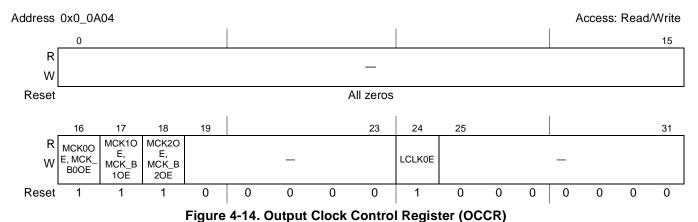

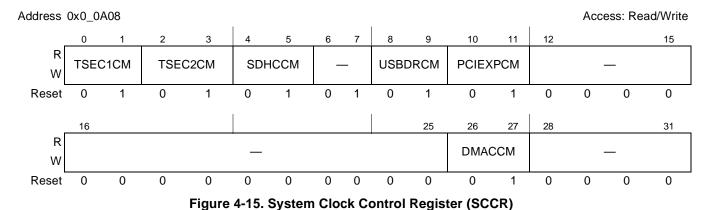

| 4.5.2               | Clock Configuration Registers                                    | 4-29           |

|                     | Chapter 5 System Configuration                                   |                |

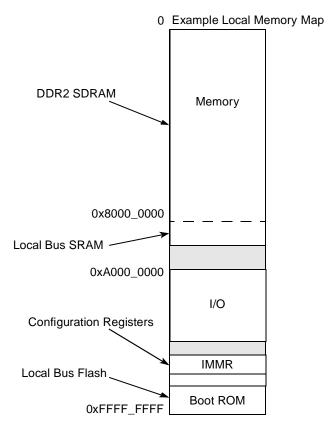

| 5.1                 | Local Memory Map Overview and Example                            | 5-1            |

| 5.1.1               | Address Translation and Mapping                                  |                |

| 5.1.2               | Window into Configuration Space                                  |                |

| 5.1.3               | Local Access Windows                                             |                |

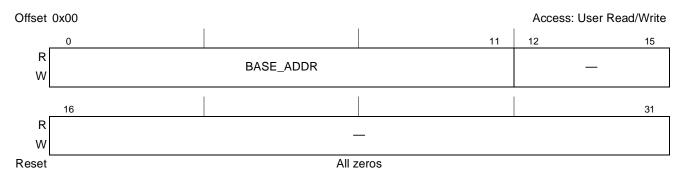

| 5.1.4               | Local Access Register Descriptions                               |                |

| 5.1.5               | Precedence of Local Access Windows                               |                |

| 5.1.6               | Configuring Local Access Windows                                 | 5-13           |

| 5.1.7               | Distinguishing Local Access Windows from Other Mapping Functions | 5-13           |

| 5.1.8               | Outbound Address Translation and Mapping Windows                 |                |

| 5.1.9               | Inbound Address Translation and Mapping Windows                  |                |

| 5.1.10              | Internal Memory Map                                              | 5-14           |

| 5.1.11              | Accessing Internal Memory from External Masters                  | 5-15           |

|                     | MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 0     |                |

iv Freescale Semiconductor

| Paragraph<br>Number | Title                                                                       | Page<br>Number |

|---------------------|-----------------------------------------------------------------------------|----------------|

| 5.2                 | System Configuration                                                        | 5-15           |

| 5.2.1               | System Configuration Register Memory Map                                    | 5-15           |

| 5.2.2               | System Configuration Registers                                              |                |

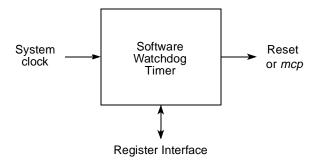

| 5.3                 | Software Watchdog Timer (WDT)                                               |                |

| 5.3.1               | WDT Overview                                                                |                |

| 5.3.2               | WDT Features                                                                |                |

| 5.3.3               | WDT Modes of Operation                                                      | 5-32           |

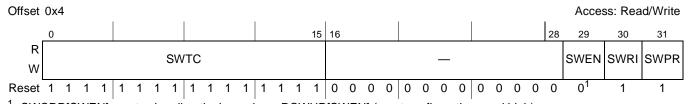

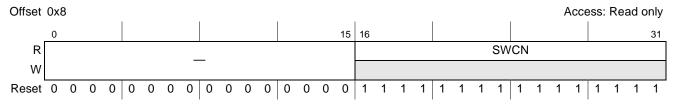

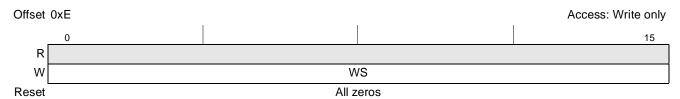

| 5.3.4               | WDT Memory Map/Register Definition                                          | 5-33           |

| 5.3.5               | Functional Description                                                      |                |

| 5.3.6               | Initialization/Application Information (WDT Programming Guidelines)         | 5-38           |

| 5.4                 | Real Time Clock (RTC) Module                                                |                |

| 5.4.1               | Overview                                                                    | 5-38           |

| 5.4.2               | Features                                                                    | 5-39           |

| 5.4.3               | Assumptions                                                                 | 5-39           |

| 5.4.4               | Modes of operation                                                          |                |

| 5.4.5               | External Signal Description                                                 | 5-40           |

| 5.4.6               | RTC Memory Map/Register Definition                                          |                |

| 5.4.7               | Functional Description                                                      | 5-44           |

| 5.4.8               | RTC Reset Sequence                                                          | 5-46           |

| 5.4.9               | RTC Initialization Sequence                                                 | 5-46           |

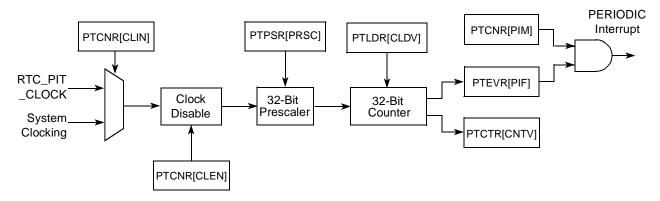

| 5.5                 | Periodic Interval Timer (PIT)                                               | 5-46           |

| 5.5.1               | PIT Overview                                                                | 5-46           |

| 5.5.2               | PIT Features                                                                | 5-47           |

| 5.5.3               | PIT Modes of Operation                                                      | 5-47           |

| 5.5.4               | PIT External Signal Description                                             | 5-47           |

| 5.5.5               | PIT Memory Map/Register Definition                                          | 5-48           |

| 5.5.6               | Functional Description                                                      | 5-51           |

| 5.5.7               | PIT Programming Guidelines                                                  | 5-52           |

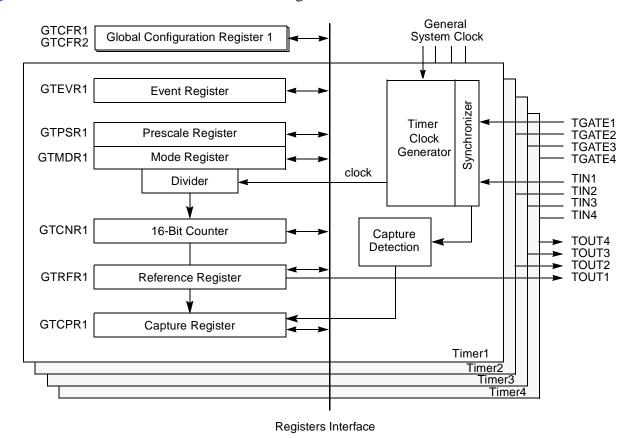

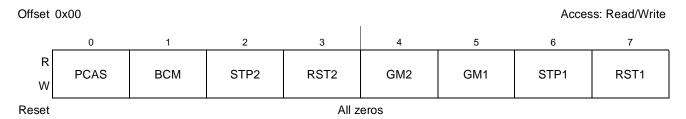

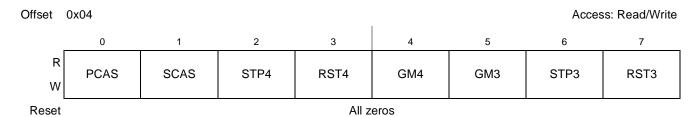

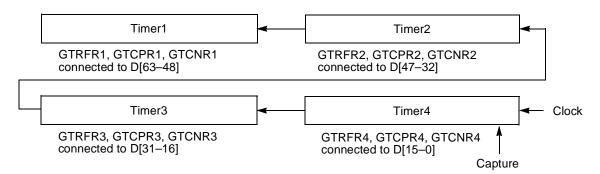

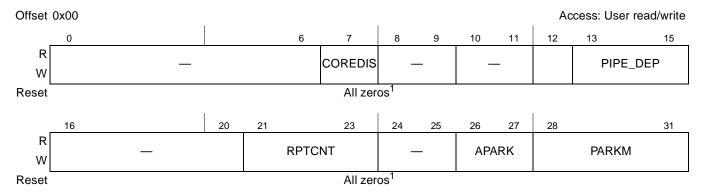

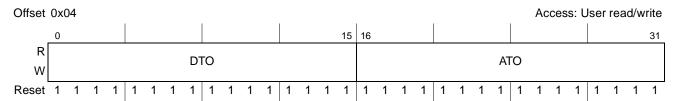

| 5.6                 | General-Purpose Timers (GTMs)                                               | 5-52           |

| 5.6.1               | GTM Overview                                                                | 5-52           |

| 5.6.2               | GTM Features                                                                | 5-53           |

| 5.6.3               | GTM Modes of Operation                                                      | 5-54           |

| 5.6.4               | GTM External Signal Description                                             |                |

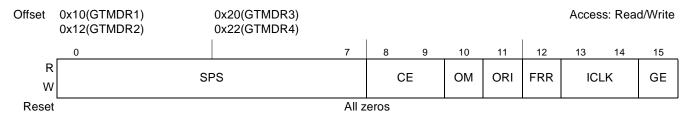

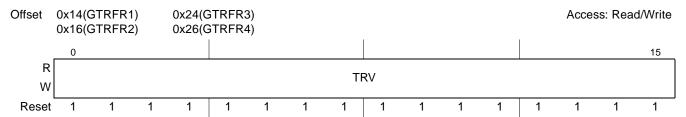

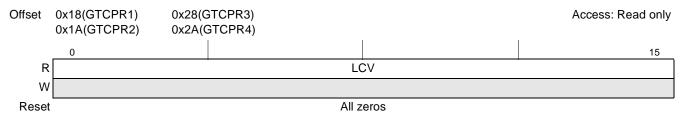

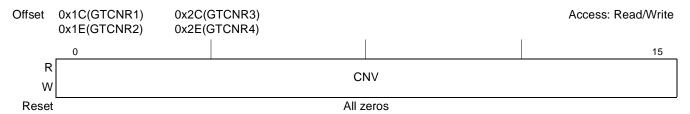

| 5.6.5               | GTM Memory Map/Register Definition                                          | 5-57           |

| 5.6.6               | Functional Description                                                      |                |

| 5.6.7               | Initialization/Application Information (Programming Guidelines for GTM 5-68 | Registers)     |

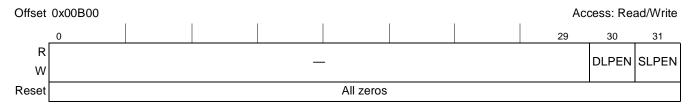

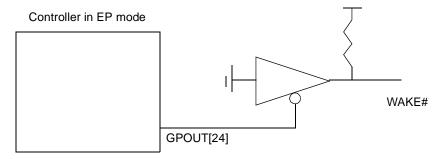

| 5.7                 | Power Management Control (PMC)                                              | 5-68           |

| 5.7.1               | External Signal Description                                                 |                |

| 5.7.2               | PMC Memory Map/Register Definition                                          | 5-69           |

| 5.7.3               | Functional Description                                                      | 5-70           |

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 0

| Number                                                                                                                               | n<br>Title                                                                                                                                                                                                                                                                                                                                                                                   | Page<br>Number     |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|                                                                                                                                      | Chapter 6                                                                                                                                                                                                                                                                                                                                                                                    |                    |

|                                                                                                                                      | Arbiter and Bus Monitor                                                                                                                                                                                                                                                                                                                                                                      |                    |

| 6.1                                                                                                                                  | Overview                                                                                                                                                                                                                                                                                                                                                                                     | 6-1                |

| 6.1.1                                                                                                                                | Coherent System Bus Overview                                                                                                                                                                                                                                                                                                                                                                 | 6-1                |

| 6.2                                                                                                                                  | Arbiter Memory Map/Register Definition                                                                                                                                                                                                                                                                                                                                                       | 6-2                |

| 6.2.1                                                                                                                                | Arbiter Configuration Register (ACR)                                                                                                                                                                                                                                                                                                                                                         | 6-3                |

| 6.2.2                                                                                                                                | Arbiter Timers Register (ATR)                                                                                                                                                                                                                                                                                                                                                                | 6-4                |

| 6.2.3                                                                                                                                | Arbiter Event Register (AER)                                                                                                                                                                                                                                                                                                                                                                 | 6-5                |

| 6.2.4                                                                                                                                | Arbiter Interrupt Definition Register (AIDR)                                                                                                                                                                                                                                                                                                                                                 | 6-6                |

| 6.2.5                                                                                                                                | Arbiter Mask Register (AMR)                                                                                                                                                                                                                                                                                                                                                                  | 6-7                |

| 6.2.6                                                                                                                                | Arbiter Event Attributes Register (AEATR)                                                                                                                                                                                                                                                                                                                                                    | 6-8                |

| 6.2.7                                                                                                                                | Arbiter Event Address Register (AEADR)                                                                                                                                                                                                                                                                                                                                                       | 6-9                |

| 6.2.8                                                                                                                                | Arbiter Event Response Register (AERR)                                                                                                                                                                                                                                                                                                                                                       | 6-10               |

| 6.3                                                                                                                                  | Functional Description                                                                                                                                                                                                                                                                                                                                                                       | 6-11               |

| 6.3.1                                                                                                                                | Arbitration Policy                                                                                                                                                                                                                                                                                                                                                                           | 6-11               |

| 6.3.2                                                                                                                                | Bus Error Detection                                                                                                                                                                                                                                                                                                                                                                          | 6-14               |

| 6.4                                                                                                                                  | Initialization/Applications Information                                                                                                                                                                                                                                                                                                                                                      | 6-17               |

|                                                                                                                                      | Initialization Cognones                                                                                                                                                                                                                                                                                                                                                                      | 6-17               |

| 6.4.1                                                                                                                                | Initialization Sequence                                                                                                                                                                                                                                                                                                                                                                      | 0 17               |

|                                                                                                                                      | Error Handling Sequence                                                                                                                                                                                                                                                                                                                                                                      |                    |

| 6.4.1                                                                                                                                | Error Handling Sequence                                                                                                                                                                                                                                                                                                                                                                      |                    |

| 6.4.1                                                                                                                                | Error Handling Sequence                                                                                                                                                                                                                                                                                                                                                                      |                    |

| 6.4.1                                                                                                                                | Error Handling Sequence                                                                                                                                                                                                                                                                                                                                                                      | 6-17               |

| 6.4.1<br>6.4.2                                                                                                                       | Error Handling Sequence                                                                                                                                                                                                                                                                                                                                                                      | 6-17               |

| 6.4.1<br>6.4.2<br>7.1                                                                                                                | Error Handling Sequence                                                                                                                                                                                                                                                                                                                                                                      | 6-17<br>7-1<br>7-3 |

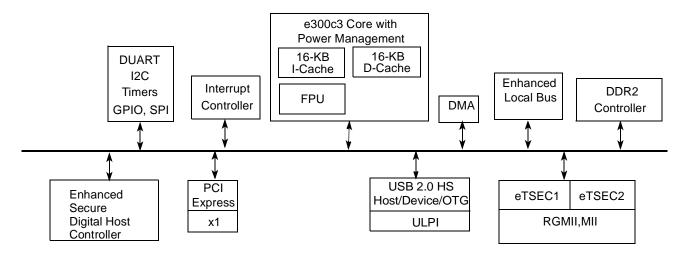

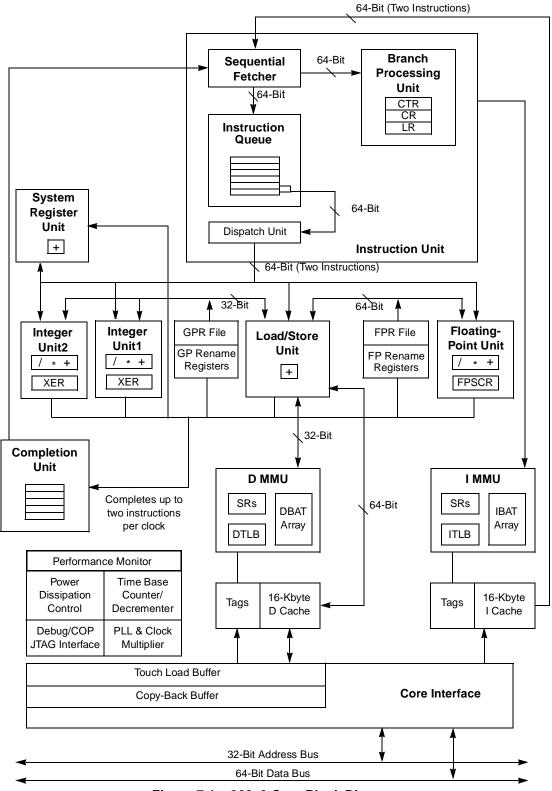

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1                                                                                                       | Chapter 7 e300 Processor Core Overview  Overview                                                                                                                                                                                                                                                                                                                                             |                    |

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2                                                                                              | Chapter 7 e300 Processor Core Overview  Overview  Features                                                                                                                                                                                                                                                                                                                                   |                    |

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3                                                                                     | Chapter 7 e300 Processor Core Overview  Overview                                                                                                                                                                                                                                                                                                                                             |                    |

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4                                                                            | Chapter 7 e300 Processor Core Overview  Overview  Features Instruction Unit Independent Execution Units Completion Unit                                                                                                                                                                                                                                                                      |                    |

| 7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5                                                                                     | Chapter 7 e300 Processor Core Overview  Overview                                                                                                                                                                                                                                                                                                                                             |                    |

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6                                                          | Chapter 7 e300 Processor Core Overview  Overview  Features Instruction Unit Independent Execution Units Completion Unit Memory Subsystem Support Bus Interface Unit (BIU)                                                                                                                                                                                                                    |                    |

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7                                                 | Chapter 7 e300 Processor Core Overview  Overview                                                                                                                                                                                                                                                                                                                                             |                    |

| 7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7                                                                   | Chapter 7 e300 Processor Core Overview  Overview                                                                                                                                                                                                                                                                                                                                             |                    |

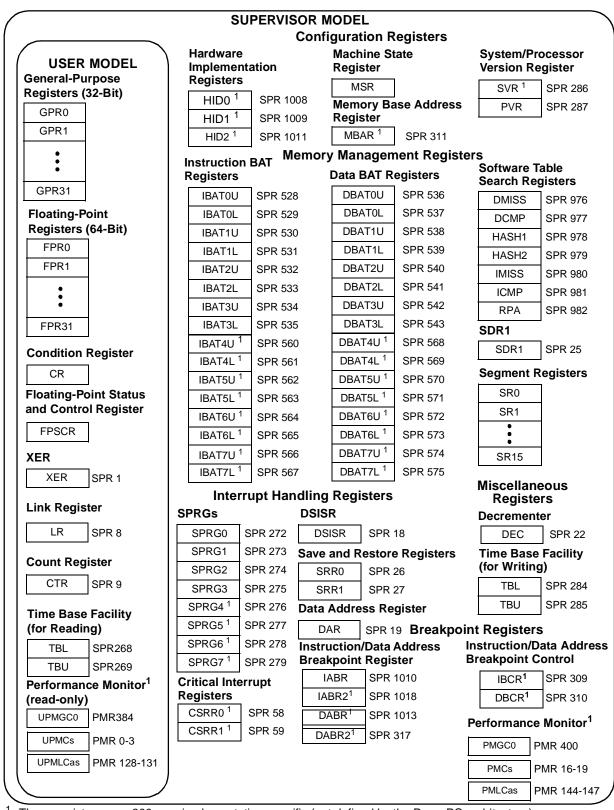

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7<br>7.2<br>7.3                                   | Chapter 7 e300 Processor Core Overview  Overview  Features Instruction Unit Independent Execution Units Completion Unit Memory Subsystem Support Bus Interface Unit (BIU) System Support Functions e300 Processor and System Version Numbers PowerPC Architecture Implementation                                                                                                             |                    |

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7<br>7.2<br>7.3<br>7.4                            | Chapter 7 e300 Processor Core Overview  Overview                                                                                                                                                                                                                                                                                                                                             |                    |

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7<br>7.2<br>7.3<br>7.4<br>7.4.1                   | Chapter 7 e300 Processor Core Overview  Overview                                                                                                                                                                                                                                                                                                                                             |                    |

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2          | Chapter 7 e300 Processor Core Overview  Overview                                                                                                                                                                                                                                                                                                                                             |                    |

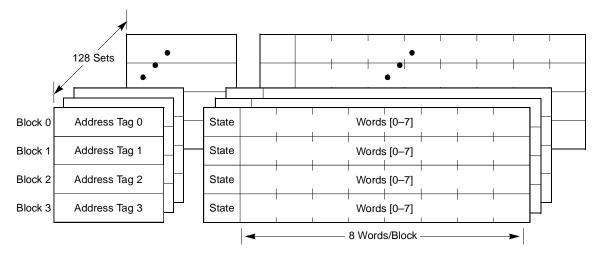

| 6.4.1<br>6.4.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3 | Chapter 7 e300 Processor Core Overview  Overview Features Instruction Unit Independent Execution Units Completion Unit Memory Subsystem Support Bus Interface Unit (BIU) System Support Functions e300 Processor and System Version Numbers PowerPC Architecture Implementation Implementation-Specific Information Register Model Instruction Set and Addressing Modes Cache Implementation |                    |

vi Freescale Semiconductor

| Paragraph<br>Number | Title                                                             | Page<br>Number |

|---------------------|-------------------------------------------------------------------|----------------|

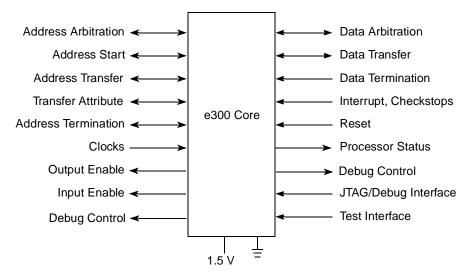

| 7.4.7               | Core Interface                                                    | 7-37           |

| 7.4.8               | Debug Features                                                    | 7-39           |

| 7.5                 | Differences Between Cores                                         | 7-40           |

|                     | Chapter 8                                                         |                |

|                     | Integrated Programmable Interrupt Controller (IPIC)               |                |

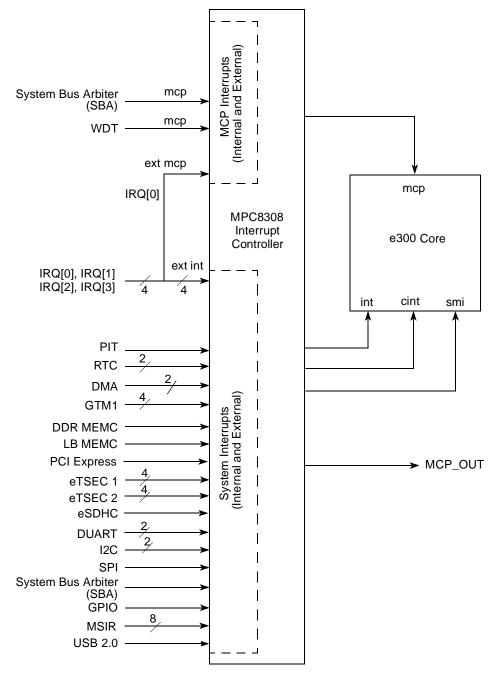

| 8.1                 | Introduction                                                      | 8-1            |

| 8.2                 | Features                                                          | 8-4            |

| 8.3                 | Modes of Operation                                                | 8-4            |

| 8.3.1               | Core Enable Mode                                                  | 8-4            |

| 8.3.2               | Core Disable Mode                                                 | 8-4            |

| 8.4                 | External Signal Description                                       | 8-5            |

| 8.4.1               | Overview                                                          | 8-5            |

| 8.4.2               | Detailed Signal Descriptions                                      | 8-5            |

| 8.5                 | Memory Map/Register Definition                                    |                |

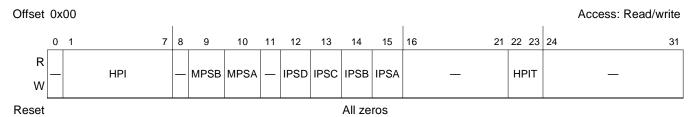

| 8.5.1               | System Global Interrupt Configuration Register (SICFR)            | 8-7            |

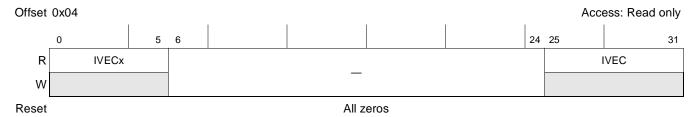

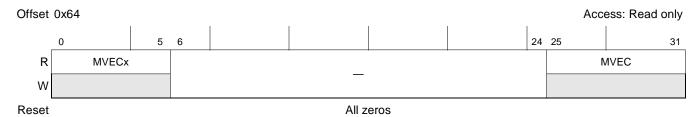

| 8.5.2               | System Global Interrupt Vector Register (SIVCR)                   | 8-8            |

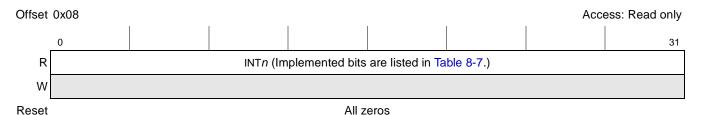

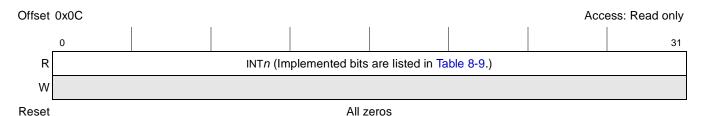

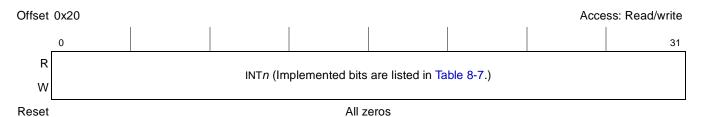

| 8.5.3               | System Internal Interrupt Pending Registers (SIPNR_H and SIPNR_L) | 8-11           |

| 8.5.4               | System Internal Interrupt Group A Priority Register (SIPRR_A)     | 8-13           |

| 8.5.5               | System Internal Interrupt Group B Priority Register (SIPRR_B)     | 8-14           |

| 8.5.6               | System Internal Interrupt Group C Priority Register (SIPRR_C)     | 8-15           |

| 8.5.7               | System Internal Interrupt Group D Priority Register (SIPRR_D)     | 8-16           |

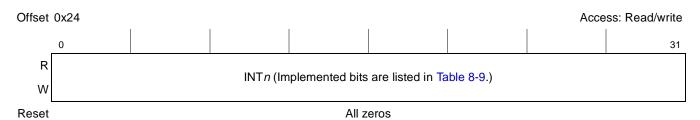

| 8.5.8               | System Internal Interrupt Mask Register (SIMSR_H and SIMSR_L)     | 8-16           |

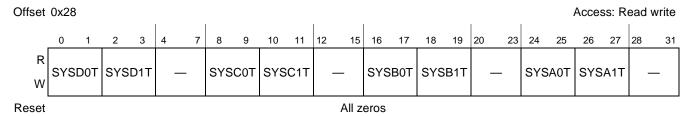

| 8.5.9               | System Internal Interrupt Control Register (SICNR)                | 8-18           |

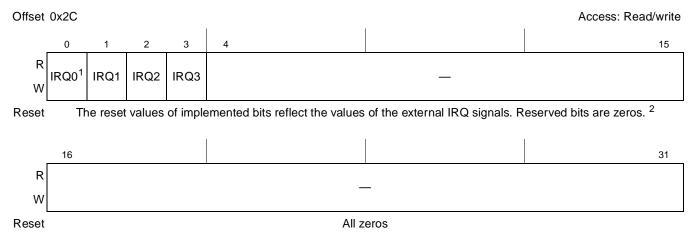

| 8.5.10              | System External Interrupt Pending Register (SEPNR)                | 8-20           |

| 8.5.11              | System Mixed Interrupt Group A Priority Register (SMPRR_A)        | 8-20           |

| 8.5.12              | System Mixed Interrupt Group B Priority Register (SMPRR_B)        | 8-21           |

| 8.5.13              | System External Interrupt Mask Register (SEMSR)                   | 8-22           |

| 8.5.14              | System External Interrupt Control Register (SECNR)                | 8-23           |

| 8.5.15              | System Error Status Register (SERSR)                              | 8-24           |

| 8.5.16              | System Error Mask Register (SERMR)                                | 8-25           |

| 8.5.17              | System Error Control Register (SERCR)                             | 8-26           |

| 8.5.18              | System External interrupt Polarity Control Register (SEPCR)       | 8-26           |

| 8.5.19              | System Internal Interrupt Force Registers (SIFCR_H and SIFCR_L)   | 8-27           |

| 8.5.20              | System External Interrupt Force Register (SEFCR)                  | 8-28           |

| 8.5.21              | System Error Force Register (SERFR)                               | 8-29           |

| 8.5.22              | System Critical Interrupt Vector Register (SCVCR)                 | 8-29           |

| 8.5.23              | System Management Interrupt Vector Register (SMVCR)               | 8-30           |

| 8.6                 | Functional Description                                            | 8-31           |

| 8.6.1               | Interrupt Types                                                   | 8-31           |

|                     |                                                                   |                |

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 0

Freescale Semiconductor vii

| Paragraph |                                             | rage   |

|-----------|---------------------------------------------|--------|

| Number    | Title                                       | Number |

| 8.6.2     | Interrupt Configuration                     | 8-32   |

| 8.6.3     | Internal Interrupts Group Relative Priority | 8-33   |

| 8.6.4     | Mixed Interrupts Group Relative Priority    | 8-33   |

| 8.6.5     | Highest Priority Interrupt                  | 8-34   |

| 8.6.6     | Interrupt Source Priorities                 | 8-34   |

| 8.6.7     | Masking Interrupt Sources                   | 8-38   |

| 8.6.8     | Interrupt Vector Generation and Calculation | 8-39   |

| 8.6.9     | Machine Check Interrupts                    | 8-39   |

| 8.7       | Message Shared Interrupts                   | 8-40   |

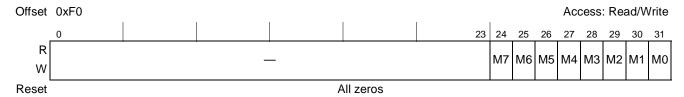

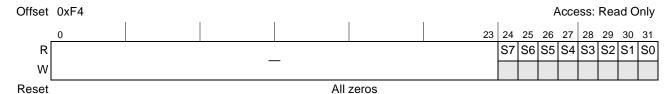

| 8.7.1     | Memory Map/Register Definition              | 8-40   |

| 8.7.2     | Message Shared Registers                    | 8-40   |

|           | Chapter 9                                   |        |

|           | DDR Memory Controller                       |        |

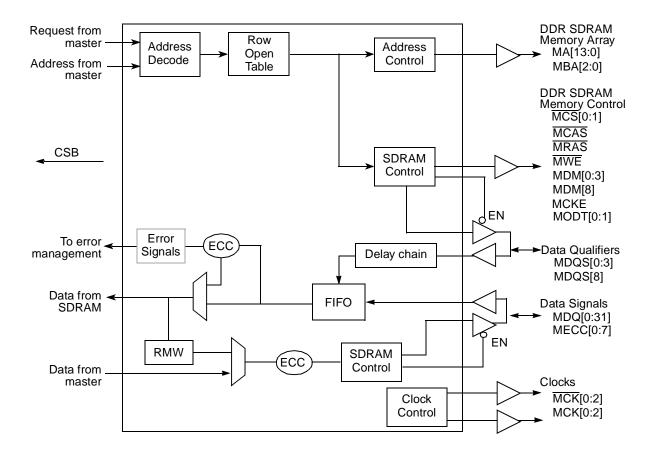

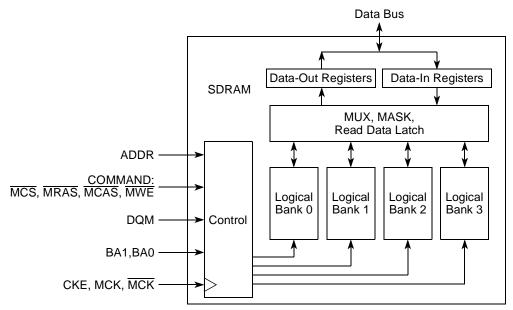

| 9.1       | Introduction                                |        |

| 9.2       | Features                                    |        |

| 9.2.1     | Modes of Operation                          |        |

| 9.3       | External Signal Descriptions                |        |

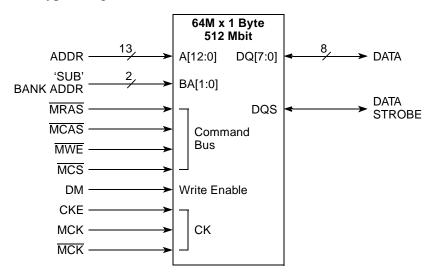

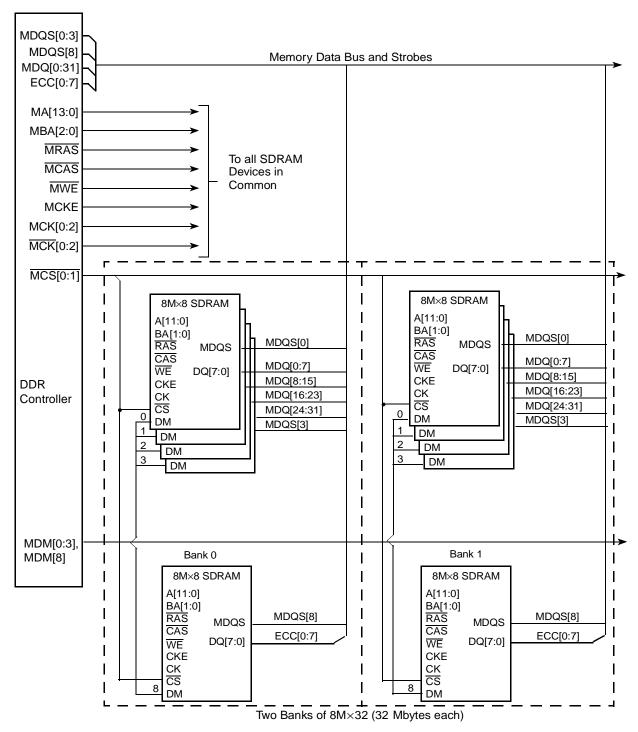

| 9.3.1     | Signals Overview                            | 9-3    |

| 9.3.2     | Detailed Signal Descriptions                | 9-6    |

| 9.4       | Memory Map/Register Definition              | 9-9    |

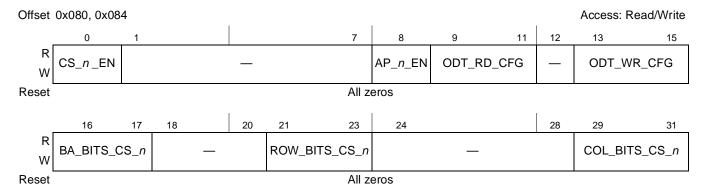

| 9.4.1     | Register Descriptions                       | 9-10   |

| 9.5       | Functional Description.                     |        |

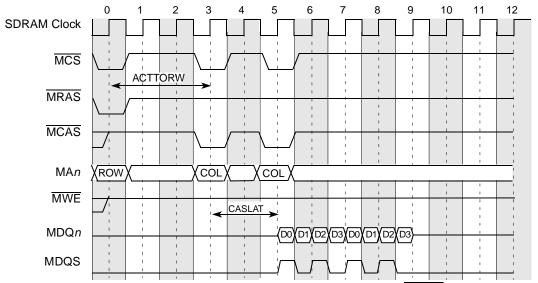

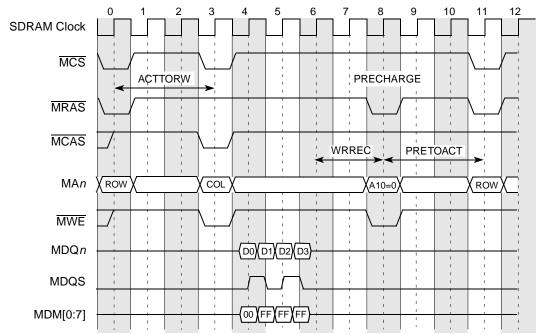

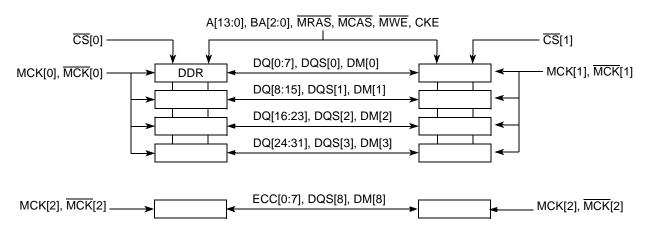

| 9.5.1     | DDR SDRAM Interface Operation               |        |

| 9.5.2     | DDR SDRAM Address Multiplexing              | 9-42   |

| 9.5.3     | JEDEC Standard DDR SDRAM Interface Commands | 9-44   |

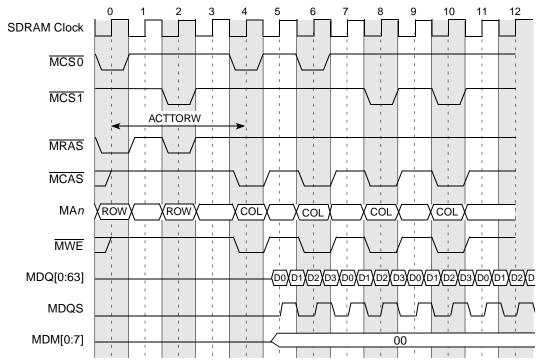

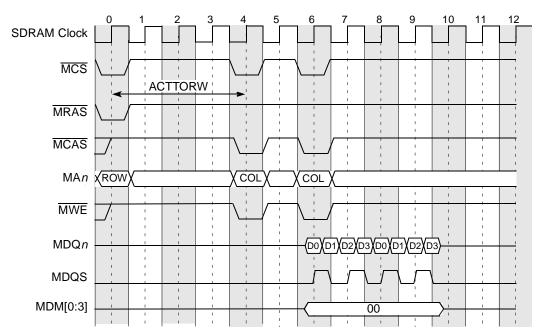

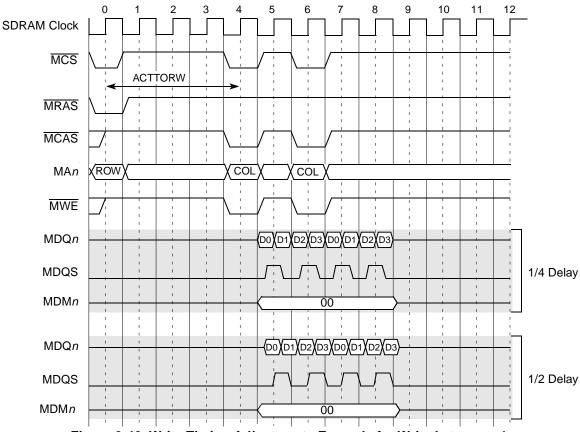

| 9.5.4     | DDR SDRAM Interface Timing                  | 9-46   |

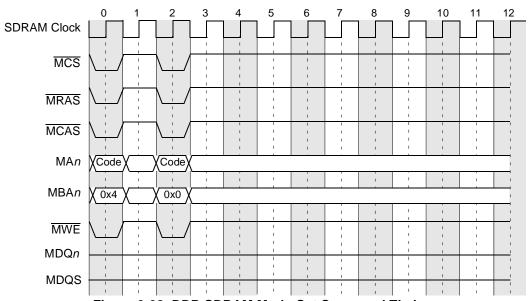

| 9.5.5     | DDR SDRAM Mode-Set Command Timing           | 9-50   |

| 9.5.6     | DDR SDRAM Registered DIMM Mode              |        |

| 9.5.7     | DDR SDRAM Write Timing Adjustments          | 9-51   |

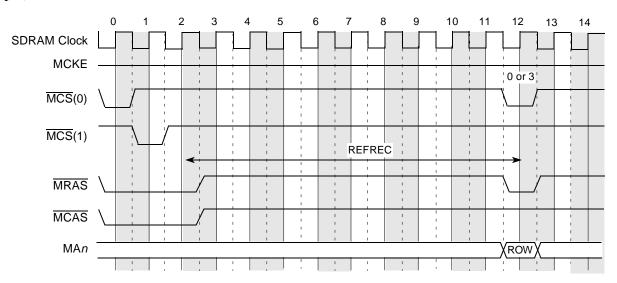

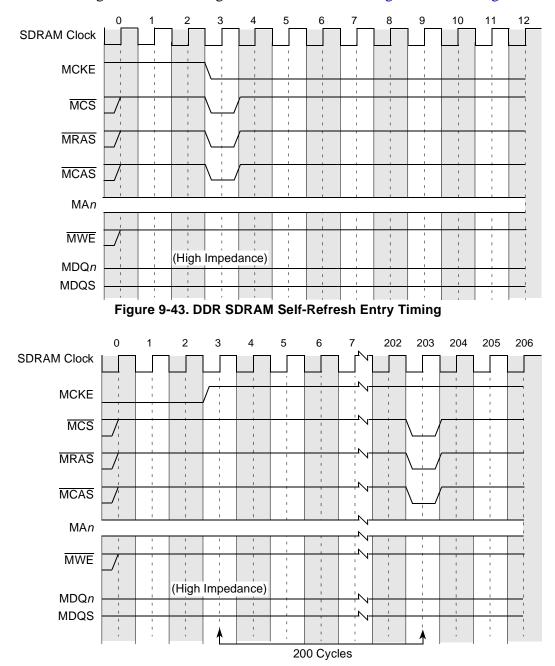

| 9.5.8     | DDR SDRAM Refresh                           | 9-52   |

| 9.5.9     | DDR Data Beat Ordering                      | 9-55   |

| 9.5.10    | Page Mode and Logical Bank Retention        | 9-56   |

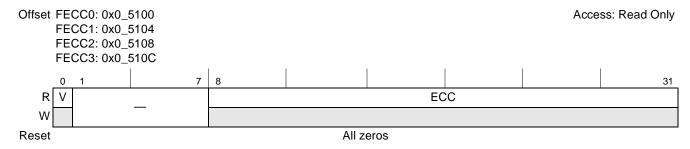

| 9.5.11    | Error Checking and Correcting (ECC)         | 9-57   |

| 9.5.12    | Error Management                            |        |

| 9.6       | Initialization/Application Information      | 9-59   |

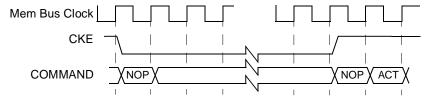

| 9.6.1     | DDR SDRAM Initialization Sequence           | 9-61   |

|           |                                             |        |

#### Chapter 10 Enhanced Local Bus Controller

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 0

viii Freescale Semiconductor

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

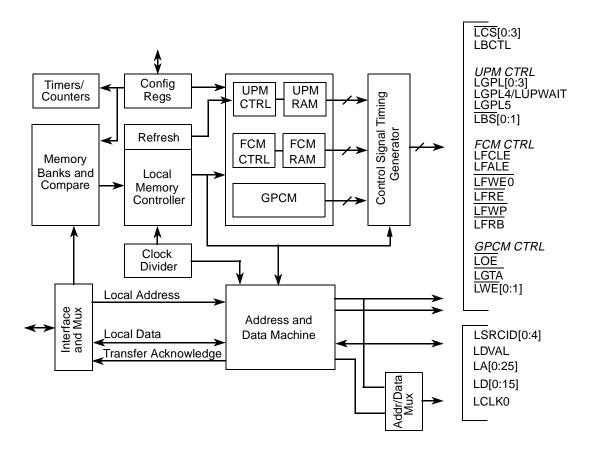

| 10.1                | Introduction                                          | 10-1           |

| 10.1.1              | Overview                                              | 10-2           |

| 10.1.2              | Features                                              | 10-2           |

| 10.1.3              | Modes of Operation                                    | 10-3           |

| 10.2                | External Signal Descriptions                          | 10-4           |

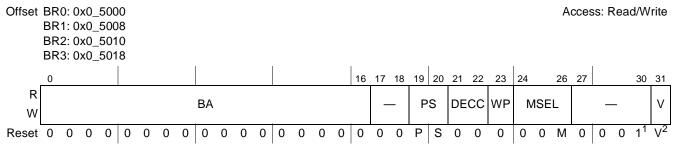

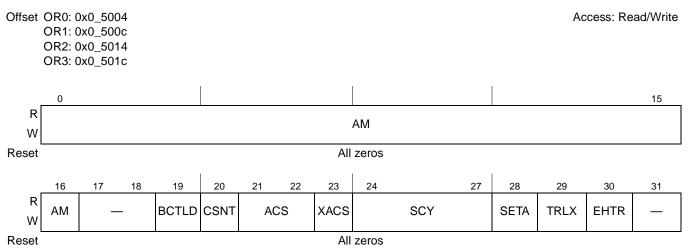

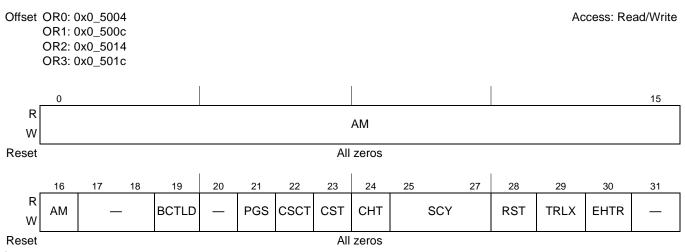

| 10.3                | Memory Map/Register Definition                        | 10-7           |

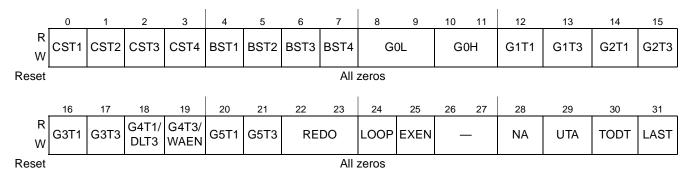

| 10.3.1              | Register Descriptions                                 | 10-8           |

| 10.4                | Functional Description                                | 10-39          |

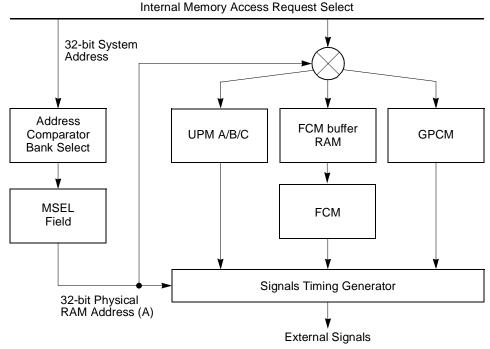

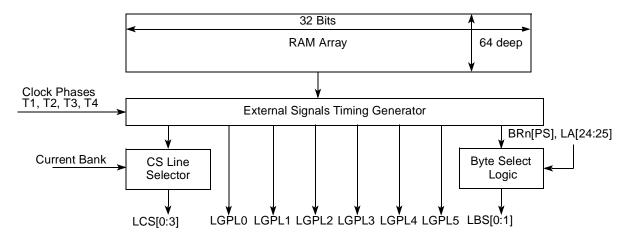

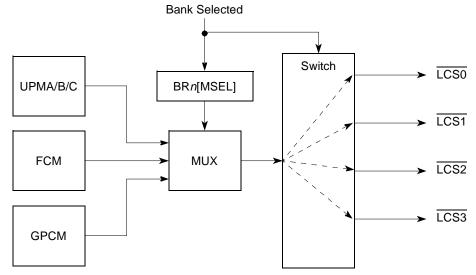

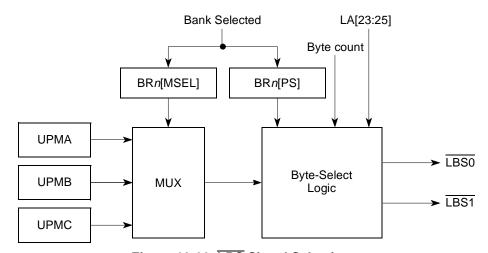

| 10.4.1              | Basic Architecture                                    | 10-40          |

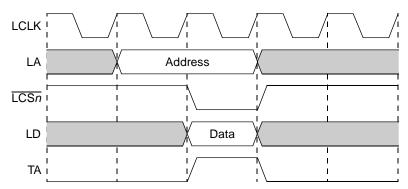

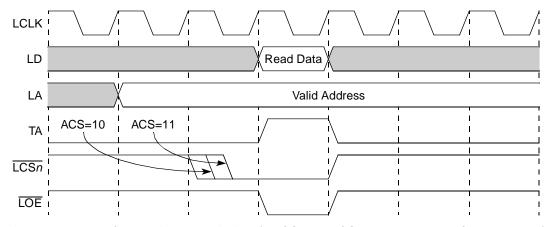

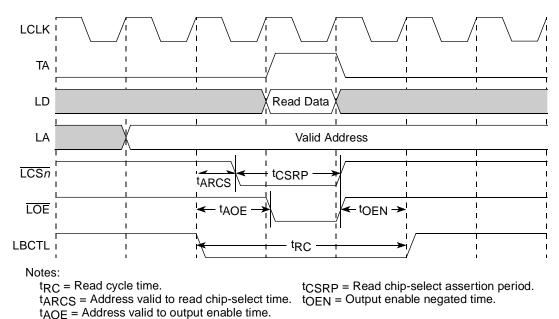

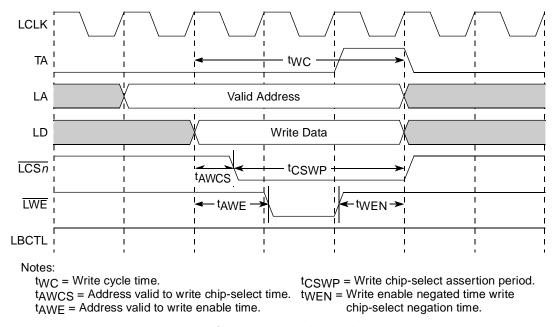

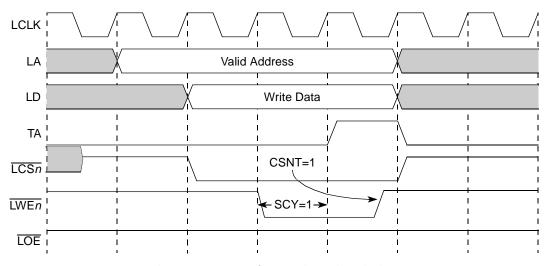

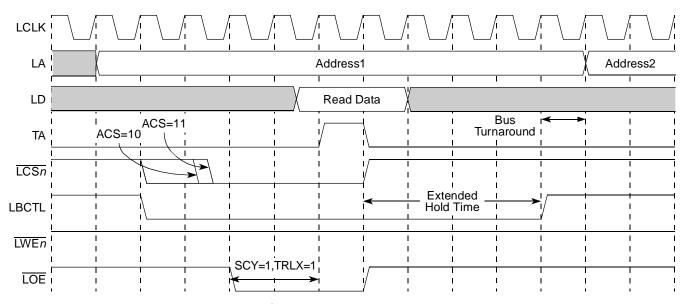

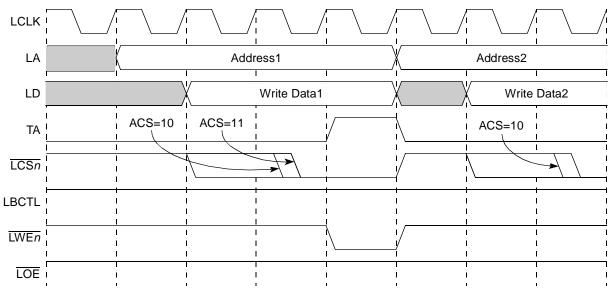

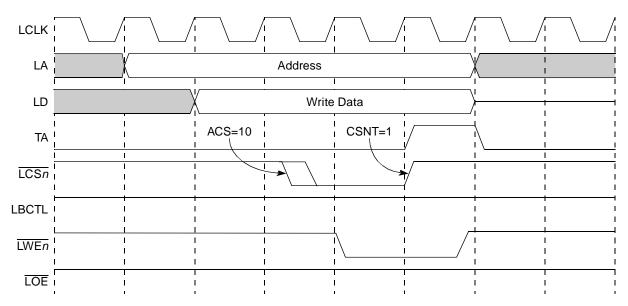

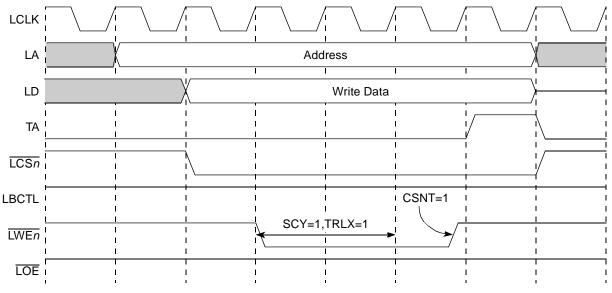

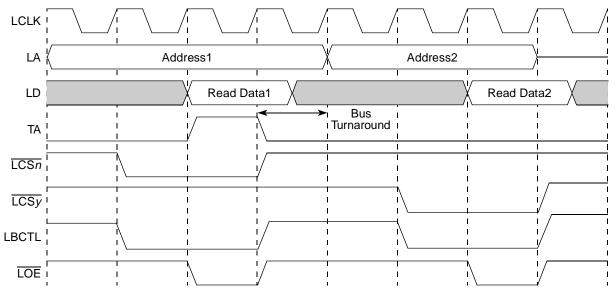

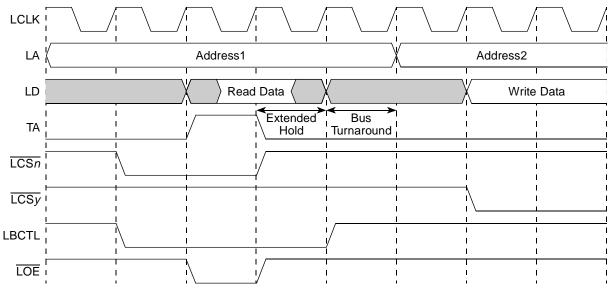

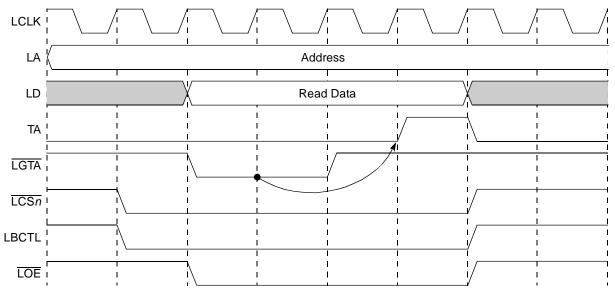

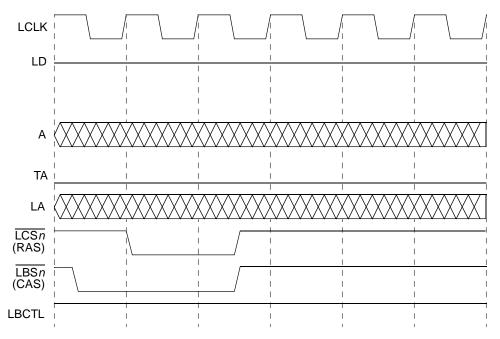

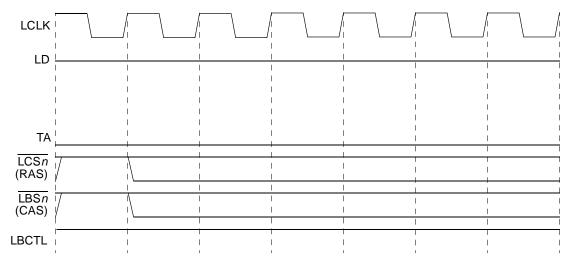

| 10.4.2              | General-Purpose Chip-Select Machine (GPCM)            | 10-42          |

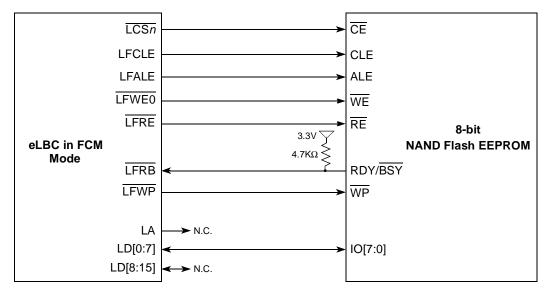

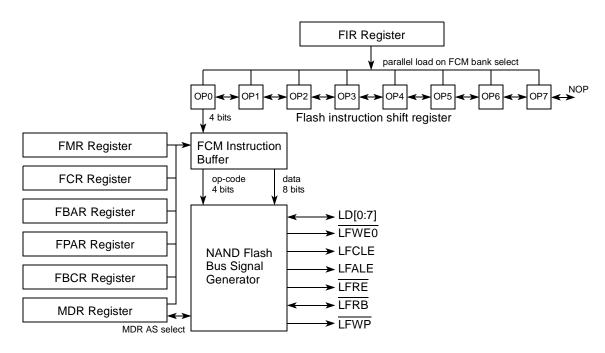

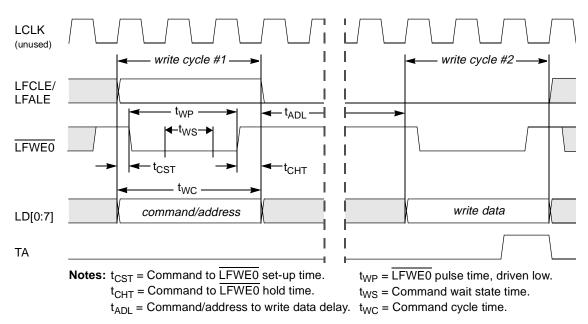

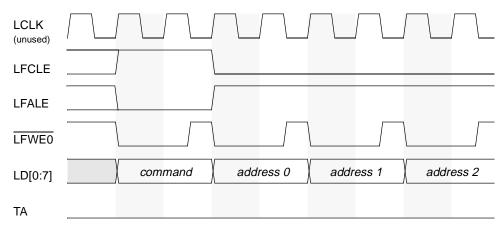

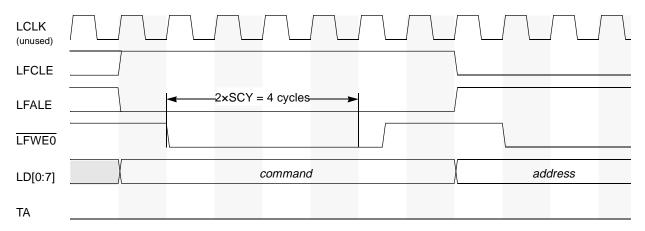

| 10.4.3              | Flash Control Machine (FCM)                           | 10-53          |

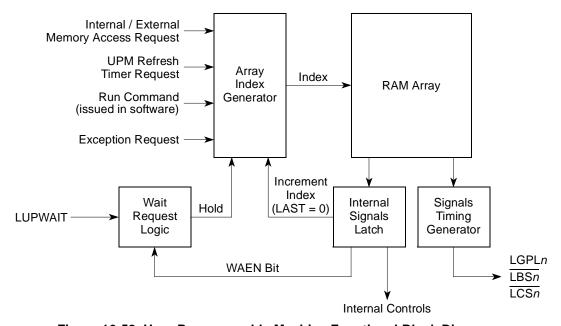

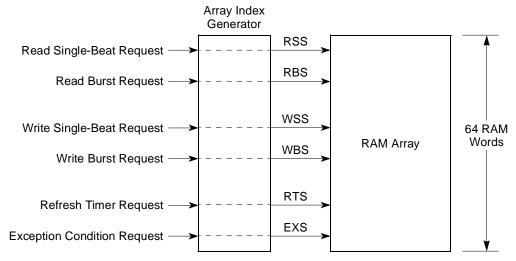

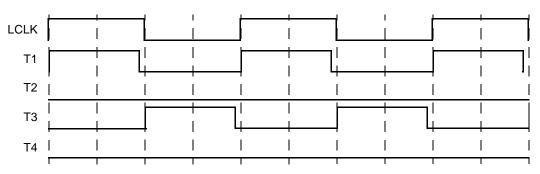

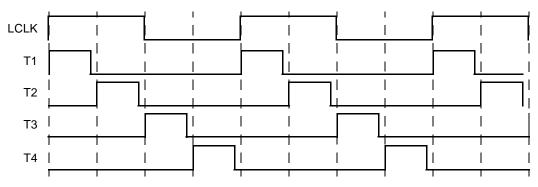

| 10.4.4              | User-Programmable Machines (UPMs)                     | 10-68          |

| 10.5                | Initialization/Application Information                | 10-82          |

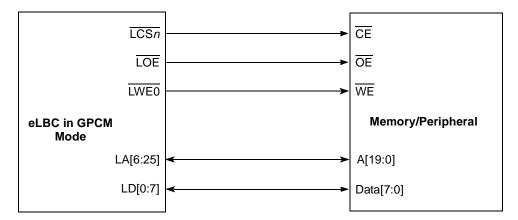

| 10.5.1              | Interfacing to Peripherals in Different Address Modes | 10-82          |

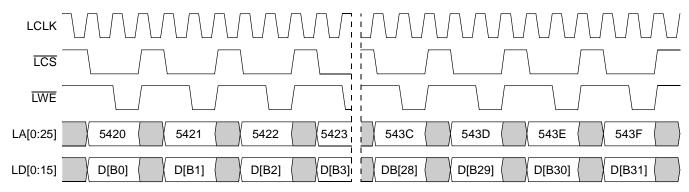

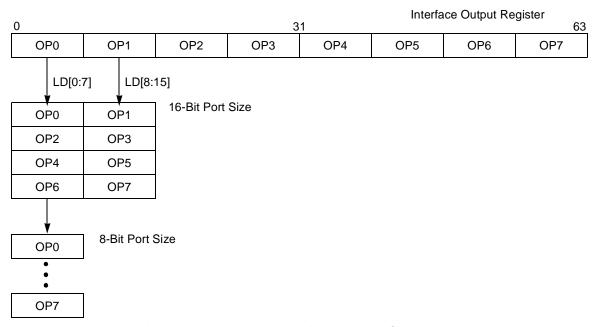

| 10.5.2              | Interface to Different Port-Size Devices              |                |

| 10.5.3              | Command Sequence Examples for NAND Flash EEPROM       | 10-84          |

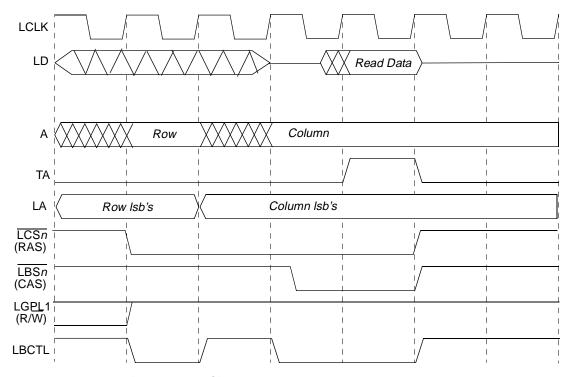

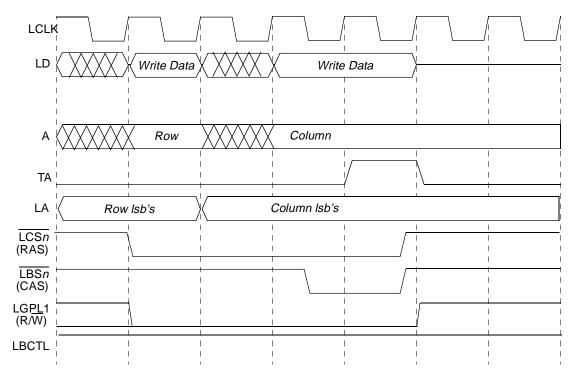

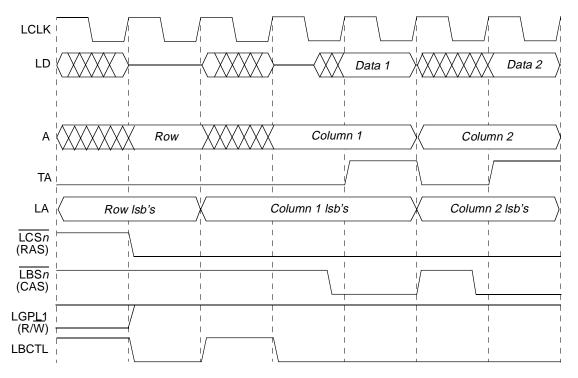

| 10.5.4              | Interfacing to Fast-Page Mode DRAM Using UPM          |                |

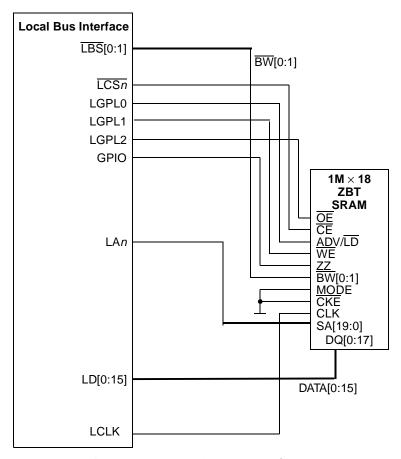

| 10.5.5              | Interfacing to ZBT SRAM Using UPM                     | 10-98          |

|                     | Chapter 11                                            |                |

|                     | Enhanced Secure Digital Host Controller               |                |

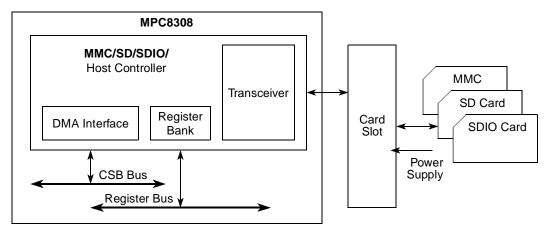

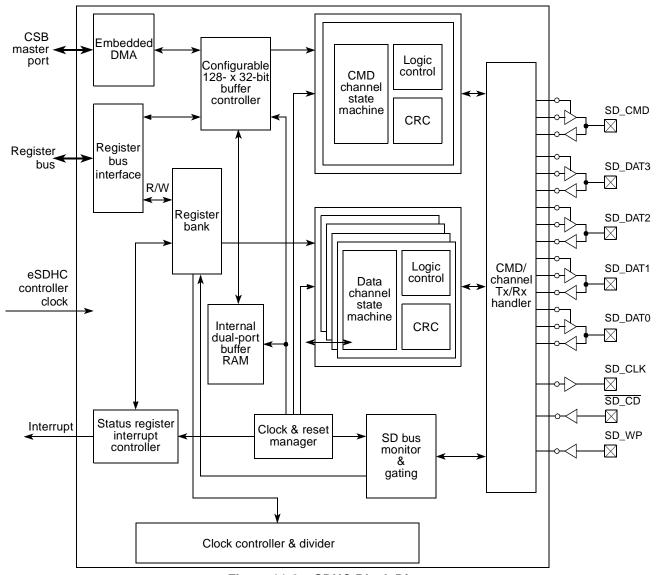

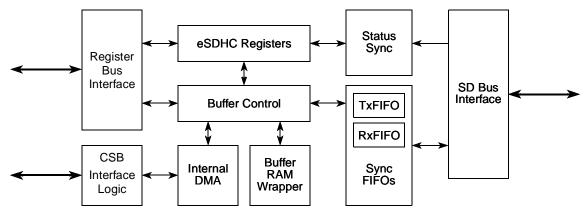

| 11.1                | Overview                                              | 11-1           |

| 11.2                | Features                                              |                |

| 11.2.1              | Data Transfer Modes                                   |                |

| 11.3                | External Signal Description                           |                |

| 11.4                | Memory Map/Register Definition                        |                |

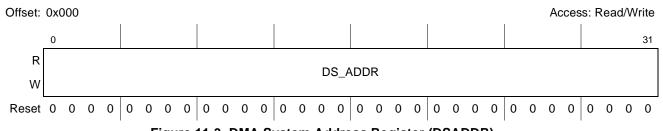

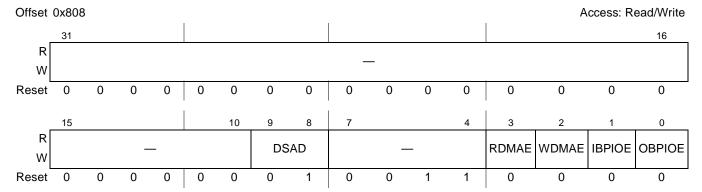

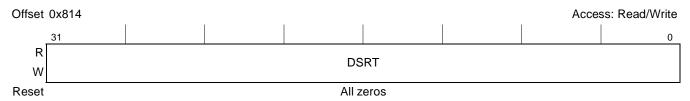

| 11.4.1              | DMA System Address Register (DSADDR)                  |                |

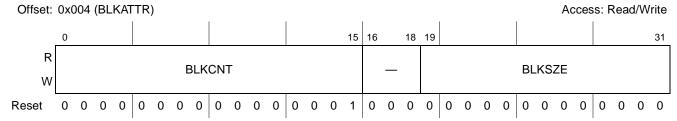

| 11.4.2              | Block Attributes Register (BLKATTR)                   |                |

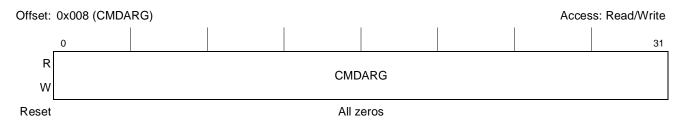

| 11.4.3              | Command Argument Register (CMDARG)                    |                |

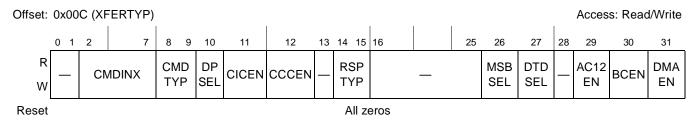

| 11.4.4              | Transfer Type Register (XFERTYP)                      |                |

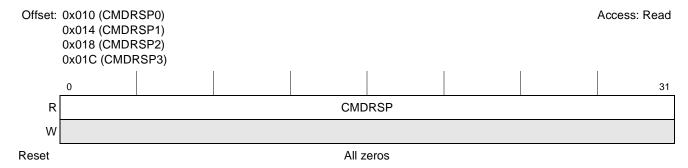

| 11.4.5              | Command Response 0–3 (CMDRSP0–3)                      |                |

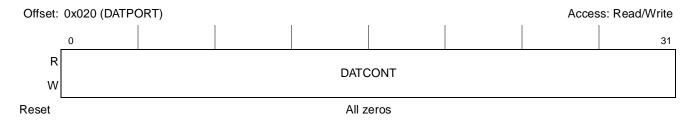

| 11.4.6              | Buffer Data Port Register (DATPORT)                   |                |

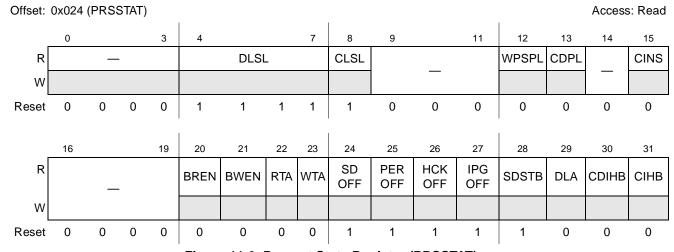

| 11.4.7              | Present State Register (PRSSTAT)                      |                |

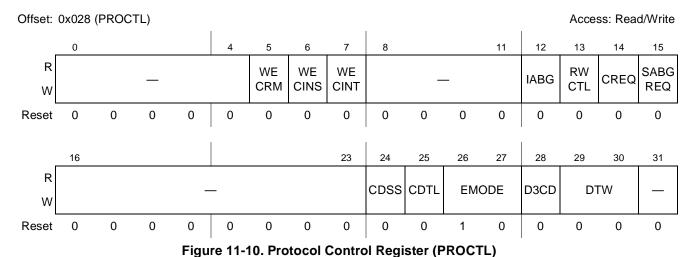

| 11.4.8              | Protocol Control Register (PROCTL)                    |                |

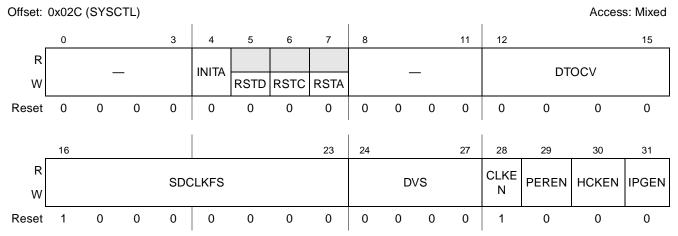

| 11.4.9              | System Control Register (SYSCTL)                      |                |

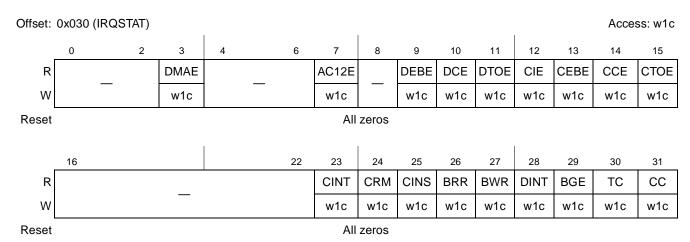

| 11.4.10             | Interrupt Status Register (IRQSTAT)                   |                |

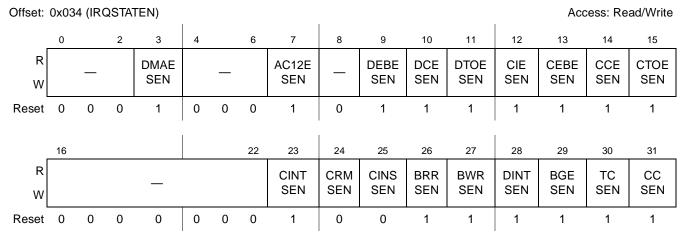

| 11.4.11             | Interrupt Status Enable Register (IRQSTATEN)          |                |

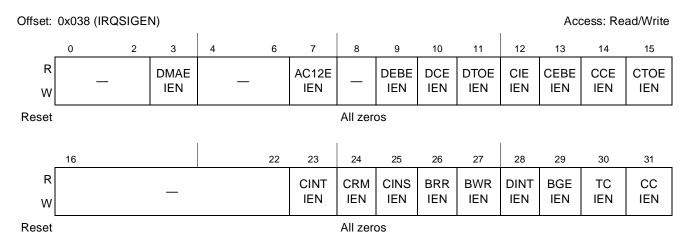

| 11.4.12             | Interrupt Signal Enable Register (IRQSIGEN)           |                |

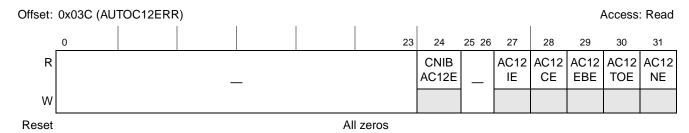

| 11.4.13             | Auto CMD12 Error Status Register (AUTOC12ERR)         |                |

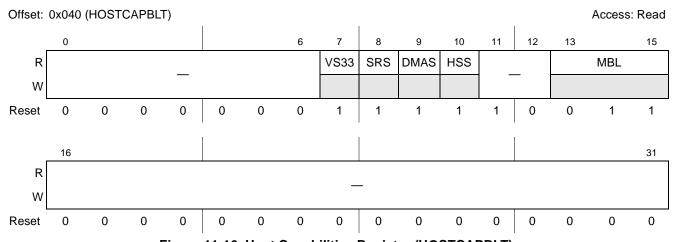

| 11.4.14             | Host Controller Capabilities (HOSTCAPBLT)             |                |

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 0

Freescale Semiconductor ix

| Paragraph |                                                   | Page   |

|-----------|---------------------------------------------------|--------|

| Number    | Title                                             | Number |

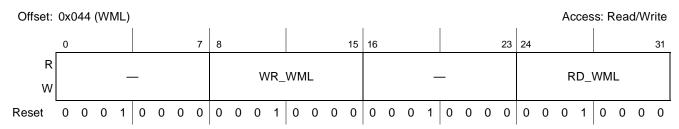

| 11.4.15   | Watermark Level Register (WML)                    | 11-35  |

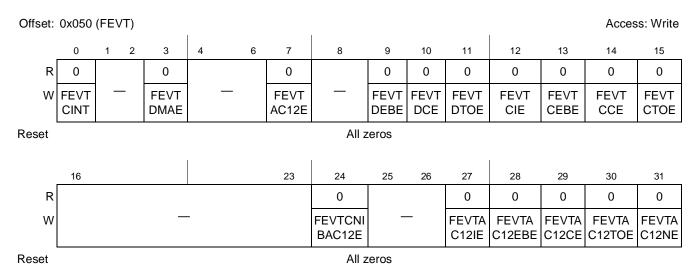

| 11.4.16   | Force Event Register (FEVT)                       | 11-35  |

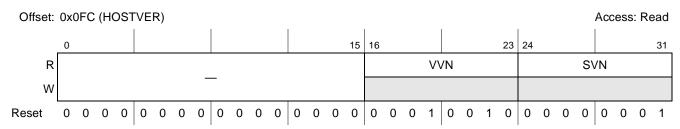

| 11.4.17   | Host Controller Version Register (HOSTVER)        | 11-37  |

| 11.4.18   | DMA Control Register (DCR)                        | 11-37  |

| 11.5      | Functional Description                            | 11-37  |

| 11.5.1    | Data Buffer                                       | 11-38  |

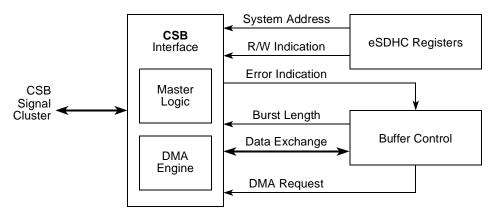

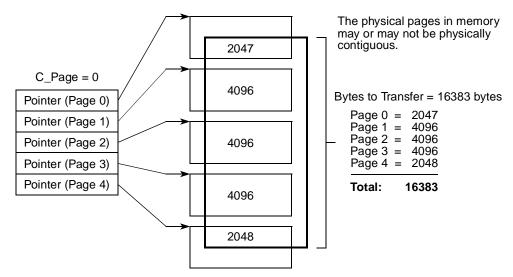

| 11.5.2    | DMA CSB Interface                                 | 11-40  |

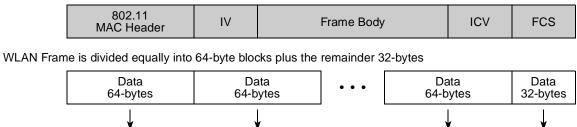

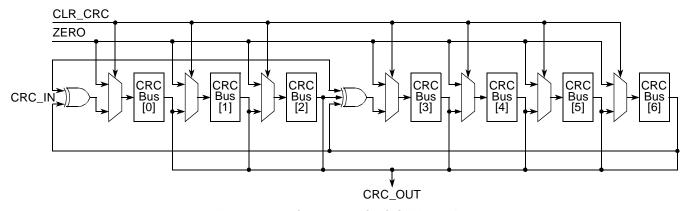

| 11.5.3    | SD Protocol Unit                                  | 11-41  |

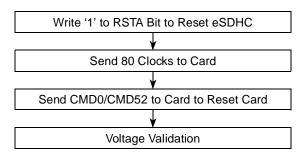

| 11.5.4    | Clock & Reset Manager                             | 11-43  |

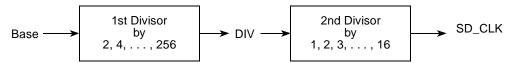

| 11.5.5    | Clock Generator                                   | 11-43  |

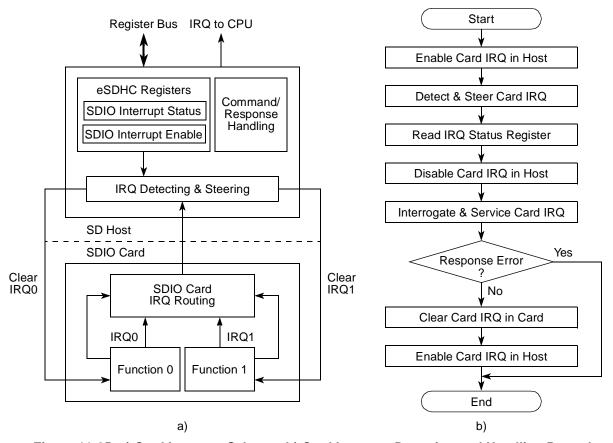

| 11.5.6    | SDIO Card Interrupt                               | 11-43  |

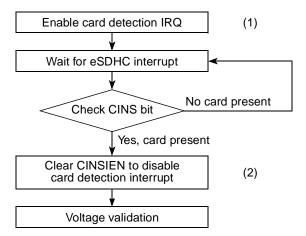

| 11.5.7    | Card Insertion and Removal Detection              | 11-45  |

| 11.5.8    | Power Management                                  | 11-45  |

| 11.6      | Initialization/Application Information            | 11-46  |

| 11.6.1    | Command Send and Response Receive Basic Operation | 11-46  |

| 11.6.2    | Card Identification Mode                          | 11-47  |

| 11.6.3    | Card Access                                       | 11-51  |

| 11.6.4    | Switch Function                                   | 11-56  |

| 11.6.5    | Commands for MMC/SD/SDIO                          | 11-59  |

| 11.7      | Software Restrictions                             | 11-64  |

| 11.7.1    | Initialization Active                             | 11-64  |

| 11.7.2    | Software Polling Procedure                        |        |

| 11.7.3    | Suspend Operation                                 | 11-64  |

| 11.7.4    | Data Port Access                                  | 11-64  |

| 11.7.5    | Multi-block Read                                  | 11-64  |

|           | Chapter 12                                        |        |

|           | <b>DMA Controller (DMAC)</b>                      |        |

| 12.1      | Overview                                          |        |

| 12.1.1    | Features                                          |        |

| 12.2      | DMAC Memory Map/Register Definition               |        |

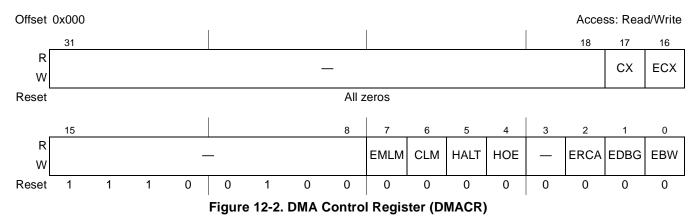

| 12.2.1    | DMA Control Register (DMACR)                      |        |

| 12.3      | DMA Error Status (DMAES)                          |        |

| 12.3.1    | DMA Enable Error Interrupt Register (DMAEEI)      |        |

| 12.3.2    | DMA Set Enable Error Interrupt (DMASEEI)          |        |

| 12.3.3    | DMA Clear Enable Error Interrupt (DMACEEI)        |        |

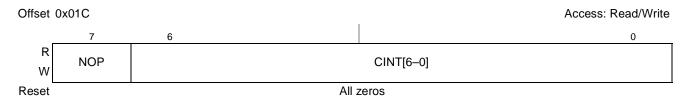

| 12.3.4    | DMA Clear Interrupt Request (DMACINT)             |        |

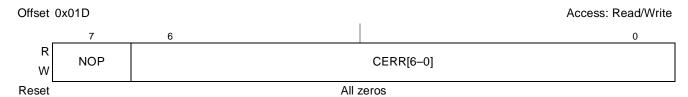

| 12.3.5    | DMA Clear Error (DMACERR)                         |        |

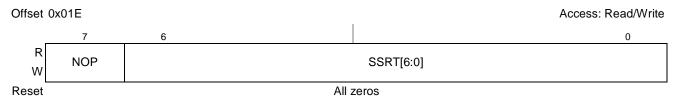

| 12.3.6    | DMA Set START Bit (DMASSRT)                       |        |

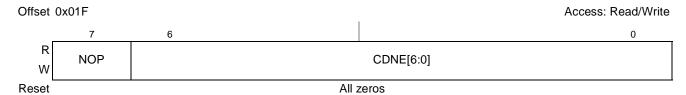

| 12.3.7    | DMA Clear DONE Status (DMACDNE)                   | 12-12  |

|           |                                                   |        |

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 0

x Freescale Semiconductor

| Paragraph<br>Number | Title                                                        | Page<br>Number |

|---------------------|--------------------------------------------------------------|----------------|

| 12.3.8              | DMA Interrupt Request Register (DMAINT)                      | 12-12          |

| 12.3.9              | DMA Error Register (DMAERR)                                  |                |

| 12.3.10             | DMA General Purpose Output Register (DMAGPOR)                | 12-14          |

| 12.3.11             | DMA Channel <i>n</i> Priority (DCHPRI <i>n</i> ), $n = 0-15$ | 12-15          |

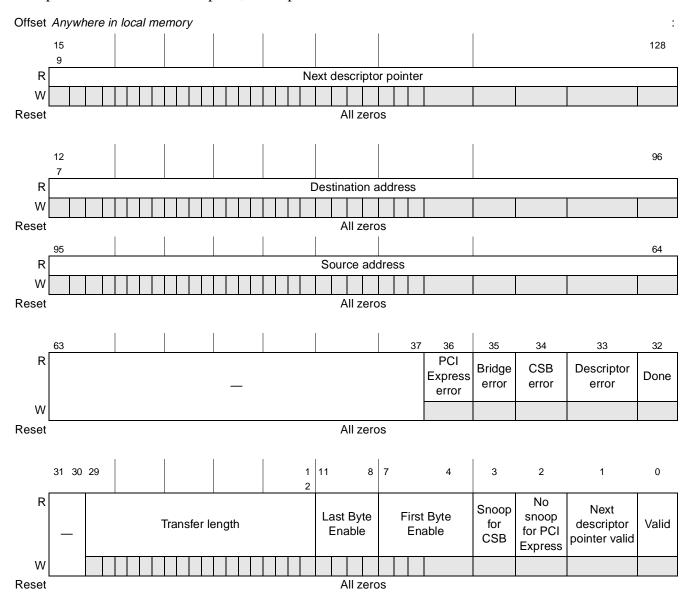

| 12.3.12             | Transfer Control Descriptor (TCD)                            | 12-16          |

| 12.4                | Functional Description                                       | 12-24          |

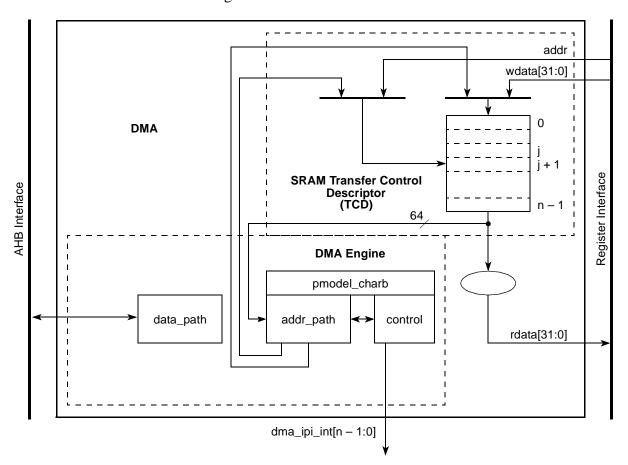

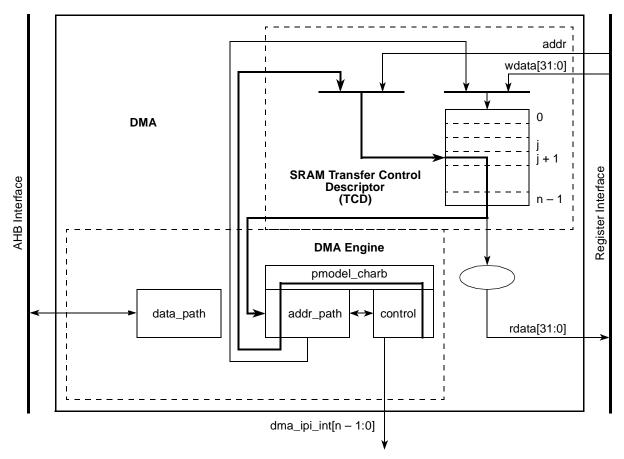

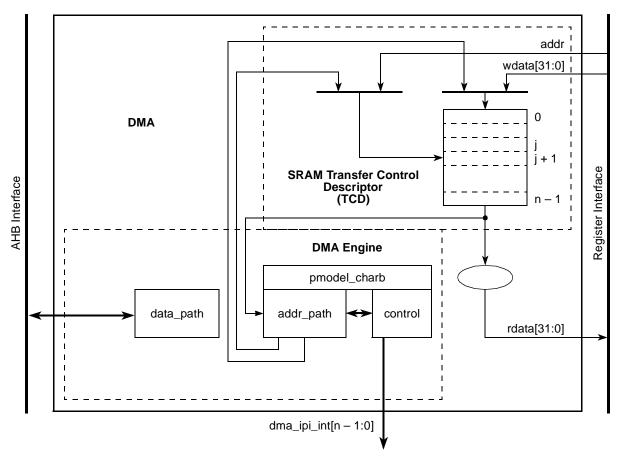

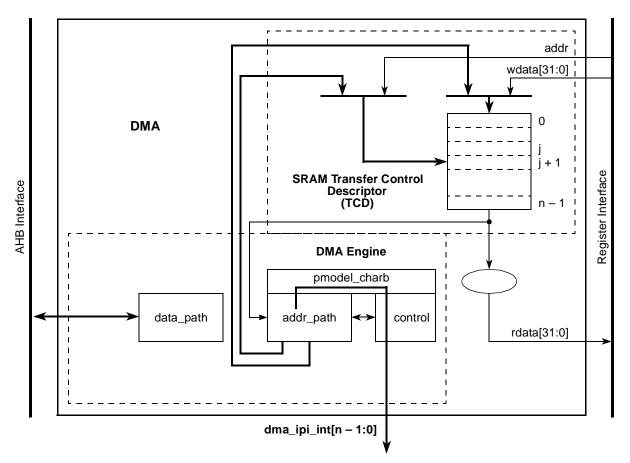

| 12.4.1              | DMA Microarchitecture                                        | 12-24          |

| 12.4.2              | DMA Basic Data Flow                                          | 12-25          |

| 12.5                | Initialization/Application Information                       | 12-28          |

| 12.5.1              | DMA Initialization                                           | 12-28          |

| 12.5.2              | DMA Programming Errors                                       | 12-29          |

| 12.6                | DMA Transfer                                                 | 12-29          |

| 12.6.1              | Single Request                                               | 12-29          |

| 12.6.2              | Multiple Requests                                            | 12-30          |

| 12.7                | TCD Status                                                   |                |

| 12.7.1              | Minor Loop Complete                                          | 12-32          |

| 12.7.2              | Active Channel TCD Reads                                     | 12-32          |

| 12.7.3              | Preemption status                                            | 12-32          |

| 12.8                | Channel Linking                                              | 12-33          |

| 12.9                | Programming during channel execution                         | 12-33          |

| 12.9.1              | Dynamic priority changing                                    | 12-33          |

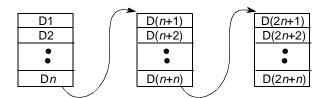

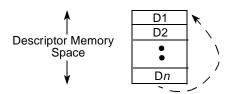

| 12.9.2              | Dynamic channel linking and dynamic scatter/gather           | 12-34          |

|                     | Chapter 13<br>Universal Serial Bus Interface                 |                |

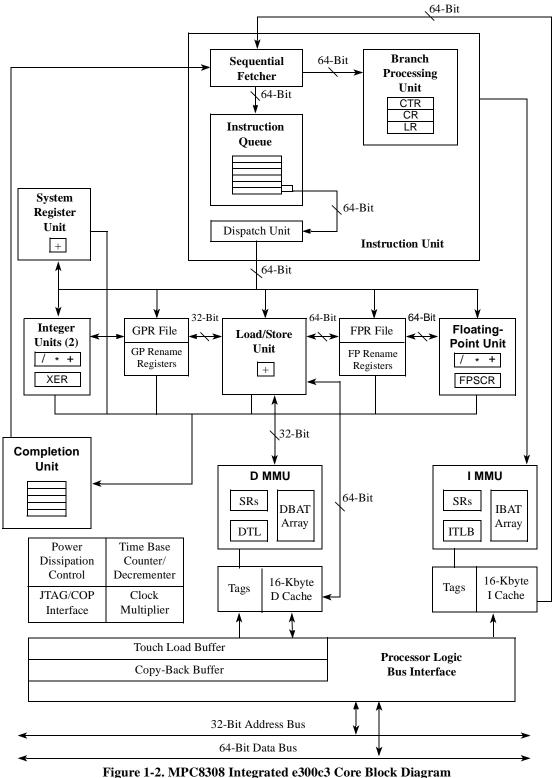

| 13.1                | Introduction                                                 | 13-1           |

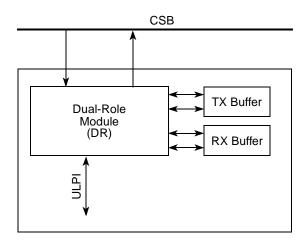

| 13.1.1              | Overview                                                     |                |

| 13.1.2              | Features                                                     |                |

| 13.1.3              | Modes of Operation                                           |                |

| 13.2                | External Signals                                             |                |

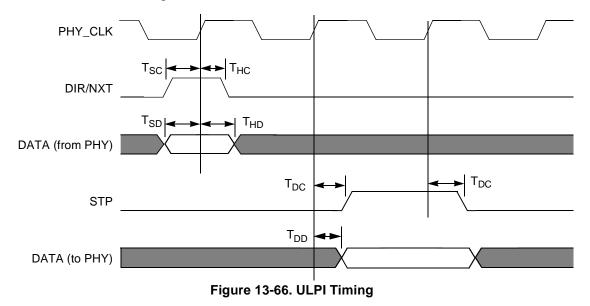

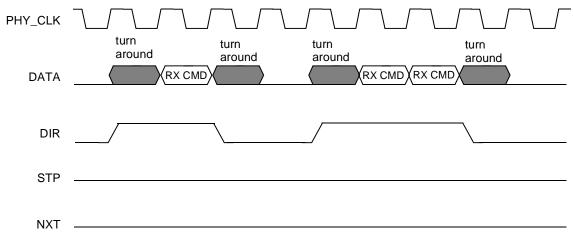

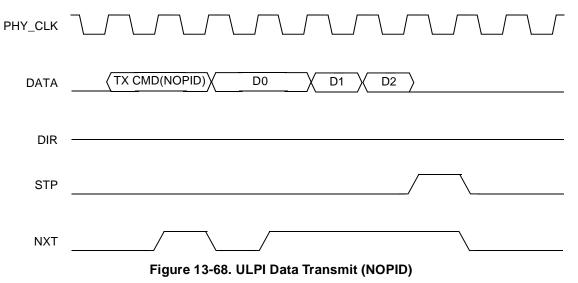

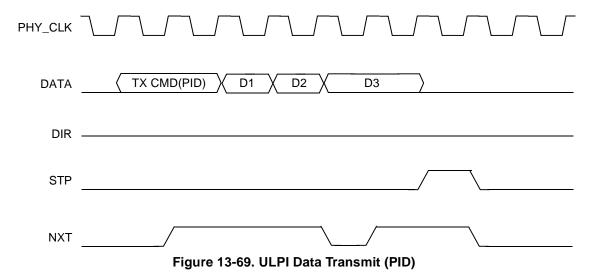

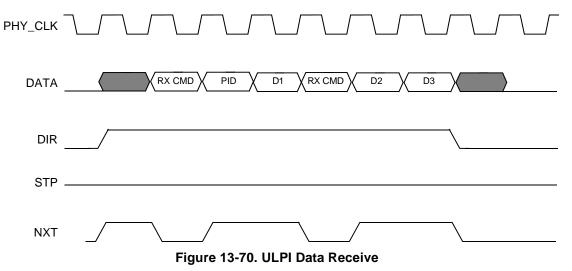

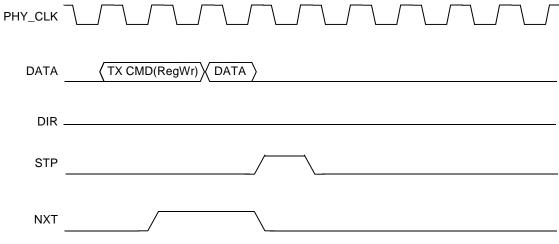

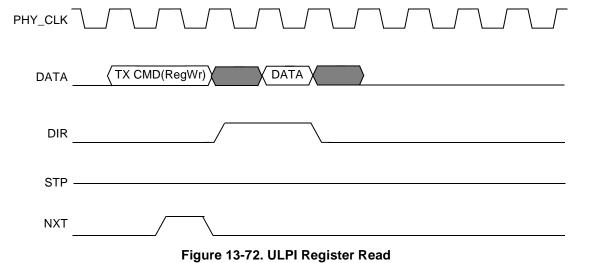

| 13.2.1              | ULPI Interface                                               | 13-3           |

| 13.3                | Memory Map/Register Definitions                              |                |

| 13.3.1              | Capability Registers                                         |                |

| 13.3.2              | Operational Registers                                        |                |

| 13.4                | Functional Description                                       | 13-44          |

| 13.4.1              | System Interface                                             | 13-44          |

| 13.4.2              | DMA Engine                                                   |                |

| 13.4.3              | FIFO RAM Controller                                          |                |

| 13.4.4              | PHY Interface                                                | 13-45          |

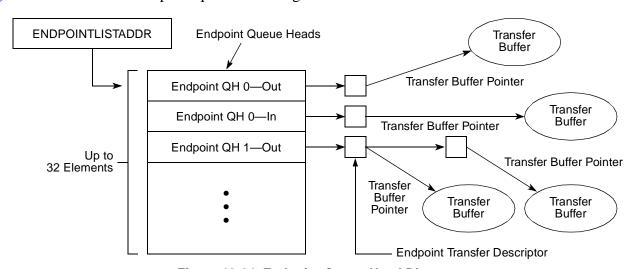

| 13.5                | Host Data Structures                                         | 13-46          |

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 0

Freescale Semiconductor xi

| Title                                                       | Page<br>Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

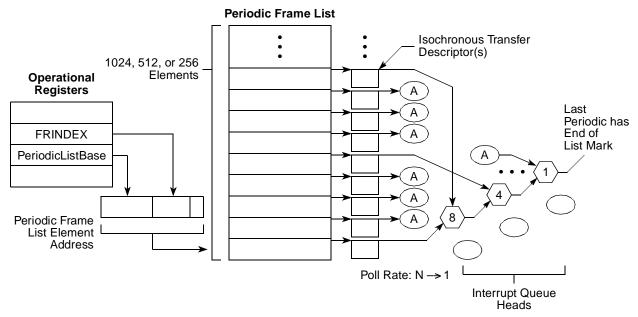

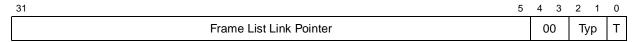

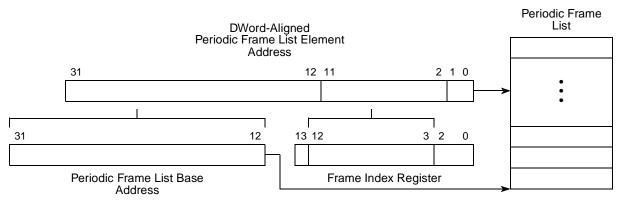

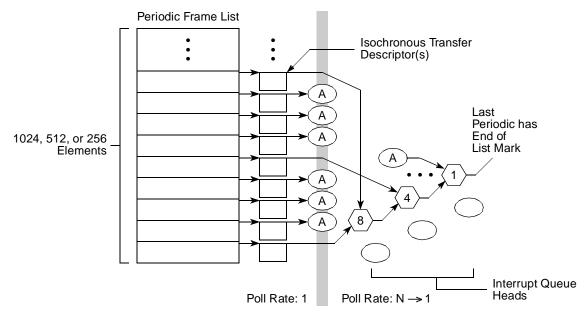

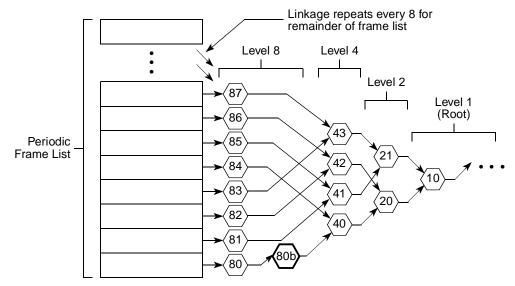

| Periodic Frame List                                         | 13-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

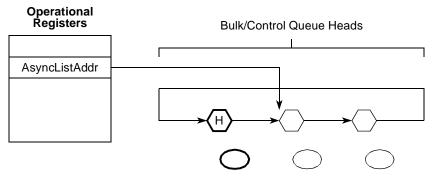

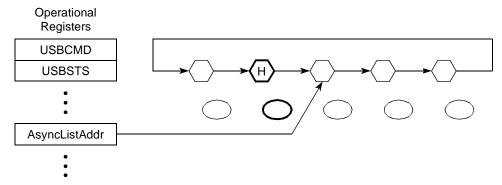

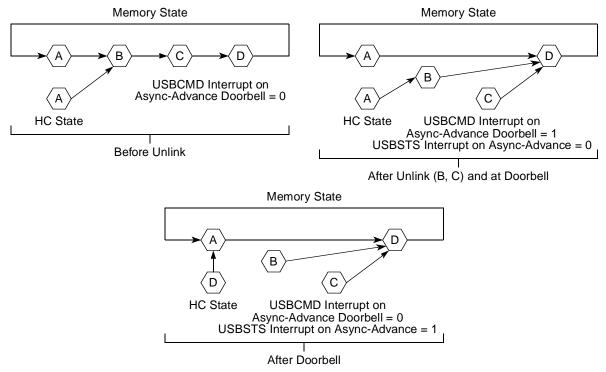

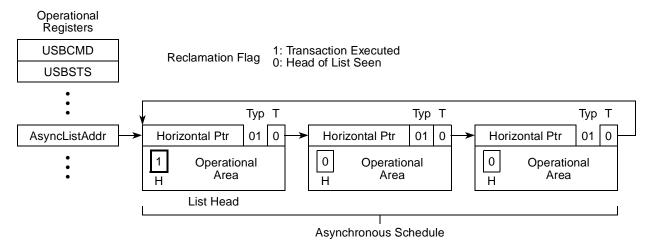

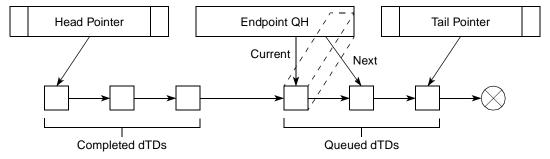

| Asynchronous List Queue Head Pointer                        | 13-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

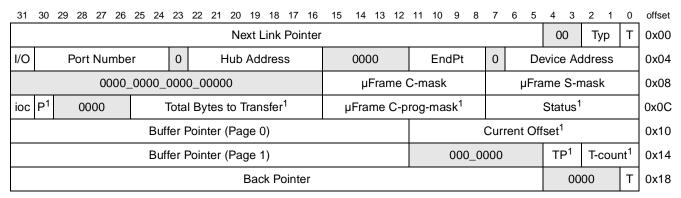

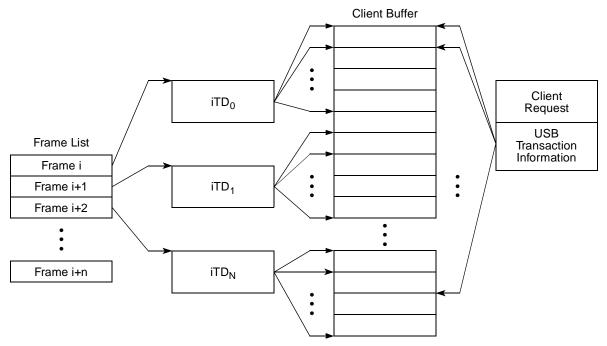

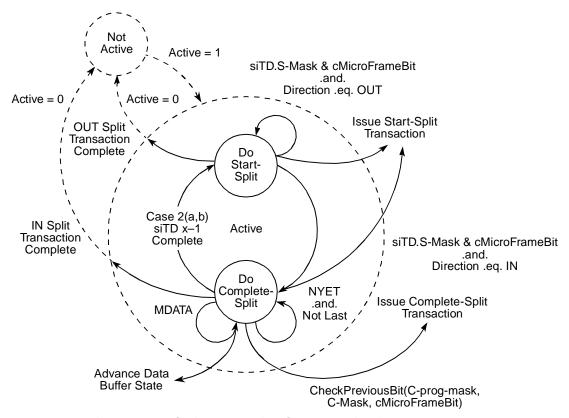

| Isochronous (High-Speed) Transfer Descriptor (iTD)          | 13-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

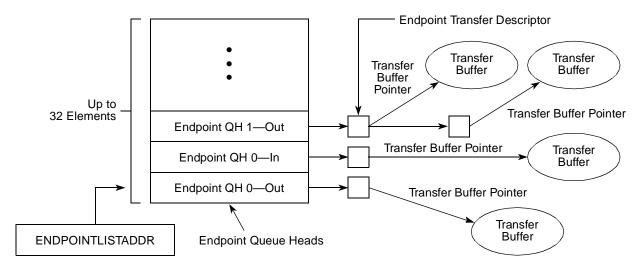

| Queue Head                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Periodic Frame Span Traversal Node (FSTN)                   | 13-66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <u>.</u>                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Host Controller Initialization                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Power Port                                                  | 13-69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Reporting Over-Current                                      | 13-69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Schedule Traversal Rules                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

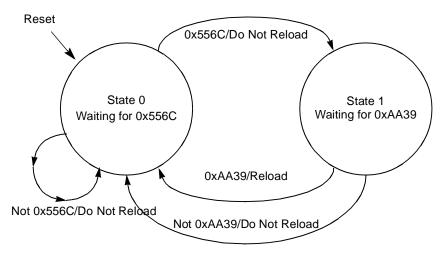

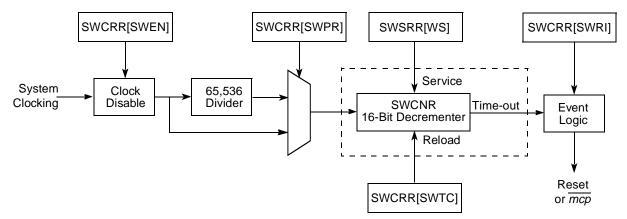

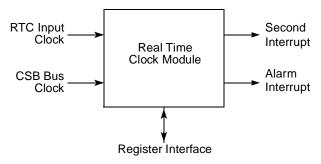

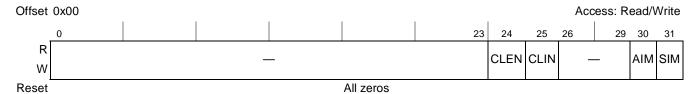

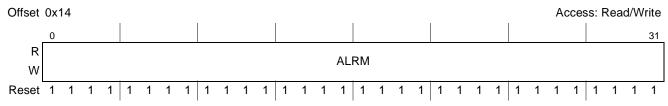

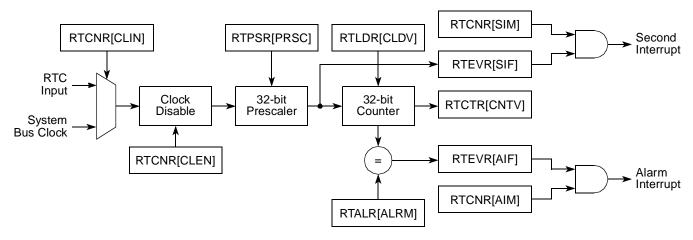

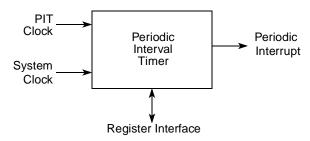

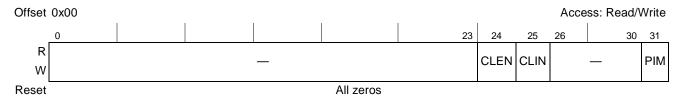

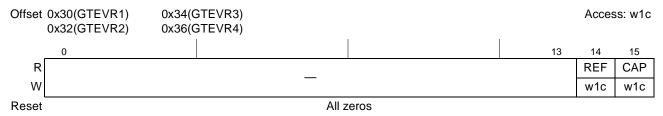

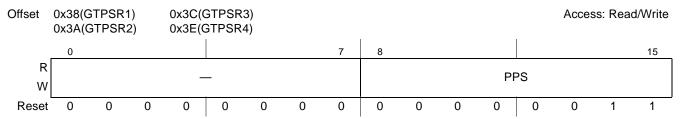

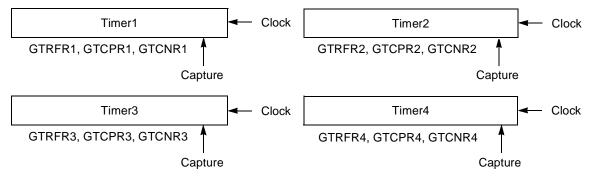

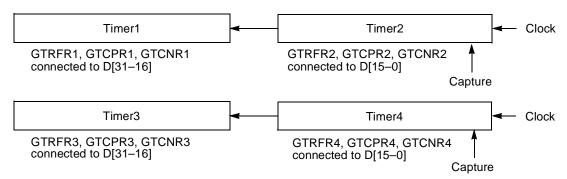

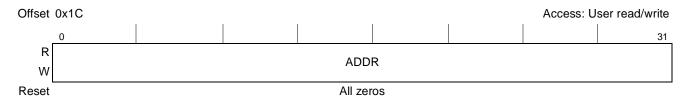

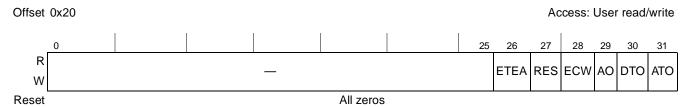

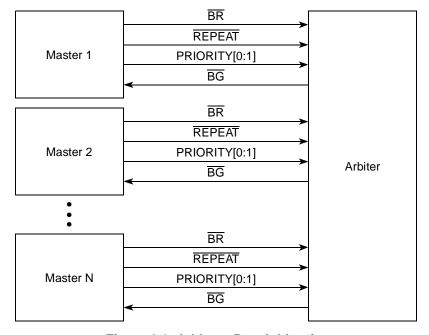

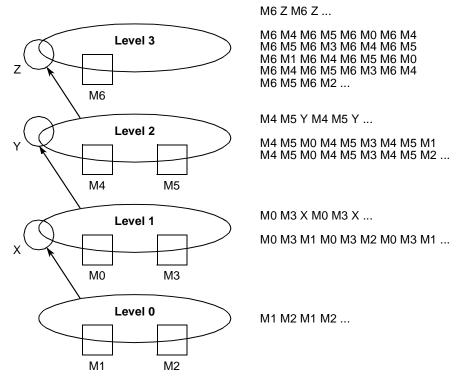

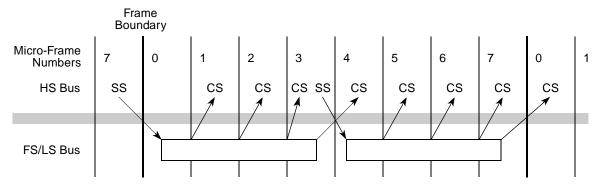

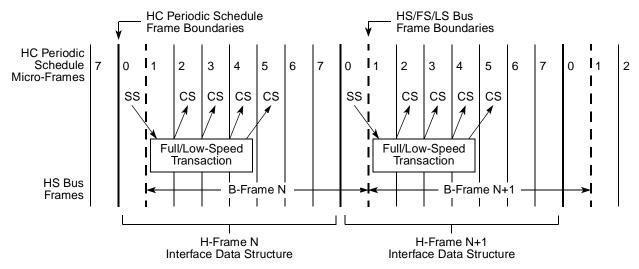

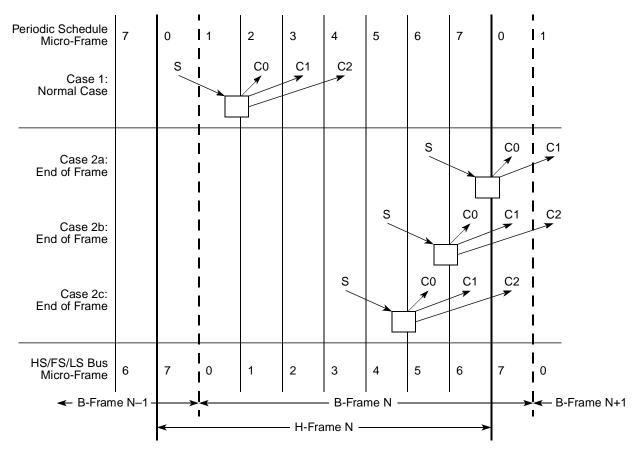

| Periodic Schedule Frame Boundaries vs. Bus Frame Boundaries | 13-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |