## PRODUCT MANUAL

# Rabbit 2000<sup>®</sup> Microprocessor

## **User's Manual**

019-0069 • 070831-P

### Rabbit 2000 Microprocessor User's Manual

Part Number 019-0069 • 070831–P • Printed in U.S.A.

©2002–2007 Rabbit Semiconductor Inc. • All rights reserved.

No part of the contents of this manual may be reproduced or transmitted in any form or by any means without the express written permission of Rabbit Semiconductor.

Permission is granted to make one or more copies as long as the copyright page contained therein is included. These copies of the manuals may not be let or sold for any reason without the express written permission of Rabbit Semiconductor.

Rabbit Semiconductor reserves the right to make changes and improvements to its products without providing notice.

#### Trademarks

Rabbit and Dynamic C are registered trademarks of Rabbit Semiconductor Inc. Rabbit 2000 is a trademark of Rabbit Semiconductor Inc.

The latest revision of this manual is available on the Rabbit Semiconductor Web site, www.rabbit.com, for free, unregistered download.

#### Rabbit Semiconductor Inc.

www.rabbit.com

## TABLE OF CONTENTS

| Chapter 1. Introduction                                         | 1  |

|-----------------------------------------------------------------|----|

| 1.1 Features and Specifications                                 | 1  |

| 1.2 Summary of Rabbit Advantages                                | 5  |

| Chapter 2. Rabbit Design Features                               | 7  |

| 2.1 The Rabbit 8-bit Processor vs. 16-bit and 32-bit Processors | 8  |

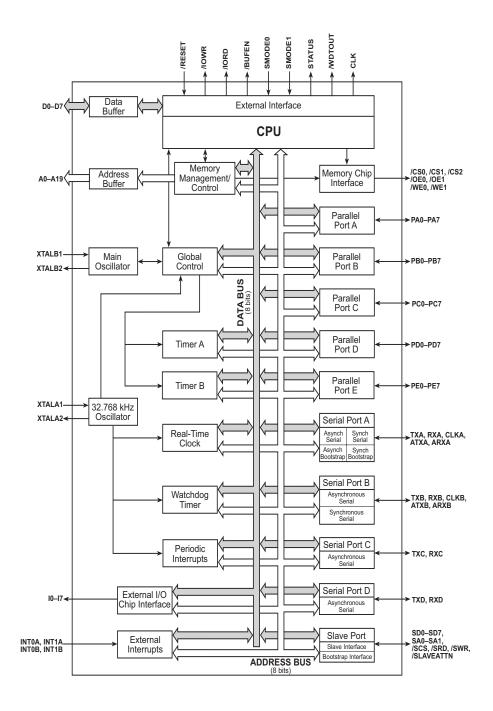

| 2.2 Overview of On-Chip Peripherals                             |    |

| 2.2.1 Serial Ports                                              |    |

| 2.2.2 System Clock                                              |    |

| 2.2.3 Time/Date Oscillator                                      | 9  |

| 2.2.4 Parallel I/O                                              | 9  |

| 2.2.5 Slave Port                                                |    |

| 2.2.6 Timers                                                    |    |

| 2.3 Design Standards                                            |    |

| 2.3.1 Programming Port                                          | 12 |

| 2.3.2 Standard BIOS                                             |    |

| 2.4 Dynamic C Support for the Rabbit                            |    |

| · 11                                                            |    |

### Chapter 3. Details on Rabbit

| Microprocessor Features                                                                           | 13 |

|---------------------------------------------------------------------------------------------------|----|

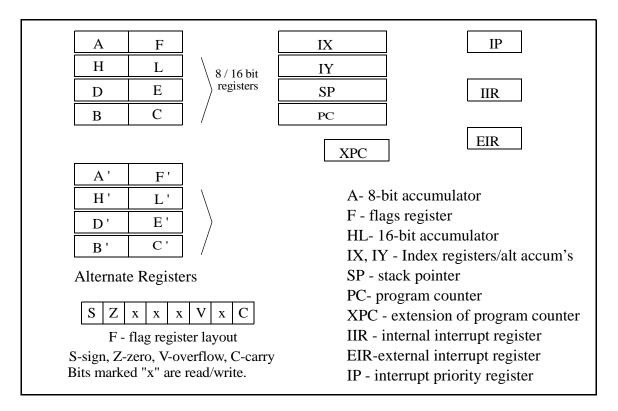

| 3.1 Processor Registers                                                                           | 13 |

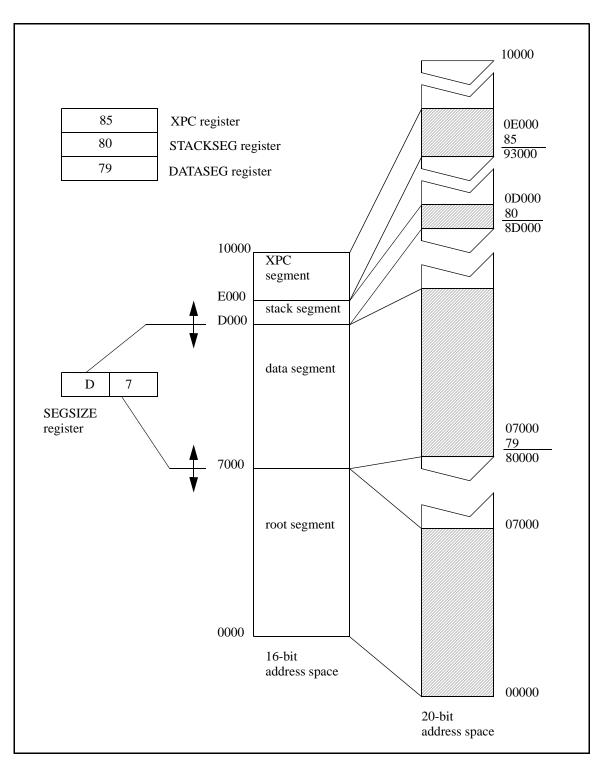

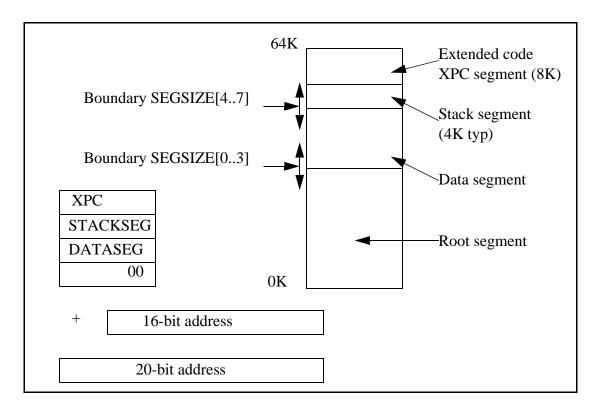

| 3.2 Memory Mapping                                                                                | 15 |

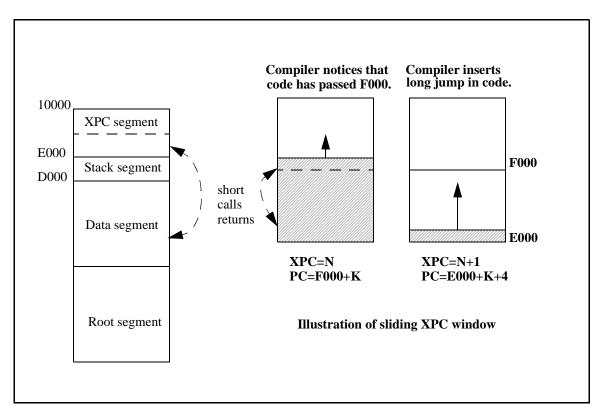

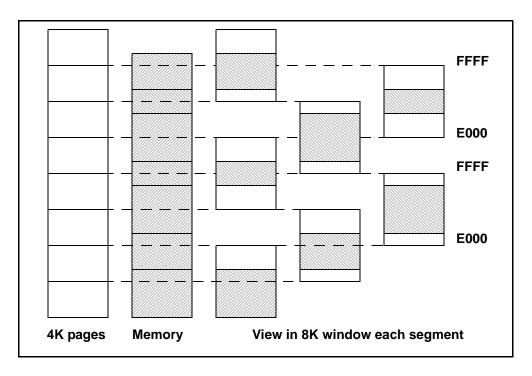

| 3.2.1 Extended Code Space                                                                         |    |

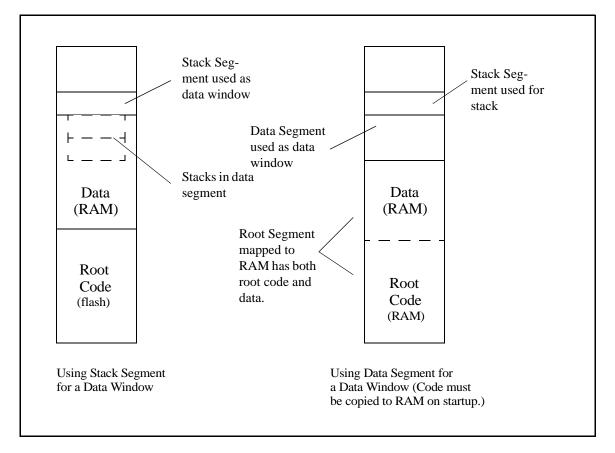

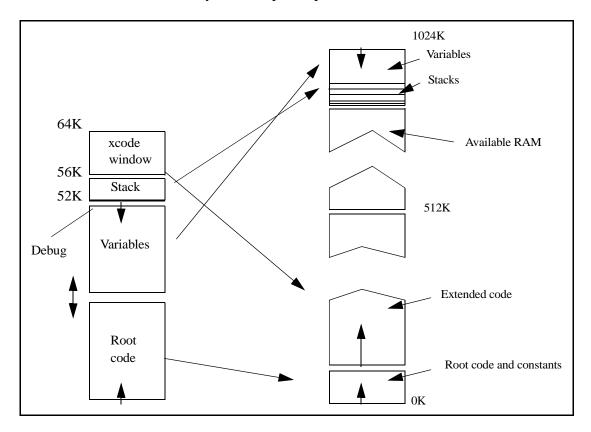

| 3.2.2 Extending Data Memory                                                                       | 19 |

| 3.2.3 Practical Memory Considerations                                                             | 21 |

| 3.3 Instruction Set Outline                                                                       |    |

| 3.3.1 Load Immediate Data To a Register                                                           |    |

| 3.3.2 Load or Store Data from or to a Constant Address                                            |    |

| 3.3.3 Load or Store Data Using an Index Register                                                  | 24 |

| 3.3.4 Register to Register Move                                                                   | 25 |

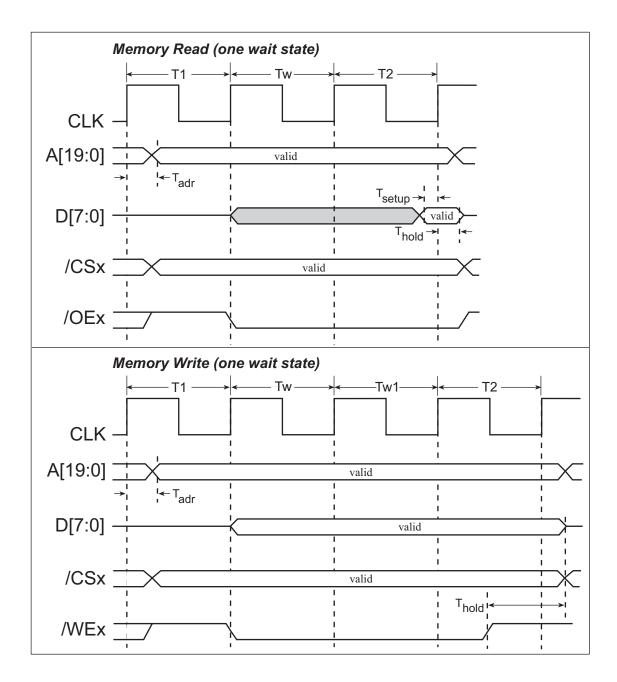

| 3.3.5 Register Exchanges                                                                          | 25 |

| 3.3.6 Push and Pop Instructions                                                                   |    |

| <ul><li>3.3.7 16-bit Arithmetic and Logical Ops</li><li>3.3.8 Input/Output Instructions</li></ul> | 20 |

| 3.4 How to Do It in Assembly Language—Tips and Tricks                                             | 31 |

| 3.4.1 Zero HL in 4 Clocks                                                                         |    |

| 3.4.2 Exchanges Not Directly Implemented                                                          |    |

| 3.4.3 Manipulation of Boolean Variables                                                           |    |

| 3.4.4 Comparisons of Integers                                                                     |    |

| 3.4.5 Atomic Moves from Memory to I/O Space                                                       |    |

| 3.5 Interrupt Structure                                                                           | 35 |

| 3.5.1 Interrupt Priority                                                                          |    |

| 3.5.2 Multiple External Interrupting Devices                                                      | 37 |

| 3.5.3 Privileged Instructions, Critical Sections and Semaphores                                   | 37 |

| 3.5.4 Critical Sections                                                                           |    |

| 3.5.5 Semaphores Using Bit B,(HL)                                                                 |    |

| 3.5.6 Computed Long Calls and Jumps                                                               |    |

| Chapter 4. Rabbit Capabilities                              | 41  |

|-------------------------------------------------------------|-----|

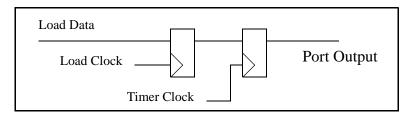

| 4.1 Precisely Timed Output Pulses                           | 41  |

| 4.1.1 Pulse Width Modulation to Reduce Relay Power          |     |

| 4.2 Open-Drain Outputs Used for Key Scan                    | 44  |

| 4.3 Cold Boot                                               |     |

| 4.4 The Slave Port                                          | 46  |

| 4.4.1 Slave Rabbit As A Protocol UART                       |     |

| Chapter 5. Pin Assignments and Functions                    | 49  |

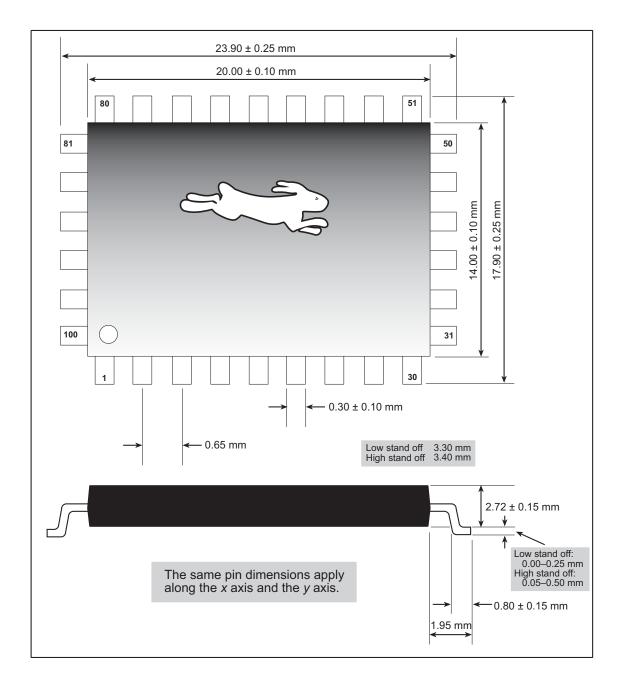

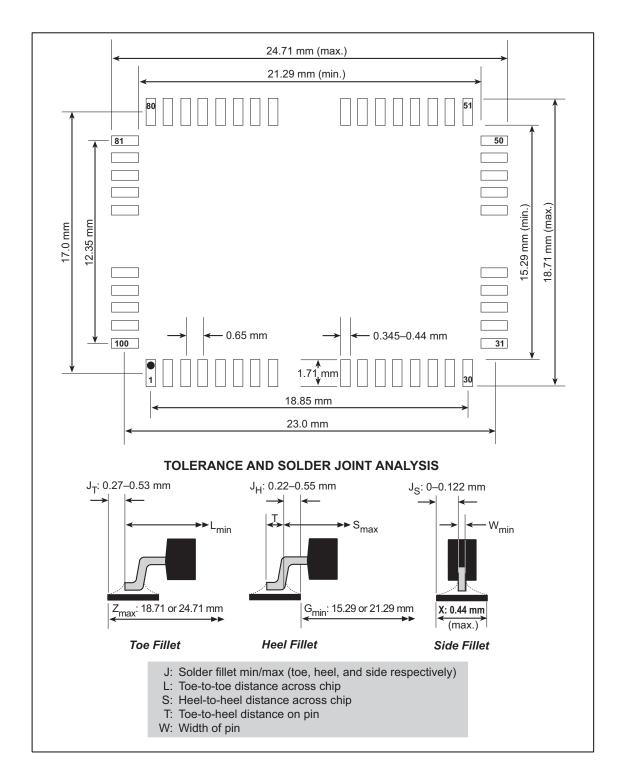

| 5.1 Package Schematic and Pinout                            | -   |

| 5.1 Package Schematic and Photot                            |     |

| 5.3 Rabbit Pin Descriptions                                 |     |

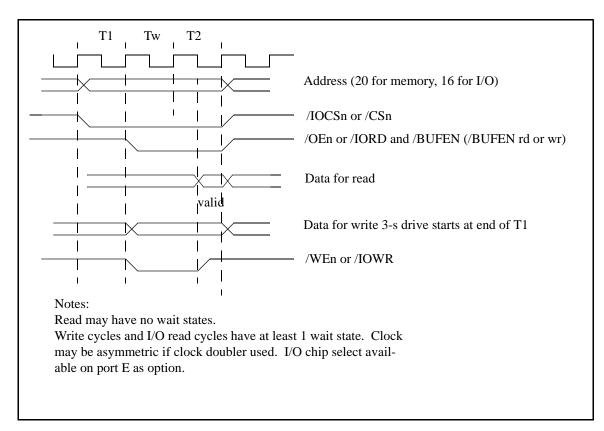

| 5.4 Bus Timing                                              |     |

| 5.5 Description of Pins with Alternate Functions            |     |

| 5.6 DC Characteristics                                      |     |

| 5.6.1 5.0 Volts                                             |     |

| 5.6.2 3.3 Volts                                             |     |

| 5.7 I/O Buffer Sourcing and Sinking Limit                   |     |

|                                                             |     |

| Chapter 6. Rabbit Internal I/O Registers                    | 65  |

| 6.1 Default Values for all the Peripheral Control Registers | 65  |

| 1 C                                                         |     |

| Chapter 7. Miscellaneous I/O Functions                      | 71  |

| 7.1 Processor Identification                                |     |

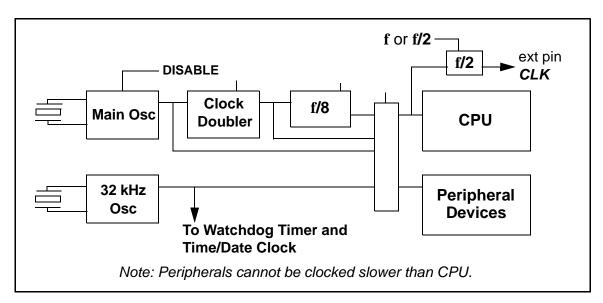

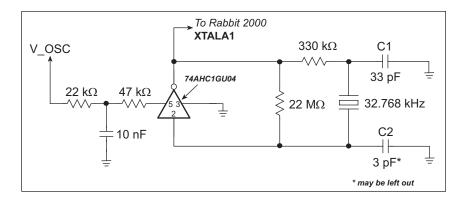

| 7.2 Rabbit Oscillators and Clocks                           |     |

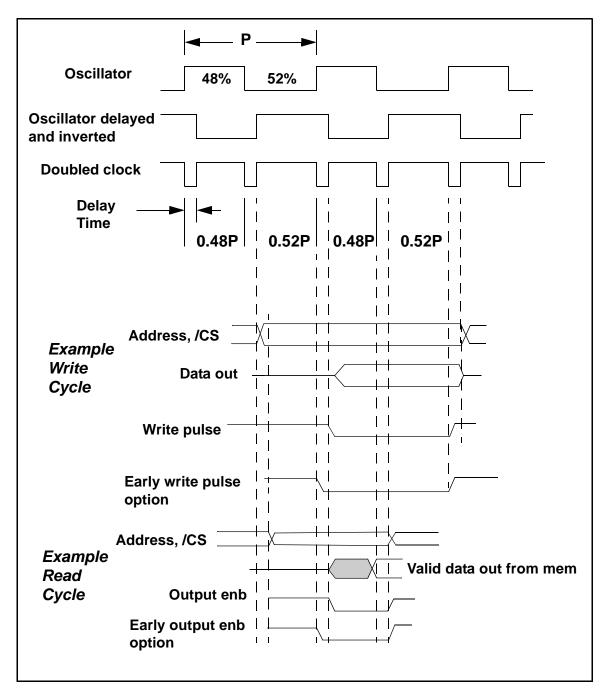

| 7.3 Clock Doubler                                           |     |

| 7.4 Controlling Power Consumption                           |     |

| 7.5 Output Pins CLK, STATUS, /WDTOUT, /BUFEN                | 77  |

| 7.6 Time/Date Clock (Real-Time Clock)                       |     |

| 7.7 Watchdog Timer                                          |     |

| 7.8 System Reset                                            | 82  |

| 7.9 Rabbit Interrupt Structure                              |     |

| 7.9.1 External Interrupts                                   |     |

| 7.9.2 Interrupt Vectors: INT0 - EIR,0x00/INT1 - EIR,0x08    |     |

| 7.10 Bootstrap Operation                                    | 88  |

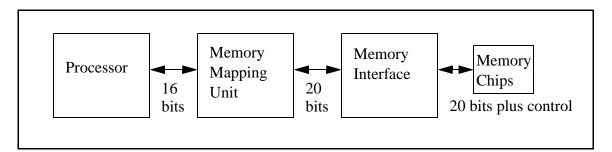

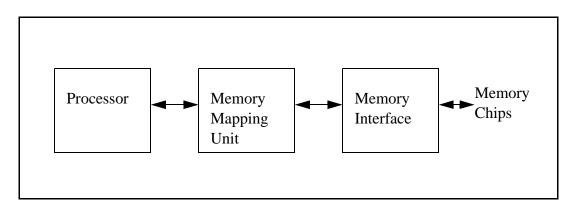

| Chapter 8. Memory Mapping and Interface                     | 91  |

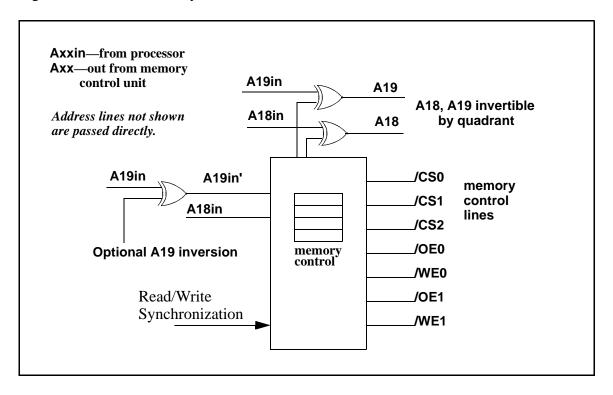

| 8.1 Memory-Mapping Unit                                     |     |

| 8.2 Memory Interface Unit                                   |     |

| 8.3 Memory Control Unit Registers                           |     |

| 8.3.1 Memory Bank Control Registers                         |     |

| 8.3.2 MMU Instruction/Data Register                         |     |

| 8.3.3 Memory Timing Control Register                        |     |

| 8.4 Allocation of Extended Code and Data                    |     |

| 8.5 How Compiler Compiles to Memory                         |     |

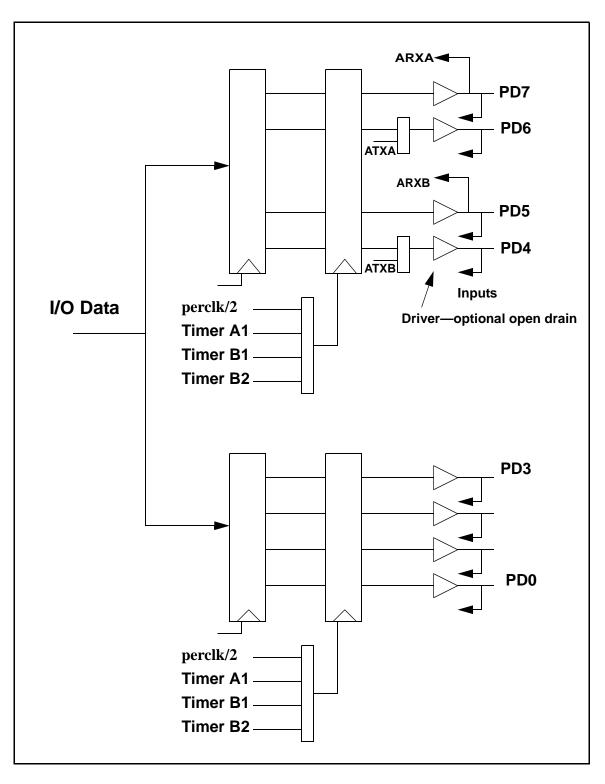

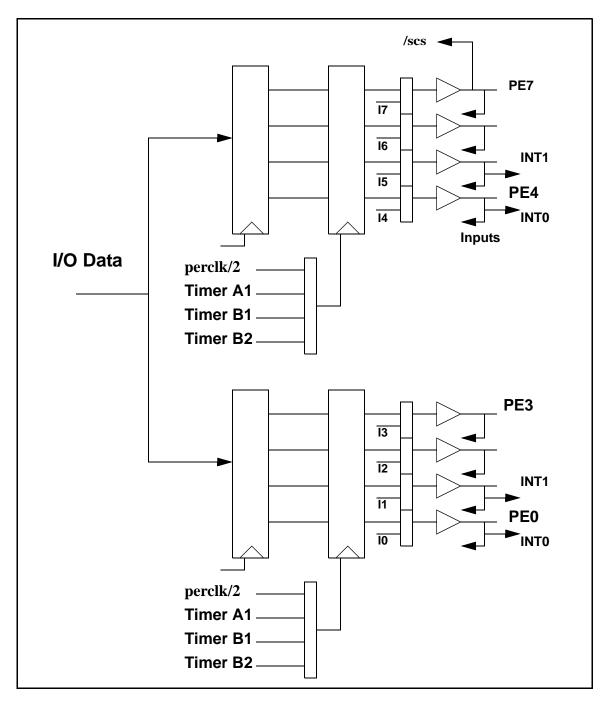

| Chapter 9. Parallel Ports                                   | 99  |

| 9.1 Parallel Port A                                         |     |

| 9.1 Parallel Port B                                         |     |

| 9.3 Parallel Port C                                         |     |

| 9.4 Parallel Port D                                         |     |

| 9.5 Parallel Port E                                         |     |

|                                                             |     |

| Chantar 10 1/0 Bank Control Bogistors                       | 100 |

#### Chapter 10. I/O Bank Control Registers

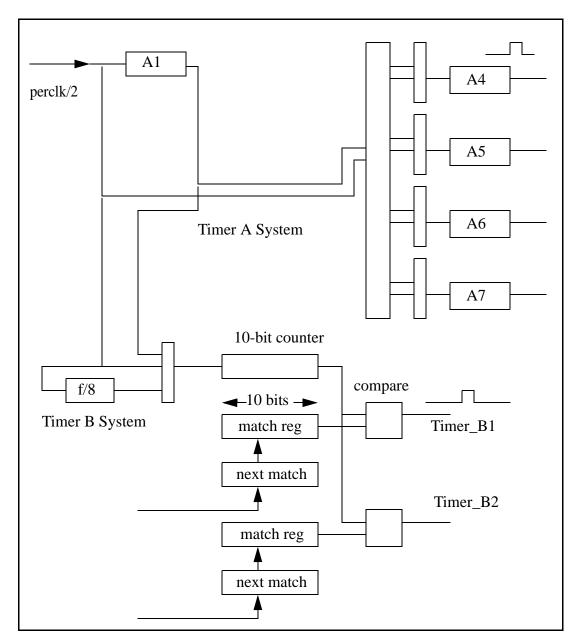

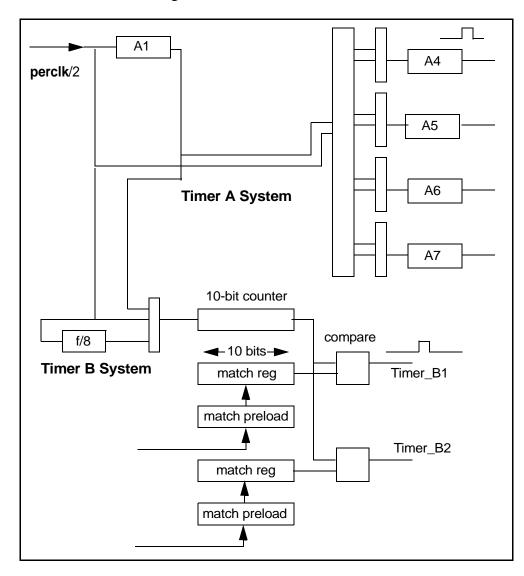

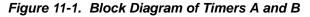

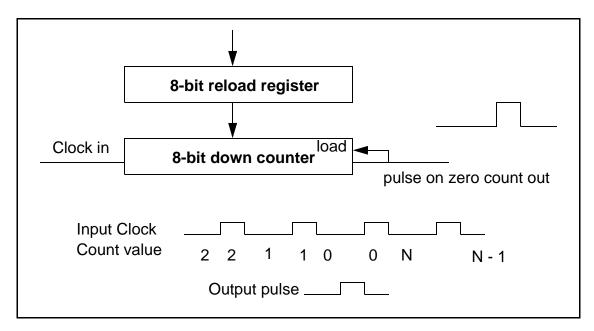

| Chapter 11. Timers                                                                                                                   | <b>11</b> 1                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 11.1 Timer A                                                                                                                         |                                                                                                       |

| 11.1.1 Timer A I/O Registers                                                                                                         |                                                                                                       |

| 11.1.2 Practical Use of Timer A                                                                                                      |                                                                                                       |

| 11.2 Timer B                                                                                                                         |                                                                                                       |

| 11.2.1 Using Timer B                                                                                                                 | 11                                                                                                    |

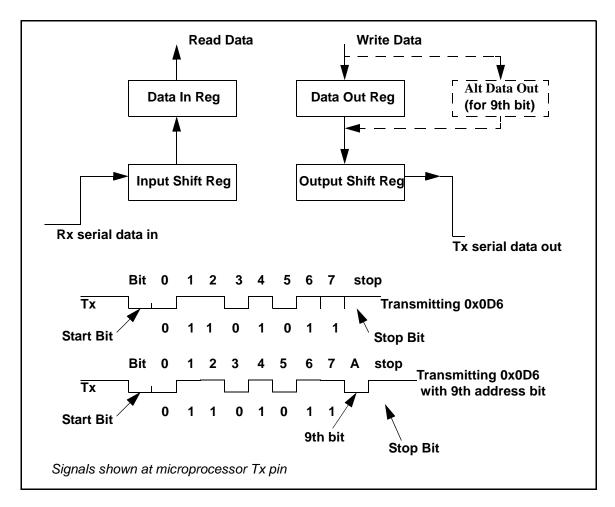

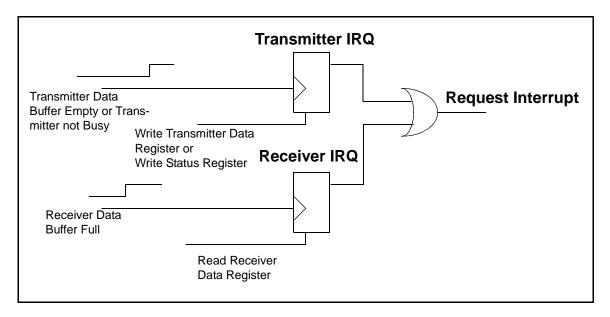

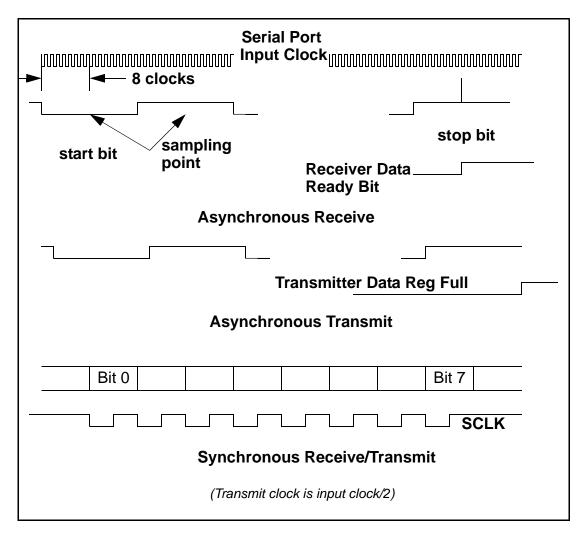

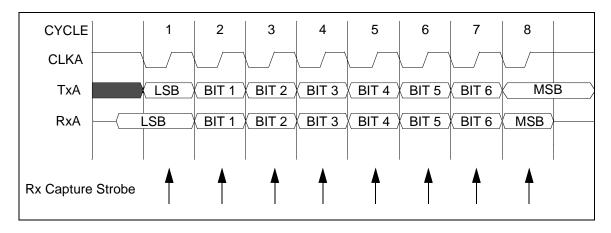

| Chapter 12. Rabbit Serial Ports                                                                                                      | 119                                                                                                   |

| 12.1 Serial Port Register Layout                                                                                                     |                                                                                                       |

| 12.2 Serial Port Interrupt                                                                                                           |                                                                                                       |

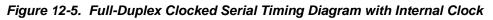

| 12.3 Transmit Serial Data Timing                                                                                                     |                                                                                                       |

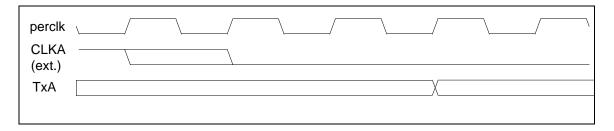

| 12.4 Receive Serial Data Timing                                                                                                      |                                                                                                       |

| 12.5 Clocked Serial Ports                                                                                                            |                                                                                                       |

| 12.6 Clocked Serial Timing                                                                                                           |                                                                                                       |

| 12.6.1 Clocked Serial Timing With Internal Clock                                                                                     |                                                                                                       |

| 12.6.2 Clocked Serial Timing with External Clock                                                                                     |                                                                                                       |

| 12.7 Serial Port Software Suggestions                                                                                                |                                                                                                       |

| 12.7.1 Controlling an RS-485 Driver and Receiver                                                                                     |                                                                                                       |

| 12.7.2 Transmitting Dummy Characters                                                                                                 |                                                                                                       |

| 12.7.3 Transmitting and Detecting a Break<br>12.7.4 Using A Serial Port to Generate a Periodic Interrupt                             | 13                                                                                                    |

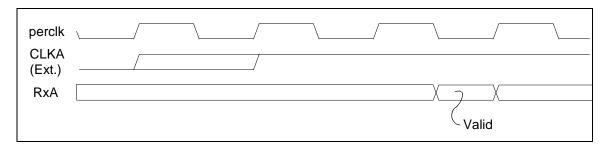

| 12.7.5 Extra Stop Bits, Sending Parity, 9th Bit Communication Schemes                                                                |                                                                                                       |

| 12.7.6 Supporting 9th Bit Communication Protocols                                                                                    |                                                                                                       |

| 12.7.7 Rabbit-Only Master/Slave Protocol                                                                                             |                                                                                                       |

| 12.7.8 Data Framing/Modbus                                                                                                           |                                                                                                       |

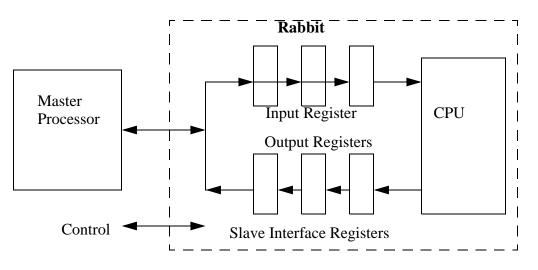

| Chapter 13. Rabbit Slave Port                                                                                                        | 13                                                                                                    |

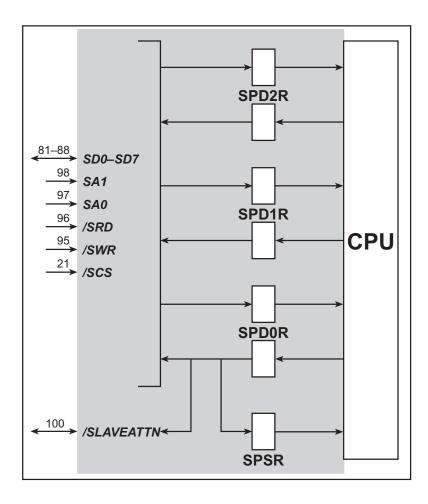

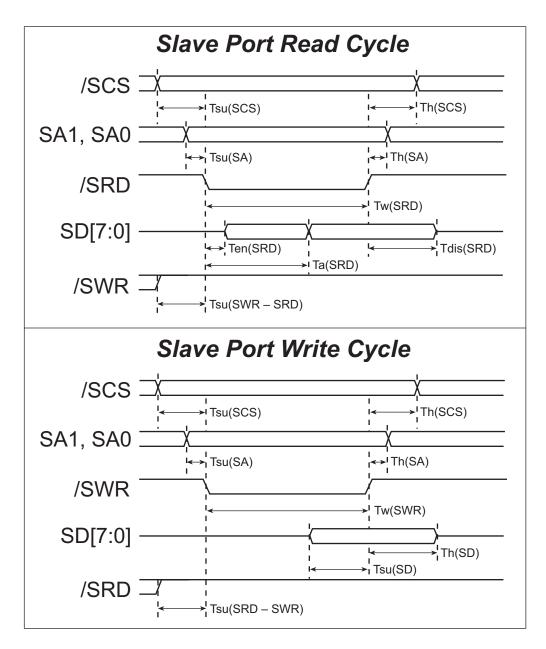

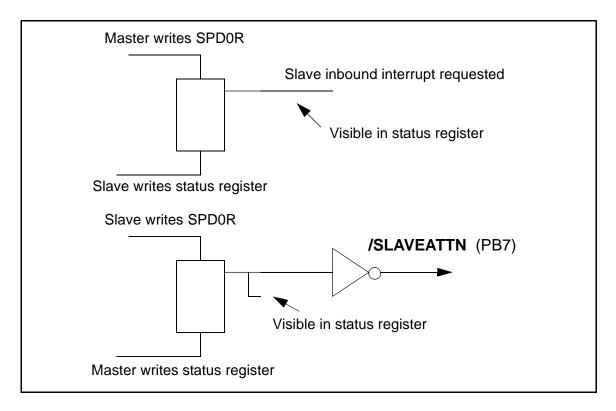

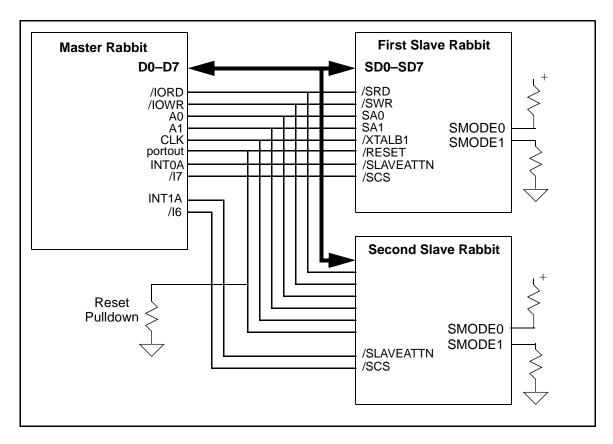

| 13.1 Hardware Design of Slave Port Interconnection                                                                                   |                                                                                                       |

| 13.2 Slave Port Registers                                                                                                            | 14                                                                                                    |

| 13.3 Applications and Communications Protocols for Slaves                                                                            |                                                                                                       |

| 13.3.1 Slave Applications                                                                                                            |                                                                                                       |

| 13.3.2 Master-Slave Messaging Protocol                                                                                               |                                                                                                       |

| Chapter 14. Rabbit 2000 Clocks                                                                                                       |                                                                                                       |

|                                                                                                                                      | 14                                                                                                    |

|                                                                                                                                      |                                                                                                       |

| 14.1 Low-Power Design                                                                                                                |                                                                                                       |

|                                                                                                                                      |                                                                                                       |

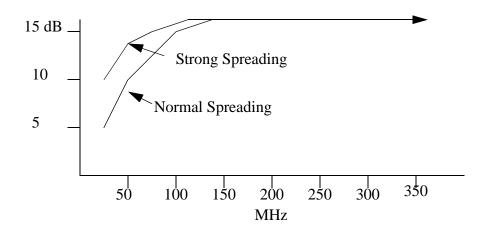

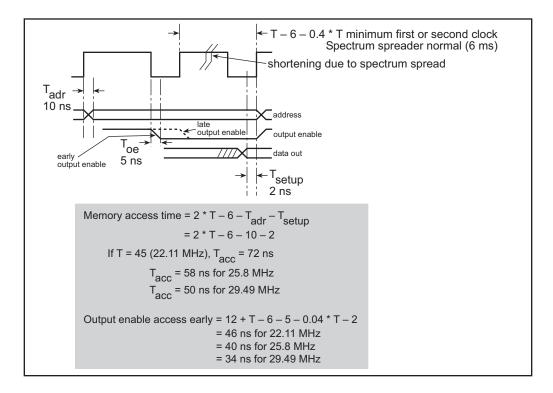

| <ul> <li>14.1 Low-Power Design</li> <li>14.2 Clock Spectrum Spreader Module</li> <li>Chapter 15. AC Timing Specifications</li> </ul> | 150<br>150<br><b>15</b> <sup>-</sup>                                                                  |

| <ul> <li>14.1 Low-Power Design</li> <li>14.2 Clock Spectrum Spreader Module</li> <li>Chapter 15. AC Timing Specifications</li> </ul> | 150<br>150<br><b>15</b> 7                                                                             |

| <ul><li>14.1 Low-Power Design</li><li>14.2 Clock Spectrum Spreader Module</li></ul>                                                  | 150<br>                                                                                               |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             |                                                                                                       |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             | 150<br>                                                                                               |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             |                                                                                                       |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             | 150<br>150<br>150<br>150<br>150<br>160<br>160<br>160<br>160<br>160<br>160<br>160<br>160<br>160<br>16  |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             |                                                                                                       |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             | 150<br>150<br>150<br>150<br>154<br>165<br>165<br>166<br>166<br>166<br>166<br>166<br>166<br>166<br>166 |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             | 150<br>150<br>150<br>150<br>154<br>165<br>165<br>166<br>166<br>166<br>166<br>166<br>166<br>166<br>166 |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             | 150<br>150<br>150<br>154<br>154<br>165<br>165<br>166<br>166<br>166<br>166<br>166<br>166<br>166<br>166 |

| <ul> <li>14.1 Low-Power Design</li></ul>                                                                                             |                                                                                                       |

| 17.3.3       Write-only Registers Without Shadow Registers       172         17.4       Timer and Clock Usage       172         Chapter 18. Rabbit Instructions       175         18.1       Load Immediate Data       178         18.2       Load Store to Immediate Address       178         18.3       8-bit Indexed Loads and Stores       178         18.4       16-bit Load and Store 20-bit Address       179         18.5       Register to Register To Moves       179         18.6       Register to Register Moves       179         18.7       Exchange Instructions       180         18.9       16-bit Arithmetic and Logical Ops       180         18.11       8-bit Bit Ster, Reset and Test.       181         18.11       8-bit Bit Ster, Reset and Test.       182         18.12       8-bit Increment and Logical Ops       181         18.13       8-bit Staft Register Operations       183         18.14       8-bit Staft Register Operations       183         18.14       8-bit Staft Register Operations       184         18.14       8-bit Staft Register Operations       184         18.14       8-bit Staft Register Operations       185         18.14       8-bit Staft Register Operati                                                                                                                                                              | 17.3.2 Interrupt While Updating Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 18. Rabbit Instructions       175         18.1 Load Immediate Data       178         18.2 Load & Store to Immediate Address       178         18.2 Load & Store to Immediate Address       178         18.3 8-bit Indexed Loads and Store       178         18.4 16-bit Load and Store 20-bit Address       179         18.4 16-bit Load and Store 20-bit Address       179         18.6 Register to Register Moves.       179         18.7 Exchange Instructions       180         18.9 16-bit Arithmetic and Logical Ops       180         18.1 18-bit Bit Set, Reset and Test.       182         18.1 18-bit Bit Set, Reset and Test.       182         18.1 28-bit Increment and Decrement.       182         18.1 3 8-bit Fast A register Operations       183         18.1 48-bit Shifts and Rotates       183         18.1 5 Instruction Prefixes       184         18.1 6 Block Move Instructions       185         18.1 7 Control Instructions - Jumps and Calls       185         18.1 8 bit Shifts and Rotates       183         18.1 7 Control Instructions - Jumps and Calls       185         18.1 8 Discellancous Instructions       185         18.1 8 Discellancous Instructions       185         18.1 8 Privileged Instructions       187                                                                                                                     | 17.3.3 Write-only Registers Without Shadow Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                    |

| 18.1       Load & Store to Immediate Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17.4 Timer and Clock Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1/2                                                                                                                                                                                |

| 18.1       Load & Store to Immediate Address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.2       Load & Store to Immediate Address.       178         18.3       8-bit Indexed Load and Stores       178         18.4       16-bit Indexed Loads and Stores       179         18.5       16-bit Indexed Loads and Stores       179         18.6       Register to Register Moves       179         18.6       Register to Register Moves       180         18.9       16-bit Arithmetic and Logical Ops       180         18.10       8-bit Arithmetic and Logical Ops       180         18.11       8-bit First and Decrement       182         18.12       8-bit Increment and Decrement       182         18.13       8-bit First A register Operations       183         18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.17       Control Instructions       185         18.19       Privileged Instructions       185         18.19       Privileged Instructions       185         18.19       Privileged Instructions       185         18.19       Privileged Instructions       187         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order </td <td></td> <td>-</td>                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                  |

| 18.3       8-bit Indexed Loads and Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.4       16-bit Indexed Loads and Store 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.5       16-bit Load and Store 20-bit Address       179         18.6       Register to Register Moves       179         18.7       Exchange Instructions       180         18.8       Stack Manipulation Instructions       180         18.8       Stack Manipulation Instructions       180         18.10       8-bit Arithmetic and Logical Ops       181         18.11       8-bit Arithmetic and Logical Ops       181         18.11       8-bit Bit Act, Reset and Test       182         18.12       8-bit Increment and Decrement       182         18.13       8-bit Fast A register Operations       183         18.14       8-bit Shifts and Rotates       183         18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.17       Control Instructions       185         18.18       Niscellaneous Instructions       185         18.19       Privileged Instructions       186         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order       197         A.1       The Rabbit Programming Port       197         A.2       Use of the Programming Por                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.6 Register to Register Moves       179         18.7 Exchange Instructions       180         18.8 Stack Manipulation Instructions       180         18.9 16-bit Arithmetic and Logical Ops       180         18.1 8-bit Bit Set, Reset and Test       182         18.1 8-bit Bit Set, Reset and Test       182         18.1 8-bit Bit Set, Reset and Test       182         18.1 8-bit Bit Set, Reset and Test       183         18.1 8-bit Bit Set, Reset and Test       183         18.1 8-bit Bit Set, Reset and Test       183         18.1 8-bit Shit's and Rotates       183         18.1 8-bit Shit's and Rotates       183         18.1 8-bit Shit's and Rotates       184         18.1 6 Block Move Instructions       184         18.1 7 Control Instructions       185         18.1 8 Miscellaneous Instructions       185         18.1 9 Privileged Instructions       186         Chapter 19. Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20. Instructions in Alphabetical Order       197         A.1 The Rabbit Programming Port       197         A.2 Use of the Programming Port       198         A.3 Alternate Programming Port       198         A.4 Suggested Rabbit Crystal Frequencies       201         <                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.7       Exchange Instructions       180         18.8       Stack Manipulation Instructions       180         18.9       16-bit Arithmetic and Logical Ops       180         18.10       8-bit Arithmetic and Logical Ops       181         18.11       8-bit Bit Reset and Test       182         18.12       8-bit Bott Reset and Test       182         18.13       8-bit Bast Aregister Operations       183         18.14       8-bit Shifts and Rotates       183         18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.17       Control Instructions - Jumps and Calls       185         18.18       Miscellaneous Instructions       185         18.19       Privileged Instructions       185         18.19       Privileged Instructions       186         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order       189         Appendix A.       197       197       197         A.1       The Rabbit Programming Port       197         A.2       Use of the Programming Port       198         A.3       Alternate Programming Port                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.8       Stack Manipulation Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.9       16-bit Arithmetic and Logical Ops       180         18.10       8-bit Arithmetic and Logical Ops       181         18.11       8-bit Bit Set, Reset and Test.       182         18.12       8-bit Increment and Decrement.       182         18.13       8-bit Shifts and Rotates       183         18.14       8-bit Shifts and Rotates       183         18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.17       Control Instructions - Jumps and Calls       185         18.18       Miscellaneous Instructions       185         18.19       Privileged Instructions       186         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order       189         With Binary Encoding       189       189         A.1       The Rabbit Programming Port       197         A.1       The Rabbit Programming Port       197         A.2       Use of the Programming Port       198         A.3       Alternate Programming Port       198         A.4       Suggested Rabbit Covestions       201         B.1       Rabbit 2000 Revisions                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.10       8-bit Arithmetic and Logical Ops.       181         18.11       8-bit Bit Set, Reset and Test.       182         18.12       8-bit Increment and Decrement.       182         18.13       8-bit Fast A register Operations.       183         18.14       8-bit Shifts and Rotates.       183         18.15       Instruction Prefixes       184         18.16       Boock Move Instructions       184         18.17       Control Instructions - Jumps and Calls.       185         18.18       Miscellaneous Instructions       185         18.19       Privileged Instructions       185         18.19       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order<br>With Binary Encoding       189         Appendix A.       197       197       197         A.1 The Rabbit Programming Port       197       198         A.3 Alternate Programming Port       198       198         A.4 Suggested Rabbit Coystal Frequencies       199         A.4 Suggested Rabbit Coy Revisions       201         B.1 Rabbit Internal I/O Registers       204         B.2.1 Rabbit Interna                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.11       8-bit Bit Set, Reset and Test.       182         18.12       8-bit Increment and Decrement.       182         18.13       8-bit Fast A register Operations       183         18.13       8-bit Shifts and Rotates       183         18.14       8-bit Shifts and Rotates       183         18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.17       Control Instructions       185         18.18       Miscellaneous Instructions       185         18.19       Privileged Instructions       185         18.19       Privileged Instructions       186         Chapter 19. Differences Rabbit vs. Z80/Z180 Instructions         Chapter 20. Instructions in Alphabetical Order         With Binary Encoding       189         A.1       The Rabbit Programming Port       197         A.2       Use of the Programming Port       197         A.3       Alternate Programming Port       198         A.4       Suggested Rabbit Crystal Frequencies       201         B.2       Discussion of Fixes and Improvements       203         B.2.1       Rabbit Internal I/O Registers       204         B.2       Serai                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.12       8-bit Increment and Decrement.       182         18.13       8-bit Shifts and Rotates       183         18.14       8-bit Shifts and Rotates       183         18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.16       Block Move Instructions       184         18.17       Control Instructions - Jumps and Calls       185         18.18       Miscellaneous Instructions       185         18.19       Privileged Instructions       185         18.19       Privileged Instructions       186         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order       187         With Binary Encoding       189       189         Appendix A.       The Rabbit Programming Port       197         A.1       The Rabbit Programming Port       197         A.2       Use of the Programming Port       198         A.3       Alternate Programming Port       198         A.4       Suggested Rabbit Cool Revisions       201         B.1       Rabbit 2000 Revisions       201         B.2       Discussion of Fixes and Improvements       20                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.13       8-bit Fast A register Operations       183         18.14       8-bit Shifts and Rotates       183         18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.16       Block Move Instructions       184         18.17       Control Instructions - Jumps and Calls       185         18.18       Miscellaneous Instructions       185         18.19       Privileged Instructions       186         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order       189         With Binary Encoding       189       189         Appendix A.       197       197         A.1 The Rabbit Programming Port       197         A.2 Use of the Programming Port       198         A.3 Alternate Programming Port       198         A.4 Suggested Rabbit Crystal Frequencies       199         Appendix B. Rabbit 2000 Revisions       201         B.1 Rabbit Internal I/O Register       203         B.2.1 Rabbit Internal I/O Register       203         B.2.2 Revision-Level ID Register       205         B.2.3 Serial Port Changes       207         B.2.4 Improved                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.14       8-bit Shifts and Rotates       183         18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.16       Block Move Instructions       185         18.17       Control Instructions - Jumps and Calls       185         18.18       Miscellaneous Instructions       185         18.19       Privileged Instructions       186         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order       189         With Binary Encoding       189       189         Appendix A.       197       197         A.1       The Rabbit Programming Port       197         A.2       Use of the Programming Port       197         A.2       Use of the Programming Port       198         A.3       Alternate Programming Port       198         A.4       Suggested Rabbit Crystal Frequencies       199         Appendix B.       Rabbit 2000 Revisions       201         B.1       Rabbit 2000 Revisions       201         B.1       Rabbit 2000 Revisions       201         B.1       Rabbit Chapter       205         B.2.3                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |

| 18.15       Instruction Prefixes       184         18.16       Block Move Instructions       184         18.17       Control Instructions - Jumps and Calls       185         18.18       Miscellaneous Instructions       185         18.19       Privileged Instructions       185         18.19       Privileged Instructions       186         Chapter 19.       Differences Rabbit vs. Z80/Z180 Instructions       187         Chapter 20.       Instructions in Alphabetical Order       189         With Binary Encoding       189         Appendix A.       197       197         A.1       The Rabbit Programming Port       197         A.2       Use of the Programming Port       198         A.3       Alternate Programming Port       198         A.4       Suggested Rabbit Crystal Frequencies       198         A.4       Suggested Rabbit 2000 Revisions       201         B.1       Rabbit 2000 Revisions       201         B.2       Discussion of Fixes and Improvements       203         B.2.1       Rabbit 2000 Revisions       204         B.2.2       Revision-Level ID Register       205         B.2.3       Serial Port Changes       207         B.2.4 <td></td> <td></td>                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                    |