# Full-Speed USB (12 Mbps) Peripheral Controller with Integrated Hub

# **TABLE OF CONTENTS**

| 1.0 FEATURES                                                  | 6  |

|---------------------------------------------------------------|----|

| 2.0 FUNCTIONAL OVERVIEW                                       | 7  |

| 2.1 GPIO                                                      |    |

| 2.2 DAC                                                       |    |

| 2.3 Clock                                                     |    |

| 2.4 Memory2.5 Power-on Reset, Watchdog, and Free-running Time |    |

| 2.6 I2C and HAPI Interface                                    |    |

| 2.7 Timer                                                     | 7  |

| 2.8 Interrupts                                                |    |

| 2.9 USB                                                       |    |

| 3.0 PIN CONFIGURATIONS                                        | _  |

| 4.0 PRODUCT SUMMARY TABLES                                    |    |

| 4.1 Pin Assignments                                           | 11 |

| 4.2 I/O Register Summary                                      |    |

| 5.0 PROGRAMMING MODEL                                         |    |

|                                                               |    |

| 5.1 14-bit Program Counter (PC)                               | 14 |

| 5.1.1 Program Memory Organization                             |    |

| 5.3 8-Bit Temporary Register (X)                              |    |

| 5.4 8-Bit Program Stack Pointer (PSP)                         | 16 |

| 5.4.1 Data Memory Organization                                |    |

| 5.5 8-Bit Data Stack Pointer (DSP)                            |    |

| 5.6.1 Data (Immediate)                                        |    |

| 5.6.2 Direct                                                  |    |

| 5.6.3 Indexed                                                 | 17 |

| 6.0 CLOCKING                                                  | 17 |

| 7.0 RESET                                                     | 18 |

| 7.1 Power-on Reset                                            | 18 |

| 7.2 Watchdog Reset                                            |    |

| 8.0 SUSPEND MODE                                              | 19 |

| 9.0 GENERAL-PURPOSE I/O (GPIO) PORTS                          | 19 |

| 9.1 GPIO Configuration Port                                   | 20 |

| 9.2 GPIO Interrupt Enable Ports                               |    |

| 10.0 DAC PORT                                                 | 22 |

| 10.1 DAC Isink Registers                                      | 23 |

| 10.2 DAC Port Interrupts                                      | 23 |

| 11.0 12-BIT FREE-RUNNING TIMER                                |    |

| 12.0 I <sup>2</sup> C AND HAPI CONFIGURATION REGISTER         |    |

| 13.0 I <sup>2</sup> C-COMPATIBLE CONTROLLER                   |    |

| 14.0 HARDWARE ASSISTED PARALLEL INTERFACE (HAPI)              | 27 |

| 15.0 PROCESSOR STATUS AND CONTROL REGISTER                    | 28 |

# TABLE OF CONTENTS (continued)

| 16.0 INTERRUPTS                                                                                                                                                                                                                               | 29             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 16.1 Interrupt Vectors 16.2 Interrupt Latency 16.3 USB Bus Reset Interrupt 16.4 Timer Interrupt 16.5 USB Endpoint Interrupts 16.6 USB Hub Interrupt 16.7 DAC Interrupt 16.8 GPIO/HAPI Interrupt 16.9 I <sup>2</sup> C Interrupt               |                |

| 17.0 USB OVERVIEW                                                                                                                                                                                                                             | 33             |

| 17.1 USB Serial Interface Engine                                                                                                                                                                                                              | 33             |

| 18.0 USB HUB                                                                                                                                                                                                                                  | _              |

| 18.1 Connecting/Disconnecting a USB Device  18.2 Enabling/Disabling a USB Device  18.3 Hub Downstream Ports Status and Control  18.4 Downstream Port Suspend and Resume  18.5 USB Upstream Port Status and Control                            | 35<br>35<br>37 |

| 19.0 USB SIE OPERATION                                                                                                                                                                                                                        | 39             |

| 19.1 USB Device Addresses 19.2 USB Device Endpoints 19.3 USB Control Endpoint Mode Registers 19.4 USB Non-Control Endpoint Mode Registers 19.5 USB Endpoint Counter Registers 19.6 Endpoint Mode/Count Registers Update and Locking Mechanism |                |

| 20.0 USB MODE TABLES                                                                                                                                                                                                                          | 44             |

| 21.0 REGISTER SUMMARY                                                                                                                                                                                                                         | 48             |

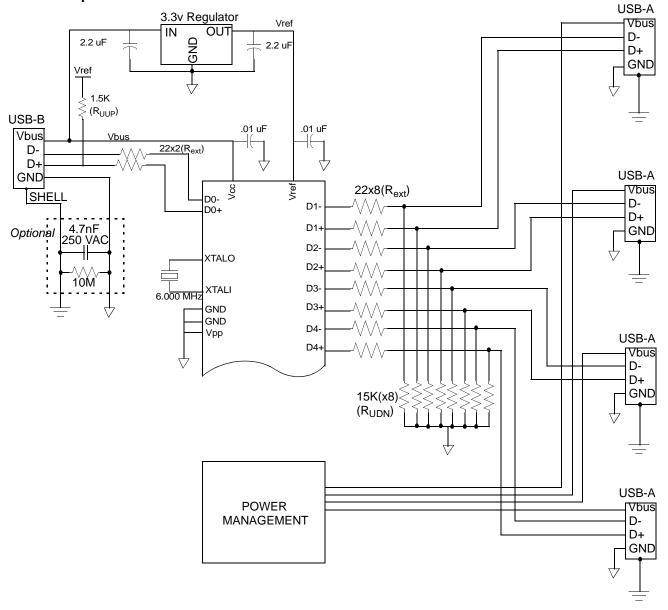

| 22.0 SAMPLE SCHEMATIC                                                                                                                                                                                                                         |                |

| 23.0 ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                 | 52             |

| 24.0 ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                               | 52             |

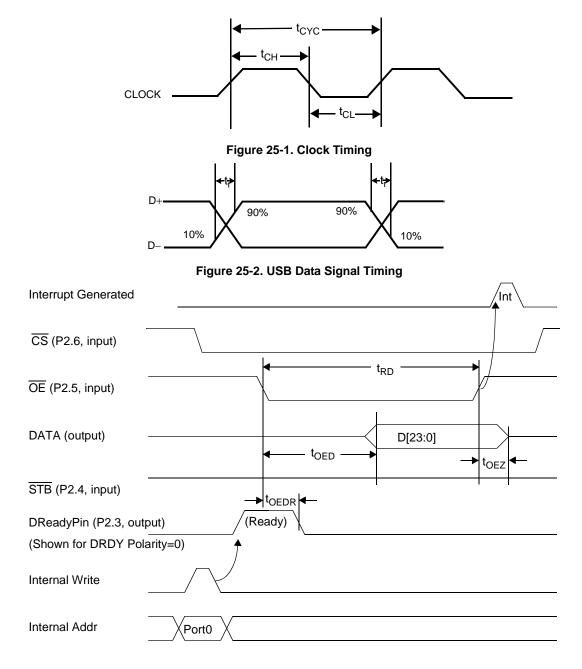

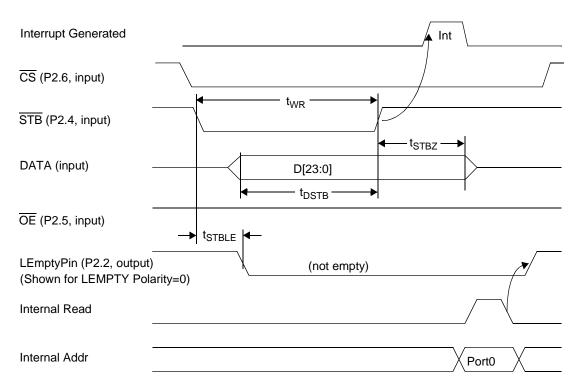

| 25.0 SWITCHING CHARACTERISTICS (fosc = 6.0 MHz)                                                                                                                                                                                               | 53             |

| 26.0 ORDERING INFORMATION                                                                                                                                                                                                                     | 55             |

| 27 0 DACKAGE DIAGDAMS                                                                                                                                                                                                                         | 56             |

# **LIST OF FIGURES**

| Figure 5-1. Program Memory Space with Interrupt Vector Table          | 15 |

|-----------------------------------------------------------------------|----|

| Figure 6-1. Clock Oscillator On-Chip Circuit                          |    |

| Figure 7-1. Watchdog Reset                                            |    |

| Figure 9-1. Block Diagram of a GPIO Pin                               |    |

|                                                                       |    |

| Figure 9-2. Port 0 Data                                               |    |

| Figure 9-3. Port1 Data                                                |    |

| Figure 9-4. Port 2 Data                                               |    |

| Figure 9-5. Port 3 Data                                               |    |

| Figure 9-6. GPIO Configuration Register                               |    |

| Figure 9-7. Port 0 Interrupt Enable                                   |    |

| Figure 9-8. Port 1 Interrupt Enable                                   |    |

| Figure 9-9. Port 2 Interrupt Enable                                   |    |

| Figure 9-10. Port 3 Interrupt Enable                                  |    |

| Figure 10-1. Block Diagram of a DAC Pin                               |    |

| Figure 10-2. DAC Port Data                                            |    |

| Figure 10-3. DAC Sink Register                                        |    |

| Figure 10-4. DAC Port Interrupt Enable                                | 23 |

| Figure 10-5. DAC Port Interrupt Polarity                              | 23 |

| Figure 11-3. Timer Block Diagram                                      | 24 |

| Figure 11-1. Timer LSB Register                                       | 24 |

| Figure 11-2. Timer MSB Register                                       | 24 |

| Figure 12-1. HAPI/I <sup>2</sup> C Configuration Register             | 24 |

| Figure 13-1. I <sup>2</sup> C Data Register                           | 25 |

| Figure 13-2. I <sup>2</sup> C Status and Control Register             | 25 |

| Figure 15-1. Processor Status and Control Register                    |    |

| Figure 16-1. Global Interrupt Enable Register                         |    |

| Figure 16-2. USB Endpoint Interrupt Enable Register                   |    |

| Figure 16-3. Interrupt Controller Function Diagram                    |    |

| Figure 16-4. GPIO Interrupt Structure                                 |    |

| Figure 18-1. Hub Ports Connect Status                                 |    |

| Figure 18-2. Hub Ports Speed                                          |    |

| Figure 18-3. Hub Ports Enable Register                                |    |

| Figure 18-4. Hub Downstream Ports Control Register                    |    |

| Figure 18-5. Hub Ports Force Low Register                             |    |

| Figure 18-6. Hub Ports Force Low Register                             |    |

| Figure 18-7. Hub Ports SE0 Status Register                            |    |

| Figure 18-8. Hub Ports Data Register                                  |    |

| Figure 18-9. Hub Ports Suspend Register                               |    |

| Figure 18-10. Hub Ports Resume Status Register                        |    |

| Figure 18-11. USB Status and Control Register                         |    |

| Figure 19-1. USB Device Address Registers                             |    |

| Figure 19-1. USB Device Address Registers                             |    |

| Figure 19-2. USB Device Enapoint Zero Mode Registers                  |    |

|                                                                       |    |

| Figure 19-4. USB Endpoint Counter Registers                           |    |

| Figure 19-5. Token/Data Packet Flow Diagram                           |    |

| Figure 22-1. Sample Schematic                                         |    |

| Figure 25-1. Clock Timing                                             |    |

| Figure 25-2. USB Data Signal Timing                                   | 54 |

| Figure 25-3. HAPI Read by External Interface from USB Microcontroller |    |

| Figure 25-4. HAPI Write by External Device to USB Microcontroller     | 55 |

# LIST OF TABLES

| Table 4-1. Pin Assignments                                                                           | 11 |

|------------------------------------------------------------------------------------------------------|----|

| Table 4-2. I/O Register Summary                                                                      | 11 |

| Table 4-3. Instruction Set Summary                                                                   |    |

| Table 9-1. GPIO Port Output Control Truth Table and Interrupt Polarity                               | 21 |

| Table 12-1. HAPI Port Configuration                                                                  | 25 |

| Table 12-2. I <sup>2</sup> C Port Configuration                                                      | 25 |

| Table 13-1. I <sup>2</sup> C Status and Control Register Bit Definitions                             |    |

| Table 14-1. Port 2 Pin and HAPI Configuration Bit Definitions                                        | 27 |

| Table 16-1. Interrupt Vector Assignments                                                             |    |

| Table 18-1. Control Bit Definition for Downstream Ports                                              | 36 |

| Table 18-2. Control Bit Definition for Upstream Port                                                 | 39 |

| Table 19-1. Memory Allocation for Endpoints                                                          | 40 |

| Table 20-1. USB Register Mode Encoding                                                               |    |

| Table 20-2. Decode Table for Table 20-3: "Details of Modes for Differing Traffic Conditions"         |    |

| Table 20-3. Details of Modes for Differing Traffic Conditions (see Table 20-2 for the decode legend) | 46 |

#### 1.0 Features

- Full-speed USB peripheral microcontroller with an integrated USB hub

- Well-suited for USB compound devices such as a keyboard hub function

- 8-bit USB optimized microcontroller

- Harvard architecture

- 6-MHz external clock source

- -12-MHz internal CPU clock

- 48-MHz internal Hub clock

- · Internal memory

- 256 bytes of RAM

- -8 KB of PROM (CY7C66013, CY7C66113)

- Integrated Master/Slave I<sup>2</sup>C-compatible controller (100 kHz) enabled through General-purpose I/O (GPIO) pins

- Hardware-assisted Parallel Interface (HAPI) for data transfer to external devices

- I/O ports

- —Three GPIO ports (Port 0 to 2) capable of sinking 8 mA per pin (typical)

- An additional GPIO port (Port 3) capable of sinking 12 mA per pin (typical) for high current requirements: LEDs

- Higher current drive achievable by connecting multiple GPIO pins together to drive a common output

- Each GPIO port can be configured as inputs with internal pull-ups or open drain outputs or traditional CMOS outputs

- A Digital-to-Analog Conversion (DAC) port with programmable current sink outputs is available on the CY7C66113 device

- Maskable interrupts on all I/O pins

- · 12-bit free-running timer with one microsecond clock ticks

- Watchdog Timer (WDT)

- Internal Power-on Reset (POR)

- USB Specification compliance

- Conforms to USB Specification, Version 1.1

- Conforms to USB HID Specification, Version 1.1

- Supports one or two device addresses with up to five user-configured endpoints

- · Up to two 8-byte control endpoints

- · Up to four 8-byte data endpoints

- · Up to two 32-byte data endpoints

- Integrated USB transceivers

- Supports four downstream USB ports

- GPIO pins can provide individual power control outputs for each downstream USB port

- GPIO pins can provide individual port over current inputs for each downstream USB port

- Improved output drivers to reduce electromagnetic interference (EMI)

- Operating voltage from 4.0V 5.5V DC

- Operating temperature from 0° 70°C

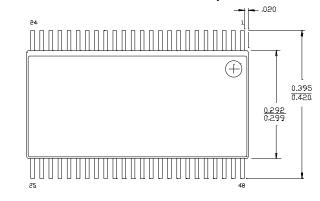

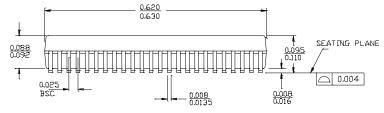

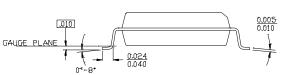

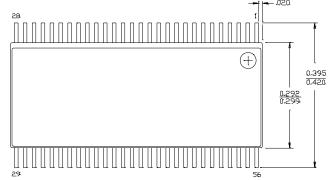

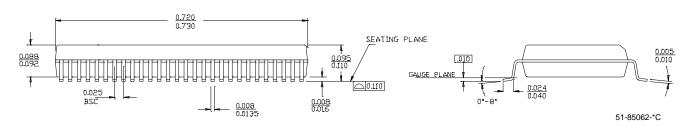

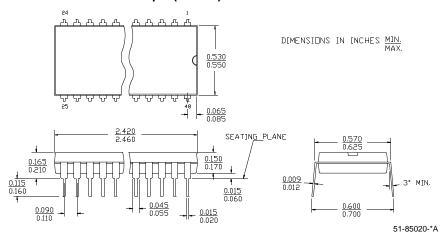

- CY7C66013 available in 48-pin PDIP (-PC) or 48-pin SSOP (-PVC) packages

- CY7C66113 available in 56-pin SSOP (-PVC) packages

- Industry-standard programmer support

Page 7 of 58

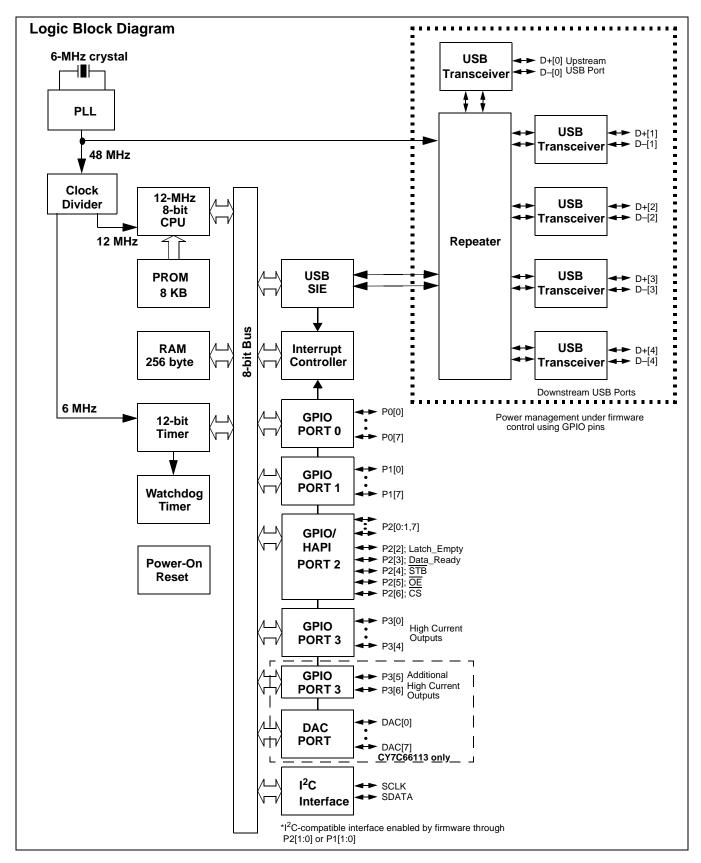

# 2.0 Functional Overview

The CY7C66013 and CY7C66113 are compound devices with a full-speed USB microcontroller in combination with a USB hub. Each device is well-suited for combination peripheral functions with hubs, such as a keyboard hub function. The eight-bit one-time-programmable microcontroller with a 12-Mbps USB Hub supports as many as four downstream ports.

#### 2.1 **GPIO**

The CY7C66013 features 29 GPIO pins to support USB and other applications. The I/O pins are grouped into four ports (P0[7:0], P1[7:0], P2[7:0], P3[4:0]) where each port can be configured as inputs with internal pull-ups, open drain outputs, or traditional CMOS outputs. Ports 0 to 2 are rated at 8 mA per pin (typical) sink current. Port 3 pins are rated at 12 mA per pin (typical) sink current, which allows these pins to drive LEDs. Multiple GPIO pins can be connected together to drive a single output for more drive current capacity. Additionally, each I/O pin can be used to generate a GPIO interrupt to the microcontroller. All of the GPIO interrupts all share the same "GPIO" interrupt vector.

The CY7C66113 has 31 GPIO pins (P0[7:0], P1[7:0], P2[7:0], P3[6:0]).

#### 2.2 DAC

The CY7C66113 have an additional port P4[7:0] that features an additional eight programmable sink current I/O pins (DAC). Every DAC pin includes an integrated 14-k $\Omega$  pull-up resistor. When a '1' is written to a DAC I/O pin, the output current sink is disabled and the output pin is driven HIGH by the internal pull-up resistor. When a '0' is written to a DAC I/O pin, the internal pull-up is disabled and the output pin provides the programmed amount of sink current. A DAC I/O pin can be used as an input with an internal pull-up by writing a '1' to the pin.

The sink current for each DAC I/O pin can be individually programmed to one of sixteen values using dedicated Isink registers. DAC bits DAC[1:0] can be used as high current outputs with a programmable sink current range of 3.2 to 16 mA (typical). DAC bits DAC[7:2] have a programmable current sink range of 0.2 to 1.0 mA (typical). Multiple DAC pins can be connected together to drive a single output that requires more sink current capacity. Each I/O pin can be used to generate a DAC interrupt to the microcontroller. Also, the interrupt polarity for each DAC I/O pin is individually programmable.

#### 2.3 Clock

The microcontroller uses an external 6-MHz crystal and an internal oscillator to provide a reference to an internal PLL-based clock generator. This technology allows the customer application to use an inexpensive 6-MHz fundamental crystal that reduces the clock-related noise emissions (EMI). A PLL clock generator provides the 6-, 12-, and 48-MHz clock signals for distribution within the microcontroller.

# 2.4 Memory

The CY7C66013 and CY7C66113 have 8 KB of PROM.

# 2.5 Power-on Reset, Watchdog, and Free-running Time

These parts include POR logic, a WDT, and a 12-bit free-running timer. The POR logic detects when power is applied to the device, resets the logic to a known state, and begins executing instructions at PROM address 0x0000. The WDT is used to ensure that the microcontroller recovers after a period of inactivity. The firmware may become inactive for a variety of reasons, including errors in the code or a hardware failure such as waiting for an interrupt that never occurs.

#### 2.6 I<sup>2</sup>C and HAPI Interface

The microcontroller can communicate with external electronics through the GPIO pins. An I<sup>2</sup>C-compatible interface accommodates a 100-kHz serial link with an external device. There is also a Hardware-assisted Parallel Interface (HAPI) which can be used to transfer data to an external device.

# 2.7 Timer

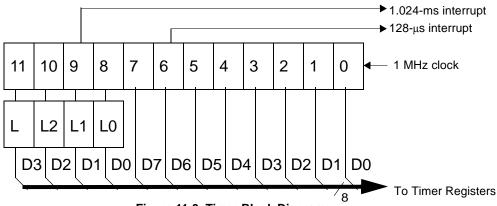

The free-running 12-bit timer clocked at 1 MHz provides two interrupt sources, 128-µs and 1.024-ms. The timer can be used to measure the duration of an event under firmware control by reading the timer at the start of the event and after the event is complete. The difference between the two readings indicates the duration of the event in microseconds. The upper four bits of the timer are latched into an internal register when the firmware reads the lower eight bits. A read from the upper four bits actually reads data from the internal register, instead of the timer. This feature eliminates the need for firmware to try to compensate if the upper four bits increment immediately after the lower eight bits are read.

Document #: 38-08024 Rev. \*A

# 2.8 Interrupts

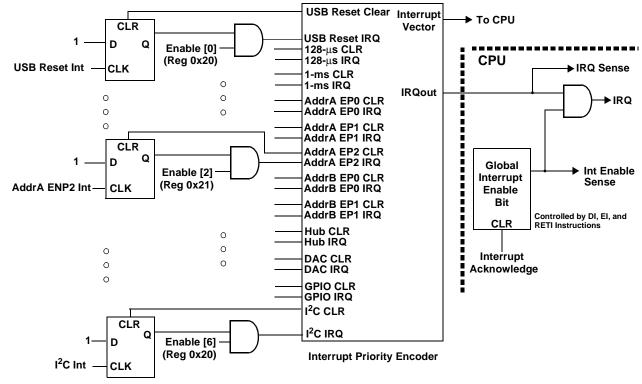

The microcontroller supports eleven maskable interrupts in the vectored interrupt controller. Interrupt sources include the 128-µs (bit 6) and 1.024-ms (bit 9) outputs from the free-running timer, five USB endpoints, the USB hub, the DAC port, the GPIO ports, and the I<sup>2</sup>C-compatible master mode interface. The timer bits cause an interrupt (if enabled) when the bit toggles from LOW '0' to HIGH '1.' The USB endpoints interrupt after the USB host has written data to the endpoint FIFO or after the USB controller sends a packet to the USB host. The DAC ports have an additional level of masking that allows the user to select which DAC inputs can cause a DAC interrupt. The GPIO ports also have a level of masking to select which GPIO inputs can cause a GPIO interrupt. For additional flexibility, the input transition polarity that causes an interrupt is programmable for each pin of the DAC port. Input transition polarity can be programmed for each GPIO port as part of the port configuration. The interrupt polarity can be rising edge ('0' to '1') or falling edge ('1' to '0').

#### 2.9 USB

The CY7C66013 and CY7C66113 include an integrated USB Serial Interface Engine (SIE) that supports the integrated peripherals and the hub controller function. The hardware supports up to two USB device addresses with one device address for the hub (two endpoints) and a device address for a compound device (three endpoints). The SIE allows the USB host to communicate with the hub and functions integrated into the microcontroller. The part includes a 1:4 hub repeater with one upstream port and four downstream ports. The USB Hub allows power-management control of the downstream ports by using GPIO pins assigned by the user firmware. The user has the option of ganging the downstream ports together with a single pair of power-management pins, or providing power management for each port with four pairs of power-management pins.

Document #: 38-08024 Rev. \*A Page 8 of 58

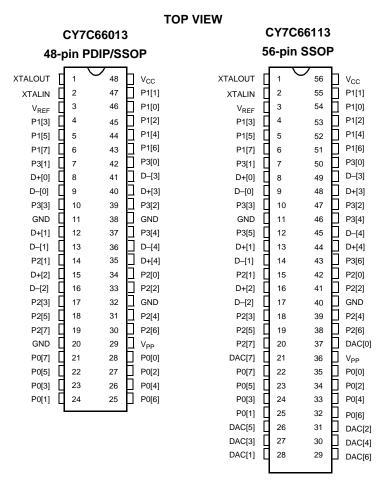

# 3.0 Pin Configurations

# 4.0 Product Summary Tables

# 4.1 Pin Assignments

Table 4-1. Pin Assignments

| Name                | I/O | 48-Pin                            | 56-Pin                            | Description                                                                                                                                                                                                                  |

|---------------------|-----|-----------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D+[0], D-[0]        | I/O | 8, 9                              | 8, 9                              | Upstream port, USB differential data.                                                                                                                                                                                        |

| D+[1], D-[1]        | I/O | 12, 13                            | 13, 14                            | Downstream port 1, USB differential data.                                                                                                                                                                                    |

| D+[2], D-[2]        | I/O | 15, 16                            | 16, 17                            | Downstream port 2, USB differential data.                                                                                                                                                                                    |

| D+[3], D-[3]        | I/O | 40, 41                            | 48, 49                            | Downstream port 3, USB differential data.                                                                                                                                                                                    |

| D+[4], D-[4]        | I/O | 35, 36                            | 44, 45                            | Downstream port 4, USB differential data.                                                                                                                                                                                    |

| P0[7:0]             | I/O | 21, 25, 22, 26,<br>23, 27, 24, 28 | 22, 32, 23, 33,<br>24, 34, 25, 35 | GPIO Port 0.                                                                                                                                                                                                                 |

| P1[7:0]             | I/O | 6, 43, 5, 44, 4,<br>45, 47, 46    | 6, 51, 5, 52, 4,<br>53, 55, 54    | GPIO Port 1.                                                                                                                                                                                                                 |

| P2[7:0]             | I/O | 19, 30, 18, 31,<br>17, 33, 14, 34 | 20, 38, 19, 39,<br>18, 41, 15, 42 | GPIO Port 2.                                                                                                                                                                                                                 |

| P3[6:0]             | I/O | 37, 10, 39, 7, 42                 | 43, 12, 46, 10,<br>47, 7, 50      | GPIO Port 3, capable of sinking 12 mA (typical).                                                                                                                                                                             |

| DAC[7:0]            | I/O | n/a                               | 21, 29, 26, 30,<br>27, 31, 28, 37 | <b>Digital to Analog Converter (DAC) Port</b> with programmable current sink outputs. DAC[1:0] offer a programmable range of 3.2 to 16 mA typical. DAC[7:2] have a programmable sink current range of 0.2 to 1.0 mA typical. |

| XTAL <sub>IN</sub>  | IN  | 2                                 | 2                                 | 6-MHz crystal or external clock input.                                                                                                                                                                                       |

| XTAL <sub>OUT</sub> | OUT | 1                                 | 1                                 | 6-MHz crystal out.                                                                                                                                                                                                           |

| V <sub>PP</sub>     |     | 29                                | 36                                | Programming voltage supply, tie to ground during normal operation.                                                                                                                                                           |

| V <sub>CC</sub>     |     | 48                                | 56                                | Voltage supply.                                                                                                                                                                                                              |

| GND                 |     | 11, 20, 32, 38                    | 11, 40                            | Ground.                                                                                                                                                                                                                      |

| V <sub>REF</sub>    | IN  | 3                                 | 3                                 | External 3.3V supply voltage for the differential data output buffers and the D+ pull-up.                                                                                                                                    |

# 4.2 I/O Register Summary

I/O registers are accessed via the I/O Read (IORD) and I/O Write (IOWR, IOWX) instructions. IORD reads data from the selected port into the accumulator. IOWR performs the reverse; it writes data from the accumulator to the selected port. Indexed I/O Write (IOWX) adds the contents of X to the address in the instruction to form the port address and writes data from the accumulator to the specified port. Specifying address 0 (e.g., IOWX 0h) means the I/O register is selected solely by the contents of X.

All undefined registers are reserved. It is important not to write to reserved registers as this may cause an undefined operation or increased current consumption during operation. When writing to registers with reserved bits, the reserved bits must be written with '0.'

Table 4-2. I/O Register Summary

| Register Name           | I/O Address | Read/Write | Function                            | Page |

|-------------------------|-------------|------------|-------------------------------------|------|

| Port 0 Data             | 0x00        | R/W        | GPIO Port 0 Data                    | 20   |

| Port 1 Data             | 0x01        | R/W        | GPIO Port 1 Data                    | 20   |

| Port 2 Data             | 0x02        | R/W        | GPIO Port 2 Data                    | 20   |

| Port 3 Data             | 0x03        | R/W        | GPIO Port 3 Data                    | 20   |

| Port 0 Interrupt Enable | 0x04        | w          | Interrupt Enable for Pins in Port 0 | 21   |

| Port 1 Interrupt Enable | 0x05        | w          | Interrupt Enable for Pins in Port 1 | 22   |

| Port 2 Interrupt Enable | 0x06        | w          | Interrupt Enable for Pins in Port 2 | 22   |

| Port 3 Interrupt Enable | 0x07        | w          | Interrupt Enable for Pins in Port 3 | 22   |

| GPIO Configuration      | 0x08        | R/W        | GPIO Port Configurations            | 20   |

Document #: 38-08024 Rev. \*A Page 11 of 58

Table 4-2. I/O Register Summary (continued)

| Register Name                           | I/O Address | Read/Write | Function                                                                                 | Page |

|-----------------------------------------|-------------|------------|------------------------------------------------------------------------------------------|------|

| HAPI and I <sup>2</sup> C Configuration | 0x09        | R/W        | HAPI Width and I <sup>2</sup> C Position Configuration                                   | 24   |

| USB Device Address A                    | 0x10        | R/W        | USB Device Address A                                                                     | 39   |

| EP A0 Counter Register                  | 0x11        | R/W        | USB Address A, Endpoint 0 Counter                                                        | 41   |

| EP A0 Mode Register                     | 0x12        | R/W        | USB Address A, Endpoint 0 Configuration                                                  | 40   |

| EP A1 Counter Register                  | 0x13        | R/W        | USB Address A, Endpoint 1 Counter                                                        | 41   |

| EP A1 Mode Register                     | 0x14        | R/W        | USB Address A, Endpoint 1 Configuration                                                  | 41   |

| EP A2 Counter Register                  | 0x15        | R/W        | USB Address A, Endpoint 2 Counter                                                        | 41   |

| EP A2 Mode Register                     | 0x16        | R/W        | USB Address A, Endpoint 2 Configuration                                                  | 41   |

| USB Status & Control                    | 0x1F        | R/W        | USB Upstream Port Traffic Status and Control                                             | 38   |

| Global Interrupt Enable                 | 0x20        | R/W        | Global Interrupt Enable                                                                  | 29   |

| Endpoint Interrupt Enable               | 0x21        | R/W        | USB Endpoint Interrupt Enables                                                           | 29   |

| Interrupt Vector                        | 0x23        | R          | Pending Interrupt Vector Read/Clear                                                      | 31   |

| Timer (LSB)                             | 0x24        | R          | Lower 8 Bits of Free-running Timer (1 MHz)                                               | 24   |

| Timer (MSB)                             | 0x25        | R          | Upper 4 Bits of Free-running Timer                                                       | 24   |

| WDT Clear                               | 0x26        | w          | Watchdog Timer Clear                                                                     | 18   |

| I <sup>2</sup> C Control & Status       | 0x28        | R/W        | I <sup>2</sup> C Status and Control                                                      | 25   |

| I <sup>2</sup> C Data                   | 0x29        | R/W        | I <sup>2</sup> C Data                                                                    | 25   |

| DAC Data                                | 0x30        | R/W        | DAC Data                                                                                 | 23   |

| DAC Interrupt Enable                    | 0x31        | w          | Interrupt Enable for each DAC Pin                                                        | 23   |

| DAC Interrupt Polarity                  | 0x32        | w          | Interrupt Polarity for each DAC Pin                                                      | 23   |

| DAC Isink                               | 0x38-0x3F   | w          | Input Sink Current Control for each DAC Pin                                              | 23   |

| USB Device Address B                    | 0x40        | R/W        | USB Device Address B (not used in 5-endpoint mode)                                       | 39   |

| EP B0 Counter Register                  | 0x41        | R/W        | USB Address B, Endpoint 0 Counter                                                        | 41   |

| EP B0 Mode Register                     | 0x42        | R/W        | USB Address B, Endpoint 0 Configuration, or USB Address A, Endpoint 3 in 5-endpoint mode | 40   |

| EP B1 Counter Register                  | 0x43        | R/W        | USB Address B, Endpoint 1 Counter                                                        | 41   |

| EP B1 Mode Register                     | 0x44        | R/W        | USB Address B, Endpoint 1 Configuration, or USB Address A, Endpoint 4 in 5-endpoint mode | 41   |

| Hub Port Connect Status                 | 0x48        | R/W        | Hub Downstream Port Connect Status                                                       | 34   |

| Hub Port Enable                         | 0x49        | R/W        | Hub Downstream Ports Enable                                                              | 35   |

| Hub Port Speed                          | 0x4A        | R/W        | Hub Downstream Ports Speed                                                               | 35   |

| Hub Port Control (Ports [4:1])          | 0x4B        | R/W        | Hub Downstream Ports Control                                                             | 36   |

| Hub Port Suspend                        | 0x4D        | R/W        | Hub Downstream Port Suspend Control                                                      | 37   |

| Hub Port Resume Status                  | 0x4E        | R          | Hub Downstream Ports Resume Status                                                       | 37   |

| Hub Ports SE0 Status                    | 0x4F        | R          | Hub Downstream Ports SE0 Status                                                          | 36   |

| Hub Ports Data                          | 0x50        | R          | Hub Downstream Ports Differential data                                                   | 37   |

| Hub Downstream Force Low                | 0x51        | R/W        | Hub Downstream Ports Force LOW                                                           | 36   |

| Processor Status & Control              | 0xFF        | R/W        | Microprocessor Status and Control Register                                               | 28   |

Document #: 38-08024 Rev. \*A Page 12 of 58

# 4.3 Instruction Set Summary

Refer to the CYASM Assembler User's Guide for more details.

Table 4-3. Instruction Set Summary

| MNEMONIC       | operand | opcode  | cycles |

|----------------|---------|---------|--------|

| HALT           |         | 00      | 7      |

| ADD A,expr     | data    | 01      | 4      |

| ADD A,[expr]   | direct  | 02      | 6      |

| ADD A,[X+expr] | index   | 03      | 7      |

| ADC A,expr     | data    | 04      | 4      |

| ADC A,[expr]   | direct  | 05      | 6      |

| ADC A,[X+expr] | index   | 06      | 7      |

| SUB A,expr     | data    | 07      | 4      |

| SUB A,[expr]   | direct  | 08      | 6      |

| SUB A,[X+expr] | index   | 09      | 7      |

| SBB A,expr     | data    | 0A      | 4      |

| SBB A,[expr]   | direct  | 0B      | 6      |

| SBB A,[X+expr] | index   | 0C      | 7      |

| OR A,expr      | data    | 0D      | 4      |

| OR A,[expr]    | direct  | 0E      | 6      |

| OR A,[X+expr]  | index   | 0F      | 7      |

| AND A,expr     | data    | 10      | 4      |

| AND A,[expr]   | direct  | 11      | 6      |

| AND A,[X+expr] | index   | 12      | 7      |

| XOR A,expr     | data    | 13      | 4      |

| XOR A,[expr]   | direct  | 14      | 6      |

| XOR A,[X+expr] | index   | 15      | 7      |

| CMP A,expr     | data    | 16      | 5      |

| CMP A,[expr]   | direct  | 17      | 7      |

| CMP A,[X+expr] | index   | 18      | 8      |

| MOV A,expr     | data    | 19      | 4      |

| MOV A,[expr]   | direct  | 1A      | 5      |

| MOV A,[X+expr] | index   | 1B      | 6      |

| MOV X,expr     | data    | 1C      | 4      |

| MOV X,[expr]   | direct  | 1D      | 5      |

| reserved       |         | 1E      |        |

| XPAGE          |         | 1F      | 4      |

| MOV A,X        |         | 40      | 4      |

| MOV X,A        |         | 41      | 4      |

| MOV PSP,A      |         | 60      | 4      |

| CALL           | addr    | 50 - 5F | 10     |

| JMP            | addr    | 80-8F   | 5      |

| CALL           | addr    | 90-9F   | 10     |

| JZ             | addr    | A0-AF   | 5      |

| JNZ            | addr    | B0-BF   | 5      |

| MNEMONIC       | operand | opcode | cycles |  |

|----------------|---------|--------|--------|--|

| NOP            |         | 20     | 4      |  |

| INC A          | acc     | 21     | 4      |  |

| INC X          | Х       | 22     | 4      |  |

| INC [expr]     | direct  | 23     | 7      |  |

| INC [X+expr]   | index   | 24     | 8      |  |

| DEC A          | acc     | 25     | 4      |  |

| DEC X          | Х       | 26     | 4      |  |

| DEC [expr]     | direct  | 27     | 7      |  |

| DEC [X+expr]   | index   | 28     | 8      |  |

| IORD expr      | address | 29     | 5      |  |

| IOWR expr      | address | 2A     | 5      |  |

| POP A          |         | 2B     | 4      |  |

| POP X          |         | 2C     | 4      |  |

| PUSH A         |         | 2D     | 5      |  |

| PUSH X         |         | 2E     | 5      |  |

| SWAP A,X       |         | 2F     | 5      |  |

| SWAP A,DSP     |         | 30     | 5      |  |

| MOV [expr],A   | direct  | 31     | 5      |  |

| MOV [X+expr],A | index   | 32     | 6      |  |

| OR [expr],A    | direct  | 33     | 7      |  |

| OR [X+expr],A  | index   | 34     | 8      |  |

| AND [expr],A   | direct  | 35     | 7      |  |

| AND [X+expr],A | index   | 36     | 8      |  |

| XOR [expr],A   | direct  | 37     | 7      |  |

| XOR [X+expr],A | index   | 38     | 8      |  |

| IOWX [X+expr]  | index   | 39     | 6      |  |

| CPL            |         | 3A     | 4      |  |

| ASL            |         | 3B     | 4      |  |

| ASR            |         | 3C     | 4      |  |

| RLC            |         | 3D     | 4      |  |

| RRC            |         | 3E     | 4      |  |

| RET            |         | 3F     | 8      |  |

| DI             |         | 70     | 4      |  |

| El             |         | 72     | 4      |  |

| RETI           |         | 73     | 8      |  |

| JC             | addr    | C0-CF  | 5      |  |

| JNC            | addr    | D0-DF  | 5      |  |

| JACC           | addr    | E0-EF  | 7      |  |

| INDEX          | addr    | F0-FF  | 14     |  |

|                |         |        |        |  |

Document #: 38-08024 Rev. \*A Page 13 of 58

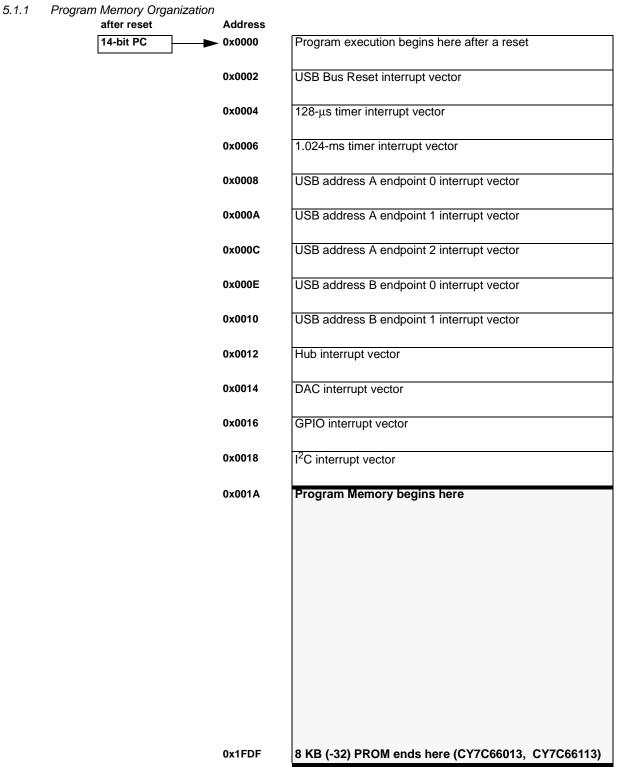

# 5.0 Programming Model

# 5.1 14-bit Program Counter (PC)

The 14-bit Program Counter (PC) allows access to up to 8 KB of PROM available with the CY7C66x13 architecture. The top 32 bytes of the ROM in the 8K part are reserved for testing purposes. The program counter is cleared during reset, such that the first instruction executed after a reset is at address 0x0000h. Typically, this is a jump instruction to a reset handler that initializes the application (see Section 16.1, Interrupt Vectors, on page 30).

The lower eight bits of the program counter are incremented as instructions are loaded and executed. The upper six bits of the program counter are incremented by executing an XPAGE instruction. As a result, the last instruction executed within a 256-byte "page" of sequential code should be an XPAGE instruction. The assembler directive "XPAGEON" causes the assembler to insert XPAGE instructions automatically. Because instructions can be either one or two bytes long, the assembler may occasionally need to insert a NOP followed by an XPAGE to execute correctly.

The address of the next instruction to be executed, the carry flag, and the zero flag are saved as two bytes on the program stack during an interrupt acknowledge or a CALL instruction. The program counter, carry flag, and zero flag are restored from the program stack during a RETI instruction. Only the program counter is restored during a RET instruction.

The program counter cannot be accessed directly by the firmware. The program stack can be examined by reading SRAM from location 0x00 and up.

Document #: 38-08024 Rev. \*A Page 14 of 58

Figure 5-1. Program Memory Space with Interrupt Vector Table

#### 5.2 8-Bit Accumulator (A)

The accumulator is the general-purpose register for the microcontroller.

## 5.3 8-Bit Temporary Register (X)

The "X" register is available to the firmware for temporary storage of intermediate results. The microcontroller can perform indexed operations based on the value in X. Refer to Section 5.6.3 for additional information.

# 5.4 8-Bit Program Stack Pointer (PSP)

During a reset, the Program Stack Pointer (PSP) is set to 0x00 and "grows" upward from this address. The PSP may be set by firmware, using the MOV PSP,A instruction. The PSP supports interrupt service under hardware control and CALL, RET, and RETI instructions under firmware control. The PSP is not readable by the firmware.

During an interrupt acknowledge, interrupts are disabled and the 14-bit program counter, carry flag, and zero flag are written as two bytes of data memory. The first byte is stored in the memory addressed by the PSP, then the PSP is incremented. The second byte is stored in memory addressed by the PSP, and the PSP is incremented again. The overall effect is to store the program counter and flags on the program "stack" and increment the PSP by two.

The Return From Interrupt (RETI) instruction decrements the PSP, then restores the second byte from memory addressed by the PSP. The PSP is decremented again and the first byte is restored from memory addressed by the PSP. After the program counter and flags have been restored from stack, the interrupts are enabled. The overall effect is to restore the program counter and flags from the program stack, decrement the PSP by two, and reenable interrupts.

The Call Subroutine (CALL) instruction stores the program counter and flags on the program stack and increments the PSP by two.

The Return From Subroutine (RET) instruction restores the program counter but not the flags from the program stack and decrements the PSP by two.

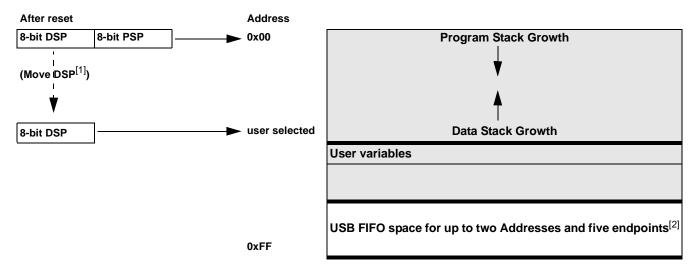

#### 5.4.1 Data Memory Organization

The CY7C66x13 microcontrollers provide 256 bytes of data RAM. Normally, the SRAM is partitioned into four areas: program stack, user variables, data stack, and USB endpoint FIFOs. The following is one example of where the program stack, data stack, and user variables areas could be located.

# 5.5 8-Bit Data Stack Pointer (DSP)

The Data Stack Pointer (DSP) supports PUSH and POP instructions that use the data stack for temporary storage. A PUSH instruction pre-decrements the DSP, then writes data to the memory location addressed by the DSP. A POP instruction reads data from the memory location addressed by the DSP, then post-increments the DSP.

During a reset, the DSP is reset to 0x00. A PUSH instruction when DSP equals 0x00 writes data at the top of the data RAM (address 0xFF). This writes data to the memory area reserved for USB endpoint FIFOs. Therefore, the DSP should be indexed at an appropriate memory location that does not compromise the Program Stack, user-defined memory (variables), or the USB endpoint FIFOs.

#### Notes:

- 1. Refer to Section 5.5 for a description of DSP.

- 2. Endpoint sizes are fixed by the Endpoint Size Bit (I/O register 0x1F, Bit 7), see Table 19-1.

For USB applications, the firmware should set the DSP to an appropriate location to avoid a memory conflict with RAM dedicated to USB FIFOs. The memory requirements for the USB endpoints are described in Section 19.2. Example assembly instructions to do this with two device addresses (FIFOs begin at 0xD8) are shown below:

MOV A,20h ; Move 20 hex into Accumulator (must be D8h or less)

SWAP A,DSP; swap accumulator value into DSP register.

#### 5.6 Address Modes

The CY7C66013 and CY7C66113 microcontrollers support three addressing modes for instructions that require data operands: data, direct, and indexed.

#### 5.6.1 Data (Immediate)

"Data" address mode refers to a data operand that is actually a constant encoded in the instruction. As an example, consider the instruction that loads A with the constant 0xD8:

MOV A, 0D8h.

This instruction requires two bytes of code where the first byte identifies the "MOV A" instruction with a data operand as the second byte. The second byte of the instruction is the constant "0xD8". A constant may be referred to by name if a prior "EQU" statement assigns the constant value to the name. For example, the following code is equivalent to the example shown above:

- DSPINIT: EQU 0D8h

- MOV A, DSPINIT.

#### 5.6.2 Direct

"Direct" address mode is used when the data operand is a variable stored in SRAM. In that case, the one byte address of the variable is encoded in the instruction. As an example, consider an instruction that loads A with the contents of memory address location 0x10:

• MOV A, [10h].

Normally, variable names are assigned to variable addresses using "EQU" statements to improve the readability of the assembler source code. As an example, the following code is equivalent to the example shown above:

- buttons: EQU 10h

- MOV A, [buttons].

#### 5.6.3 Indexed

"Indexed" address mode allows the firmware to manipulate arrays of data stored in SRAM. The address of the data operand is the sum of a constant encoded in the instruction and the contents of the "X" register. Normally, the constant is the "base" address of an array of data and the X register contains an index that indicates which element of the array is actually addressed:

- · array: EQU 10h

- MOV X, 3

- MOV A, [X+array].

This would have the effect of loading A with the fourth element of the SRAM "array" that begins at address 0x10. The fourth element would be at address 0x13.

# 6.0 Clocking

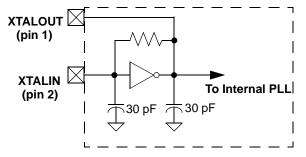

Figure 6-1. Clock Oscillator On-Chip Circuit

The XTALIN and XTALOUT are the clock pins to the microcontroller. The user can connect an external oscillator or a crystal to these pins. When using an external crystal, keep PCB traces between the chip leads and crystal as short as possible (less than 2 cm). A 6-MHz fundamental frequency parallel resonant crystal can be connected to these pins to provide a reference frequency for the internal PLL. The two internal 30-pF load caps appear in series to the external crystal and would be equivalent to a 15-pF

Document #: 38-08024 Rev. \*A Page 17 of 58

load. Therefore, the crystal must have a required load capacitance of about 15–18 pF. A ceramic resonator does not allow the microcontroller to meet the timing specifications of full speed USB and therefore a ceramic resonator is not recommended with these parts.

An external 6-MHz clock can be applied to the XTALIN pin if the XTALOUT pin is left open. Grounding the XTALOUT pin when driving XTALIN with an oscillator does not work because the internal clock is effectively shorted to ground.

#### 7.0 Reset

The CY7C66x13 supports two resets: POR and a Watchdog Reset (WDR). Each of these resets causes:

- all registers to be restored to their default states

- the USB device addresses to be set to 0

- · all interrupts to be disabled

- the PSP and DSP to be set to memory address 0x00.

The occurrence of a reset is recorded in the Processor Status and Control Register, as described in Section 15.0. Bits 4 and 6 are used to record the occurrence of POR and WDR, respectively. Firmware can interrogate these bits to determine the cause of a reset.

Program execution starts at ROM address 0x0000 after a reset. Although this looks like interrupt vector 0, there is an important difference. Reset processing does NOT push the program counter, carry flag, and zero flag onto program stack. The firmware reset handler should configure the hardware before the "main" loop of code. Attempting to execute a RET or RETI in the firmware reset handler causes unpredictable execution results.

#### 7.1 Power-on Reset

When  $V_{CC}$  is first applied to the chip, the POR signal is asserted and the CY7C66x13 enters a "semi-suspend" state. During the semi-suspend state, which is different from the suspend state defined in the USB specification, the oscillator and all other blocks of the part are functional, except for the CPU. This semi-suspend time ensures that both a valid  $V_{CC}$  level is reached and that the internal PLL has time to stabilize before full operation begins. When the  $V_{CC}$  has risen above approximately 2.5V, and the oscillator is stable, the POR is deasserted and the on-chip timer starts counting. The first 1 ms of suspend time is not interruptible, and the semi-suspend state continues for an additional 95 ms unless the count is bypassed by a USB Bus Reset on the upstream port. The 95 ms provides time for  $V_{CC}$  to stabilize at a valid operating voltage before the chip executes code.

If a USB Bus Reset occurs on the upstream port during the 95 ms semi-suspend time, the semi-suspend state is aborted and program execution begins immediately from address 0x0000. In this case, the Bus Reset interrupt is pending but not serviced until firmware sets the USB Bus Reset Interrupt Enable bit (bit 0 of register 0x20) and enables interrupts with the EI command.

The POR signal is asserted whenever  $V_{CC}$  drops below approximately 2.5V, and remains asserted until  $V_{CC}$  rises above this level again. Behavior is the same as described above.

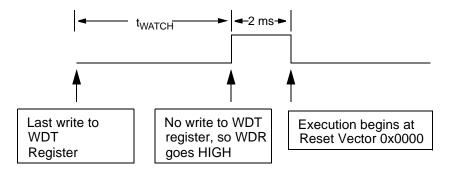

# 7.2 Watchdog Reset

The WDR occurs when the internal WDT rolls over. Writing any value to the write-only Watchdog Restart Register at address 0x26 clears the timer. The timer rolls over and WDR occurs if it is not cleared within t<sub>WATCH</sub> (8 ms minimum) of the last clear. Bit 6 of the Processor Status and Control Register is set to record this event (the register contents are set to 010X0001 by the WDR). A WDT Reset lasts for 2 ms, after which the microcontroller begins execution at ROM address 0x0000.

Figure 7-1. Watchdog Reset

The USB transmitter is disabled by a WDR because the USB Device Address Registers are cleared (see Section 19.1). Otherwise, the USB Controller would respond to all address 0 transactions.

Document #: 38-08024 Rev. \*A Page 18 of 58

It is possible for the WDR bit of the Processor Status and Control Register (0xFF) to be set following a POR event. If a firmware interrogates the Processor Status and Control Register for a set condition on the WDR bit, the WDR bit should be ignored if the POR (bit 3 of register 0xFF) bit is set.

# 8.0 Suspend Mode

The CY7C66x13 can be placed into a low-power state by setting the Suspend bit of the Processor Status and Control register. All logic blocks in the device are turned off except the GPIO interrupt logic and the USB receiver. The clock oscillator and PLL, as well as the free-running and WDTs, are shut down. Only the occurrence of an enabled GPIO interrupt or non-idle bus activity at a USB upstream or downstream port wakes the part from suspend. The Run bit in the Processor Status and Control Register must be set to resume a part out of suspend.

The clock oscillator restarts immediately after exiting suspend mode. The microcontroller returns to a fully functional state 1 ms after the oscillator is stable. The microcontroller executes the instruction following the I/O write that placed the device into suspend mode before servicing any interrupt requests.

The GPIO interrupt allows the controller to wake-up periodically and poll system components while maintaining a very low average power consumption. To achieve the lowest possible current during suspend mode, all I/O should be held at V<sub>CC</sub> or Gnd. This also applies to internal port pins that may not be bonded in a particular package.

Typical code for entering suspend is shown below:

.. ; All GPIO set to low-power state (no floating pins).. ; Enable GPIO interrupts if desired for wake-up

mov a, 09h : Set suspend and run bits

iowr FFh ; Write to Status and Control Register - Enter suspend, wait for USB activity (or GPIO Interrupt)

nop ; This executes before any ISR

... ; Remaining code for exiting suspend routine.

# 9.0 General-purpose I/O (GPIO) Ports

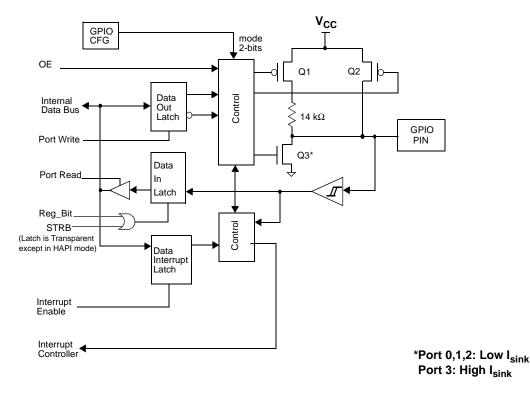

Figure 9-1. Block Diagram of a GPIO Pin

Document #: 38-08024 Rev. \*A Page 19 of 58

There are up to 31 GPIO pins (P0[7:0], P1[7:0], P2[7:0], and P3[6:0]) for the hardware interface. The number of GPIO pins changes based on the package type of the chip. Each port can be configured as inputs with internal pull-ups, open drain outputs, or traditional CMOS outputs. Port 3 offers a higher current drive, with typical current sink capability of 12 mA. The data for each GPIO port is accessible through the data registers. Port data registers are shown in *Figure 9-2* through *Figure 9-5*, and are set to 1 on reset.

| Port 0 Data |      |      |      |      |      |      |      |      |

|-------------|------|------|------|------|------|------|------|------|

| Bit #       | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Bit Name    | P0.7 | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0 |

| Read/Write  | R/W  |

| Reset       | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Figure 9-2. Port 0 Data

| Port 1 Data |      |      |      |      |          |      |      |      |

|-------------|------|------|------|------|----------|------|------|------|

| Bit #       | 7    | 6    | 5    | 4    | 3        | 2    | 1    | 0    |

| Bit Name    | P1.7 | P1.6 | P1.5 | P1.4 | Reserved | P1.2 | P1.1 | P1.0 |

| Read/Write  | R/W  | R/W  | R/W  | R/W  | R/W      | R/W  | R/W  | R/W  |

| Reset       | 1    | 1    | 1    | 1    | 1        | 1    | 1    | 1    |

Figure 9-3. Port1 Data

| Port 2 Data |      |      |      |      |      |          |          | ADDRESS 0x02 |

|-------------|------|------|------|------|------|----------|----------|--------------|

| Bit #       | 7    | 6    | 5    | 4    | 3    | 2        | 1        | 0            |

| Bit Name    | P2.7 | P2.6 | P2.5 | P2.4 | P2.3 | Reserved | Reserved | Reserved     |

| Read/Write  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W      | R/W      | R/W          |

| Reset       | 1    | 1    | 1    | 1    | 1    | 1        | 1        | 1            |

Figure 9-4. Port 2 Data

| Port 3 Data |          | -        | ā.       | _        | =        | _        | _    | ADDRESS UXUS |

|-------------|----------|----------|----------|----------|----------|----------|------|--------------|

| Bit #       | 7        | 6        | 5        | 4        | 3        | 2        | 1    | 0            |

| Bit Name    | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | P3.1 | P3.0         |

| Read/Write  | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W  | R/W          |

| Reset       | 1        | 1        | 1        | 1        | 1        | 1        | 1    | 1            |

Figure 9-5. Port 3 Data

Special care should be taken with any unused GPIO data bits. An unused GPIO data bit, either a pin on the chip or a port bit that is not bonded on a particular package, must not be left floating when the device enters the suspend state. If a GPIO data bit is left floating, the leakage current caused by the floating bit may violate the suspend current limitation specified by the USB specifications. If a '1' is written to the unused data bit and the port is configured with open drain outputs, the unused data bit remains in an indeterminate state. Therefore, if an unused port bit is programmed in open-drain mode, it must be written with a '0.' Notice that the CY7C66013 always requires that P3[7:5] be written with a '0.' When the CY7C66113 is used the P3[7] should be written with a '0.'

In normal non-HAPI mode, reads from a GPIO port always return the present state of the voltage at the pin, independent of the settings in the Port Data Registers. If HAPI mode is activated for a port, reads of that port return latched data as controlled by the HAPI signals (see Section 14.0). During reset, all of the GPIO pins are set to a high impedance input state ('1' in open drain mode). Writing a '0' to a GPIO pin drives the pin LOW. In this state, a '0' is always read on that GPIO pin unless an external source overdrives the internal pull-down device.

#### 9.1 **GPIO Configuration Port**

Every GPIO port can be programmed as inputs with internal pull-ups, outputs LOW or HIGH, or Hi-Z (floating, the pin is not driven internally). In addition, the interrupt polarity for each port can be programmed. The Port Configuration bits (*Figure 9-6*) and the Interrupt Enable bit (*Figure 9-7* through *Figure 9-10*) determine the interrupt polarity of the port pins.

| <b>GPIO Configurat</b> | SPIO Configuration     |                        |                        |                        |                        |                        |                        |                        |  |

|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--|

| Bit #                  | 7                      | 6                      | 5                      | 4                      | 3                      | 2                      | 1                      | 0                      |  |

| Bit Name               | Port 3<br>Config Bit 1 | Port 3<br>Config Bit 0 | Port 2<br>Config Bit 1 | Port 2<br>Config Bit 0 | Port 1<br>Config Bit 1 | Port 1<br>Config Bit 0 | Port 0<br>Config Bit 1 | Port 0<br>Config Bit 0 |  |

| Read/Write             | R/W                    |  |

| Reset                  | 0                      | 0                      | 0                      | 0                      | 0                      | 0                      | 0                      | 0                      |  |

Figure 9-6. GPIO Configuration Register

Document #: 38-08024 Rev. \*A Page 20 of 58

As shown in *Table 9-1* below, a positive polarity on an input pin represents a rising edge interrupt (LOW to HIGH), and a negative polarity on an input pin represents a falling edge interrupt (HIGH to LOW).

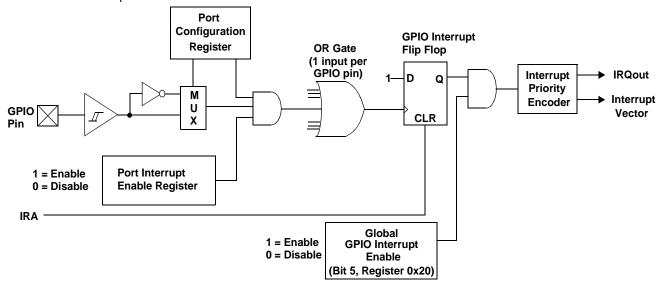

The GPIO interrupt is generated when all of the following conditions are met: the Interrupt Enable bit of the associated Port Interrupt Enable Register is enabled, the GPIO Interrupt Enable bit of the Global Interrupt Enable Register (*Figure 16-1*) is enabled, the Interrupt Enable Sense (bit 2, *Figure 15-1*) is set, and the GPIO pin of the port sees an event matching the interrupt polarity.

The driving state of each GPIO pin is determined by the value written to the pin's Data Register (*Figure 9-2* through *Figure 9-5*) and by its associated Port Configuration bits as shown in the GPIO Configuration Register (*Figure 9-6*). These ports are configured on a per-port basis, so all pins in a given port are configured together. The possible port configurations are detailed in *Table 9-1*. As shown in this table below, when a GPIO port is configured with CMOS outputs, interrupts from that port are disabled.

During reset, all of the bits in the GPIO Configuration Register are written with '0' to select Hi-Z mode for all GPIO ports as the default configuration.

| Port Config Bit 1 | Port Config Bit 0 | Data Register | Output Drive Strength | Interrupt Enable Bit | Interrupt Polarity |

|-------------------|-------------------|---------------|-----------------------|----------------------|--------------------|

| 1                 | 1                 | 0             | Output LOW            | 0                    | Disabled           |

|                   |                   | 1             | Resistive             | 1                    | - (Falling Edge)   |

| 1                 | 0                 | 0             | Output LOW            | 0                    | Disabled           |

|                   |                   | 1             | Output HIGH           | 1                    | Disabled           |

| 0                 | 1                 | 0             | Output LOW            | 0                    | Disabled           |

|                   |                   | 1             | Hi-Z                  | 1                    | - (Falling Edge)   |

| 0                 | 0                 | 0             | Output LOW            | 0                    | Disabled           |

|                   |                   | 1             | Hi-Z                  | 1                    | + (Rising Edge)    |

Table 9-1. GPIO Port Output Control Truth Table and Interrupt Polarity

Q1, Q2, and Q3 discussed below are the transistors referenced in Figure 9-1. The available GPIO drive strength are:

- Output LOW Mode: The pin's Data Register is set to '0'

Writing '0' to the pin's Data Register puts the pin in output LOW mode, regardless of the contents of the Port Configuration

Bits[1:0]. In this mode, Q1 and Q2 are OFF. Q3 is ON. The GPIO pin is driven LOW through Q3.

- Output HIGH Mode: The pin's Data Register is set to 1 and the Port Configuration Bits[1:0] is set to '10' In this mode, Q1 and Q3 are OFF. Q2 is ON. The GPIO is pulled up through Q2. The GPIO pin is capable of sourcing ... of current

- Resistive Mode: The pin's Data Register is set to 1 and the Port Configuration Bits[1:0] is set to '11'

Q2 and Q3 are OFF. Q1 is ON. The GPIO pin is pulled up with an internal 14kΩ resistor. In resistive mode, the pin may serve as an input. Reading the pin's Data Register returns a logic HIGH if the pin is not driven LOW by an external source.

- **Hi-Z Mode**: The pin's Data Register is set to1 and Port Configuration Bits[1:0] is set either '00' or '01' Q1, Q2, and Q3 are all OFF. The GPIO pin is not driven internally. In this mode, the pin may serve as an input. Reading the Port Data Register returns the actual logic value on the port pins.

# 9.2 GPIO Interrupt Enable Ports

Each GPIO pin can be individually enabled or disabled as an interrupt source. The Port 0–3 Interrupt Enable registers provide this feature with an interrupt enable bit for each GPIO pin. When HAPI mode (Section 14.0) is enabled the GPIO interrupts are blocked, including ports not used by HAPI, so GPIO pins cannot be used as interrupt sources.

During a reset, GPIO interrupts are disabled by clearing all of the GPIO interrupt enable ports. Writing a '1' to a GPIO Interrupt Enable bit enables GPIO interrupts from the corresponding input pin. All GPIO pins share a common interrupt, as discussed in Section 16.8.

| Port 0 Interrupt I | ort 0 Interrupt Enable AD |                     |                     |                     |                     |                     |                     |                     |

|--------------------|---------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| Bit #              | 7                         | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

| Bit Name           | P0.7 Intr<br>Enable       | P0.6 Intr<br>Enable | P0.5 Intr<br>Enable | P0.4 Intr<br>Enable | P0.3 Intr<br>Enable | P0.2 Intr<br>Enable | P0.1 Intr<br>Enable | P0.0 Intr<br>Enable |

| Read/Write         | w                         | W                   | W                   | w                   | W                   | W                   | w                   | W                   |

| Reset              | 0                         | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

Figure 9-7. Port 0 Interrupt Enable

Document #: 38-08024 Rev. \*A Page 21 of 58

| Port 1 Interrupt | ort 1 Interrupt Enable |                     |                     |                     |          |                     |                     |                     |

|------------------|------------------------|---------------------|---------------------|---------------------|----------|---------------------|---------------------|---------------------|

| Bit #            | 7                      | 6                   | 5                   | 4                   | 3        | 2                   | 1                   | 0                   |

| Bit Name         | P1.7 Intr<br>Enable    | P1.6 Intr<br>Enable | P1.5 Intr<br>Enable | P1.4 Intr<br>Enable | Reserved | P0.2 Intr<br>Enable | P1.1 Intr<br>Enable | P1.0 Intr<br>Enable |

| Read/Write       | w                      | w                   | w                   | w                   | w        | w                   | w                   | w                   |

| Reset            | 0                      | 0                   | 0                   | 0                   | 0        | 0                   | 0                   | 0                   |

Figure 9-8. Port 1 Interrupt Enable

| Port 2 Interrupt | ort 2 Interrupt Enable |                     |                     |                     |                     |          |          |          |  |

|------------------|------------------------|---------------------|---------------------|---------------------|---------------------|----------|----------|----------|--|

| Bit #            | 7                      | 6                   | 5                   | 4                   | 3                   | 2        | 1        | 0        |  |

| Bit Name         | P0.7 Intr<br>Enable    | P0.6 Intr<br>Enable | P0.5 Intr<br>Enable | P0.4 Intr<br>Enable | P0.3 Intr<br>Enable | Reserved | Reserved | Reserved |  |

| Read/Write       | w                      | W                   | w                   | w                   | w                   | w        | w        | w        |  |

| Reset            | 0                      | 0                   | 0                   | 0                   | 0                   | 0        | 0        | 0        |  |

Figure 9-9. Port 2 Interrupt Enable

| Port 3 Interrupt | rt 3 Interrupt Enable ADD |          |          |          |          |          |                     |                     |  |

|------------------|---------------------------|----------|----------|----------|----------|----------|---------------------|---------------------|--|

| Bit #            | 7                         | 6        | 5        | 4        | 3        | 2        | 1                   | 0                   |  |

| Bit Name         | Reserved                  | Reserved | Reserved | Reserved | Reserved | Reserved | P3.1 Intr<br>Enable | P0.3 Intr<br>Enable |  |

| Read/Write       | w                         | w        | w        | W        | w        | w        | w                   | w                   |  |

| Reset            | 0                         | 0        | 0        | 0        | 0        | 0        | 0                   | 0                   |  |

Figure 9-10. Port 3 Interrupt Enable

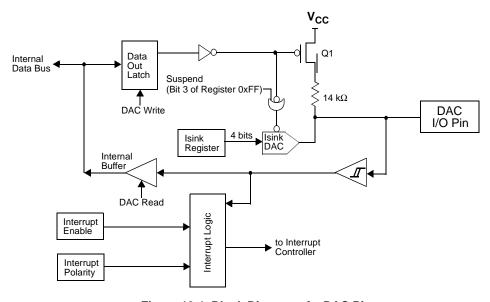

#### 10.0 DAC Port

The CY7C66113 features a programmable sink current 8 bit port which is also known as DAC port. Each of these port I/O pins have a programmable current sink. Writing a '1' to a DAC I/O pin disables the output current sink ( $I_{sink}$  DAC) and drives the I/O pin HIGH through an integrated 14-k $\Omega$  resistor. When a '0' is written to a DAC I/O pin, the  $I_{sink}$  DAC is enabled and the pull-up resistor is disabled. This causes the  $I_{sink}$  DAC to sink current to drive the output LOW. *Figure 10-1* shows a block diagram of the DAC port pin.

Figure 10-1. Block Diagram of a DAC Pin

The amount of sink current for the DAC I/O pin is programmable over 16 values based on the contents of the DAC Isink Register (*Figure 10-3*) for that output pin. DAC[1:0] are high current outputs that are programmable from 3.2 mA to 16 mA (typical). DAC[7:2] are low current outputs, programmable from 0.2 mA to 1.0 mA (typical).

When the suspend bit in Processor Status and Control Register (*Figure 15-1*) is set, the Isink DAC block of the DAC circuitry is disabled. Special care should be taken when the CY7C66113 device is placed in the suspend. The DAC Port Data Register(*Figure 10-2*) should normally be loaded with all '1's (*Figure 15-1*) before setting the suspend bit. If any of the DAC bits

Document #: 38-08024 Rev. \*A Page 22 of 58

are set to '0' when the device is suspended, that DAC input will float. The floating pin could result in excessive current consumption by the device, unless an external load places the pin in a deterministic state.

**DAC Port Data** ADDRESS 0x30 Bit # **Bit Name** DAC[7] DAC[6] DAC[5] DAC[4] DAC[3] DAC[2] DAC[1] DAC[0] Read/Write R/W R/W R/W R/W R/W R/W R/W R/W Reset 1

Figure 10-2. DAC Port Data

# Bit [1..0]: High Current Output 3.2 mA to 16 mA typical

1= I/O pin is an output pulled HGH through the 14-k $\Omega$  resistor. 0 = I/O pin is an input with an internal 14-k $\Omega$  pull-up resistor.

#### Bit [7..2]: Low Current Output 0.2 mA to 1 mA typical

1= I/O pin is an output pulled HGH through the 14-k $\Omega$  resistor. 0 = I/O pin is an input with an internal 14-k $\Omega$  pull-up resistor.

# 10.1 DAC Isink Registers

Each DAC I/O pin has an associated DAC Isink register to program the output sink current when the output is driven LOW. The first Isink register (0x38) controls the current for DAC[0], the second (0x39) for DAC[1], and so on until the Isink register at 0x3F, controls the current to DAC[7].

| DAC SINK Regist | ter      |          |          |          |          |          | ADDR     | ESS 0X38 -0X3F |

|-----------------|----------|----------|----------|----------|----------|----------|----------|----------------|

| Bit #           | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0              |

| Bit Name        | Reserved | Reserved | Reserved | Reserved | Isink[3] | Isink[2] | Isink[1] | Isink[0]       |

| Read/Write      |          |          |          |          | W        | W        | w        | w              |

| Reset           | -        | -        | -        | -        | 0        | 0        | 0        | 0              |

Figure 10-3. DAC Sink Register

#### Bit [4..0]: Isink [x] (x= 0..4)

Writing all '0's to the Isink register causes 1/5 of the max current to flow through the DAC I/O pin. Writing all '1's to the Isink register provides the maximum current flow through the pin. The other 14 states of the DAC sink current are evenly spaced between these two values.

#### Bit [7..5]: Reserved

#### 10.2 DAC Port Interrupts

A DAC port interrupt can be enabled/disabled for each pin individually. The DAC Port Interrupt Enable register provides this feature with an interrupt enable bit for each DAC I/O pin. All of the DAC Port Interrupt Enable register bits are cleared to '0' during a reset. All DAC pins share a common interrupt, as explained in Section 16.7.

| DAC Port Interru | ıpt          | ā.           | _            | _            | _            | _            | _            | ADDRESS 0x31 |

|------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Bit #            | 7            | 6            | 5            | 4            | 3            | 2            | 1            | 0            |

| Bit Name         | Enable Bit 7 | Enable Bit 6 | Enable Bit 5 | Enable Bit 4 | Enable Bit 3 | Enable Bit 2 | Enable Bit 1 | Enable Bit 0 |

| Read/Write       | w            | w            | w            | w            | w            | w            | w            | w            |

| Reset            | 0            | 0            | 0            | 0            | 0            | 0            | 0            | 0            |

Figure 10-4. DAC Port Interrupt Enable

#### Bit [7..0]: Enable bit x (x = 0..7)

1= Enables interrupts from the corresponding bit position; 0= Disables interrupts from the corresponding bit position

As an additional benefit, the interrupt polarity for each DAC pin is programmable with the DAC Port Interrupt Polarity register. Writing a '0' to a bit selects negative polarity (falling edge) that causes an interrupt (if enabled) if a falling edge transition occurs on the corresponding input pin. Writing a '1' to a bit in this register selects positive polarity (rising edge) that causes an interrupt (if enabled) if a rising edge transition occurs on the corresponding input pin. All of the DAC Port Interrupt Polarity register bits are cleared during a reset.

| DAC Port Interru | DAC Port Interrupt AD |              |              |              |              |              |              |              |

|------------------|-----------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Bit #            | 7                     | 6            | 5            | 4            | 3            | 2            | 1            | 0            |

| Bit Name         | Enable Bit 7          | Enable Bit 6 | Enable Bit 5 | Enable Bit 4 | Enable Bit 3 | Enable Bit 2 | Enable Bit 1 | Enable Bit 0 |

| Read/Write       | W                     | w            | W            | W            | W            | W            | W            | W            |

Figure 10-5. DAC Port Interrupt Polarity

Document #: 38-08024 Rev. \*A Page 23 of 58

| - |       |   |     |   |   |   |   |   |     |

|---|-------|---|-----|---|---|---|---|---|-----|

| 1 | Reset | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0   |

|   |       | _ | 1 ~ | _ | _ | ~ | ~ | _ | 1 - |

Figure 10-5. DAC Port Interrupt Polarity

## Bit [7..0]: Enable bit x (x = 0..7)

- 1= Selects positive polarity (rising edge) that causes an interrupt (if enabled);

- 0= Selects negative polarity (falling edge) that causes an interrupt (if enabled).

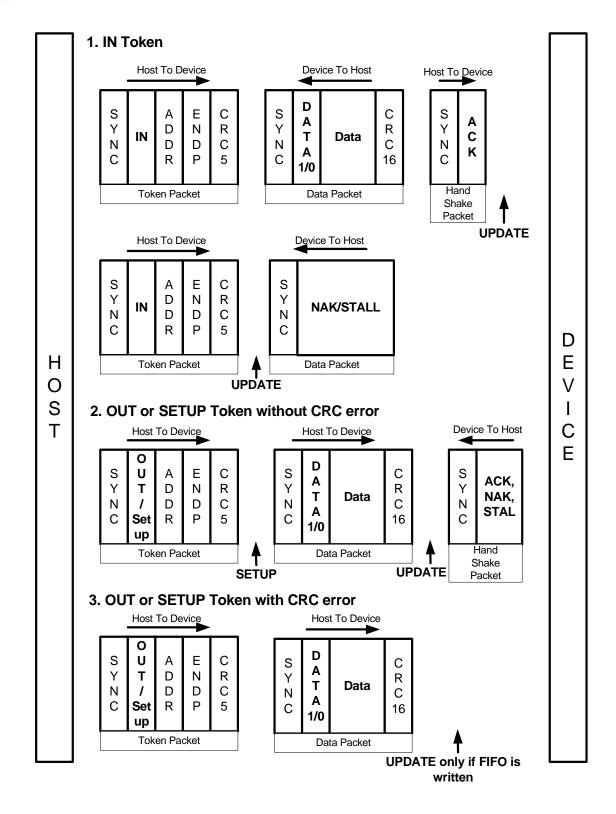

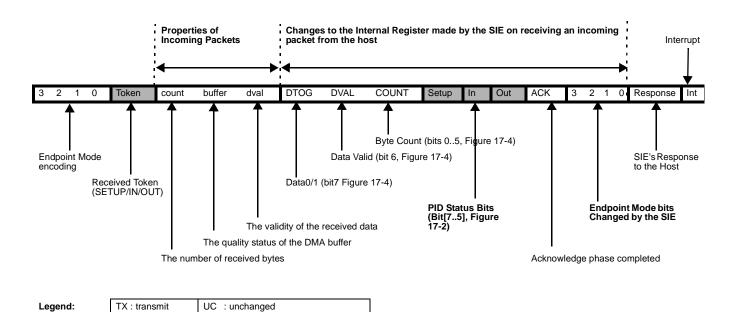

# 11.0 12-bit Free-running Timer