# **BL1700**

**C-Programmable Controller**

# **User's Manual**

019-0048 • 020415-G

## **BL1700 User's Manual**

Part Number 019-0048 • 020415-G • Printed in U.S.A.

© 1999–2002 Z-World, Inc. • All rights reserved.

Z-World reserves the right to make changes and improvements to its products without providing notice.

### Notice to Users

Z-WORLD PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE-SUPPORT DEVICES OR SYSTEMS UNLESS A SPE-CIFIC WRITTEN AGREEMENT REGARDING SUCH INTENDED USE IS ENTERED INTO BETWEEN THE CUSTOMER AND Z-WORLD PRIOR TO USE. Life-support devices or systems are devices or systems intended for surgical implantation into the body or to sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling and user's manual, can be reasonably expected to result in significant injury.

No complex software or hardware system is perfect. Bugs are always present in a system of any size. In order to prevent danger to life or property, it is the responsibility of the system designer to incorporate redundant protective mechanisms appropriate to the risk involved.

### Trademarks

- Dynamic  $C^{^{(\!\!\!\!\)}}$  is a registered trademark of Z-World

- Windows<sup>®</sup> is a registered trademark of Microsoft Corporation

- PLCBus<sup>TM</sup> is a trademark of Z-World

- Hayes Smart Modem<sup>®</sup> is a registered trademark of Hayes Microcomputer Products, Inc.

**Z-World, Inc.** 2900 Spafford Street Davis, California 95616-6800 USA Telephone:(530)757-3737Facsimile:(530)757-3792Web Site:http://www.zworld.comE-Mail:zworld@zworld.com

# TABLE OF CONTENTS

### **About This Manual**

| Chapter 1: <b>Overview</b>       | 11 |

|----------------------------------|----|

| Overview                         | 12 |

| Features                         | 13 |

| Flexibility and Customization    | 14 |

| Standard Models                  | 14 |

| Customization Options            | 14 |

| Development and Evaluation Tools | 15 |

| Development Kit                  | 15 |

| Software                         | 15 |

| CE Compliance                    | 16 |

####

| Connecting the BL1700 to a Host PC         |  |

|--------------------------------------------|--|

| Establishing Communication with the BL1700 |  |

| Running a Sample Program                   |  |

#### Chapter 3: BL1700 Hardware

| •                                          |    |

|--------------------------------------------|----|

| Operating Modes                            | 24 |

| Changing the Operating Mode                |    |

| Run Mode                                   |    |

| BL1700 Subsystems Overview                 |    |

| Microprocessor Core Module                 |    |

| Core Module External Connections           |    |

| Digital Inputs and Outputs                 |    |

| External Connections                       |    |

| Digital Inputs                             |    |

| Operating Modes and Configuration          |    |

| Digital Outputs                            |    |

| Operating Modes and Configuration          |    |

| High-Voltage Drivers                       |    |

| Pulse-Width Modulation (PWM) Configuration |    |

|                                            |    |

vii

23

| Analog Inputs                              |  |

|--------------------------------------------|--|

| Operating Modes and Configuration          |  |

| Drift                                      |  |

| Low-Pass Filter                            |  |

| Excitation Resistors                       |  |

| Using the Unconditioned Converter Channels |  |

| Internal Test Voltages                     |  |

| Power-Down Mode                            |  |

| External Connections                       |  |

| Serial Channels                            |  |

| Operating Modes and Configuration          |  |

| Configuring a Multidrop Network            |  |

| RS-485 Termination                         |  |

| External Connections                       |  |

| PLCBus                                     |  |

| Operating Modes and Configuration          |  |

| External Connections                       |  |

# Chapter 4: Software Development

| Supplied Software                   |    |

|-------------------------------------|----|

| Digital Inputs                      |    |

| How to Read the Input               |    |

| Sample Program                      |    |

| Digital Outputs                     | 61 |

| Sample Program                      |    |

| Pulse-Width Modulated (PWM) Outputs |    |

| How to Use the PWM Feature          |    |

| PWM Software                        |    |

| Sample Program                      |    |

| Analog Inputs                       |    |

| Using the Analog Inputs             |    |

| Sample Program                      |    |

| Serial Channels                     |    |

| RS-232 Communication                |    |

| RS-485 Communication                |    |

| Software                            | 71 |

| Sample Program                      | 71 |

| LED                                 |    |

| Additional Software                 |    |

|                                     |    |

57

| Appendix A: Troubleshooting                 | 73  |

|---------------------------------------------|-----|

| Out of the Box                              | 74  |

| LCD Connected to BL1700 Does Not Work       | 74  |

| Dynamic C Will Not Start                    | 75  |

| BL1700 Resets Repeatedly                    | 76  |

| Troubleshooting Software                    | 76  |

| Appendix B: Specifications                  | 77  |

| Electronic and Mechanical Specifications    | 78  |

| BL1700 Mechanical Dimensions                | 79  |

| Header and Jumper Information               | 80  |

| Protected Digital Inputs                    |     |

| Frequency Response for the Protected Inputs |     |

| High-Voltage Drivers                        |     |

| Sinking Driver                              |     |

| Sourcing Driver                             |     |

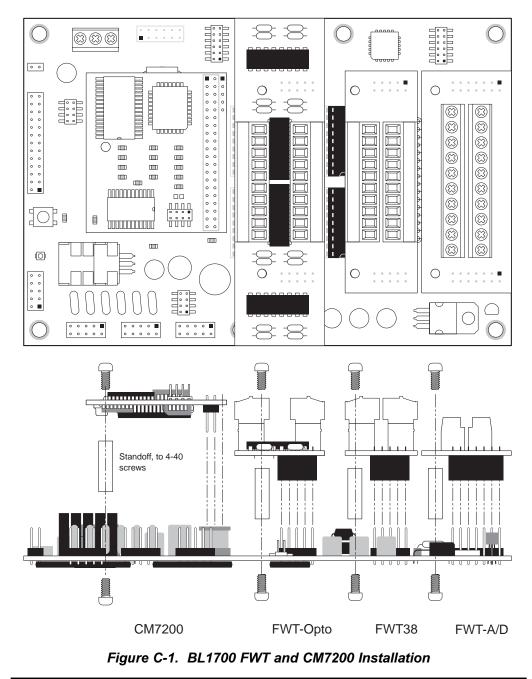

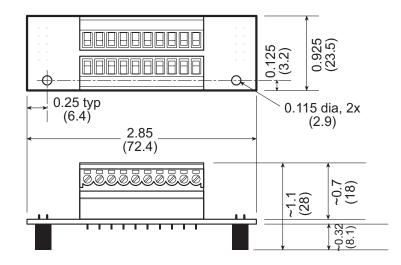

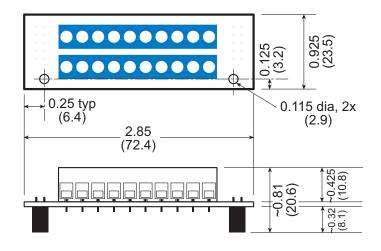

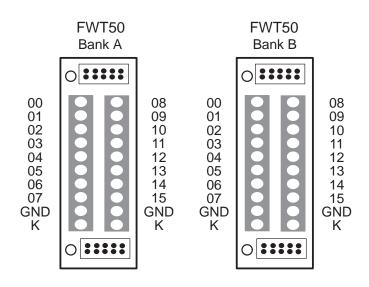

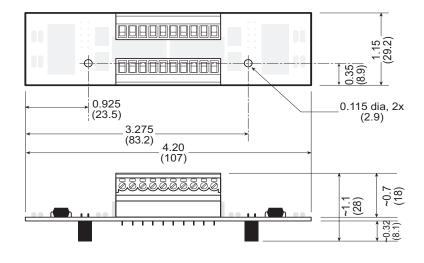

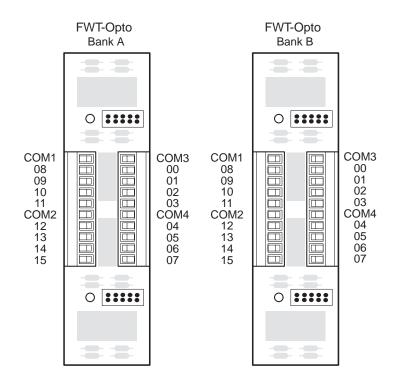

| Appendix C: Field Wiring Terminals (FWT)    |     |

| and DIN Rails                               | 89  |

| Field Wiring Terminals                      |     |

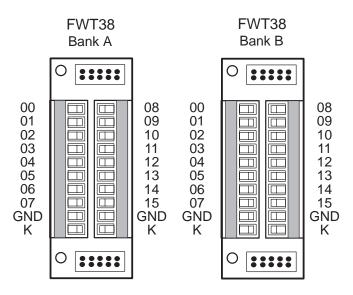

| FWT38                                       |     |

| FWT50                                       |     |

| FWT-Opto                                    |     |

| FWT-A/D                                     |     |

| DIN Rails                                   |     |

| Appendix D: Sinking and Sourcing Drivers    | 99  |

| BL1700 Series Sinking and Sourcing Outputs  |     |

| Installing Sourcing Drivers                 |     |

| TTL/CMOS Outputs                            |     |

| Using Output Drivers                        |     |

| Using Output Drivers                        | 103 |

| Appendix E: PLCBus                          | 105 |

| PLCBus Overview                             |     |

| Allocation of Devices on the Bus            |     |

| 4-Bit Devices                               |     |

| 8-Bit Devices                               |     |

| Expansion Bus Software                      |     |

|                                             |     |

|                            | <i>vi</i> • Contents                |

|----------------------------|-------------------------------------|

| Downloaded from Elcodis.co | m electronic components distributor |

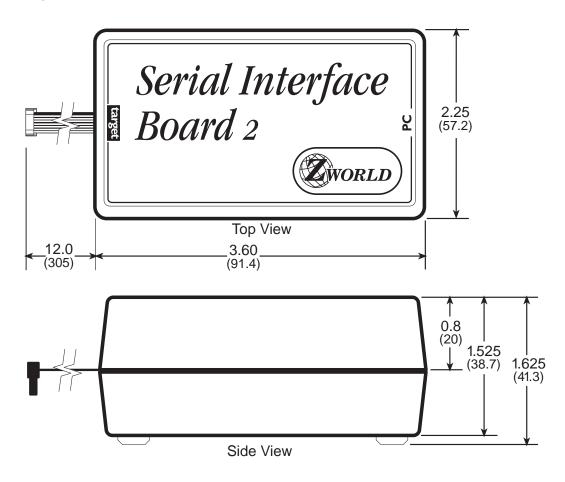

| Appendix F: Serial Interface Board 2 | 117 |

|--------------------------------------|-----|

| Introduction                         |     |

| External Dimensions                  |     |

# Appendix G: Advanced Topics

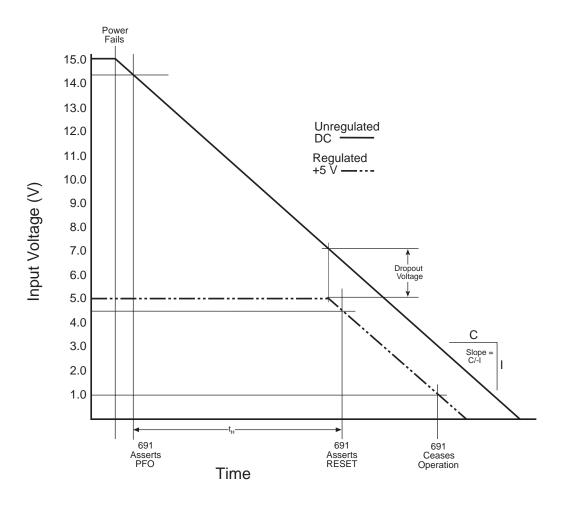

| Power Management                                        | 122 |

|---------------------------------------------------------|-----|

| Power Failure Detection Circuitry                       | 122 |

| Power Failure Sequence of Events                        | 122 |

| Memory Map                                              | 125 |

| Input/Output Select Map                                 | 125 |

| Z180 Internal Input/Output Register Addresses 0x00-0x3F | 125 |

| BL1700 Peripheral Addresses                             | 127 |

| Epson 72423 Timer Registers 0x4180–0x418F               |     |

| Interrupts                                              | 129 |

| Interrupt Service Routines                              | 129 |

| Interrupt Vectors                                       | 130 |

| Jump Vectors                                            | 131 |

| Flash EPROM                                             | 132 |

| Simulated EEPROM                                        | 132 |

| Other Flash EPROM Software                              | 133 |

| Pulse-Width Modulation (PWM) Software                   | 134 |

| PWM Addressing Detail                                   | 134 |

| PWM Software                                            | 138 |

| Sample Program                                          | 140 |

|                                                         |     |

# Appendix H: Battery

| Battery Life and Storage Conditions | 142 |

|-------------------------------------|-----|

| Replacing Soldered Lithium Battery  | 142 |

| Battery Cautions                    | 143 |

### Index

**Schematics**

145

141

121

#### 1<del>4</del>J

BL1700

# **ABOUT THIS MANUAL**

This manual provides instructions for installing, testing, configuring, and interconnecting the Z-World BL1700 controller. Instructions are also provided for using Dynamic C functions.

# Assumptions

Assumptions are made regarding the user's knowledge and experience in the following areas:

- Ability to design and engineer the target system that a BL1700 will control.

- Understanding of the basics of operating a software program and editing files under Windows on a PC.

- Knowledge of the basics of C programming. ٠

$\frown$  For a full treatment of C, refer to the following texts.

The C Programming Language by Kernighan and Ritchie C: A Reference Manual by Harbison and Steel

٠ Knowledge of basic Z80 assembly language and architecture.

$\frown$  For documentation from Zilog, refer to the following texts.

**Z180 MPU User's Manual Z180 Serial Communication Controllers Z80** Microprocessor Family User's Manual

# Acronyms

Table 1 lists and defines the acronyms that may be used in this manual.

| Acronym | Meaning                                                                   |  |

|---------|---------------------------------------------------------------------------|--|

| EPROM   | Erasable Programmable Read-Only Memory                                    |  |

| EEPROM  | Electronically Erasable Programmable Read-Only Memory                     |  |

| LCD     | Liquid Crystal Display                                                    |  |

| LED     | Light-Emitting Diode                                                      |  |

| NMI     | Nonmaskable Interrupt                                                     |  |

| PIO     | Parallel Input/Output Circuit<br>(Individually Programmable Input/Output) |  |

| PRT     | Programmable Reload Timer                                                 |  |

| RAM     | Random Access Memory                                                      |  |

| RTC     | Real-Time Clock                                                           |  |

| SIB     | Serial Interface Board                                                    |  |

| SRAM    | Static Random Access Memory                                               |  |

| UART    | Universal Asynchronous Receiver Transmitter                               |  |

Table 1. Acronyms

## lcons

Table 2 displays and defines icons that may be used in this manual.

| Icon         | Meaning         | lcon | Meaning      |

|--------------|-----------------|------|--------------|

| <i>&amp;</i> | Refer to or see |      | Note         |

| 7            | Please contact  | Tip  | Tip          |

|              | Caution         |      | High Voltage |

| (FD)         | Factory Default |      |              |

Table 2. Icons

# Conventions

Table 3 lists and defines the typographic conventions that may be used in this manual.

| Example   | Description                                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| while     | Courier font (bold) indicates a program, a fragment of a program, or a Dynamic C keyword or phrase.                                                  |

| // IN-01  | Program comments are written in Courier font, plain face.                                                                                            |

| Italics   | Indicates that something should be typed instead of the italicized words (e.g., in place of <i>filename</i> , type a file's name).                   |

| Edit      | Sans serif font (bold) signifies a menu or menu selection.                                                                                           |

|           | An ellipsis indicates that (1) irrelevant program text is<br>omitted for brevity or that (2) preceding program text may<br>be repeated indefinitely. |

| []        | Brackets in a C function's definition or program segment indicate that the enclosed directive is optional.                                           |

| < >       | Angle brackets occasionally enclose classes of terms.                                                                                                |

| a   b   c | A vertical bar indicates that a choice should be made from<br>among the items listed.                                                                |

Table 3. Typographic Conventions

#### Pin Number 1

A black square indicates pin 1 of all headers.

#### Measurements

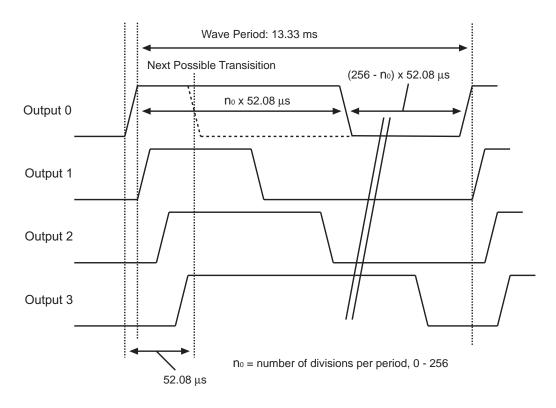

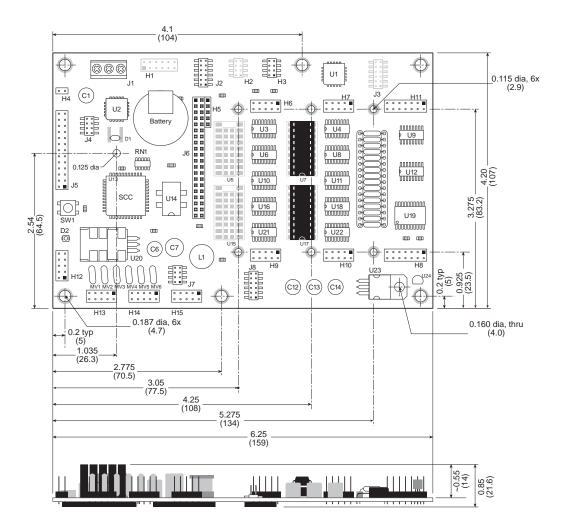

All diagram and graphic measurements are in inches followed by millimeters enclosed in parenthesis.

#### x • About This Manual

# CHAPTER 1: **OVERVIEW**

Chapter 1 provides an overview and a brief description of the BL1700 features.

# Overview

The BL1700 is a feature-rich controller with modular digital and analog I/O that allows easy custom modification. The BL1700 is programmed using Dynamic C, Z-World's version of the C programming language designed for embedded control.

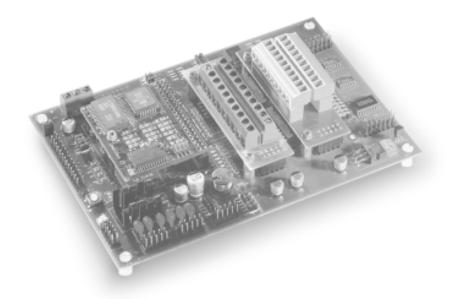

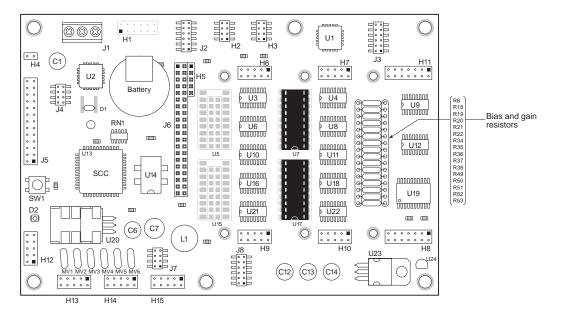

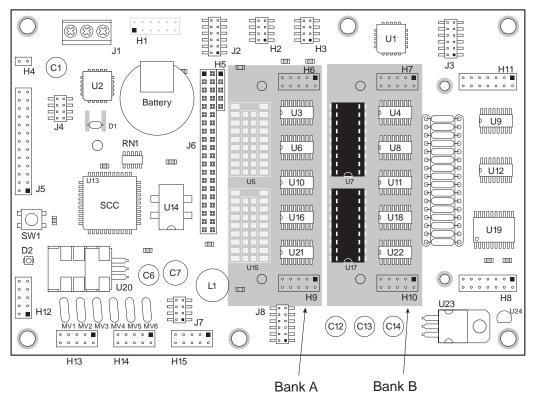

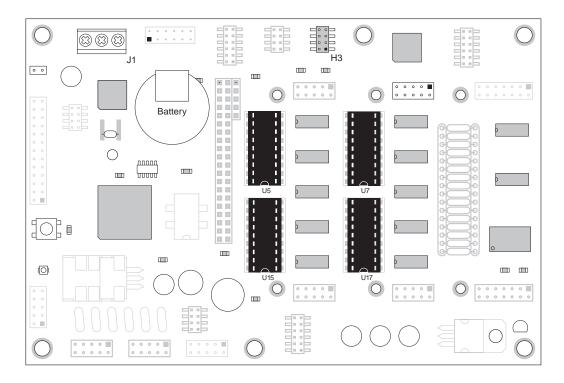

Figure 1-1 illustrates the BL1700 board layout.

Figure 1-1. BL1700 Board Layout

# Features

The BL1700 includes the following features.

#### Core Module

The BL1700 uses a core module (Z-World part number 129-0099) designed for easy, in-system programming. The core module includes the CPU, RAM, flash EPROM, real-time clock, and microprocessor watchdog circuitry.

#### • //0

Serial channels—Four full-duplex serial channels interface directly with serial I/O devices. RS-232 and RS-485 signal levels are supported.

Digital inputs—Up to 32 protected digital inputs capable of detecting logic level or high-voltage signals.

Digital outputs—Up to 32 high-voltage, high-current outputs capable of driving resistive and inductive loads.

Pulse-width modulated outputs—Up to 7 digital outputs can provide pulse-width modulation.

Analog inputs—Eight conditioned analog inputs, each with user-configurable bias and gain, interface directly with many sensors. Two unconditioned analog inputs which allow for custom signal conditioning circuitry or direct interfacing.

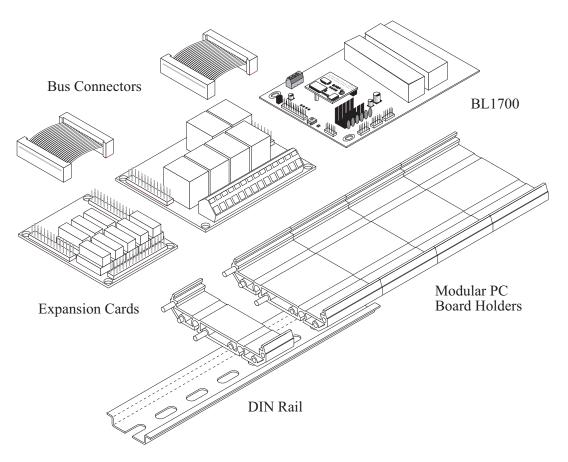

Expansion bus—I/O expansion via built-in PLCBus. The PLCBus uses inexpensive off-the-shelf Z-World expansion boards.

### • Additional Features

Field Wiring Terminals—Removable field wiring terminals in several configurations are available for the digital and analog I/O ports.

Compact form factor—Compatible with standard 100 mm wide DIN mounting products.

LED—A general-purpose, user-programmable LED is included.

DIN Rails—The Bl1700 may be mounted in 110 mm DIN rail trays.

$\mathcal{G}$

Appendix B provides detailed specifications for the BL1700.

See Appendix C, "Field Wiring Terminals (FWT) and DIN Rails," for more information on FWTs and DIN rail mounting.

# **Flexibility and Customization**

The BL1700 was designed with customization in mind. The design was optimized for cost effective, quick-turn, custom manufacturing. Surface mount technology was used extensively in order to reduce both size and cost while providing the flexibility to meet individual design needs. For quantity orders, the BL1700 can be customized to better meet the needs of your application.

#### Standard Models

The BL1700 Series of controllers currently has four versions. Table 1-1 lists the standard features for these versions.

| Model  | Features                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BL1700 | 18.432 MHz clock, 16 protected digital inputs, 16 high-<br>voltage sinking outputs, 4 full-duplex serial channels, 10<br>A/D channels, PLCBus expansion port. |

| BL1710 | BL1700 without A/D channels.                                                                                                                                  |

| BL1720 | BL1700 with two serial channels instead of four.                                                                                                              |

| BL1730 | BL1700 with two serial channels instead of four and 9.216 MHz clock.                                                                                          |

Table 1-1. BL1700 Series Features

### **Customization Options**

The BL1700 can be customized for individual applications. The options include the following configurations.

• Core module configuration—CM7100 and CM7200 core modules can be used on the BL1700. Customization options include RAM size, flash EPROM size, EPROM size, clock speed, and real-time clock option.

CM7100 and CM7200 core modules must have a 5-pin header installed at H1, and the BIOS must be customized for these core modules to be used on the BL1700.

- Digital I/O configuration—optional TTL level I/O.

- Analog input configuration—gain and offset configuration.

- Serial channel configuration—two or four serial ports.

For ordering information, or for more details about the various options and prices, call your Z-World Sales Representative at (530) 757-3737.

14 • Overview

## **Development and Evaluation Tools**

The BL1700 is supported by a Development Kit that includes everything you need to start development with the BL1700.

### **Development Kit**

The Development Kit includes these items.

- Manual with schematics.

- Programming cables and adapter. ٠

- 24 V DC wall-mount power supply. ٠

- Field wiring terminals. ٠

- Sourcing high-voltage driver ICs. •

An optional Serial Interface Board (SIB) allows full access to all serial ports during development.

### Software

The BL1700 is programmed using Z-World's Dynamic C, an integrated development environment that includes an editor, a C compiler, and a debugger. Library functions provide an easy and robust interface to the BL1700.

Z-World's Dynamic C reference manuals provide complete software descriptions and programming instructions.

# **CE Compliance**

The BL1700 has been tested by an approved competent body, and was found to be in conformity with applicable EN and equivalent standards. Note the following requirements for incorporating the BL1700 in your application to comply with CE requirements.

- The power supply provided with the Development Kit is for development purposes only. It is the customer's responsibility to provide a clean DC supply to the controller for all applications in end-products.

- Fast transients/burst tests were not performed on the BL1700. Signal and process lines that are longer than 3 m should be routed in a separate shielded conduit.

- The BL1700 has been tested to Light Industrial Immunity standards. Additional shielding or filtering may be required for an industrial environment.

- The BL1700 has been tested to EN55022 Class A emission standards. Additional shielding or filtering may be required to meet Class B emission standards.

Visit the "Technical Reference" pages of the Z-World Web site at http://www.zworld.com for more information on shielding and filtering.

# CHAPTER 2: GETTING STARTED

Chapter 2 provides instructions for connecting the BL1700 to a host PC and running a sample program. The following sections are included.

- Development Kit Packing List

- Connecting the BL1700 to Your PC

- Establishing Communication with the BL1700

- Running a Sample Program

# **Development Kit Packing List**

The BL1700 Development Kit includes the following items.

- Two serial cables with DB-9 and 10-pin header connectors.

- DB-25 to DB-9 serial adapter.

- 24 V DC wall-mount power transformer.

- Two FWT-50 field wiring terminals.

- One FWT-A/D field wiring terminal.

- Two 2985 high-voltage driver ICs.

- BL1700 User's Manual (this document).

# Connecting the BL1700 to a Host PC

The BL1700 can be programmed using a PC through an RS-232 port with the programming cable provided in the Developer's Kit. You can also use Z-World's SIB2 to program the BL1700. Using the SIB2 frees all of the serial channels for the application during development. The SIB2 is not part of the standard Developer's Kit, and must be purchased separately. Both programming methods are described below.

For ordering information, call your Z-World Sales Representative at (530) 757-3737.

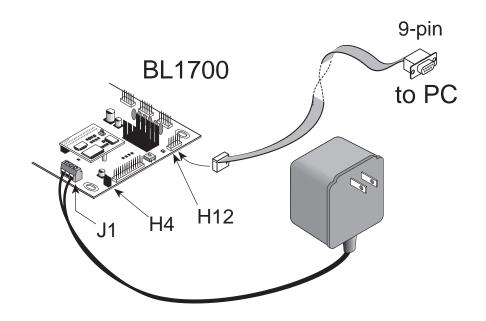

#### Connecting the BL1700 to a PC using the serial port.

- 1. Make sure that Dynamic C is installed on your system as described in the Dynamic C *Technical Reference* manual.

- 2. Connect the 10-pin programming cable from H12 on the BL1700 to the appropriate COM port of your computer as shown in Figure 2-1. Make sure that pin 1 on the ribbon cable connector (indicated by a small triangle on the connector) matches up with pin 1 on H12 (indicated by a small white circle near the corner of the connector).

Figure 2-1. BL1700 Programming Connections

Use only the transformer and programming cable supplied by Z-World.

- 3. Make sure that the Run/Program jumper on header H4 is installed.

- 4. Connect the 24 V DC transformer as follows.

- Connect the lead with the red sleeve to the screw terminal (J1) labeled DCIN on the BL1700.

- Connect the other lead to the screw terminal (J1) labeled GND.

- 5. Plug the transformer into a wall socket.

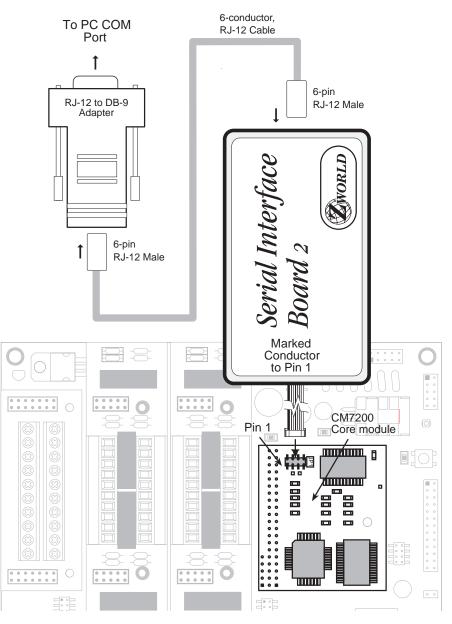

#### Connecting the BL1700 to your PC using the SIB2.

- 1. Make sure that Dynamic C is installed on your system as described in the *Dynamic C Technical Reference* manual.

- 2. Disconnect power from the BL1700. Connect an RJ-12 cable between the RJ-12/DB-9 adapter attached to the PC and the SIB2.

- 3. Plug the SIB2's 8-pin connector onto header JP1 located on the CM7200 core module (mounted on the BL1700), as shown in Figure 2-2. Make sure that pin 1 on the ribbon cable connector (on the striped side) matches up with pin 1 on JP1 (indicated by a small white circle next to the header).

Figure 2-2. SIB2 Connection (BL1700 Top View)

Use only the transformer and programming cable supplied by Z-World.

Observe the polarity of the cable and the 8-pin connector. Attach the connector to JP1 exactly as shown in Figure 2-2.

- 4. Make sure that the Run/Program jumper on header H4 is installed.

- 5. Connect the 24 V DC transformer as follows.

- Connect the lead with the red sleeve to the screw terminal (J1) labeled DCIN on the BL1700.

- Connect the other lead to the screw terminal (J1) labeled GND.

- 6. Plug the power supply into a wall socket.

# Establishing Communication with the BL1700

- 1. Double-click the Dynamic C icon to start the software. Note that communication with the BL1700 is attempted each time you start Dynamic C.

- 2. If the communication attempt is successful, no error messages are displayed.

See Appendix A, "Troubleshooting," if an error message such as **Target Not Responding** or **Communication Error** appears.

Once the necessary changes have been made to establish communication between the host PC and the BL1700, use the Dynamic C shortcut **<Ctrl Y>** to reset the controller and initiate communication.

## **Running a Sample Program**

- 1. Open the sample program **BL17FLSH**.**C** located in the Dynamic C **SAMPLES**\**BL17XX** directory. This program flashes the onboard LED.

- 2. Compile the program by pressing **F3** or by choosing **Compile** from the **Compile** menu. Dynamic C compiles and downloads the program into the BL1700's flash memory.

During compilation, Dynamic C rapidly displays several messages in the compiling window. This condition is normal.

- 3. Run the program by pressing **F9** or by choosing **Run** from the **Run** Menu.

- 4. To halt the program, press **<Ctrl Z>**. This action halts program execution.

- 5. To restart program execution, when required, press F9.

# CHAPTER 3: BL1700 HARDWARE

Chapter 3 describes the BL1700 hardware subsystems. The following sections are included.

- Operating Modes

- BL1700 Subsystems Overview

- Microprocessor Core Module

- Serial Communications Channels

- High-Voltage Digital Outputs

- Protected Digital Inputs

- Analog Inputs

- PLCBus Expansion Port

# **Operating Modes**

The BL1700 has two mutually exclusive operating modes, run mode and program mode. Each mode is explained in detail below.

Program Mode

In program mode, the BL1700 controller runs under the control of your PC that is running Dynamic C. The BL1700 must be in this mode to compile a program to the BL1700 or debug a program.

- In program mode, the BL1700 matches the baud rate of the PC COM port up to 57,600 bps.

- USER LED is "ON" in program mode.

#### • Run Mode

In run mode, the BL1700 controller runs standalone. At power-up, the BL1700 checks to see if its onboard memory contains a program. If a program exists, the BL1700 controller executes the program immediately after power-up.

- In run mode, the BL1700 does not respond to Dynamic C running on the PC. A program cannot be compiled or debugged when the BL1700 is in run mode.

- USER LED D2 is under the control of the application on the BL1700 when the BL1700 is in run mode.

Table 3-1 shows the jumper settings for the program and run modes.

Table 3-1. BL1700 Jumper Settings for Run/Program Modes

| Operating<br>Mode | Header<br>H4 | Permissible Activities                                                                                                                                                                           |

|-------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program<br>Mode   | = H4         | <ul> <li>Compile a program.</li> <li>Run a program under debugger control.</li> <li>Run a program without "polling." See your Dynamic C manuals for a description of program polling.</li> </ul> |

| Run Mode          | ■ H4         | Run application.                                                                                                                                                                                 |

#### Changing the Operating Mode

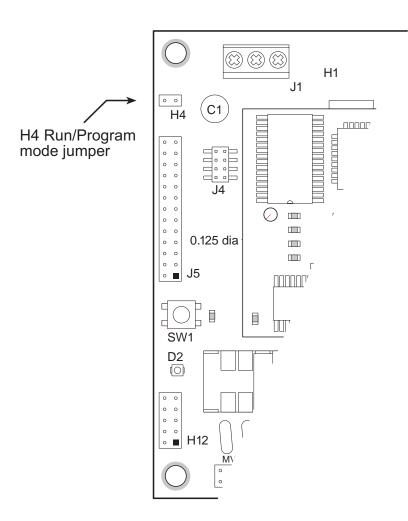

1. Locate the **Run/Program** jumper on header H4. Figure 3-1 shows the location of header H4.

#### Figure 3-1. H4 Run/Program Jumper Location

- 2. Select the desired operating mode.

- Install jumper on header H4 to select program mode.

- Remove jumper on header H4 to select run mode.

- 3. Press the reset switch SW1 to switch the BL1700 to the selected mode.

Be sure careful when installing or removing the H4 jumper if power is connected to the BL1700.

#### Run Mode

- 1. Place the BL1700 in program mode (with the H4 jumper installed) and cycle the unit's power.

- 2. Open a program if one is not already open.

- 3. Select the **Compile** command from the **Compile** menu, or press **F3** on your keyboard.

- 4. If no errors are detected, Dynamic C compiles the program and automatically downloads it into the BL1700's onboard flash memory.

- 5. Remove the **Run/Program** jumper.

- 6. Press the reset switch SW1 on the BL1700. This action resets the BL1700 and places it into run mode. The downloaded program begins to run immediately.

The downloaded program begins to run as soon as the reset switch is pressed or power is applied. Pay close attention to any electronic or mechanical devices connected to the BL1700 that could cause injury.

The program is now loaded in the BL1700's onboard flash EPROM. This program runs automatically every time the BL1700 powers up in run mode until you load another program.

Follow these steps to return to the program mode.

- 1. Re-install the **Run/Program** jumper on header **H4**. Refer to Figure 3-1 for the jumper location.

- 2. Press the reset switch on the BL1700.

Refer to the previous section, "Changing the Operating Mode," for more detailed information.

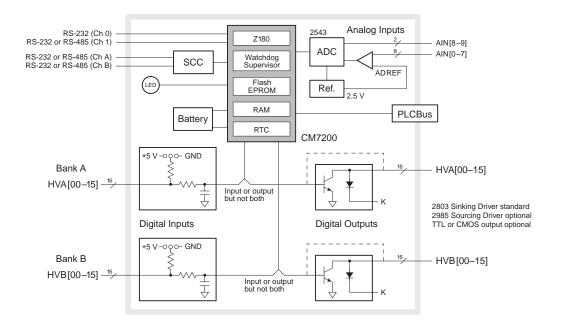

## **BL1700 Subsystems Overview**

The BL1700 is comprised of several subsystems including a microprocessor core module, serial communications channels, digital I/O, analog inputs, and PLCBus expansion port. Figure 3-2 illustrates the BL1700 subsystems.

Figure 3-2. BL1700 Block Diagram

#### Microprocessor Core Module

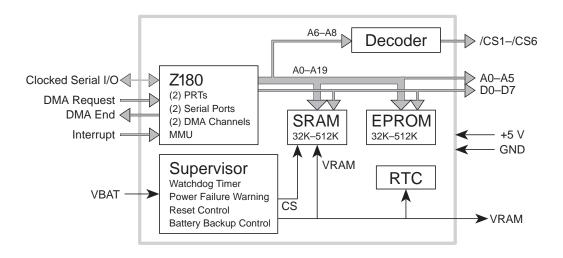

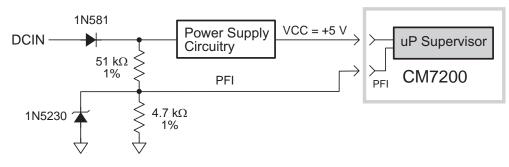

The BL1700 is built around a Z-World CM7200 Series microprocessor core module. The core module is comprised of a Zilog Z180 microprocessor, 32K of battery-backed static RAM, 128K of flash EPROM, a real-time clock, and a watchdog timer/microprocessor supervisor.

The Z180 CPU runs at 18.432 MHz. Internal to the Z180 are two asynchronous serial ports, two DMA channels, two programmable-reload timers (PRTs), and three interrupt lines.

Six chip-select lines (/CS1–/CS6) enable one of six groups of 64 I/O addresses. These lines are used to access peripherals on the BL1700 board.

The power-supervisor IC performs several functions. It provides a watchdog timer function, performs power-failure detection, RAM protection, and battery backup when the CM7200 is unpowered.

Your program can obtain the time and the date from the real-time clock.

Figure 3-3 shows a block diagram of the CM7200 microprocessor core module.

Figure 3-3. CM7200 Block Diagram

#### **Core Module External Connections**

The core module also provides connections to the Clock Serial I/O (CSIO) port on the Z180. This port can be used to program the BL1700 using Z-World's Serial Interface Board 2 (SIB2). This allows programming and debugging of the BL1700 while providing access to all the onboard serial channels.

## **Digital Inputs and Outputs**

The digital inputs and outputs are divided into two banks, A and B, as shown in Figure 3-2 and Figure 3-4. The 16 factory-default digital inputs on the BL1700, BL1710, BL1720, and BL1730 occupy Bank A, and 16 digital outputs are located on Bank B. Future and/or custom versions of the BL1700 may have both or no banks configured as digital inputs. In order for a bank to be configured as an input, the appropriate interface ICs must be installed. In order for a bank to be configured as an output, the appropriate high-voltage driver ICs must be installed. These modifications should only be performed at Z-World's manufacturing facility.

Figure 3-4. BL1700 Banks A and B

#### **External Connections**

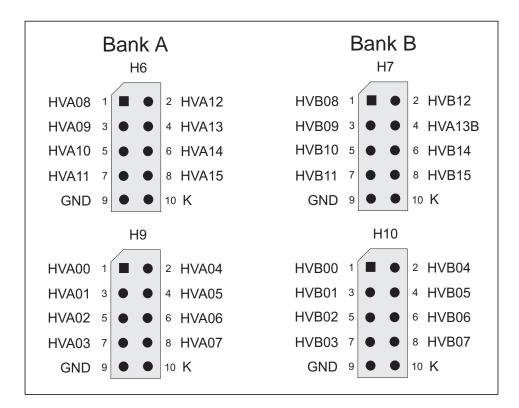

Connections to Bank A are made on headers H6 and H9. Connections to Bank B are made on headers H7 and H10. The pinouts for headers H6, H7, H9 and H10 are shown in Figure 3-5.

Figure 3-5. Pinouts for BL1700 Digital Input External Connections

Connections to the digital inputs/outputs can be made with a ribbon cable, Z-World's FWT field wiring terminals, or a custom interface board. Z-World offers FWT modules for the digital inputs in three configurations.

- Screw terminals (Z-World part number 101-0184).

- Removable screw terminals (Z-World part number 101-0185)

- Optically isolated removable screw terminals (Z-World part number 101-0186)

Input lines connected to optically isolated devices must be configured as pull-up. Otherwise, damage to the circuit may occur.

Each FWT module mates with one of the BL1700's header pairs (H6–H9 and H7–H10). Different types of field wiring terminals can be mixed on the same BL1700.

See Appendix C, "Specifications," for FWT mechanical dimensions and pinouts.

#### **Digital Inputs**

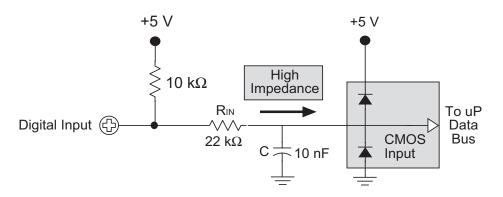

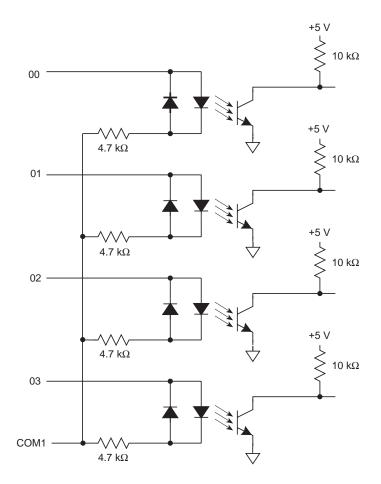

The BL1700 can provide up to 32 protected digital inputs designed as logical data inputs, returning a 1 or 0. Their normal operating range is -20 V DC to +24 V DC, and they are protected from voltages between -48 V DC and +48 V DC. The inputs can detect logic-level signals and have a nominal logic threshold of 2.5 V DC. This means an input returns a 0 if the input voltage is below 2.5 V DC and a 1 if the input voltage is above 2.5 V DC. The inputs can be pulled up to +5 V or down to ground.

A low-pass filter on each input channel has a time constant of

$T_{\rm RC} = 220 \ \mu s \ (4.5 \ \rm kHz).$

They may be configured as pull-up or pull-down in groups of fours and eights. The configuration of each input should be determined by normal operating conditions, power-down mode and possible failure modes including open or shorted conditions. These factors will influence your decision about configuring the inputs as pull-up or pull-down.

#### **Operating Modes and Configuration**

Inputs may be pulled up to +5 V or pulled down to ground by configuring the jumpers on BL1700 headers J2 and J3.

J2 jumpers select pull-up/pull-down resistors for Bank A. Jumpers on J3 select pull-up/pull-down resistors for inputs for Bank B. To change an input from the factory default of pull-up, simply place a jumper across the appropriate two pins of J2 and/or J3.

Table 3-2 and Table 3-3 illustrate the jumper settings for pull-up and pulldown configurations for the BL1700's Bank A and Bank B inputs.

The factory default is for the digital inputs to be pulled up to +5 V.

| Channel                                                                     | Jumper Settings                                       |                                                                                                   |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

| Channel                                                                     | Inputs Pulled Up                                      | Inputs Pulled Down                                                                                |  |

| HVA 8–11<br>Bank A<br>Channels<br>8–11<br>(Physical<br>Channels<br>24–27)   | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | J2<br>1<br>3<br>5<br>6<br>7<br>9<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |  |

| HVA 12–15<br>Bank A<br>Channels<br>12–15<br>(Physical<br>Channels<br>28–31) | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | J2<br>1<br>3<br>5<br>7<br>9<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1      |  |

| HVA 0–7<br>Bank A<br>Channels<br>0–7<br>(Physical<br>Channels<br>16–23)     | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                             |  |

#### Table 3-2. BL1700 Bank A Digital Input Jumper Configurations

| Channel                                                                  | Jumper Settings                                                   |                                                                                            |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| Channel                                                                  | Inputs Pulled Up                                                  | Inputs Pulled Down                                                                         |  |

| HVB 0–3<br>Bank B<br>Channels<br>0–3<br>(Physical<br>Channels<br>0–3)    | J3<br>1<br>3<br>5<br>6<br>7<br>9<br>9<br>10<br>10<br>12<br>12     | J3<br>1 0 2<br>3 0 4<br>5 0 6<br>7 0 8<br>9 0 10<br>11 0 12                                |  |

| HVB 4–7<br>Bank B<br>Channels<br>4–7<br>(Physical<br>Channels<br>4–7)    | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$             | J3<br>1<br>3<br>4<br>5<br>7<br>•<br>•<br>•<br>1<br>6<br>7<br>•<br>•<br>10<br>11<br>•<br>12 |  |

| HVB 8–15<br>Bank B<br>Channels<br>8–15<br>(Physical<br>Channels<br>8–15) | J3<br>1 • • 2<br>3 • • 4<br>5 • • 6<br>7 • 8<br>9 10<br>11 • • 12 | J3<br>1 • • 2<br>3 • • 4<br>5 • • 6<br>7 • • 8<br>9 • 10<br>11 • 12                        |  |

#### Table 3-3. BL1700 Bank B Digital Input Jumper Configurations

The high-voltage driver chips must be removed from Bank B and interface chips must be installed before the Bank B inputs can be used as digital inputs.

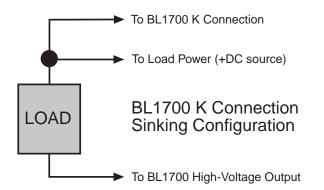

### Digital Outputs

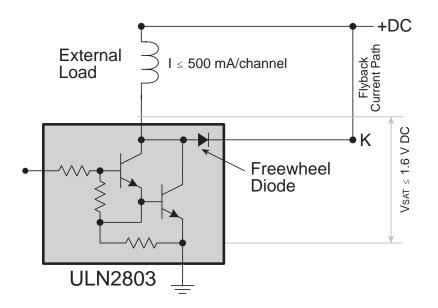

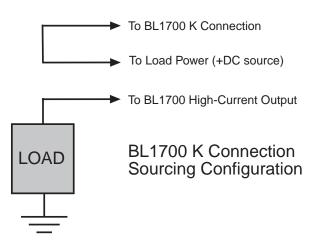

Up to 32 high-voltage, high-current digital outputs are possible on the BL1700. The digital outputs can be configured in groups of eight for either sinking or sourcing operation by setting jumpers and installing the appropriate driver ICs. Sinking drivers can sink up to 500 mA at voltages up to 48 V DC. Sourcing drivers can source up to 250 mA at voltages up to 30 V DC. All outputs are diode protected against inductive spikes.

TTL/CMOS level outputs are also possible by bypassing the driver ICs. This option is for quantity orders only, and should be performed at Z-World's manufacturing facility.

High-voltage outputs are diode protected against inductive spikes. All outputs are individually addressable.

#### **Operating Modes and Configuration**

The digital inputs and outputs are divided into two banks, Bank A and Bank B. In the factory default, digital outputs occupy Bank B and digital inputs are located on Bank A. In order for a bank to be configured as an output, the appropriate interface ICs must be installed. Z-World recommends that this be done only at Z-World's manufacturing facility.

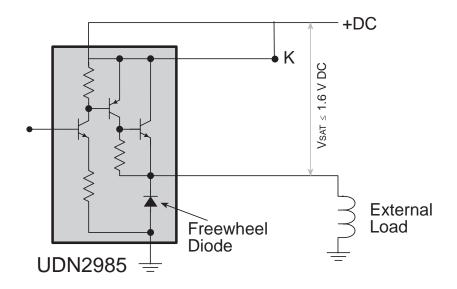

#### **High-Voltage Drivers**

Outputs may be configured for either sinking or sourcing current. The configuration is determined by the type of driver ICs installed and the jumper settings.

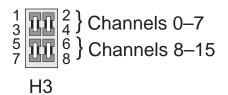

For Bank A, U5 drives outputs 8-15 and U15 drives outputs 0-7. For Bank B, U7 drives outputs 8-15 and U17 drives outputs 0-7. The jumpers placed on H3 configure sourcing/sinking modes for the outputs on Bank B. Jumpers on H2 configure sourcing/sinking modes for the outputs on Bank A (if it is configured for output). Table 3-4 and Table 3-5 show the jumper settings for sinking and sourcing configurations.

The sinking driver chips used on the BL1700 are ULN2803 or equivalent. The sourcing driver chips are UDN2985 or equivalent.

To configure drivers for sinking outputs (default for Bank B), install the ULN2803 driver chips in the appropriate socket locations. For sourcing outputs, install UDN2985 driver chips.

When installing high-voltage driver chips, make sure that pin 1 on the IC matches up with pin 1 on the socket. The chip has a small semicircular notch on one end that matches up with a similar notch on the IC socket. The chips can be removed by gently prying them out with a small screwdriver or IC extractor.

| Bank B                       | Jumper Settings                                                                              |                                                                   |

|------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Dalik D                      | Sinking Outputs                                                                              | Sourcing Outputs                                                  |

| HVB 0–7<br>Channels<br>0–7   | H3<br>1<br>3<br>5<br>7<br>1<br>1<br>2<br>4<br>6<br>8<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | H3<br>1<br>3<br>5<br>7<br>H3<br>2<br>4<br>6<br>8<br>U17 = UDN2985 |

| HVB 8–15<br>Channels<br>8–15 | H3<br>1<br>3<br>5<br>7<br>U7 = ULN2803                                                       | H3<br>1<br>3<br>5<br>7<br>U7 = UDN2985                            |

Table 3-4. BL1700 Bank B Digital Output Jumper Configurations

Also make sure that the jumpers on H3 and/or H2 are properly configured. If the jumpers are not properly set for the drivers installed, damage to both the drivers and the circuit board is possible.

Connections to Bank A are made on headers H6 and H9. Connections to Bank B are made on headers H7 and H10. The pinouts for headers H6, H7, H9 and H10 are shown in Figure 3-5 on page 30.

See Appendix B, "Specifications," for detailed specifications on the high-voltage drivers.

| Bank A                       | Jumper Settings                                                               |                                                                  |

|------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|

|                              | Sinking Outputs                                                               | Sourcing Outputs                                                 |

| HVA 8–15<br>Channels<br>8–15 | H2<br>1 $2$<br>3 $4$<br>5 $6$<br>7 $0$ $8$<br>U5 = ULN2803                    | H2<br>1<br>3<br>5<br>7<br>H2<br>2<br>4<br>6<br>8<br>U5 = UDN2985 |

| HVA 0–7<br>Channels<br>0–7   | H2<br>$1 \\ 2 \\ 4 \\ 6 \\ 7 \\ 15 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10$ | H2<br>1<br>3<br>5<br>7<br>U15 = UDN2985                          |

Table 3-5. BL1700 Bank A Digital Output Jumper Configurations

The digital interface chips must be removed from Bank A and high-voltage driver chips must be installed before the Bank A inputs can be used as outputs.

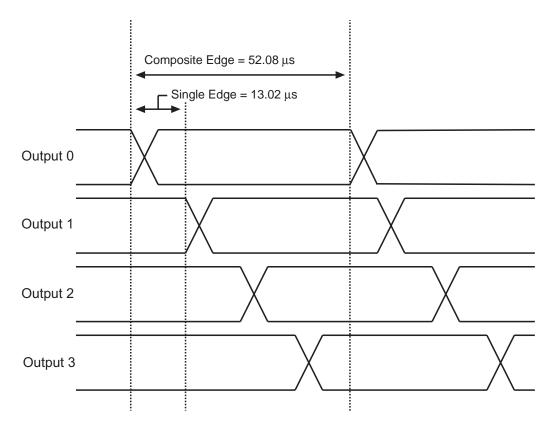

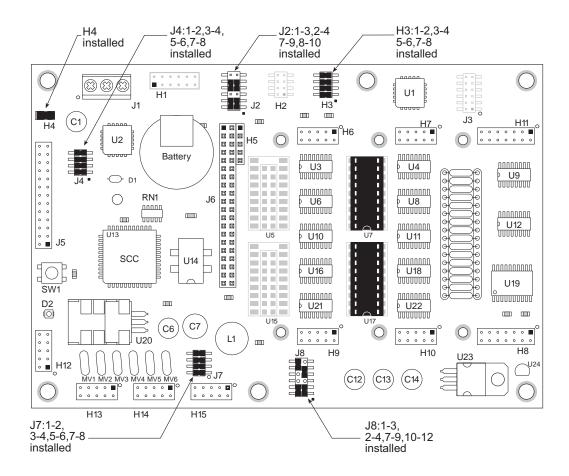

### **Pulse-Width Modulation (PWM) Configuration**

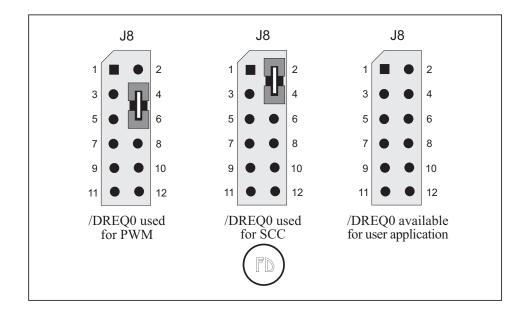

In order to use the PWM feature of the digital outputs, J8 must be jumpered from pin 4 to pin 6. See Figure 3-6.

Figure 3-6. /DREQ0 Jumper Settings

# Analog Inputs

The BL1700, BL1720, and BL1730 provide 10 single-ended analog-todigital conversion channels with 12-bit resolution. Eight channels are conditioned and two are unconditioned. The eight conditioned inputs can measure bipolar or unipolar signals. User-installable resistors determine the signal conditioning for your application. Two inputs are connected directly to the A/D converter.

# **Operating Modes and Configuration**

User-selected gain and bias resistors determine voltage ranges for the conditioned input signals.

Standard BL1700, BL1720, and BL1730 controllers come with 2370  $\Omega$  gain resistors and 39.2 k $\Omega$  bias resistors. These resistors provide a gain of 0.25 for a unipolar input signal range of 0 V to 10 V.

The BL1700 comes with gain and bias resistors installed for an input range of 0 V to 10 V. Table 3-6 lists the gain and bias resistors for other selected input-voltage ranges. A step-by-step procedure follows to explain how to calculate the values for the gain and bias resistors for a particular input-voltage range.

| Input Voltage Range<br>(V) | Gain   | R <sub>gain</sub><br>(Ω) | R <sub>bias</sub><br>(Ω) |

|----------------------------|--------|--------------------------|--------------------------|

| -10.0 to +10.0             | 0.125  | 1180                     | 8060                     |

| -5.0 to +5.0               | 0.250  | 2370                     | 6650                     |

| -2.5 to +2.5               | 0.500  | 4750                     | 4990                     |

| -2.0 to +2.0               | 0.625  | 5900                     | 4530                     |

| -1.0 to +1.0               | 1.250  | 11,800                   | 2870                     |

| -0.5 to +0.5               | 2.500  | 23,700                   | 1690                     |

| -0.25 to +0.25             | 5.000  | 47,500                   | 931                      |

| -0.10 to +0.10             | 12.500 | 118,000                  | 392                      |

| 0 to + 10.0                | 0.250  | 2370                     | 39,200                   |

| 0 to +5.0                  | 0.500  | 4750                     | 20,000                   |

| 0 to +2.5                  | 1.000  | 9530                     | 10,000                   |

| 0 to +1.0                  | 2.500  | 23,200                   | 4020                     |

Table 3-6. Representative Analog Input Setups

#### 1. Set up the analog inputs.

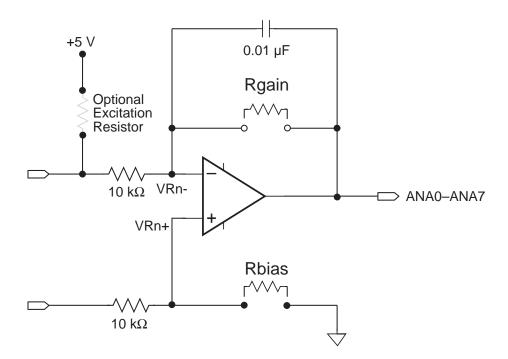

The first eight analog input signals are routed to the inverting input of one of the eight op-amps in U9 and U12. The op-amps in U9 and U12 operate in an inverting configuration. User-selectable resistors set the gain and bias voltages of the amplifiers. The 10 k $\Omega$  input resistors are fixed. Feedback capacitors roll off the high-frequency response of the amplifiers to attenuate noise. Figure 3-7 shows a schematic diagram of the conditioned input amplifier circuit.

Figure 3-7. Analog Conditioning Circuit

Table 3-7 lists the gain and bias resistors for each of the eight conditioned analog input channels.

| Channel | R <sub>bias</sub> | R <sub>gain</sub> |

|---------|-------------------|-------------------|

| ANA0    | R20               | R21               |

| ANA1    | R19               | R34               |

| ANA2    | R6                | R22               |

| ANA3    | R18               | R35               |

| ANA4    | R51               | R36               |

| ANA5    | R52               | R49               |

| ANA6    | R53               | R37               |

| ANA7    | R50               | R38               |

Table 3-7. Gain and Bias Resistors

Strip sockets spaced 0.400 inches (10.2 mm) apart accommodate the gain and bias resistors.

Z-World can install surface-mounted excitation, gain and bias resistors for your exact configuration in production quantities. For more information, call your Z-World Sales Representative at (530) 757-3737.

#### 2. Select gain resistor.

The gain and bias resistors determine the input signal's voltage relative to ground as well as its range. For example, assume your circuit must handle an input signal voltage range of 10 V spanning -5 V to +5 V. You should first select the gain (feedback) resistor to suit an input signal voltage range of 10 V.

The gain of the amplifier is the ratio of its maximum output-voltage swing to your application's maximum input-voltage swing. The 2.5 V input-voltage range of the A/D chip limits the op-amp's output swing to 2.5 V. Therefore, Equation (3-1) expresses an amplifier's gain in terms of its input-voltage range.

$$g = \frac{2.5 \text{ V}}{\text{V}_{\text{IN}_{\text{max}}} - \text{V}_{\text{IN}_{\text{min}}}}$$

(3-1)

where g is the gain,  $V_{\rm IN_{max}}$  is the maximum input voltage and  $V_{\rm IN_{min}}$  is the minimum input voltage.

The ratio of the user-specified gain resistor  $R_{gain}$  to its associated fixed input resistor determines an amplifier's gain. For the amplifier in Figure 3-7 with its input resistor fixed at 10 k $\Omega$ , the gain is

$$g = \frac{R_{gain}}{10,000 \,\Omega}$$

(3-2)

Given an input voltage range of 10 V, this gain equation fixes the amplifier's gain at 0.25. This gain scales the input signal's range properly down to the op-amp's 2.5 V maximum output range.  $R_{gain}$  must therefore be 2500  $\Omega$ .

#### 3. Determine bias resistor.

If the op-amp is to servo its output properly around the desired center voltage, you must establish the appropriate bias voltage at the op-amp's noninverting input. You must select the bias, or offset, resistor,  $R_{bias}$ , to position the input-voltage range correctly with respect to ground. For this example, let us use -5 V to +5 V.

Because the value for  $R_{gain}$  has already been selected, the maximum input voltage,  $V_{INmax}$ , determines the maximum voltage seen at the amplifier's summing junction (inverting input)—circuit nodes VR0– through VR7–. Compute VR0– through VR7– using Equation (3-3).

$$VR0 = V_{IN_{max}} \times \left(\frac{g}{1+g}\right)$$

(3-3)

For each op-amp, the bias voltage,  $V_{bias}$ , must equal its corresponding VRn–. A voltage divider, comprising a bias resistor and a fixed 10 k $\Omega$  resistor, derive the bias voltage from VREF+. Note that VREF+ is not necessarily the same as REF+. REF+ is the positive reference voltage the A/D chip uses.

$$R_{bias} = \frac{V_{bias} \times 10,000 \,\Omega}{2.5 \,V - V_{bias}} \quad . \tag{3-4}$$

Continuing the example for an input-voltage range that necessitates a gain of 0.25, and for which  $V_{MAX}$  is +5 V,  $V_{bias}$  is then 1.0 V. Therefore,  $R_{bias}$  is 6667  $\Omega$  in absolute mode.

Now suppose that the input range is 0 V to +10 V instead of -5 V to +5 V. V<sub>max</sub> is now +10 V and V<sub>bias</sub> becomes 2.0 V. R<sub>bias</sub> is then 40 kΩ.

#### 4. Choose resistor values.

The calculated values, of course, will not always be available as standard resistor values. In these cases, use the nearest standard resistor value. For example, rather than 6667  $\Omega$ , use 6650  $\Omega$  if you are using 1% resistors, or use 6800  $\Omega$  if you are using 5% resistors.

#### 5. Bracket input range.

To be sure of accurately measuring signals at the extremes of an input range, you must be aware of the interaction between the 10 k $\Omega$  fixed resistors and the resistors you install. In the ideal case, if you were to measure a signal at the minimum input level, the A/D converter's input would be at the maximum expected value of 2.5 V.

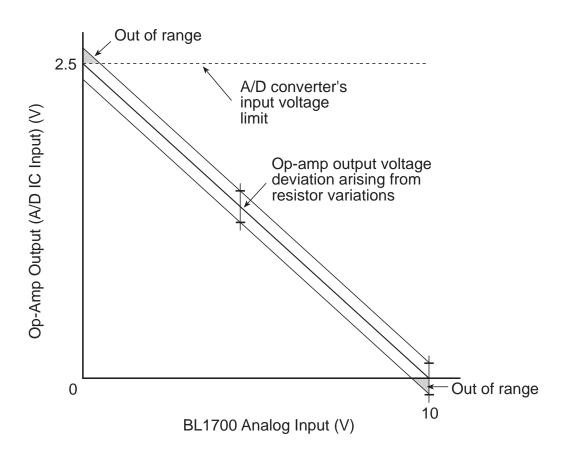

However, in the real world, resistor values vary within their rated tolerance bands. Thus, if the fixed input resistor is lower than its nominal value, and the installed resistor is slightly higher than its nominal value, the actual input to the A/D converter would be greater than 2.5 V. A loss of accuracy then results because the A/D converter input would reach its maximum input value before the true signal input reaches the minimum expected input level, as shown in Figure 3-8.

Figure 3-8. Input Out of Range

A deviation from nominal values in the bias network could skew the A/D converter's input voltage away from the theoretically computed value. For example, a small positive or negative deviation of the bias voltage arising from variances in the resistive divider would offset the A/D converter's input voltage. This offset would be positive or negative, tracking the deviation's sign, and would be equal to the bias deviation multiplied by the amplifier's gain plus one. Both of these effects could occur in the same circuit.

#### 6. Pick proper tolerance.

Use care when compensating for any discrepancies discovered. For example, if you use standard 5% resistors, the values are spaced approximately 10% apart. If your gain is too high by just a small amount, then going to the next smallest standard 5% value could result in a drop in gain, and an A/D converter excursion approaching 10%. The same caveat applies to the bias network. Using 1% resistors allows a more precise choice of values.

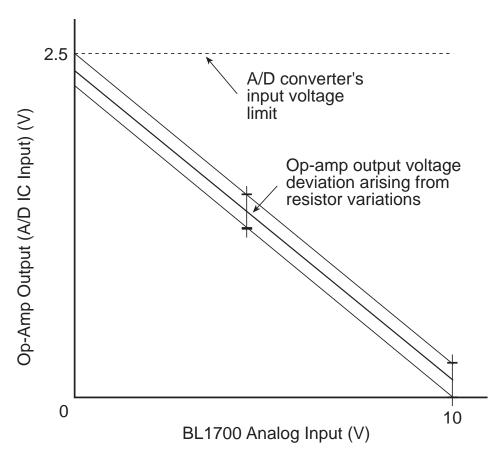

Figure 3-9 illustrates the result of adjusting the resistor values so that the input signal to the A/D converter stays within its specified 2.5 V range.

Figure 3-9. Proper Input Range

#### 7. Confirm performance.

If your measurements are critical, check setups after installing resistors by measuring test signals at and near the input-voltage limits. See if the voltages fall within the A/D converter's input range or if accuracy is lost due to over-excursions at the A/D converter's input. Another method is to measure the resistance of the factory-installed fixed resistors before selecting your own resistors.

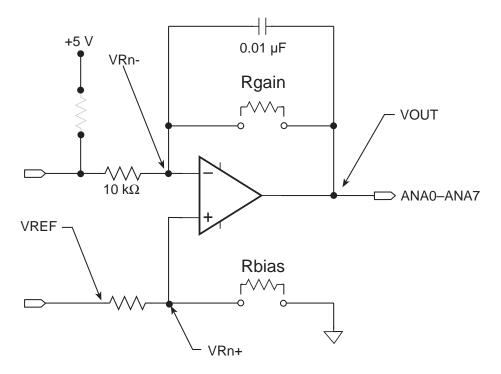

You can indirectly measure the fixed resistors after installation by measuring the voltages at the amplifiers' inputs and outputs. See Figure 3-10.

Figure 3-10. Signal Conditioning Test Points

Using Channel 0 as an example, ground the input A0 at pin 1 of H11. Then measure the voltages at VR0- and the amplifier's output. Because the currents through the input resistor and the feedback resistor are essentially identical, the ratio of the voltages across the resistors is equivalent to the ratio of the resistors. Therefore, the gain is

$$gain = \frac{VOUT - VR0 -}{VR0 -} \qquad (3-5)$$

Again using Channel 0 as an example, measure the voltage of VREF and the voltage at VR0+. Because the current into the op-amp input is negligible, the resistance ratio of the two resistors in the voltage divider alone determines VR0+. You can then compute the value of the fixed resistor in the divider once you know both the value of the resistor you installed and the value of VR0+.

#### 8. Calibrate the BL1700 A/D converter.

Mathematically derived values provide good baseline gain values. Calibration is necessary because the inherent component-to-component variations of resistors can completely swamp the 0.25% resolution of the A/D converter. To achieve the highest accuracy possible, calibrate the BL1700.

Dynamic C provides a routine to compute calibration coefficients and store the coefficients in nonvolatile memory. The routine uses two reference points to compute the coefficients. Each reference point comprises a pair of values: the actual applied test voltage and raw converted A/D value (a 12-bit integer). The supplied Z-World A/D software will automatically use these calibration coefficients to correct all subsequent A/D readings.

The factory installed fixed resistors have a 1% tolerance.

Calibration constants for the factory installed resistors are stored in simulated EEPROM during testing.

#### 9. Recalibrate the BL1700.

To recalibrate a BL1700, apply two known test voltages to each channel you plan to use. Get the converted reading for each test voltage and pass them, along with the test voltages, to the function **eioBrdACalib** to calculate the conversion coefficients for that channel. **eioBrdACalib** will automatically store the coefficients in the flash EPROM.

Sample program **BL17AIN**.**C** in the Dynamic C **SAMPLES** directory shows how to calibrate the conditioned analog input channels of a BL1700 manually, assuming test voltages of 1.00 V and 9.00 V.

### Drift

The AD680JT voltage reference displays a voltage drift of 10 ppm/°C (typ) to 30 ppm/°C (max). This drift corresponds to 25 mV/°C to 75 mV/°C, or 1.75 mV to 5.25 mV over the temperature range of 0°C to 70°C.

The LMC660C operational amplifier exhibits an offset-voltage drift of 1.3  $\mu$ V/°C (typ), or 91 mV over the operating temperature range.

### Low-Pass Filter

The 0.01 mF feedback capacitors in the amplifier's feedback path transform the amplifiers into low-pass filters. These filters attenuate any highfrequency noise that may be present in your signal. These filters' characteristics depend on the resistors your select.

The 3 dB corner frequency of a filter is

$$f_{3\,db} = \frac{1}{2\pi \times R_{g} \times 0.01\,\mu F} \quad . \tag{3-6}$$

For the case above with a gain of 0.25 using a 1% feedback resistor of 2490  $\Omega$ , the 3 dB corner frequency is 6392 Hz.

### **Excitation Resistors**

Some transducers require an excitation voltage. For example, a thermistor, serving as one leg of a voltage divider (having a fixed resistor in the other leg), measures temperature. The voltage at the divider's junction will vary with temperature. There is provision for excitation resistors to be installed on the inputs of the eight conditioned analog channels. The excitation resistors are tied to the +5 V analog supply.

# Using the Unconditioned Converter Channels

The eight conditioned channels use the first eight channels, AIN0–AIN7, of the A/D converter chip. Two additional channels are also available. You can access these channels with software by inserting your desired channel number in the library functions that control the BL1700. These signals are available on headers H8 and H11.

For optimum results, drive these channels with low output impedance voltage sources–less than 50  $\Omega$ . Op-amps are ideal for this purpose. High output impedance sources, on the other hand, are susceptible to coupled noise. In addition, only a low-impedance source can quickly charge the sampling capacitors within the A/D converter. When designing the signal sources to drive the extra channels, be sure to consider whether the amplifiers you choose can handle the capacitance of the cable that connects to the analog input connectors.

# Internal Test Voltages

In addition to the external input channels of the A/D converter chip, three additional internal channels exist to measure reference points within the A/D converter chip. Unfortunately, the A/D converter compares its internal nodes to REF+ and REF- so the conversions yield either all 1s or all 0s. You may access these channels using ordinary library routines by specifying the appropriate channel address when calling the functions.

| Channel    | Internal Voltage Read      |

|------------|----------------------------|

| Channel 11 | $(VREF + - VREF -) \div 2$ |

| Channel 12 | VREF-                      |

| Channel 13 | VREF+                      |

Table 3-8. Internal Test Voltages

# Power-Down Mode

If you select Channel 14, the A/D converter chip enters a power-down mode in which all circuitry within the chip goes into a low-current, standby mode. Upon power-up and before the first conversion, the chip also goes into the power-down mode. The chip remains in the power-down mode until you select a channel other than 14. The normal operating current of the A/D converter chip is 1 mA to 2.5 mA. In power-down mode this consumption is reduced to 4  $\mu$ A to 25  $\mu$ A.

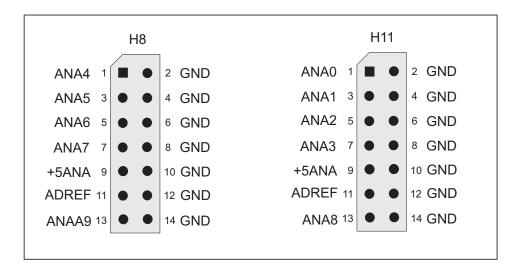

# **External Connections**

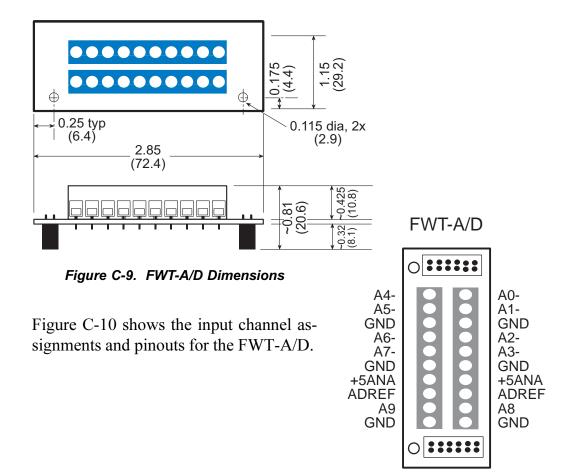

Connections to the analog inputs can be made with a ribbon cable, Z-World's FWT field wiring terminals, or a custom interface board. Z-World offers FWT modules for the digital inputs in three configurations.

- Screw terminals (Z-World part number 101-0184).

- Removable screw terminals (Z-World part number 101-0185)

The FWT module mates with the BL1700's header pairs H8–H11.

Connections to the analog inputs are made on headers H8 and H11. The pinouts for headers H8 and H11 are shown in Figure 3-11.

See Appendix C, "Field Wiring Terminals and DIN Rails," for FWT mechanical dimensions and pinouts.

Figure 3-11. Pinouts for BL1700 Analog Input Headers H8 and H11

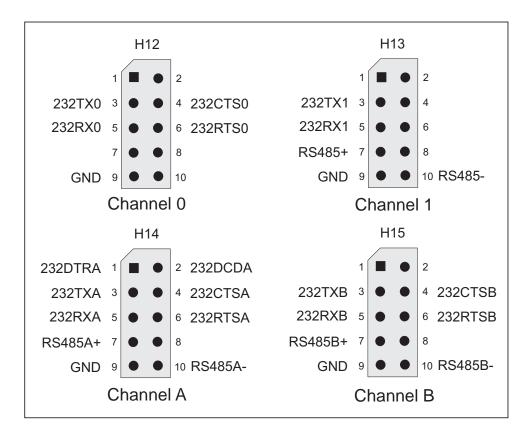

# **Serial Channels**

Four serial channels are available on the BL1700. One channel, Channel 0, is a dedicated RS-232 communication channel. The other three are available in either RS-232 or RS-485 configurations. Channel 0 and Channel 1 are connected to the Z180's Serial Channel 0 and Serial Channel 1, respectively. Channel A and Channel B are controlled by the Serial Communications Controller (SCC) chip on the BL1700; these two ports also have hardware support for synchronous communication. Serial channel signals are routed to either RS-232 or RS-485 converters via configuration jumpers. Baud rates up to 57,600 bps are supported.

The BL1720 and BL1730 versions have two serial ports. The serial ports on the BL1720–BL1730 versions do not support synchronous communication.

Table 3-9 summarizes the operating modes for the four channels.

| Channel   | Configurations                                        |  |  |

|-----------|-------------------------------------------------------|--|--|

| Channel 0 | Three-wire or five-wire RS-232 only                   |  |  |

| Channel 1 | Two-wire RS-485 or three-wire RS-232                  |  |  |

| Channel A | Two-wire RS-485 or five-wire RS-232, plus DCD and DTR |  |  |

| Channel B | Two-wire RS-485 or five-wire RS-232                   |  |  |

Table 3-9. Serial Channel Configuration Options

### Channel 0

Channel 0 is the BL1700's RS-232 programming port and is configured as three-wire or five-wire RS-232. Channel 0 cannot be reconfigured.

# Channel 1

Channel 1 is a general-purpose serial channel that can be configured as two-wire RS-485 or three-wire RS-232.

# Channel A

Channel A is a general-purpose serial channel controlled by a Zilog Serial Communication Controller (SCC) chip on the BL1700. Channel A can be configured as two-wire RS-485 or five-wire RS-232. When configured as RS-232, Channel A also provides DCD and DTR signals. Synchronous communication is possible on this channel, but is not supported by Dynamic C drivers at this time. Channel A is not available on the BL1720 or BL1730.

# Channel B

Channel B is a general-purpose serial channel. Along with Channel A, it is controlled by the Serial Communication Controller chip. Channel B can be configured as two-wire RS-485 or five-wire RS-232. Synchronous communication is possible on this channel, but is not supported by Dynamic C drivers at this time. Channel B is not available on the BL1720 or BL1730.

# **Operating Modes and Configuration**

Table 3-10 and Table 3-11 show the operating modes and jumper configurations for the serial channels on the BL1700.

| Channel   | Jumper Settings       |                      |  |  |  |

|-----------|-----------------------|----------------------|--|--|--|

| Channel   | RS-232 Communication  | RS-485 Communication |  |  |  |

| Channel 0 | No jumpe              | er settings          |  |  |  |

|           | J8                    | J8                   |  |  |  |

|           | 1 🔳 🔴 2               | 1 🔳 🕚 2              |  |  |  |

|           | 3 • • 4               | 3 • • 4              |  |  |  |

| Channel 1 | 5 • • 6               | 5 • • 6              |  |  |  |

|           | 7                     | 7 • 8                |  |  |  |

|           | 9                     | 9 10                 |  |  |  |

|           | 11 • • 12             | 11 💾 • 12            |  |  |  |

|           | 3-wire RS-232         | 2-wire RS-485        |  |  |  |

|           | J2                    | J2                   |  |  |  |

|           | 1 🔳 🕘 2               | 1 2                  |  |  |  |

|           | 3 • • 4               | 3 • • 4              |  |  |  |

|           | 5 • • 6               | 5 • • 6              |  |  |  |

| Channel A | 7 • 🖪 8 🕞             | 7 • • 8              |  |  |  |

|           | 9 • 10                | 9 • 10               |  |  |  |

|           | 11 • • 12             | 11 🔍 💾 12            |  |  |  |

|           | 5-wire RS-232<br>+DCD | 2-wire RS-485        |  |  |  |

|           | +DTR                  |                      |  |  |  |

|           | J8                    | J8                   |  |  |  |

|           | 1 🚺 🗕 2               | 1 🔳 🕚 2              |  |  |  |

|           | 3 🚺 🗕 4               | 3 • 4                |  |  |  |

| Channel B | 5 • • 6               | 5 🚺 • 6              |  |  |  |

|           |                       | 7 • • 8              |  |  |  |

|           | 9 • • 10              | 9 • • 10             |  |  |  |

|           | 11 • • 12             | 11 • • 12            |  |  |  |

|           | 5-wire RS-232         | 2-wire RS-485        |  |  |  |

Table 3-10. Serial Channel Configuration Jumper Settings

| Channel                       | Jumper                                                                                                                                       | ettings                                                                                                                                   |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Channel                       | SCC Option                                                                                                                                   | User Application Option                                                                                                                   |  |  |

| Channel A                     | J8<br>1<br>3<br>5<br>7<br>9<br>11<br>2<br>4<br>6<br>8<br>10<br>12<br>/DREQ0 used for SCC<br>Channel A                                        | J8<br>1<br>3<br>4<br>5<br>7<br>9<br>11<br>2<br>4<br>6<br>8<br>9<br>10<br>12<br>/DREQ0 available for<br>user application                   |  |  |

| Channel B                     | J8<br>1<br>3<br>5<br>7<br>9<br>11<br>2<br>4<br>6<br>8<br>10<br>12<br>/DREQ1 used for SCC<br>Channel B                                        | J8<br>1<br>3<br>5<br>7<br>9<br>11<br>$\bullet$<br>$\bullet$<br>$\bullet$<br>$\bullet$<br>$\bullet$<br>$\bullet$<br>$\bullet$<br>$\bullet$ |  |  |

| Channel A<br>and<br>Channel B | J4<br>1 2<br>3 4<br>5 7<br>6 8<br>7 1 8<br>7 1 8<br>7 1 1 1<br>6 8<br>7 1 1 1<br>6 8<br>7 1 1 1 1<br>7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | J4<br>1 $\bullet$ 2<br>3 $\bullet$ 4<br>5 $\bullet$ 6<br>7 $\bullet$ 8<br>/INTO available for user<br>application                         |  |  |

# Table 3-11. Serial Channel Configuration Jumper Settings

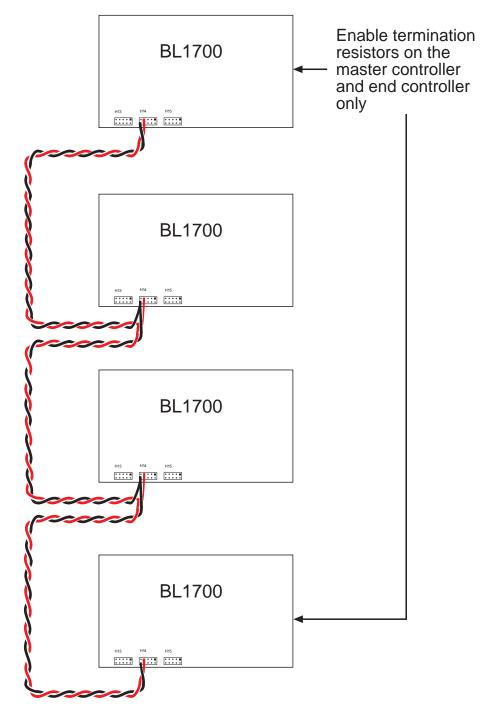

# Configuring a Multidrop Network

- Configure the serial channels that you wish to use for RS-485 communication.

- On all networked controllers, connect RS-485+ to RS-485+ and ٠ RS-485- to RS-485- using single twisted pair wires (nonstranded, tinned).

Refer to the Dynamic C manuals for more details on masterslave networking.

### **RS-485** Termination

Termination and bias resistors are required in a multidrop network to minimize reflections (echoing), and to keep the network line active in an idle state. Typically, termination resistors are installed at the master node and the physical end node of an RS-485 network. Termination resistors are provided for Channel 1, Channel A, and Channel B configured as RS-485.

If you wish to configure a multidrop network, be sure to enable the 120  $\Omega$ termination resistors on both the master network controller and the "end" slave controller.

Figure 3-12 illustrates a multidrop network, and Table 3-12 provides the jumper settings to enable/disable the termination resistors.

# **External Connections**

Each serial channel has its own individual header for external connections. Both RS-232 and RS-485 signal lines for Channel 1, Channel A, and Channel B are brought out to a serial channel's 10-pin header. Only one set of signals, RS-232 or RS-485, is active.

The three-wire RS-232 interface provides the following signals.

- RX

- TX

- GND

The five-wire RS-232 interface provides the following signals.

- RX

- TX

- RTS

- CTS

- GND

The two-wire RS-485 interface provides the following signals.

- RS-485+

- RS-485-

**BL1700**

The RS-485 drivers supplied with the BL1700 support up to 32 nodes. The transmission bandwidth may be reduced as additional nodes over the benchmark quantity of 32 are added to the network. Contact Z-World Technical Support for assistance with large-scale network design.

|           | Jumper Settings                                                                                                                                                                       |                                                       |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| Channel   | Termination Resistors<br>Enabled                                                                                                                                                      | Termination Resistors<br>Disabled                     |  |  |  |

| Channel 0 | No RS-485                                                                                                                                                                             | available                                             |  |  |  |

| Channel 1 | $ \begin{array}{c}       J4 \\       1 \\       3 \\       5 \\       7 \\   \end{array} $ $ \begin{array}{c}       J4 \\       2 \\       4 \\       6 \\       8 \\   \end{array} $ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |  |  |

| Channel A | $ \begin{array}{c} J7\\ 1\\ 3\\ 5\\ 7\\ \bullet \bullet \\ 8\\ \end{array} $                                                                                                          | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |  |  |

| Channel B | $ \begin{array}{c}     J7 \\ 1 \\ 3 \\ 5 \\ 7 \end{array} $ $ \begin{array}{c}     2 \\ 4 \\ 6 \\ 8 \end{array} $                                                                     | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |  |  |

### Table 3-12. Termination Resistor Jumper Settings

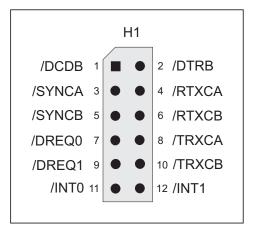

Connections to the serial channels are made via the 10-pin headers shown in Figure 3-13. The headers are standard vertical 0.025" square (0.635 mm square) posts on 0.100" (2.54 mm) centers.

Figure 3-13. Pinouts of BL1700 Serial Communication Headers H12 through H15

# **PLCBus**

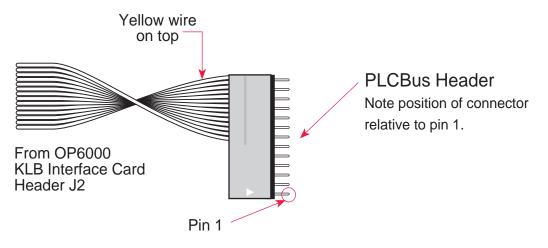

The PLCBus provides easy I/O expansion for the BL1700. PLCBus expansion boards provide additional I/O capacity, A/D converters, D/A converters, serial channels, relay outputs, stepper motor controllers, and more. Expansion boards are connected to the BL1700 via a 26-conductor ribbon cable. Several PLCBus expansion boards may be daisy-chained to increase the I/O capacity further. Dynamic C provides easy to use software for all Z-World expansion boards.

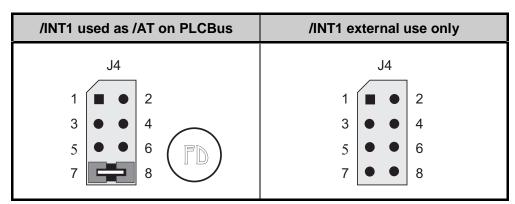

# **Operating Modes and Configuration**

Some PLCBus expansion boards use the /AT line on the PLCBus. Jumpers on header J4 on the BL1700 determine whether the /INT1 signal is connected to the PLCBus /AT line, as shown in Table 3-13. If you intend to use a PLCBus expansion board that uses the /AT signal, make sure that a jumper is installed in the JP4:7-8 position. If you want to use the /INT1 signal for another external signal, and it is not needed for the PLCBus, then remove the jumper from the J4:7-8 position.

Table 3-13. BL1700 PLCBus Jumper Settings

# **External Connections**

J5 is the PLCBus connector on the BL1700. PLCBus devices are connected with ribbon cables on 26-pin connectors.

Refer to Appendix E, "PLCBus," for more detailed information on the PLCBus and Z-World's expansion boards.

# CHAPTER 4: SOFTWARE DEVELOPMENT

Chapter 4 describes how to use the features of the BL1700 Series controller. The following major sections are included.

- Supplied Software

- Digital Inputs

- Digital Outputs

- PWM Outputs

- Analog Inputs

- Serial Channels

- LED

- Additional Software

# **Supplied Software**

Software drivers for controlling the BL1700's inputs/outputs are provided with Dynamic C. The library **EZIOBL17.LIB** provides drivers specific to the BL1700. In order to use **EZIOBL17.LIB** and other libraries, it is necessary to include the appropriate Dynamic C libraries. These libraries are listed in Table 4-1.

| Library      | Application                                  |

|--------------|----------------------------------------------|

| AASC.LIB     | All BL1700 serial communication applications |

| AASCURT2.LIB | XP8700 applications only                     |

| EZIOBL17.LIB | All BL1700 applications                      |

| EZIOPBDV.LIB | All expansion board applications             |

| EZIOPLC2.LIB | All expansion board applications             |

| STEP2.LIB    | XP8800 applications only                     |

Table 4-1. BL1700 Software Libraries

Your application program can use these libraries by including them in your program. To include these libraries, use the **#use** directive as shown below.

```

#use eziobl17.lib

```

See the *Dynamic C Technical Reference* manual for more information on **#use** and other directives as well as other libraries.

# **Digital Inputs**

The BL1700 is equipped with protected digital inputs designed as logical data inputs that return a 1 when the input is high or 0 when the input is low.

A low-pass filter on each input channel has a time constant of:

$T_{\rm RC} = 220 \ \mu s \ (4.5 \ \rm kHz).$

If the signals present on the digital inputs change states faster than this, the readings on the inputs may not be accurate.

# How to Read the Input

This section provides information on using the Dynamic C software drivers for the BL1700's protected digital inputs.

The following software drivers read the status of the protected digital inputs.

- unsigned BankA( unsigned eioAddr )

- unsigned BankB( unsigned eioAddr )

**BankA** converts **eioAddr** to a value of 16–31 for addressing the correct input or output assignments. **BankB** converts **eioAddr** to a value of 0–15.

PARAMETER: **eioAddr** specifies channel number from 0–15.

RETURN VALUE: the formatted I/O assignment, or -1 if the parameter **eioAddr** is out of range.

#### int eioBrdDI( unsigned eioAddr )

Reads the state from one of the 32 physical digital inputs. Sets **eioErrorCode** if **eioAddr** is out of range.

PARAMETER: **eioAddr** specifies the input to be read. Valid numbers are from 0 to 31. 0–15 represents Bank B. 16–31 represents Bank A.

RETURN VALUE: 0 if input reads low, 1 if input reads high.

### unsigned inport( unsigned port )

Reads a value from an I/O port.

PARAMETER 1: **port** is the BL1700 port address to read. When used to read the digital inputs, **port** is one of four groups of eight inputs. There are two groups of eight inputs for each bank.

RETURN VALUE: The value read from the port.

Table 4-2 lists the addresses and corresponding headers of the digital input ports on the BL1700.

| Bank                 | Bar         | ık B        | Bar         | nk A        |

|----------------------|-------------|-------------|-------------|-------------|

| Header               | H10         | H10 H7      |             | Н9          |

| Channels             | HVB00–HVB07 | HVB08–HVB15 | HVA08–HVA15 | HVA00–HVA07 |

| Physical<br>Channels | 0–7         | 8–15        | 24–31       | 16–23       |

| Address              | 0x4040      | 0x4041      | 0x4042      | 0x4043      |

Table 4-2. Digital Input Addresses

The factory default is for Bank A to be configured for digital inputs.

The lower eight bits of the value read back by the inport function represent the status of the inputs. Bit 0 represents inputs 0, 8, 16, or 24, depending on which address is read. Bit 1 represents inputs 1, 9, 17, or 25, and so forth.

# Sample Program

The sample program **BL17DIO**.**C** shows how to use the digital I/O. It can be found in the Dynamic C **SAMPLES**\**BL17XX** subdirectory.

# **Digital Outputs**

The BL1700 provides up to 32 high-voltage, high-current driver outputs. Some outputs can also function as pulse width modulated (PWM) outputs. This section provides information on the Dynamic C software drivers for the BL1700's high-voltage driver outputs.

The following software function turns a specified high-voltage driver ON or OFF.

- unsigned BankA( unsigned eioAddr )

- unsigned BankB( unsigned eioAddr )

**BankA** converts **eioAddr** to a value of 16–31 for addressing the correct input or output assignments. **BankB** converts **eioAddr** to a value of 0–15.

PARAMETER: **eioAddr** specifies channel number from 0–15.