# **Errata Sheet for Cyclone IV Devices**

ES-01027-2.0 Errata Sheet

This errata sheet provides updated information on known device issues affecting Cyclone® IV devices.

Table 1 lists specific Cyclone IV issues and which Cyclone IV devices are affected by each issue.

Table 1. Known Issues for Cyclone IV Devices (Part 1 of 2)

| Issue                                                                                                                                                                                                                                                                         | Affected Devices                                                                                                                                                  | Planned Fix                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| "Human Body Model Electrostatic Discharge"  The row I/Os on certain Cyclone IV GX devices do not meet the human body model (HBM) electrostatic discharge (ESD) specification stated in the device datasheet.                                                                  | EP4CGX15 and EP4CGX30<br>(except for the F484 package)<br>Devices                                                                                                 | No plan to fix silicon.    |

| "DisplayPort Receiver Specification"  The Cyclone IV GX transceiver is compliant with the DisplayPort transmitter specifications only for 1.62 Gbps and 2.7 Gbps data rates. The transceiver is not compliant with the DisplayPort receiver jitter tolerance specification.   | All Cyclone IV GX Devices                                                                                                                                         | No plan to fix silicon.    |

| "Asynchronous Spread Spectrum Clock Modulation<br>Tracking"  The transceiver channels do not support tracking of the<br>incoming data with asynchronous spread spectrum clock<br>(SSC) modulation.                                                                            | EP4CGX30 (F484 package),<br>EP4CGX50, and EP4CGX75<br>Devices only.<br>Support of asynchronous SSC<br>tracking capability was never<br>planned for other Devices. | No plan to fix silicon.    |

| "SATA CDR PPM Tolerance"  To support the serial ATA (SATA) protocol in  Cyclone IV GX devices, you must constrain the clock data recovery (CDR) parts-per-million (PPM) tolerance to a specified range.                                                                       | EP4CGX30 (F484 package),<br>EP4CGX50, and EP4CGX75<br>Devices                                                                                                     | No plan to fix silicon.    |

| "Remote System Upgrade"  The remote system upgrade (RSU) feature fails when loading an invalid configuration image.                                                                                                                                                           | All Cyclone IV GX Devices                                                                                                                                         | Future Quartus II Software |

| "Pin Connection Guidelines Update for Transceiver Applications that Run at ≥ 2.97 Gbps Data Rate"  The affected Cyclone IV GX devices may not able to meet the protocol jitter specification or may have a higher bit error rate (BER) if you do not follow these guidelines. | EP4CGX30 (F484 package),<br>EP4CGX50, EP4CGX75,<br>EP4CGX110, and EP4CGX150<br>Devices                                                                            | No plan to fix silicon.    |

101 Innovation Drive San Jose, CA 95134 www.altera.com © 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at work and the common / legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 1. Known Issues for Cyclone IV Devices (Part 2 of 2)

| Issue                                                                                                                           | Affected Devices                                   | Planned Fix                                               |  |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|--|

| "Quartus II Mapping Issue with a PCIe ×1 Interface Using the Hard IP Block"                                                     | All Cyclone IV GX Devices                          | Quartus II software                                       |  |

| The Quartus II software incorrectly maps the PCle interfaces when using the hard IP block.                                      | All Gydlotte IV dix Devices                        | version 10.1                                              |  |

| "PLL Cascading for Transceiver Applications is not Supported"                                                                   |                                                    | Quartus II software                                       |  |

| Only the direct REFCLK or DIFFCLK pins driving the phase-locked loop (PLL) input of a transceiver are allowed.                  | All Cyclone IV GX Devices                          | version 10.1 and later.                                   |  |

| "Removal of the ±500 PPM and ±1000 PPM Options for<br>the Programmable PPM Detector in the ALTGX<br>MegaWizard Plug-In Manager" | All Cyclone IV GX Devices                          | No plan to fix silicon.                                   |  |

| The ±500 PPM and ±1000 PPM options in the ALTGX MegaWizard Plug-In Manager are not supported.                                   |                                                    |                                                           |  |

| "External Memory Specification for DDR2 SDRAM"                                                                                  | All Cyclone IV E Core Voltage                      | For the solution, refer to                                |  |

| Final full-rate DDR2 SDRAM maximum clock rate specification on column and row I/Os.                                             | All Cyclone IV E Core Voltage<br>1.0-V I8L Devices | "External Memory Specification for DDR2 SDRAM" on page 9. |  |

### **Human Body Model Electrostatic Discharge**

The row I/Os on certain Cyclone IV GX devices do not meet the human body model (HBM) electrostatic discharge (ESD) specification stated in the device datasheet. All other I/Os, including the high-speed serial interface (HSSI) I/Os, meet the HBM ESD specification.

This issue only affects the EP4CGX15 and EP4CGX30 (except for the F484 package) devices and there will not be a silicon fix.

The EP4CGX15 and EP4CGX30 (except for the F484 package) devices are considered HBM Class 0 per JEDEC standard 22-A114. Altera recommends handling the ESD-sensitive devices using the ESD control methods as stated in ANSI/ESD S20.20 or IEC61340-5-1.

If you have additional questions, contact your local Altera® sales representative.

### **DisplayPort Receiver Specification**

The Cyclone IV GX transceiver meets the transmitter compliance specifications as a 1.62 Gbps and 2.7 Gbps transmitter for a digital display interface unit.

However, the Cyclone IV GX transceiver does not meet the receiver jitter tolerance specification that requires tracking of at least one unit interval (UI) at 2 MHz jitter tolerance test without asynchronous spread spectrum clocking (SSC) modulation enabled. If you want to use the transceiver as a DisplayPort receiver, you must verify the system margin and its jitter components in the application design.

## **Asynchronous Spread Spectrum Clock Modulation Tracking**

The receiver clock data recover (CDR) is not able to track the incoming data with asynchronous SSC modulation for the serial ATA (SATA), DisplayPort, and V-by-one HS protocols.

The receiver CDR is able to track the incoming data with synchronous SSC modulation for the PCI Express<sup>®</sup> (PCIe<sup>®</sup>) Gen1 protocol.

If you are considering a custom protocol design that requires SSC modulation in a Basic mode configuration, Altera recommends designing with synchronous SSC modulation.

### **SATA CDR PPM Tolerance**

You must constrain the CDR PPM tolerances for both SATA Gen1 and Gen2 data rates based on Table 2 without asynchronous SSC modulation for incoming data.

Table 2. CDR PPM Device Tolerances (Asynchronous SSC Not Enabled)

|                                                       | Device   |          |                                     |                               |          |          |           |           |      |

|-------------------------------------------------------|----------|----------|-------------------------------------|-------------------------------|----------|----------|-----------|-----------|------|

|                                                       | EP4CGX15 | EP4CGX22 | EP4CGX30<br>(F169/F324<br>packages) | EP4CGX30<br>(F484<br>package) | EP4CGX50 | EP4CGX75 | EP4CGX110 | EP4CGX150 | Unit |

| CDR PPM<br>tolerance<br>(Async SSC<br>not<br>enabled) | ±350 (1) | ±350 (1) | ±350 (1)                            | ±200                          | ±200     | ±200     | ±350 (1)  | ±350 (1)  | PPM  |

#### Note to Table 2:

### **Remote System Upgrade**

The remote system upgrade (RSU) feature does not operate correctly when you initiate a reconfiguration cycle that goes from a factory configuration image to an invalid application configuration image. In this scenario, the Cyclone IV GX device fails to revert back to the factory configuration image after a configuration error is detected while loading the invalid application configuration image. The failure is indicated by a continuous toggling of the nstatus pin, or the CONF\_DONE pin stays low after configuration.

In a correct operation, the Cyclone IV GX device would revert back to the factory configuration image after a configuration error is detected with the invalid configuration image.

An invalid application configuration image is classified as one of the following:

- A partially programmed application image

- An application image assigned with a wrong start address

The RSU feature works correctly with all other reconfiguration trigger conditions.

<sup>(1)</sup> To support CDR PPM tolerances greater than ±300 PPM, implement a PPM detector in your user logic and configure your device in CDR to Manual Lock mode.

### **Workaround**

A workaround is being implemented in the ALTREMOTE\_UPDATE megafunction and will be available in the future Quartus® II software release. If you have any questions, contact Altera Technical Support at www.altera.com/support.

# Pin Connection Guidelines Update for Transceiver Applications that Run at $\geq$ 2.97 Gbps Data Rate

You may not meet the protocol jitter specification or may have a higher bit error rate (BER) if you do not use the following guidelines.

If your transceiver applications run at  $\geq 2.97$  Gbps data rate, you must ground specific pins (refer to Table 3) next to the reference clock directly through the via under the device to the PCB ground plane on your board. You also must assign the specific pins to ground in the Quartus II software. To minimize the impact listed in Table 3, Altera recommends using REFCLK[1..0] and REFCLK[5..4] reference clocks before using REFCLK2 and REFCLK3 reference clocks.

There is no action required and no performance degradation for input reference clocks that are used to drive transceiver channels at < 2.97 Gbps data rates.

Table 3 lists the reference clock pins and the associated I/O pins to be grounded for transceiver applications that run at  $\geq$  2.97 Gbps data rate.

Table 3. Reference Clock Pins and the Associated I/O Pins to be Grounded for  $\geq$  2.97 Gbps Transceiver Applications (Part 1 of 3)

| Package | Reference<br>Clock | Bank          | Reference<br>Clock Pins | I/O Pins to Ground                                                            | Impact                                                                                                                                                                               |

|---------|--------------------|---------------|-------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | REFCLK[10]         | 3B <i>(1)</i> | M7<br>M8<br>N7<br>N8    | AA4 (CRC_ERROR) (5)<br>W8 (INIT_DONE) (5)<br>AB3 (NCEO) (5)<br>T7<br>T8<br>V6 | MPLL_5 and/or GPLL_1 ZDB mode is not supported. (7)                                                                                                                                  |

| F23     | REFCLK2            | 3A <i>(2)</i> | M11<br>N11              | AB10<br>AB11<br>R13<br>T13<br>W12<br>W13                                      | If you use a DDR system, the following DQ groups will not be supported (8):  DQ4B in × 8 groups  DQ5B in × 8/× 9 groups  DQ3B and DQ5B in × 16/× 18 groups  DQ5B in × 32/× 36 groups |

Table 3. Reference Clock Pins and the Associated I/O Pins to be Grounded for  $\geq$  2.97 Gbps Transceiver Applications (Part 2 of 3)

| Package | Reference<br>Clock | Bank               | Reference<br>Clock Pins                | I/O Pins to Ground                                                                                                                                           | Impact                                                                                                                                                                               |

|---------|--------------------|--------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | REFCLK[10]         | 3B (1)             | T9<br>T10<br>U9<br>U10                 | AC6 (CRC_ERROR) (5) AB7 (INIT_DONE) (5) AC7 (nCEO) (5) AC5 AD4 AB5                                                                                           | MPLL_5 and/or GPLL_1<br>ZDB mode is not<br>supported. (7)                                                                                                                            |

|         | REFCLK[54]         | 8B (1)             | K9<br>K10<br>L9<br>L10                 | E6 (DATA1/ASDO) (5) D5 (nCSO) (5) E2 D4 (CLKUSR) (5), (6) E1 D6 (DATAO) (5)                                                                                  | MPLL_8 ZDB mode is not supported. (7)                                                                                                                                                |

| F27     | REFCLK2            | 3A <i>(2), (4)</i> | T14<br>T15                             | AC14<br>AD14<br>AE14<br>AF10<br>AF11<br>AF12                                                                                                                 | If you use a DDR system, the following DQ groups will not be supported (7):  DQ4B in × 8 groups  DQ5B in × 8/× 9 groups  DQ3B and DQ5B in × 16/× 18 groups  DQ5B in × 32/× 36 groups |

| REFCLK3 | 8A <i>(3), (4)</i> | L14<br>L15         | A12<br>A13<br>B13<br>C13<br>C14<br>C15 | If you use a DDR system, the following DQ groups will not be supported (7):  DQ5T in × 8 groups  DQ3T and DQ5T in × 16/× 18 groups  DQ5T in × 32/× 36 groups |                                                                                                                                                                                      |

Table 3. Reference Clock Pins and the Associated I/O Pins to be Grounded for  $\geq$  2.97 Gbps Transceiver Applications (Part 3 of 3)

| Package | Reference<br>Clock | Bank        | Reference<br>Clock Pins  | I/O Pins to Ground                                                          | Impact                                                                                                                                                                      |

|---------|--------------------|-------------|--------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | REFCLK[10]         | 3B (1)      | V11<br>V12<br>W11<br>W12 | AD6 (CRC_ERROR) (5) AE8 (INIT_DONE) (5) AE7 (nCEO) (5) AE6 AF6 AG6          | MPLL_5 and/or GPLL_1<br>ZDB mode is not<br>supported. (7)                                                                                                                   |

|         | REFCLK[54]         | 8B (1)      | K11<br>L10<br>L11<br>M10 | G9 (DATA1/ASDO) (5) B4 (nCSO) (5) A4 (CLKUSR) (5), (6) A3 (DATA0) (5) F8 G8 | MPLL_8 ZDB mode is not supported. (7)                                                                                                                                       |

| F31     | REFCLK2            | 3A (2), (4) | V15<br>W15               | AA17<br>AF16<br>AG16<br>AH16<br>AJ13<br>AK14                                | If you use a DDR system, the following DQ groups will not be supported (8):  DQ4B in × 8 groups  DQ5B in × 8/× 9 groups  DQ4B in × 16/× 18 groups  DQ2B in × 32/× 36 groups |

|         | REFCLK3            | 8A (3), (4) | K15<br>L15               | A16<br>B16<br>C16<br>F16<br>G15<br>K17                                      | If you use a DDR system, DQ5T in $\times 8/\times 9$ , $\times 16/\times 18$ , and $\times 32/\times 36$ groups will not be supported. (8)                                  |

#### Notes to Table 3:

- (1) The unused adjacent reference clock pins in the same bank can only be used as differential input clock.

- (2) The unused adjacent reference clock pins in Bank 4 (Package F23: AA12 and AB12 pins, package F27: AF13 and AF14 pins, and package F31: AJ16 and AK16 pins) can only be used as differential input clock.

- (3) The unused adjacent reference clock pins in Bank 7 (Package F27: A14 and B14 pins and package F31: A15 and B15 pins) can only be used as differential input clock.

- (4) You can only use REFCLK2 in Bank 3A for transceiver block GXBL0 and REFCLK3 in Bank 8A for transceiver block GXBL1.

- (5) Do not tie this pin to ground if it is used for configuration or a dedicated function in User mode. Dedicated functions include using the DATA1/ASDO, nCSO, and DATA0 pins for EPCS access and the crc\_error pin for a cyclic redundancy check (CRC) error function. Do not use this pin as a user I/O in User mode.

- (6) Do not toggle the CLKUSR pin in User mode. Reassign the CLKUSR pin to another I/O pin if it is being used in User mode.

- (7) You can alternatively use zero delay buffer (ZDB) mode with other phase-locked loops (PLLs).

- (8) You can alternatively use other DQ/DQS groups or wraparound DQ/DQS groups. For more information about wraparound DQ/DQS performance, refer to the External Memory Interface Spec Estimator page on Altera website.

Table 4 lists the Quartus II software support planning.

**Table 4. Quartus II Software Planned Support**

| Quartus II Software Version    | Software Enforcement Plan                                                                                           |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Releases prior to version 11.0 | Follow the guidelines documented in this errata sheet as the Quartus II software does not enforce these guidelines. |

| Version 11.0 release and later | The Quartus II software enforces the guidelines documented in this errata sheet.                                    |

The Cyclone IV Device Family Pin Connection Guidelines has been updated with the guidelines for transceiver applications that run at  $\geq$  2.97 Gbps data rate.

# Quartus II Mapping Issue with a PCIe $\times 1$ Interface Using the Hard IP Block

The Quartus II software version 10.0 SP1 and prior releases incorrectly allowed logical channel 0 to be placed in any physical channel for the PCIe Gen1  $\times$ 1 interface with the hard IP block. For correct operation with the hard IP block, logical channel 0 must be placed in physical channel 0.

This issue is fixed in the Quartus II software version 10.1. If you have already designed or fabricated your boards using the incorrect mapping, file a service request using mysupport for assistance to remedy this issue.

### **PLL Cascading for Transceiver Applications is not Supported**

Using the clock output of another PLL to drive the PLL input of a transceiver is not allowed. Only the direct REFCLK or DIFFCLK pins driving the PLL input of a transceiver is allowed.

Hence, PLL cascading for transceiver applications is restricted by the Quartus II software version 10.1 and later. If you use PLL cascading for transceiver applications, the Quartus II Analysis and Synthesis reports an error during compilation.

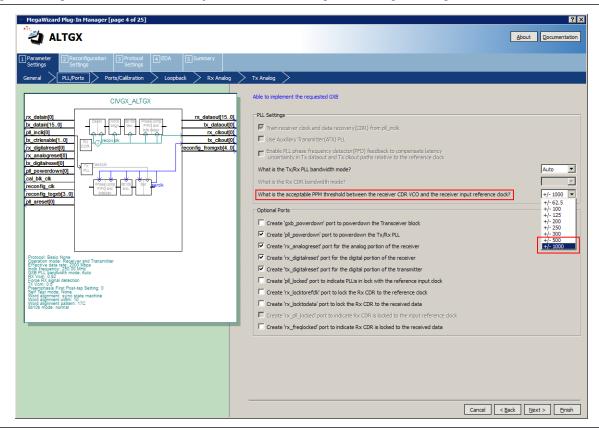

# Removal of the $\pm 500$ PPM and $\pm 1000$ PPM Options for the Programmable PPM Detector in the ALTGX MegaWizard Plug-In Manager

The ±500 PPM and ±1000 PPM options for the Programmable PPM Detector feature in the ALTGX MegaWizard™ Plug-In Manager, as shown in Figure 1, are no longer supported in the Quartus II software version 10.0 SP1 and later. These options are removed because the programmed PPM threshold values exceed the receiver CDR PPM tolerance between the upstream transmitter reference clock and the local receiver reference clock.

Figure 1 shows the Programmable PPM Detector options in ALTGX MegaWizard Plug-In Manager in the Quartus II software, version 10.0.

Figure 1. Programmable PPM Detector Options in the ALTGX MegaWizard Plug-In Manager

Designs compiled with the Quartus II software version 10.0 and earlier may have a link failure risk when the receiver is operating in a system that has ±500 PPM or ±1000 PPM differences for the reference clock frequencies between the upstream transmitter and the local receiver. Using CDR Manual Lock mode does not overcome the link failure risk.

For a receiver design that has the ±500 PPM or ±1000 PPM options selected in the Programmable PPM Detector feature, Altera recommends evaluating the system operation with different options, ranging between ±62.5 PPM and ±300 PPM. To change the **Programmable PPM Detector** option, regenerate and recompile the ALTGX MegaWizard Plug-In Manager design file with the supported options.

If you compiled your designs using a Quartus II software version prior to 10.0 SP1, and you have selected the  $\pm 500 \text{ PPM}$  or the  $\pm 1000 \text{ PPM}$  option for the Programmable PPM Detector feature, the Quartus II Analysis and Synthesis error will be reported in the Quartus II software version 10.0 SP1 and later.

### **External Memory Specification for DDR2 SDRAM**

In the Quartus II software version 10.0, the Cyclone IV E I8L speed grade supported full-rate DDR2 SDRAM with a maximum clock rate of up to 150 MHz on column and row I/Os. This maximum clock rate is a preliminary specification pending the finalization of the timing model.

In the Quartus II software version 10.0 SP1 and later, the Cyclone IV E I8L speed grade full-rate DDR2 SDRAM maximum clock rate specification on column and row I/Os has been revised due to the finalization of the timing model for the Cyclone IV E device family. Table 5 lists the current specification.

Table 5. Full-Rate DDR2 SDRAM Support for Cyclone IV E Core Voltage 1.0-V Devices

| Memory Standard | Device                                | Speed Grade | Maximum Clock Rate (MHz)  Column and Row I/O  Single Chip Select |

|-----------------|---------------------------------------|-------------|------------------------------------------------------------------|

| DDR2 SDRAM      | Cyclone IV E<br>Core Voltage<br>1.0 V | I8L         | 133 <i>(1)</i>                                                   |

### Note to Table 5:

(1) You must use the 267-MHz memory device speed grade to achieve the maximum clock rate.

Designs that already use the affected devices running full-rate DDR2 SDRAM at the old maximum clock rate and pass timing in the Quartus II software version 10.0 SP1 and later run acceptably at the old frequencies—provided that the board settings panel in the IP MegaWizard Plug-In Manager is populated accurately and the board trace models representative of the relevant system are correctly entered in the Pin Planner.

Page 10 Document Revision History

# **Document Revision History**

Table 6 lists the revision history for this Errata Sheet.

**Table 6. Document Revision History**

| Date          | Version | Changes                                                                                                         |  |  |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------|--|--|

|               |         | Added the following sections:                                                                                   |  |  |

|               |         | "Human Body Model Electrostatic Discharge"                                                                      |  |  |

|               |         | "DisplayPort Receiver Specification"                                                                            |  |  |

| March 2011    | 2.0     | "Asynchronous Spread Spectrum Clock Modulation Tracking"                                                        |  |  |

|               |         | ■ "SATA CDR PPM Tolerance"                                                                                      |  |  |

|               |         | "Remote System Upgrade"                                                                                         |  |  |

|               |         | Removed the old "Human Body Model Electrostatic Discharge" section.                                             |  |  |

|               |         | Added the following sections:                                                                                   |  |  |

|               |         | "Cyclone IV GX Pin Connection Guidelines Update for Transceiver Applications that Run at 3 2.97 Gbps Data Rate" |  |  |

| November 2010 | 1.1     | ■ "Quartus II Mapping Issue with PCIe ×1 Interface Using the Hard IP Block"                                     |  |  |

| November 2010 | 1.1     | "PLL Cascading for Transceiver Applications is not Supported"                                                   |  |  |

|               |         | "Removal of ±500 PPM and ±1000 PPM Options for Programmable PPM Detector in ALTGX MegaWizard Plug-In Manager"   |  |  |

|               |         | "External Memory Specification for DDR2 SDRAM"                                                                  |  |  |

| April 2010    | 1.0     | Initial release.                                                                                                |  |  |