Data Sheet July 2004 FN1850.4

## CMOS Video Speed, 8-Bit, 50 MSPS, R2R D/A Converters

The CA3338 family are CMOS/SOS high speed R2R voltage output digital-to-analog converters. They can operate from a single +5V supply, at video speeds, and can produce "rail-to-rail" output swings. Internal level shifters and a pin for an optional second supply provide for an output range below digital ground. The data complement control allows the inversion of input data while the latch enable control provides either feedthrough or latched operation. Both ends of the R2R ladder network are available externally and may be modulated for gain or offset adjustments. In addition, "glitch" energy has been kept very low by segmenting and thermometer encoding of the upper 3 bits.

The CA3338 is manufactured on a sapphire substrate to give low dynamic power dissipation, low output capacitance, and inherent latch-up resistance.

## Ordering Information

| PART<br>NUMBER      | LINEARITY<br>(INL, DNL) | TEMP.<br>RANGE (°C) | PACKAGE                 | PKG.<br>DWG.# |

|---------------------|-------------------------|---------------------|-------------------------|---------------|

| CA3338E             | ±1.0 LSB                | -40 to 85           | 16 Ld PDIP              | E16.3         |

| CA3338EZ<br>(Note)  | ±1.0 LSB                | -40 to 85           | 16 Ld PDIP<br>(Pb-free) | E16.3         |

| CA3338AE            | ±0.75 LSB               | -40 to 85           | 16 Ld PDIP              | E16.3         |

| CA3338AEZ<br>(Note) | ±0.75 LSB               | -40 to 85           | 16 Ld PDIP<br>(Pb-free) | E16.3         |

| CA3338M             | ±1.0 LSB                | -40 to 85           | 16 Ld SOIC              | M16.3         |

| CA3338MZ<br>(Note)  | ±1.0 LSB                | -40 to 85           | 16 Ld SOIC<br>(Pb-free) | M16.3         |

| CA3338AM            | ±0.75 LSB               | -40 to 85           | 16 Ld SOIC              | M16.3         |

| CA3338AMZ<br>(Note) | ±0.75 LSB               | -40 to 85           | 16 Ld SOIC<br>(Pb-free) | M16.3         |

Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B.

#### **Features**

- CMOS/SOS Low Power

- · R2R Output, Segmented for Low "Glitch"

- CMOS/TTL Compatible Inputs

- · Feedthrough Latch for Clocked or Unclocked Use

- · Data Complement Control

- High Update Rate (Typ) . . . . . . . . . . . . . . . . 50MHz

- Unipolar or Bipolar Operation

- · Pb-free Available

## **Applications**

- TV/Video Display

- · High Speed Oscilloscope Display

- · Digital Waveform Generator

- · Direct Digital Synthesis

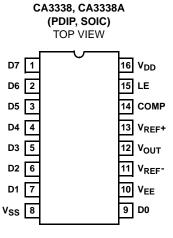

#### **Pinout**

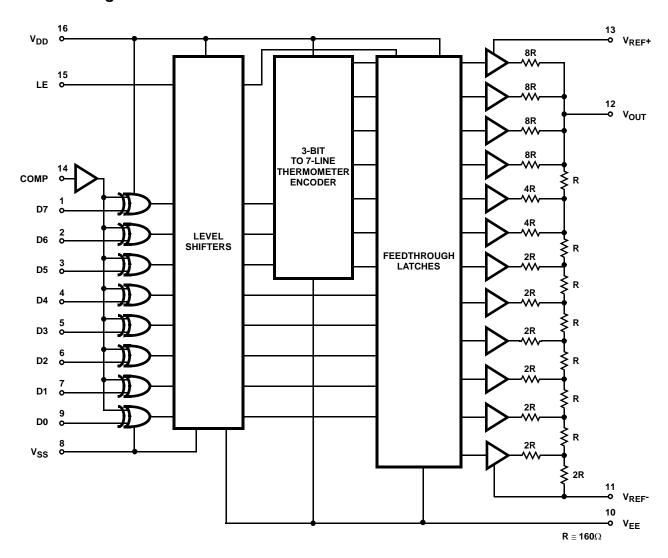

## Functional Diagram

## CA3338, CA3338A

#### **Absolute Maximum Ratings**

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)   | $\theta_{JA}$ (oC/W) | θ <sub>JC</sub> (oC/M)               |

|----------------------------------------|----------------------|--------------------------------------|

| PDIP Package                           | 90                   | N/A                                  |

| SOIC Package                           | 100                  | N/A                                  |

| Maximum Junction Temperature           |                      |                                      |

| Plastic Packages                       |                      | 150°C                                |

| Maximum Storage Temperature Range, To  | STG65                | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10 | Os)                  | 300°C                                |

| (SOIC - Lead Tips Only)                |                      |                                      |

#### **Operating Conditions**

Temperature Range (T<sub>A</sub>)

Plastic Package, E suffix, M suffix . . . . . . . -40°C to 85°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

##

| PARAMETER                        | TEST CONDITIONS                                                          | MIN | TYP | MAX   | UNITS |

|----------------------------------|--------------------------------------------------------------------------|-----|-----|-------|-------|

| ACCURACY                         | ·                                                                        |     | 1   | •     | 1     |

| Resolution                       |                                                                          | 8   | -   | -     | Bits  |

| Integral Linearity Error         | See Figure 4                                                             |     |     |       |       |

| CA3338                           |                                                                          | -   | -   | ±1    | LSB   |

| CA3338A                          |                                                                          | -   | -   | ±0.75 | LSB   |

| Differential Linearity Error     | See Figure 4                                                             |     |     |       |       |

| CA3338                           |                                                                          | -   | -   | ±0.75 | LSB   |

| CA3338A                          |                                                                          | -   | -   | ±0.5  | LSB   |

| Gain Error                       | Input Code = FF <sub>HEX</sub> , See Figure 3                            |     |     |       |       |

| CA3338                           |                                                                          | -   | -   | ±0.75 | LSB   |

| CA3338A                          |                                                                          | -   | -   | ±0.5  | LSB   |

| Offset Error                     | Input Code = 00 <sub>HEX</sub> ; See Figure 3                            | -   | -   | ±0.25 | LSB   |

| DIGITAL INPUT TIMING             |                                                                          |     |     | 1     | 1     |

| Update Rate                      | To Maintain <sup>1</sup> / <sub>2</sub> LSB Settling                     | DC  | 50  | -     | MHz   |

| Update Rate                      | V <sub>REF</sub> - = V <sub>EE</sub> = -2.5V, V <sub>REF</sub> + = +2.5V | DC  | 20  | -     | MHz   |

| Set Up Time t <sub>SU1</sub>     | For Low Glitch                                                           | -   | -2  | -     | ns    |

| Set Up Time t <sub>SU2</sub>     | For Data Store                                                           | -   | 8   | -     | ns    |

| Hold Time t <sub>H</sub>         | For Data Store                                                           | -   | 5   | -     | ns    |

| Latch Pulse Width t <sub>W</sub> | For Data Store                                                           | -   | 5   | -     | ns    |

| Latch Pulse Width t <sub>W</sub> | V <sub>REF</sub> - = V <sub>EE</sub> = -2.5V, V <sub>REF</sub> + = +2.5V | -   | 25  | -     | ns    |

| OUTPUT PARAMETERS                | R <sub>L</sub> Adjusted for 1V <sub>P-P</sub> Output                     |     |     | 1     | 1     |

| Output Delay t <sub>D1</sub>     | From LE Edge                                                             | -   | 25  | -     | ns    |

| Output Delay t <sub>D2</sub>     | From Data Changing                                                       | -   | 22  | -     | ns    |

| Rise Time t <sub>r</sub>         | 10% to 90% of Output                                                     | -   | 4   | -     | ns    |

| Settling Time t <sub>S</sub>     | 10% to Settling to <sup>1</sup> / <sub>2</sub> LSB                       | -   | 20  | -     | ns    |

| Output Impedance                 | V <sub>REF</sub> + = 6V, V <sub>DD</sub> = 6V                            | 120 | 160 | 200   | Ω     |

| Glitch Area                      |                                                                          | -   | 150 | -     | pV/s  |

| Glitch Area                      | $V_{REF}$ = $V_{EE}$ = -2.5 $V$ , $V_{REF}$ + = +2.5 $V$                 | -   | 250 | -     | pV/s  |

## CA3338, CA3338A

##

| PARAMETER                                  | TEST CONDITIONS                                | MIN                                           | TYP | MAX                    | UNITS                |

|--------------------------------------------|------------------------------------------------|-----------------------------------------------|-----|------------------------|----------------------|

| REFERENCE VOLTAGE                          |                                                |                                               |     |                        |                      |

| V <sub>REF</sub> + Range                   | (+) Full Scale, Note 2                         | (+) Full Scale, Note 2 V <sub>REF</sub> -+3 - |     | V <sub>DD</sub>        | V                    |

| V <sub>REF</sub> - Range                   | (-) Full Scale, Note 2                         | V <sub>EE</sub>                               | -   | V <sub>REF</sub> + - 3 | V                    |

| V <sub>REF</sub> + Input Current           | V <sub>REF</sub> + = 6V, V <sub>DD</sub> = 6V  | -                                             | 40  | 50                     | mA                   |

| SUPPLY VOLTAGE                             |                                                |                                               |     |                        |                      |

| Static I <sub>DD</sub> or I <sub>EE</sub>  | LE = Low, D0 - D7 = High                       | -                                             | 100 | 220                    | μΑ                   |

|                                            | LE = Low, D0 - D7 = Low                        | -                                             | -   | 100                    | μΑ                   |

| Dynamic I <sub>DD</sub> or I <sub>EE</sub> | V <sub>OUT</sub> = 10MHz, 0V to 5V Square Wave | -                                             | 20  | -                      | mA                   |

| Dynamic I <sub>DD</sub> or I <sub>EE</sub> | V <sub>OUT</sub> = 10MHz, ±2.5V Square Wave    | -                                             | 25  | -                      | mA                   |

| V <sub>DD</sub> Rejection                  | 50kHz Sine Wave Applied                        | -                                             | 3   | -                      | mV/V                 |

| V <sub>EE</sub> Rejection                  | 50kHz Sine Wave Applied                        | -                                             | 1   | -                      | mV/V                 |

| DIGITAL INPUTS D0 - D7,                    | LE, COMP                                       |                                               |     |                        |                      |

| High Level Input Voltage                   | Note 2                                         | 2                                             | -   | -                      | V                    |

| Low Level Input Voltage                    | Note 2                                         | -                                             | -   | 0.8                    | V                    |

| Leakage Current                            |                                                | -                                             | ±1  | ±5                     | μΑ                   |

| Capacitance                                |                                                | -                                             | 5   | -                      | pF                   |

| TEMPERATURE COEFFICIE                      | NTS                                            |                                               | ,   | •                      | ,                    |

| Output Impedance                           |                                                | -                                             | 200 | -                      | ppm/x <sup>o</sup> C |

## NOTE:

<sup>2.</sup> Parameter not tested. but guaranteed by design or characterization.

## Pin Descriptions

| PIN | NAME               | DESCRIPTION                                |  |  |

|-----|--------------------|--------------------------------------------|--|--|

| 1   | D7                 | Most Significant Bit                       |  |  |

| 2   | D6                 | Input                                      |  |  |

| 3   | D5                 | Data                                       |  |  |

| 4   | D4                 | Bits                                       |  |  |

| 5   | D3                 | (High = True)                              |  |  |

| 6   | D2                 |                                            |  |  |

| 7   | D1                 |                                            |  |  |

| 8   | V <sub>SS</sub>    | Digital Ground                             |  |  |

| 9   | D <sub>0</sub>     | Least Significant Bit. Input Data Bit      |  |  |

| 10  | VEE                | Analog Ground                              |  |  |

| 11  | V <sub>REF</sub> - | Reference Voltage Negative Input           |  |  |

| 12  | V <sub>OUT</sub>   | Analog Output                              |  |  |

| 13  | V <sub>REF</sub> + | Reference Voltage Positive Input           |  |  |

| 14  | COMP               | Data Complement Control input. Active High |  |  |

| 15  | LE                 | Latch Enable Input. Active Low             |  |  |

| 16  | $V_{DD}$           | Digital Power Supply, +5V                  |  |  |

#### Digital Signal Path

The digital inputs (LE, COMP, and D0 - D7) are of TTL compatible HCT High Speed CMOS design: the loading is essentially capacitive and the logic threshold is typically 1.5V.

The 8 data bits, D0 (weighted  $2^0$ ) through D7 (weighted  $2^7$ ), are applied to Exclusive OR gates (see Functional Diagram). The COMP (data complement) control provides the second input to the gates: if COMP is high, the data bits will be inverted as they pass through.

The input data and the LE (latch enable) signals are next applied to a level shifter. The inputs, operating between the levels of  $V_{DD}$  and  $V_{SS}$ , are shifted to operate between  $V_{DD}$  and  $V_{EE}$ . VEE optionally at ground or at a negative voltage, will be discussed under bipolar operation. All further logic elements except the output drivers operate from the  $V_{DD}$  and  $V_{EE}$  supplies.

The upper 3 bits of data, D5 through D7, are input to a 3-to-7 line bar graph encoder. The encoder outputs and D0 through D4 are applied to a feedthrough latch, which is controlled by LE (latch enable).

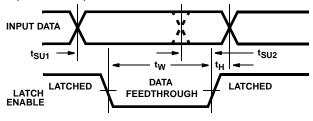

FIGURE 1. DATA TO LATCH ENABLE TIMING

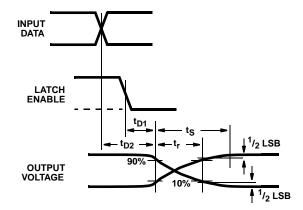

FIGURE 2. DATA AND LATCH ENABLE TO OUTPUT TIMING

## Latch Operation

Data is fed from input to output while LE is low: LE should be tied low for non-clocked operation.

Non-clocked operation or changing data while LE is low is not recommended for applications requiring low output "glitch" energy: there is no guarantee of the simultaneous changing of input data or the equal propagation delay of all bits through the converter. Several parameters are given if the converter is to be used in either of these modes:  $t_{D2}$  gives the delay from the input changing to the output changing (10%), while  $t_{SU2}$  and  $t_H$  give the set up and hold times (referred to LE rising edge) needed to latch data. See Figures 1 and 2.

Clocked operation is needed for low "glitch" energy use. Data must meet the given  $t_{SU1}$  set up time to the LE falling edge, and the  $t_H$  hold time from the LE rising edge. The delay to the output changing,  $t_{D1}$ , is now referred to the LE falling edge.

There is no need for a square wave LE clock; LE must only meet the minimum  $t_W$  pulse width for successful latch operation. Generally, output timing (desired accuracy of settling) sets the upper limit of usable clock frequency.

#### **Output Structure**

The latches feed data to a row of high current CMOS drivers, which in turn feed a modified R2R ladder network.

The "N" channel (pull down) transistor of each driver plus the bottom "2R" resistor are returned to  $V_{REF}$ - this is the (-) full-scale reference. The "P" channel (pull up) transistor of each driver is returned to  $V_{REF}$ +, the (+) full-scale reference.

In unipolar operation,  $V_{REF}$ - would typically be returned to analog ground, but may be raised above ground (see specifications). There is substantial code dependent current that flows from  $V_{REF}$ + to  $V_{REF}$ - (see  $V_{REF}$ + input current in specifications), so  $V_{REF}$ - should have a low impedance path to ground.

In bipolar operation,  $V_{REF}$ - would be returned to a negative voltage (the maximum voltage rating to  $V_{DD}$  must be observed).  $V_{EE}$ , which supplies the gate potential for the output drivers, must be returned to a point at least as negative as  $V_{REF}$ -. Note that the maximum clocking speed decreases when the bipolar mode is used.

#### Static Characteristics

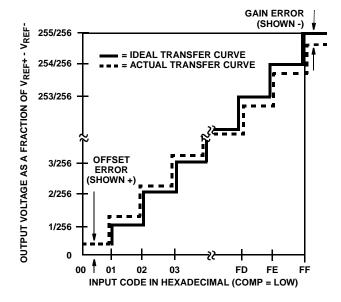

The ideal 8-bit D/A would have an output equal to  $V_{REF}$ - with an input code of  $00_{HEX}$  (zero scale output), and an output equal to 255/256 of  $V_{REF}$ + (referred to  $V_{REF}$ -) with an input code of  $FF_{HEX}$  (full scale output). The difference between the ideal and actual values of these two parameters are the OFFSET and GAIN errors, respectively; see Figure 3.

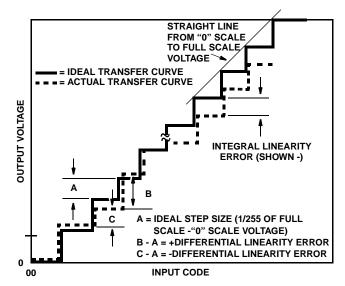

If the code into an 8-bit D/A is changed by 1 count, the output should change by 1/255 (full scale output - zero scale output). A deviation from this step size is a differential linearity error, see Figure 4. Note that the error is expressed in fractions of the ideal step size (usually called an LSB). Also note that if the (-) differential linearity error is less (in absolute numbers) than 1 LSB, the device is monotonic. (The output will always increase for increasing code or decrease for decreasing code).

If the code into an 8-bit D/A is at any value, say "N", the output voltage should be N/255 of the full scale output (referred to the zero scale output). Any deviation from that output is an integral linearity error, usually expressed in LSBs. See Figure 4.

Note that OFFSET and GAIN errors do not affect integral linearity, as the linearity is referenced to actual zero and full scale outputs, not ideal. Absolute accuracy would have to also take these errors into account.

FIGURE 3. D/A OFFSET AND GAIN ERROR

FIGURE 4. D/A INTEGRAL AND DIFFERENTIAL LINEARITY

## **Dynamic Characteristics**

Keeping the full-scale range ( $V_{REF}$ + -  $V_{REF}$ -) as high as possible gives the best linearity and lowest "glitch" energy (referred to 1V). This provides the best "P" and "N" channel gate drives (hence saturation resistance) and propagation delays. The  $V_{REF}$ + (and  $V_{REF}$ - if bipolar) terminal should be well bypassed as near the chip as possible.

"Glitch" energy is defined as a spurious voltage that occurs as the output is changed from one voltage to another. In a binary input converter, it is usually highest at the most significant bit transition (7F<sub>HEX</sub> to 80<sub>HEX</sub> for an 8 bit device), and can be measured by displaying the output as the input code alternates around that point. The "glitch" energy is the area between the actual output display and an ideal one LSB step voltage (subtracting negative area from positive), at either the positive or negative-going step. It is usually expressed in pV/s.

The CA3338 uses a modified R2R ladder, where the 3 most significant bits drive a bar graph decoder and 7 equally weighted resistors. This makes the "glitch" energy at each  $^{1}/_{8}$  scale transition (1F $_{\rm HEX}$  to 20 $_{\rm HEX}$ , 3F $_{\rm HEX}$  to 40 $_{\rm HEX}$ , etc.) essentially equal, and far less than the MSB transition would otherwise display.

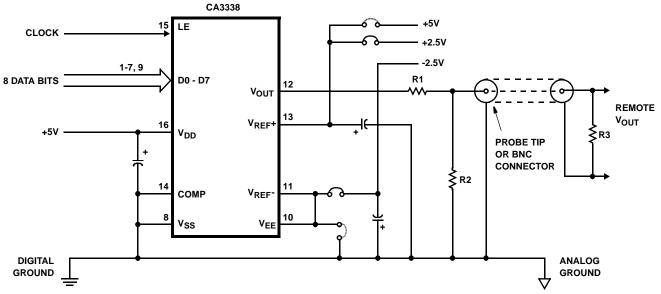

For the purpose of comparison to other converters, the output should be resistively divided to 1V full scale. Figure 5 shows a typical hook-up for checking "glitch" energy or settling time.

The settling time of the A/D is mainly a function of the output resistance (approximately  $160\Omega$  in parallel with the load resistance) and the load plus internal chip capacitance. Both "glitch" energy and settling time measurements require very good circuit and probe grounding: a probe tip connector such as Tektronix part number 131-0258-00 is recommended.

| FUNCTION             | CONNECTOR | R1    | R2  | R3  | V <sub>OUT (P-P)</sub> |

|----------------------|-----------|-------|-----|-----|------------------------|

| Oscilloscope Display | Probe Tip | 82Ω   | 62Ω | N/C | 1V                     |

| Match 93Ω Cable      | BNC       | 75    | 160 | 93  | 1V                     |

| Match 75Ω Cable      | BNC       | 18    | 130 | 75  | 1V                     |

| Match 50Ω Cable      | BNC       | Short | 75  | 50  | 0 79V                  |

#### NOTES:

- 3.  $V_{OUT(P-P)}$  is approximate, and will vary as  $R_{OUT}$  of D/A varies.

- 4. All drawn capacitors are  $0.1\mu F$  multilayer ceramic/4.7  $\mu F$  tantalum.

- 5. Dashed connections are for unipolar operation. Solid connection are for bipolar operation.

#### FIGURE 5. CA3338 DYNAMIC TEST CIRCUIT

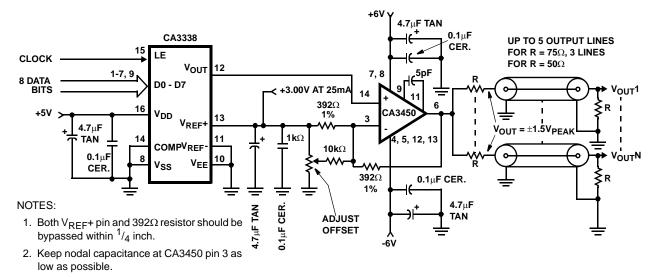

3.  $V_{OUT}$  Range =  $\pm 3V$  at CA3450.

FIGURE 6. CA3338 AND CA3450 FOR DRIVING MULTIPLE COAXIAL LINES

TABLE 1. OUTPUT VOLTAGE vs INPUT CODE AND  $V_{REF}$

| V <sub>REF</sub> +                                                                                  | 5.12V             | 5.00V             | 4.608V            | 2.56V             | 2.50V             |

|-----------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| V <sub>REF</sub> -                                                                                  | 0                 | 0                 | 0                 | -2.56V            | -2.50V            |

| STEP SIZE                                                                                           | 0.0200V           | 0.0195V           | 0.0180V           | 0.0200V           | 0.0195V           |

| Input Code<br>111111111 <sub>2</sub> =FF <sub>HEX</sub><br>11111110 <sub>2</sub> =FE <sub>HEX</sub> | 5.1000V<br>5.0800 | 4.9805V<br>4.9610 | 4.5900V<br>4.5720 | 2.5400V<br>2.5200 | 2.4805V<br>2.4610 |

| •                                                                                                   |                   |                   |                   |                   |                   |

| 10000001 <sub>2</sub> =81 <sub>HEX</sub>                                                            | 2.5800            | 2.5195            | 2.3220            | 0.0200            | 0.0195            |

| 10000000 <sub>2</sub> =80 <sub>HEX</sub>                                                            | 2.5600            | 2.5000            | 2.3040            | 0.0000            | 0.0000            |

| 01111111 <sub>2</sub> =7F <sub>HEX</sub>                                                            | 2.5400            | 2.4805            | 2.2860            | - 0.0200          | -0.0195           |

| •                                                                                                   |                   |                   |                   |                   |                   |

| 00000001 <sub>2</sub> =01 <sub>HEX</sub>                                                            | 0.0200            | 0.0195            | 0.0180            | -2.5400           | -2.4805           |

| 00000000 <sub>2</sub> =00 <sub>HEX</sub>                                                            | 0.0000            | 0.0000            | 0.0000            | -2.5600           | -2.5000           |

## **Applications**

The output of the CA3338 can be resistively divided to match a doubly terminated  $50\Omega$  or  $75\Omega$  line, although peak-to-peak swings of less than 1V may result. The output magnitude will also vary with the converter's output impedance. Figure 5 shows such an application. Note that because of the HCT input structure, the CA3338 could be operated up to +7.5V  $V_{DD}$  and  $V_{REF}+$  supplies and still accept 0V to 5V CMOS input voltages.

If larger voltage swings or better accuracy is desired, a high speed output buffer, such as the HA-5033, HA-2542, or CA3450, can be employed. Figure 6 shows a typical application, with the output capable of driving  $\pm 2 \text{V}$  into multiple  $50\Omega$  terminated lines.

# Operating and Handling Considerations HANDLING

All inputs and outputs of CMOS devices have a network for electrostatic protection during handling. Recommended handling practices for CMOS devices are described in AN6525. "Guide to Better Handling and Operation of CMOS Integrated Circuits."

#### **OPERATING**

#### **OPERATING VOLTAGE**

During operation near the maximum supply voltage limit, care should be taken to avoid or suppress power supply turn-on and turn-off transients, power supply ripple, or ground noise; any of these conditions must not cause the absolute maximum ratings to be exceeded.

#### **INPUT SIGNALS**

To prevent damage to the input protection circuit, input signals should never be greater than  $V_{DD}$  nor less than  $V_{SS}$ . Input currents must not exceed 20mA even when the power supply is off.

#### **UNUSED INPUTS**

A connection must be provided at every input terminal. All unused input terminals must be connected to either  $V_{CC}$  or GND, whichever is appropriate.

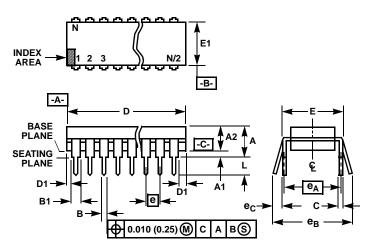

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- Dimensions A, A1 and L are measured with the package seated in JE-DEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E16.3 (JEDEC MS-001-BB ISSUE D)

16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES |       | MILLIM | ETERS |       |

|----------------|--------|-------|--------|-------|-------|

| SYMBOL         | MIN    | MAX   | MIN    | MAX   | NOTES |

| Α              | -      | 0.210 | -      | 5.33  | 4     |

| A1             | 0.015  | -     | 0.39   | -     | 4     |

| A2             | 0.115  | 0.195 | 2.93   | 4.95  | -     |

| В              | 0.014  | 0.022 | 0.356  | 0.558 | -     |

| B1             | 0.045  | 0.070 | 1.15   | 1.77  | 8, 10 |

| С              | 0.008  | 0.014 | 0.204  | 0.355 | -     |

| D              | 0.735  | 0.775 | 18.66  | 19.68 | 5     |

| D1             | 0.005  | -     | 0.13   | -     | 5     |

| Е              | 0.300  | 0.325 | 7.62   | 8.25  | 6     |

| E1             | 0.240  | 0.280 | 6.10   | 7.11  | 5     |

| е              | 0.100  | BSC   | 2.54   | BSC   | -     |

| e <sub>A</sub> | 0.300  | BSC   | 7.62   | BSC   | 6     |

| e <sub>B</sub> | -      | 0.430 | -      | 10.92 | 7     |

| L              | 0.115  | 0.150 | 2.93   | 3.81  | 4     |

| N              | 1      | 6     | 1      | 6     | 9     |

Rev. 0 12/93

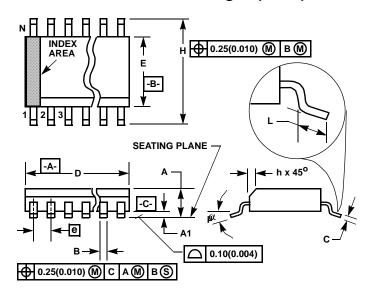

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M16.3 (JEDEC MS-013-AA ISSUE C)

16 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES |                | MILLIMETERS |       |       |

|--------|--------|----------------|-------------|-------|-------|

| SYMBOL | MIN    | MAX            | MIN         | MAX   | NOTES |

| Α      | 0.0926 | 0.1043         | 2.35        | 2.65  | -     |

| A1     | 0.0040 | 0.0118         | 0.10        | 0.30  | -     |

| В      | 0.013  | 0.0200         | 0.33        | 0.51  | 9     |

| С      | 0.0091 | 0.0125         | 0.23        | 0.32  | -     |

| D      | 0.3977 | 0.4133         | 10.10       | 10.50 | 3     |

| Е      | 0.2914 | 0.2992         | 7.40        | 7.60  | 4     |

| е      | 0.050  | BSC            | 1.27 BSC    |       | -     |

| Н      | 0.394  | 0.419          | 10.00       | 10.65 | -     |

| h      | 0.010  | 0.029          | 0.25        | 0.75  | 5     |

| L      | 0.016  | 0.050          | 0.40        | 1.27  | 6     |

| N      | 16     |                | 1           | 6     | 7     |

| α      | 0°     | 8 <sup>0</sup> | 0°          | 8°    | -     |

Rev. 0 12/93

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com