#

# Calibrated Quad 12-Bit Voltage-Output D/A Converters

### **General Description**

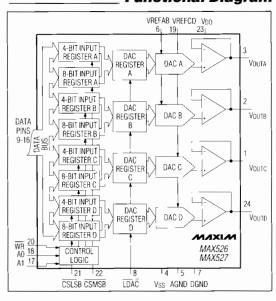

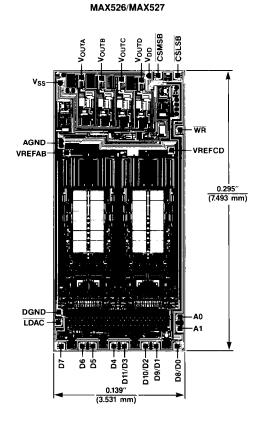

The MAX526/MAX527 contain four 12-bit, voltage-output digital-to-analog converters (DACs). Precision output buffer amplifiers are included on-chip to provide voltage outputs. The MAX527 operates with ±5V power supplies, while the MAX526 utilizes -5V and +12V to +15V supplies. Offset, gain, and linearity are factory calibrated to provide the MAX526's 1LSB total unadjusted error (TUE).

These devices feature double-buffered interface logic with a 12-bit input register and a 12-bit DAC register. Data in the DAC register sets the DAC output voltage. The MAX526/MAX527 have an 8-bit-wide data bus. Data is loaded into the input register using two write operations with an 8-bit LSB write load and a 4-bit MSB write load. An asynchronous load DAC (LDAC) input transfers data from the input register to the DAC register. All logic inputs are TTL and CMOS compatible.

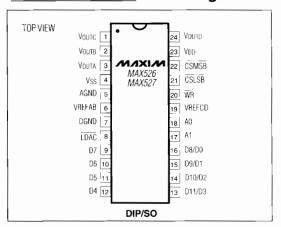

The MAX526/MAX527 are available in 24-pin, 300 mil plastic DIP, Ceramic SB, and wide SO packages.

### \_Applications

Minimum Component Count Analog Systems

Digital Offset/Gain Adjustment

Arbitrary Function Generators

Industrial Process Controls

Automatic Test Equipment

### **Functional Diagram**

### Features

- ◆ Reference Input Range Includes Ground (C, D grades)

- ♦ Full 12-Bit Performance Without Adjustments

- ♦ 1 LSB Total Unadjusted Error (MAX526)

- ♦ Buffered Voltage Outputs

- Fast Output Settling 3μs for MAX526 5μs for MAX527

- ♦ Double-Buffered Digital Inputs

- ♦ Microprocessor and TTL/CMOS Compatible

- ♦ ±5V Supply Operation (MAX527)

### Ordering Information

| PART       | TEMP. RANGE     | PIN-PACKAGE            | INL<br>(LSBs) |

|------------|-----------------|------------------------|---------------|

| MAX526CCNG | 0°C to +70°C    | 24 Narrow Plastic DIP  | ±1/2          |

| MAX526DCNG | 0°C to +70°C    | 24 Narrow Plastic DIP  | ±1            |

| MAX526CCWG | 0°C to +70°C    | 24 Wide SO             | ±1/2          |

| MAX526DCWG | 0°C to +70°C    | 24 Wide SO             | ±1            |

| MAX526DC/D | 0°C to +70°C    | Dice*                  | ±1            |

| MAX526CENG | -40°C to +85°C  | 24 Narrow Plastic DIP  | ± 1/2         |

| MAX526DENG | -40°C to +85°C  | 24 Narrow Plastic DIP  | ±1            |

| MAX526CEWG | -40°C to +85°C  | 24 Wide SO             | ± 1/2         |

| MAX526DEWG | -40°C to +85°C  | 24 Wide SO             | ±1            |

| MAX526CMYG | -55°C to +125°C | 24 Narrow Ceramic SB** | ± 1/2         |

| MAX526DMYG | -55°C to +125°C | 24 Narrow Ceramic SB** | ±1            |

### Ordering Information continued on last page.

- Contact factory for dice specifications.

- \*\* Contact factory for availability and processing to MIL-STD-883.

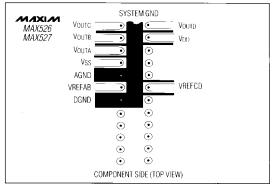

### Pin Configuration

ノレノスコノレ

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

### **ABSOLUTE MAXIMUM RATINGS - MAX526**

| 712002012 III/1/IIII0III 11/11 III                    |                                   |

|-------------------------------------------------------|-----------------------------------|

| V <sub>DD</sub> to AGND or DGND                       | 0.3V, +17V                        |

| Vss to AGND or DGND                                   | 7V, to 0.3V                       |

| Digital Input Voltage to AGND or DGND0.3V             | $V_{1}, V_{DD} + 0.3V_{1}$        |

| VREF to AGND or DGND0.3V                              | $V_1 V_{DD} + 0.3V_1$             |

| Vout to AGND or DGND                                  | V <sub>DD</sub> , V <sub>SS</sub> |

| Maximum Current into Any Pin                          | 50mA                              |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                   |

| Plastic DIP (derate 13.33mW/°C above +70°C)           | 733mW                             |

|                                                       |                                   |

| Wide SO (derate 11.76mW/°C above +70  | °C)647mW       |

|---------------------------------------|----------------|

| Ceramic SB (derate 14.29mW/°C above - | +70°C)1143mW   |

| Operating Temperature Ranges:         |                |

| MAX526_C_G                            | 0°C to +70°C   |

| MAX526_E_G                            | 40°C to +85°C  |

| MAX526_MYG                            | 55°C to +125°C |

| Storage Temperature Range             | 65°C to +150°C |

| Lead Temperature (soldering, 10 sec)  | +300°C         |

|                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS - MAX526**

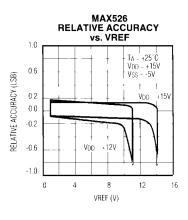

$(V_{DD} = +15V, V_{SS} = -5V, VREF = 10V, AGND = DGND = 0V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                          | SYMBOL                   | CONDITIONS                                                   |                        | MIN | TYP    | MAX     | UNITS |  |

|------------------------------------|--------------------------|--------------------------------------------------------------|------------------------|-----|--------|---------|-------|--|

| STATIC PERFORMANCE                 | - ANALOG SECTI           | ON (R <sub>L</sub> = $5k\Omega$ , C <sub>L</sub> = $100pF$ ) |                        |     |        |         |       |  |

| Resolution                         | N                        |                                                              |                        | ±12 |        |         | Bits  |  |

|                                    |                          | MAX526C                                                      | T <sub>A</sub> = +25°C |     |        | ±1.0    |       |  |

|                                    |                          | MAX526D                                                      | 14 - 725 0             |     |        | ±2.0    | ]     |  |

| Total Unadjusted Error<br>(Note 1) |                          | MAX526CC                                                     |                        |     |        | ±2.0    | 1     |  |

|                                    | TUE                      | MAX526DC                                                     |                        |     |        | ±3.0    | LSB   |  |

|                                    | 105                      | MAX526CE                                                     |                        |     |        | ±2.5    | LOD   |  |

|                                    |                          | MAX526DE                                                     |                        |     |        | ±3.5    | 1     |  |

|                                    |                          | MAX526CM                                                     |                        |     |        | ±3.0    | 1     |  |

|                                    |                          | MAX526DM                                                     |                        |     |        | ±4.0    | 1     |  |

|                                    |                          | MAX526C                                                      |                        |     | ±0.15  | ±0.50   | 1.00  |  |

| Integral Nonlinearity              | INL                      | MAX526D                                                      |                        |     |        | ±1      | LSB   |  |

| Differential Nonlinearity          | DNL                      | Guaranteed monotonic                                         |                        |     |        | ±1      | LSB   |  |

|                                    |                          | MAX526C                                                      | 7 0500                 | -   |        | ±1.0    |       |  |

|                                    | 1                        | MAX526D                                                      | $T_A = +25^{\circ}C$   |     |        | ±2.0    |       |  |

|                                    |                          | MAX526CC<br>MAX526DC                                         |                        |     |        | ±2.0    | LSB   |  |

|                                    |                          |                                                              |                        |     |        | ±3.0    |       |  |

| Offset Error                       |                          | MAX526CE                                                     |                        |     |        | ±2.5    |       |  |

|                                    |                          | MAX526DE                                                     |                        |     |        | ±3.5    |       |  |

|                                    |                          | MAX526CM<br>MAX526DM                                         |                        |     |        | ±3.0    |       |  |

|                                    |                          |                                                              |                        |     |        | ±4.0    |       |  |

|                                    |                          | MAX526_C/E/M, R <sub>L</sub> = ∞                             |                        |     |        | ±1.0    |       |  |

| Gain Error                         |                          | MAX526_C/E                                                   |                        |     |        | ±1.5    | LSB   |  |

|                                    |                          | MAX526_M                                                     |                        |     |        | ±2.0    | 1     |  |

|                                    | ΔGain/ΔVDD               | V <sub>DD</sub> from +10.8V to +16.5V                        |                        |     | ±0.001 | ±0.01   |       |  |

|                                    | ΔGain/ΔVss               | Vss from -4.5V to -5.5V                                      | 7 0500                 |     | ±0.001 | ±0.01   | 1.000 |  |

| Power-Supply Rejection             | ΔOffset/ΔV <sub>DD</sub> | V <sub>DD</sub> from +10.8V to +16.5V                        | $T_A = +25^{\circ}C$   |     | ±0.007 | ±0.075  | LSB/% |  |

|                                    | ΔOffset/ΔVss             | Vss from -4.5V to -5.5V                                      |                        |     | ±0.003 | 3 ±0.03 | 1     |  |

| MATCHING PERFORMAN                 | CE                       |                                                              |                        |     |        |         |       |  |

| Total Unadjusted Error             | TUE                      | MAX526C                                                      | T <sub>A</sub> = +25°C |     |        | ±1.0    | LSB   |  |

| (Note 1)                           | IUE                      | MAX526D                                                      | 1A = +25°C             |     |        | ±2.0    | LSB   |  |

| Gain Error                         |                          |                                                              | T <sub>A</sub> = +25°C |     | 0.1    | ±1.0    | LSB   |  |

| Officet France                     |                          | MAX526C                                                      | T <sub>A</sub> = +25°C |     | 0.5    | ±1.0    | LSB   |  |

| Offset Error                       |                          | MAX526D                                                      | 1A = +25°C             |     | 0.5    | ±2.0    | LSB   |  |

| Integral Nonlinearity              | INL                      |                                                              | T <sub>A</sub> = +25°C |     | 0.2    | ±1.0    | LSB   |  |

2 \_\_\_\_\_\_ /VI/IXI/VI

### **ELECTRICAL CHARACTERISTICS – MAX526 (continued)**

(VDD = +15V, VSS = -5V, VREF = 10V, AGND = DGND = 0V, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                            | SYMBOL                 | CONDI                            | TIONS                      | MIN      | TYP   | MAX                 | UNITS        |

|--------------------------------------|------------------------|----------------------------------|----------------------------|----------|-------|---------------------|--------------|

| REFERENCE INPUT (Note 2)             | )                      |                                  |                            |          |       |                     |              |

| Reference Input Range                | REF                    |                                  |                            | 0        |       | V <sub>DD</sub> - 4 | V            |

| Reference Input Resistance           | RREF                   |                                  |                            | 5        |       |                     | kΩ           |

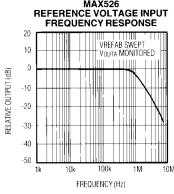

| MULTIPLYING MODE PERFO               | RMANCE                 |                                  |                            |          |       |                     |              |

| Reference 3dB Bandwidth              |                        |                                  |                            |          | 700   |                     | kHz          |

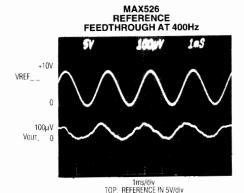

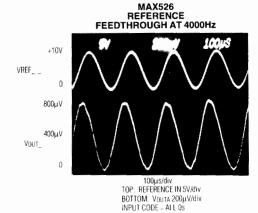

| Deference Foodthrough                |                        | Input code = all 0s              | VREF = 10Vp-p at 400HZ     |          | -100  |                     | dB           |

| Reference Feedthrough                |                        | Imput code = air os              | VREF = 10Vp-p at<br>4000HZ | <u> </u> | -82   |                     | ab           |

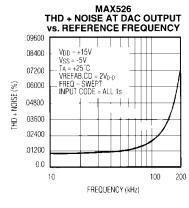

| Total Harmonic Distortion plus Noise | THD+N                  | VREF = 2V <sub>p-p</sub> at 50kH | dz                         |          | 0.012 |                     | %            |

| DIGITAL INPUTS                       |                        |                                  |                            | ,        |       | ,                   |              |

| Input High Voltage                   | VINH                   |                                  |                            | 2.4      |       |                     |              |

| Input Low Voltage                    | VINL                   |                                  |                            |          |       | 0.8                 | V            |

| Input Leakage Current                | I <sub>IN</sub>        | $V_{IN} = 0V \text{ or } V_{DD}$ |                            |          |       | 1.0                 | μΑ           |

| Input Capacitance                    | CIN                    | (Note 3)                         |                            |          |       | 10                  | pF           |

| DYNAMIC PERFORMANCE                  | $(R_L = 5k\Omega, C_L$ | = 100pF)                         | _                          |          |       | 1                   |              |

| Voltage-Output Slew Rate             |                        |                                  |                            | ↓ _      | 5     |                     | V/μs         |

| Output Settling Time                 | <u> </u>               | To ±1/2LSB of full sca           | <u></u>                    | l        | 3     |                     | μs           |

| Digital Feedthrough                  |                        |                                  |                            |          | 5     | _                   | nV-s_        |

| Digital Crosstalk                    |                        |                                  | <u>.</u> .                 |          | 5     | _                   | n <u>V-s</u> |

| POWER SUPPLIES                       |                        |                                  |                            |          |       |                     |              |

| Positive Supply Range                | $V_{DD}$               |                                  |                            | 10.8     |       | 16.5                | V            |

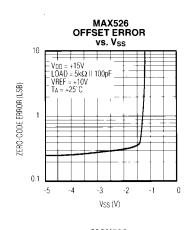

| Negative Supply Range                | V <sub>SS</sub>        |                                  |                            | -4.5     |       | -5.5                | V            |

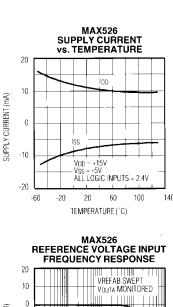

| Positive Supply Current              | loo                    | (Note 4)                         | T <sub>A</sub> = +25°C     | _        | 11    | $-\frac{20}{28}$    | mA_          |

| Negative Supply Current              | Iss                    | (Note 4)                         | T <sub>A</sub> = +25°C     |          | 8     | 18<br>26            | mA           |

Note 1: TUE is specified with no resistive load.

Note 2: See Reference Input section.

Note 3: Guaranteed by design. Not production tested.

Note 4: Digital inputs at 2.4V; with digital inputs at 0V, IDD decreases typically by 1.5mA at +25°C.

$\begin{array}{l} \textbf{TIMING CHARACTERISTICS - MAX526} \\ \text{(VDD = +15V, VSS = -5V, VREF = 10V, AGND = DGND = 0V, T_A = T_{MIN} to T_{MAX}, unless otherwise noted.)} \end{array}$

| PARAMETER              | SYMBOL          | CONDITIONS | MIN | TYP MAX | UNITS |

|------------------------|-----------------|------------|-----|---------|-------|

| CS Pulse Width         | tcs             | <u> </u>   | 100 |         | ns    |

| WR Pulse Width         | twR             |            | 100 |         | ns    |

| CS to WR Setup         | tcws            |            | 0   |         | ns_   |

| CS to WR Hold          | tcwH            |            | 0   |         | ns    |

| Data Valid to WR Setup | tos             |            | 75  |         | ns    |

| Data to WR Hold        | t <sub>DH</sub> |            | 10  |         | ns    |

| LDAC Pulse Width       | tLDAC           |            | 120 |         | ns    |

| Address to WR Setup    | tas             |            | 25  |         | ns    |

| Address to WR Hold     | tah             |            | 0   |         | ns    |

/VI/IXI/VI -

### **ABSOLUTE MAXIMUM RATINGS - MAX527**

| -0.3V, +12V                       |

|-----------------------------------|

| -7V, to 0.3V                      |

| $V_{DD} + 0.3V$                   |

| $V_{DD} + 0.3V$                   |

| V <sub>DD</sub> , V <sub>SS</sub> |

| 50mA                              |

|                                   |

| 733mW                             |

|                                   |

| Wide SO (derate 11.76mW/°C above +70  | °C)647mW       |

|---------------------------------------|----------------|

| Ceramic SB (derate 14.29mW/°C above + | +70°C)1143mW   |

| Operating Temperature Ranges:         |                |

| MAX527_C_G                            | 0°C to +70°C   |

| MAX527_E_G                            | 40°C to +85°C  |

| MAX527_MYG                            | 55°C to +125°C |

| Storage Temperature Range             | 65°C to +150°C |

| Lead Temperature (soldering, 10 sec)  | +300°C         |

|                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS - MAX527**

$(V_{DD} = +5V, V_{SS} = -5V, V_{REF} = 2.5V, AGND = DGND = 0V, T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                  | SYMBOL                   | CONDITIONS                                        |                        | MIN | TYP    | MAX       | UNITS |  |

|----------------------------|--------------------------|---------------------------------------------------|------------------------|-----|--------|-----------|-------|--|

| STATIC PERFORMANCE -       | ANALOG SECTI             | ON (R <sub>L</sub> = 5kΩ, C <sub>L</sub> = 100pF) |                        |     |        |           |       |  |

| Resolution                 | N                        |                                                   |                        | 12  |        | -         | Bits  |  |

| Integral Nonlinearity      | INL                      | MAX527C                                           |                        |     | ±0.15  | ±0.50     | 1 SB  |  |

| megrai Nonimeamy           | IINL                     | MAX527D                                           |                        |     |        | ±1        | LSB   |  |

| Differential Nonlinearity  | DNL                      | Guaranteed monotonic                              |                        |     |        | ±1        | LSB   |  |

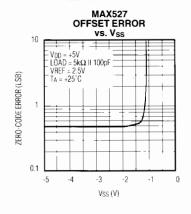

|                            |                          | MAX527C                                           | T <sub>A</sub> = +25°C |     |        | ±3        |       |  |

|                            |                          | MAX527D                                           | TA = +25 C             |     |        | ±6        |       |  |

|                            |                          | MAX527CC                                          |                        |     |        | ±6        |       |  |

| Offset Error               |                          | MAX527DC                                          |                        |     |        | ±9        | mV    |  |

|                            |                          | MAX527CE                                          |                        |     |        | ±7        | mv    |  |

|                            |                          | MAX527DE                                          |                        |     |        | ±11       |       |  |

|                            |                          | MAX527CM<br>MAX527DM                              |                        |     |        | ±9        |       |  |

|                            |                          |                                                   |                        |     |        | ±15       |       |  |

|                            |                          | MAX527_C/E, R <sub>L</sub> = ∞                    |                        |     |        | ±1.0      | LSB   |  |

|                            |                          | MAX527_M, R <sub>L</sub> = ∞                      |                        |     |        | ±1.0      |       |  |

| Gain Error                 |                          | MAX527_C                                          |                        |     |        | ±2.0      |       |  |

|                            |                          | MAX527_E                                          |                        |     |        | ±2.5      |       |  |

|                            |                          | MAX527_M                                          |                        |     |        | ±3.0      |       |  |

|                            | ΔGain/ΔV <sub>DD</sub>   | V <sub>DD</sub> from +4.5V to +5.5V               |                        |     | ±0.002 | ±0.02     | LSB/% |  |

| Power-Supply Rejection     | ΔGain/ΔVss               | Vss from -4.5V to -5.5V                           | T <sub>A</sub> = +25°C |     | ±0.002 | ±0.02     |       |  |

| Tower-Supply Hejection     | ΔOffset/ΔV <sub>DD</sub> | V <sub>DD</sub> from +4.5V to +5.5V               | 14 = +23 0             |     | ±0.005 | ±0.05     |       |  |

|                            | ΔOffset/ΔVss             | Vss from -4.5V to -5.5V                           |                        |     | ±0.005 | ±0.05     |       |  |

| MATCHING PERFORMANC        | E                        |                                                   |                        |     |        |           |       |  |

| Gain Error                 |                          |                                                   | $T_A = +25^{\circ}C$   |     | 0.1    | ±1.0      | LSB   |  |

| Offset Error               |                          | MAX527C                                           | T <sub>A</sub> = +25°C |     | 0.5    | ±5        | LSB   |  |

| (Note 1)                   |                          | MAX527D                                           | 1A = +25 O             |     | 0.5    | ±10       | LOD   |  |

| Integral Nonlinearity      | INL.                     |                                                   | $T_A = +25^{\circ}C$   |     | 0.2    | ±1.0      | LSB   |  |

| REFERENCE INPUT (Note:     |                          |                                                   |                        |     |        |           |       |  |

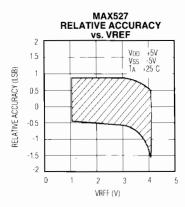

| Reference Input Range      | REF                      | Note 2                                            |                        | 0   | VI     | DD - 2.20 | V     |  |

| Reference Input Resistance | RREF                     |                                                   |                        | 5   |        |           | kΩ    |  |

| 4 |  |  | 101 21 21 31 |

|---|--|--|--------------|

|   |  |  |              |

### **ELECTRICAL CHARACTERISTICS (continued) – MAX527**

$(V_{DD} = +5V, V_{SS} = -5V, V_{REF} = +2.5V, AGND = DGND = 0V, T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                            | SYMBOL                  |                          | CONDITIONS                 | MIN  | TYP   | MAX  | UNITS         |

|--------------------------------------|-------------------------|--------------------------|----------------------------|------|-------|------|---------------|

| MULTIPLYING MODE PERFO               | ORMANCE                 |                          |                            |      |       |      |               |

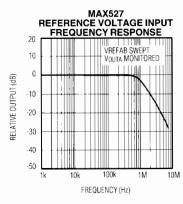

| Reference 3dB Bandwidth              |                         |                          |                            |      | 700   |      | kHz           |

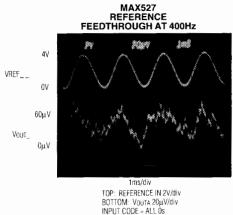

| Deference Foodtbrough                |                         | 400Hz                    |                            | i -  | -100  |      | dB            |

| Reference Feedthrough                | i                       | 4000Hz                   |                            |      | -82   |      | UB UB         |

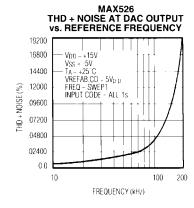

| Total Harmonic Distortion plus Noise | THD+N                   | VREF = 850m <sup>1</sup> | V <sub>p-p</sub> at 100kHz |      | 0.024 |      | %             |

| DIGITAL INPUTS                       |                         |                          |                            |      |       |      |               |

| Input High Voltage                   | VINH                    |                          |                            | 2.4  |       |      | V             |

| Input Low Voltage                    | VINL                    |                          |                            |      |       | 0.8  | V             |

| Input Leakage Current                | liN                     | VIN = OV or VI           | DD                         | _ i  |       | 1.0  | μΑ            |

| Input Capacitance                    | CIN                     | (Note 3)                 |                            |      |       | 10   | pF            |

| DYNAMIC PERFORMANCE                  | $(R_L = 5k\Omega, C_L)$ | = 100pF)                 |                            |      |       |      |               |

| Voltage-Output Slew Rate             |                         |                          |                            |      | 3     | _    | V/ <u>u</u> s |

| Output Settling Time                 |                         | To ±1/2LSB of            | full scale                 |      | 5     |      | μs            |

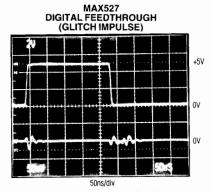

| Digital Feedthrough                  |                         |                          |                            |      | 5     |      | nV-s          |

| Digital Crosstalk                    |                         |                          |                            |      | 5     |      | nV-s          |

| POWER SUPPLIES                       |                         |                          |                            |      |       |      |               |

| Positive Supply Range                | V <sub>DD</sub>         |                          |                            | 4.75 |       | 5.5  | V             |

| Negative Supply Range                | Vss                     |                          |                            | -4.5 |       | -5.5 | V             |

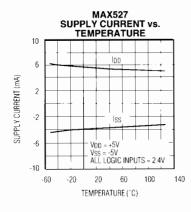

| Positive Supply Current              | IDD                     | (Note 4)                 | $T_A = +25^{\circ}C$       |      | 5.5   | 12   | mA            |

| r ositive Supply Current             | OO'                     | (14016 4)                |                            |      |       | 18   |               |

| Negative Supply Current              | Iss                     | (Note 4)                 | T <sub>A</sub> = +25°C     |      | 3.6   | 10   | mA            |

| riegative Supply Current             | 155                     | (14016 4)                |                            |      |       | 16   | "             |

Note 1: TUE is specified with no resistive load.

Note 2: See Reference Input section.

Note 3: Guaranteed by design. Not production tested.

Note 4: Digital inputs at 2.4V.

### **TIMING CHARACTERISTICS - MAX527**

(VDD = +5V, VSS = -5V, VREF = +2.5V, AGND = DGND = 0V, TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER              | SYMBOL                       | CONDITIONS | MIN 7 | TYP MAX | UNITS |

|------------------------|------------------------------|------------|-------|---------|-------|

| ČŠ Pulse Width         | tcs                          | MAX527_C/E | 180   |         | ns    |

|                        | ics _                        | MAX527_M   | 200   |         | 115   |

| WR Pulse Width.        | twn                          | MAX527_C/E | 180   |         | ns    |

|                        | - WH                         | MAX527_M   | 200   |         | 115   |

| CS to WR Setup         | tcws                         |            | 0     |         | ns    |

| ĈŜ to WR Hold          | tcwh                         |            | 0     |         | ns    |

| Data Valid to WR Setup | tds                          |            | 75    |         | _ ns  |

| Data to WR Hold        | t <sub>DH</sub>              |            | 0     |         | ns    |

| LDAC Pulse Width       | th t_DAC MAX527_C/E MAX527_M | MAX527_C/E | 120   |         | ns    |

|                        |                              | MAX527_M   | 150   |         |       |

| Address to WR Setup    | tas                          |            | 25    |         | ns    |

| Address to WR Hold     | t <sub>AH</sub>              | L          | 0     |         | ns    |

/VI/XI/VI \_\_\_\_\_\_\_ 5

### **Typical Operating Characteristics**

### **MAX526**

6 \_\_\_\_\_\_\_\_\_/VI/1XI/VI

# MAX526/MAX527

# Calibrated Quad 12-Bit Voltage-Output D/A Converters

## **Typical Operating Characteristics (continued)**

BOTTOM: VOUTA 100µV/div

INPUT CODE - ALL 0s

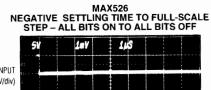

MAX526

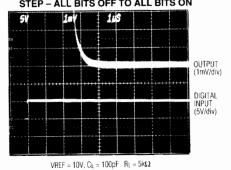

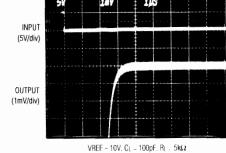

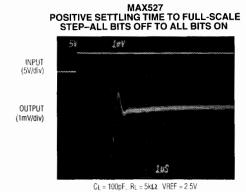

POSITIVE SETTLING TIME TO FULL-SCALE

STEP - ALL BITS OFF TO ALL BITS ON

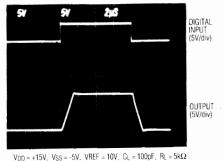

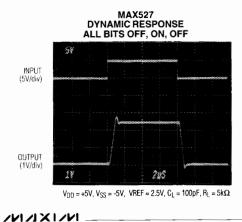

MAX526 DYNAMIC RESPONSE ALL BITS OFF, ON, OFF

TOP: DIGITAL TRANSITION ON ALL DATA BITS 5V/div BOTTOM: DAC OUPUT WITH WR HIGH 50mV/div

NINXIN

### **Typical Operating Characteristics**

2.5V

0V 100μV

### **Typical Operating Characteristics (continued)**

MAX527 REFERENCE FEEDTHROUGH AT 4000Hz

VREF\_\_

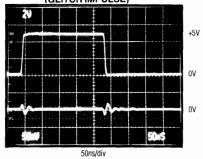

TOP: DIGITAL TRANSITION ON ALL DATA BITS 5V/div BOTTOM: DAC OUPUT WITH WR HIGH 50mV/div

9

### \_Pin Description

| PIN       | NAME            | FUNCTION                                                                                                                                       |  |  |  |  |

|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1         | Voutc           | DAC C Output Voltage                                                                                                                           |  |  |  |  |

| 2         | Voutb           | DAC B Output Voltage                                                                                                                           |  |  |  |  |

| 3         | Vouta           | DAC A Output Voltage                                                                                                                           |  |  |  |  |

| 4         | Vss             | Negative Power Supply                                                                                                                          |  |  |  |  |

| 5         | AGND            | Analog Ground                                                                                                                                  |  |  |  |  |

| 6         | VREFAB          | Reference Voltage Input for DAC A and DAC B                                                                                                    |  |  |  |  |

| _ 7       | DGND            | Digital Ground                                                                                                                                 |  |  |  |  |

| 8         | LDAC            | Load DAC Input (active low). Driving this asynchronous input low transfers the contents of each input register to its respective DAC register. |  |  |  |  |

| 9         | D7              | Data Bit 7                                                                                                                                     |  |  |  |  |

| 10        | D6              | Data Bit 6                                                                                                                                     |  |  |  |  |

| 11_       | D5              | Data Bit 5                                                                                                                                     |  |  |  |  |

| _12       | D4              | Data Bit 4                                                                                                                                     |  |  |  |  |

| 13 D11/D3 |                 | Data Bit 11 (MSB) if CSMSB is low and CSLSB is high. Data Bit 3 (MSB) if CSMSB is high and CSLSB is low.                                       |  |  |  |  |

| 14 D10/D2 |                 | Data Bit 10 (MSB) if CSMSB is low and CSLSB is high. Data Bit 2 (MSB) if CSMSB is high and CSLSB is low.                                       |  |  |  |  |

| 15        | D9//D1          | Data Bit 9 (MSB) if CSMSB is low and CSLSB is high. Data Bit 1 (MSB) if CSMSB is high and CSLSB is low.                                        |  |  |  |  |

| 16        | D8/D0           | Data Bit 8 (MSB) if CSMSB is low and CSLSB is high. Data Bit 0 (MSB) if CSMSB is high and CSLSB is low.                                        |  |  |  |  |

| 17        | A1              | DAC Address Select Bit (MSB)                                                                                                                   |  |  |  |  |

| 18        | A0              | DAC Address Select Bit (LSB)                                                                                                                   |  |  |  |  |

| 19        | VREFCD          | Reference Voltage Input for DAC C and DAC D                                                                                                    |  |  |  |  |

| 20 WR     |                 | Write Input (active low). WR along with CSMSB and CSLSB load data into the DAC input register selected by A1 and A0                            |  |  |  |  |

| 21        | CSLSB           | Chip Select for LS Byte (active low).<br>Selects the lower 8 bits of the addressed<br>input register.                                          |  |  |  |  |

| 22        | CSMSB .         | Chip Select for MS Nibble (active low).<br>Selects the upper 4 bits of the addressed<br>input register.                                        |  |  |  |  |

| 23        | V <sub>DD</sub> | Positive Supply Voltage                                                                                                                        |  |  |  |  |

| _24       | Voutd           | DAC D Output Voltage                                                                                                                           |  |  |  |  |

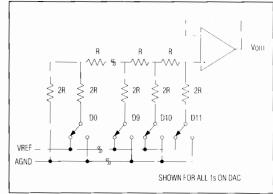

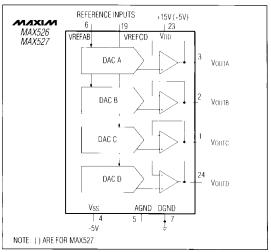

# Detailed Description Analog Section

The MAX526/MAX527 contain four voltage output DACs. The DACs are "inverted" R-2R ladder networks that convert 12-bit digital inputs into equivalent analog output voltages in proportion to the applied reference voltages. The MAX526/MAX527 have two reference inputs: one shared by DAC A and DAC B (VREFAB), and the other shared by DAC C and DAC D (VREFCD). These inputs allow different full-scale output voltage ranges for each pair of DACs (Figure 1).

Figure 1. Simplified DAC Circuit Diagram

### Reference Input

The MAX526/MAX527 can be used for multiplying applications. The reference accepts both DC and AC signals. The voltage at each VREF input sets the full-scale output voltages for its respective DACs. The input impedance of the VREF inputs are code dependent, with the lowest value (typically  $6k\Omega$  for VREFAB or VREFCD) occuring when the input code is 0101 0101 0101. The maximum value, typically  $60k\Omega$ , occurs when the input code is 0000 0000 0000. Since the input impedance at VREF is code dependent, load regulation of the reference used is important.

The guaranteed minimum input impedance of each reference input of the MAX526/MAX527 is  $5k\Omega$ . When the reference inputs are driven from the same source, the minimum impedance that must be driven by the reference source is  $2.5k\Omega$ . A voltage reference such as the MAX674 would typically deviate by 0.165LSB (0.33LSB worst case) when simultaneously driving both MAX526 reference inputs at 10V. Improve accuracy by driving VREFAB and VREFCD separately or by using a reference with excellent accuracy and superior load regulation, such as the MAX676/MAX677/MAX678.

Using an op amp to buffer the reference is another way to obtain high accuracy. The closed-loop output impedance of the op amp should be kept below  $0.05\Omega$ . This ensures errors of less than 0.08LSB when driving both reference inputs simultaneously. The MAX400 or OP07 are suitable for this application. The input capacitance at VREF is also code dependent and typically varies from 125pF to 300pF.

VOUTA-D are represented by a digitally programmable voltage source as:

Vout = (NB x VREF) / 4096

where N<sub>B</sub> is the numeric value of the DAC's binary input code (0 to 4095).

### **Output Buffer Amplifiers**

All MAX526/MAX527 voltage outputs are internally buffered by precision unity-gain followers with a typical slew rate of  $5V/\mu s$  for the MAX526 and  $3V/\mu s$  for the MAX527.

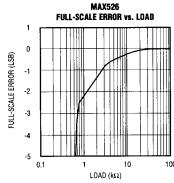

With a full-scale transition at the MAX526 output (0V to  $\pm 10V$  or  $\pm 10V$  to 0V), the typical settling time to  $\pm 1/2 LSB$  is  $3\mu s$  when loaded with  $5k\Omega$  in parallel with 100pF (loads less than  $5k\Omega$  degrade performance). Typical output dynamic response and settling performance of the MAX526 output amplifier are shown in the Typical Operating Characteristics section.

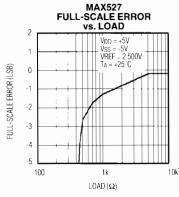

With a full-scale transition at the MAX527 output (0V to +2.5V or +2.5V to 0V), the typical settling time to  $\pm 1/2 LSB$  is 5µs when loaded with 5k $\Omega$  in parallel with 100pF (loads less than 5k $\Omega$  degrade performance). Typical output dynamic response and settling performance of the MAX527 output amplifiers are shown in the Typical Operating Characteristics section.

### Digital Inputs and Interface Logic

Digital inputs are compatible with both TTL and 5V CMOS logic. The MAX526/MAX527 interface with microprocessors using an 8-bit-wide data bus. The double-buffered input structure consists of a 12-bit (8 + 4) input register and a 12-bit DAC register for each of the four DACs.

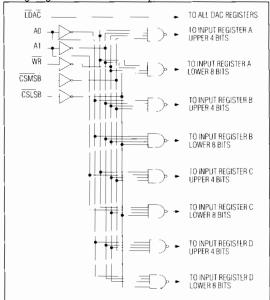

Each DAC's analog output reflects the data held in its DAC register. Address lines A0 and A1 select which DAC receives data from the data bus, as shown in Table 1. All MAX526/MAX527 control inputs are level-triggered. Figure 2 shows the MAX526/MAX527 input control logic.

Table 1. DAC Addressing

| A1 | A0 | SELECTED INPUT REGISTER |   |

|----|----|-------------------------|---|

| L  | L  | DAC A Input Register    |   |

| L  | Н  | DAC B Input Register    |   |

| Н  | L  | DAC C Input Register    | _ |

| Н  | Н  | DAC D Input Register    | _ |

CSMSB, CSLSB, and WR load from the data bus to the input register selected by A0 and A1. Pulling CSLSB and WR low loads the lower 8 bits of the input register, while CSMSB and WR load the upper 4 bits. The order in which the data is loaded into the input register (i.e. upper 4 bits first or lower 8 bits first) is not important. It is possible to concurrently load the full 12 bits of the input register by pulling CSLSB, CSMSB, and WR low. Note that the same data will be written to the 4MSBs (D11-D8) and the 4LSBs (D3-D0), respectively. If the DACs are configured in the unipolar output mode (see Figure 5 and Table 3), this method can be used to quickly zero the DAC outputs.

Data is latched into the selected input register on the rising edge of  $\overline{WR}$ . Alternatively, data will be latched into

Figure 2. Input Control Logic

### Table 2. Write-Cycle Truth Table

| CSLSB | CSMSB | WR | LDAC | FUNCTION                                                                                                                                                                 |  |  |  |

|-------|-------|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| L_    | н     | L  | Н    | Loads LS byte into selected input register                                                                                                                               |  |  |  |

| L     | _ н   |    | Н    | Latches LS byte into selected input register                                                                                                                             |  |  |  |

|       | Н     | L  | Н    | Latches LS byte into selected input register                                                                                                                             |  |  |  |

| H     | L     | L  | Н    | Loads MS nibble into selected input register                                                                                                                             |  |  |  |

| Н     | L     |    | Н    | Latches MS nibble into selected input register                                                                                                                           |  |  |  |

| Н     |       | L  | Н    | Latches MS nibble into selected input register                                                                                                                           |  |  |  |

| X     | Х     | Н  | L    | Transfers data from input registers into DAC registers. DAC outputs reflect data held in their respective input registers                                                |  |  |  |

| X     | X     | Н  |      | Latches the four DAC registers. Input registers cannot be written to.                                                                                                    |  |  |  |

| Н     | L     | L  | L    | Loads MS nibble into selected input register and loads input registers into DAC registers.                                                                               |  |  |  |

|       | X     | Н  | Н    | No operation. Device is not selected.                                                                                                                                    |  |  |  |

| L     | L     | L  | L    | Loads all 12 bits of selected input register. Transfers data from input registers into DAC registers. DAC outputs reflect data held in their respective input registers. |  |  |  |

| L     | L     | L  | Н    | Loads all 12 bits into selected input register.                                                                                                                          |  |  |  |

| L     | Н     | L  | L    | Loads LS byte into selected input register. Transfers data from input registers into DAC registers. DAC outputs reflect data held in their respective input registers.   |  |  |  |

| Н     | Н     | L  | L    | Transfers data from input registers into DAC registers. DAC outputs reflect data held in their respective input registers.                                               |  |  |  |

| Н     | Н     | L  | Н    | No operation                                                                                                                                                             |  |  |  |

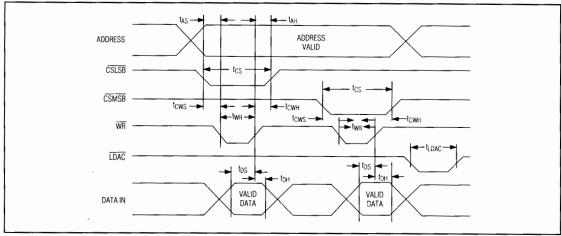

Figure 3. Write-Cycle Timing

the lower 8 bits of the input register on the rising edge of  $\overline{\text{CSLSB}}$ , and the upper 4 bits will be latched on the rising edge of  $\overline{\text{CSMSB}}$ .

Data is transferred from all input registers to the DAC registers by pulling  $\overline{\text{LDAC}}$  low. This simultaneously updates all four DACs. Since  $\overline{\text{LDAC}}$  is asynchronous with respect to  $\overline{\text{WR}}$ , be sure that incorrect data is not latched to the output. Table 2 shows the truth table for operation of  $\overline{\text{WR}}$ ,  $\overline{\text{LDAC}}$ ,  $\overline{\text{CSLSB}}$ , and  $\overline{\text{CSMSB}}$ . Figure 3 shows the MAX526 /MAX527write-cycle timing.

# Application Information Ground Management

Digital or AC transient signals between AGND and DGND can create noise at the analog outputs. It is recommended that AGND and DGND be tied together at the DAC and that this point be tied to the highest quality ground available. If separate ground buses are used, two clamp diodes (1N914 or equivalent) should be connected in inverse parallel between AGND and DGND. This will ensure that the two ground pins always remain within one diode drop of each other.

Careful PCB ground layout minimizes crosstalk between DAC outputs, reference inputs, and digital inputs. Figure 4 shows a suggested circuit-board layout for minimizing crosstalk.

### **Unipolar Output**

In unipolar operation, the output voltages and the reference inputs are the same polarity. Figure 5 shows the MAX526/MAX527 unipolar output circuit. The unipolar output codes are listed in Table 3.

Table 3. Unipolar Code Table

|           | •           |                                                         |

|-----------|-------------|---------------------------------------------------------|

| DAC CONT  | ENTS<br>LSB | ANALOG OUTPUT                                           |

| 1111 1111 | 1111        | +VREF $\left(\frac{4095}{4096}\right)$                  |

| 1000 0000 | 0001        | $+VREF\left(\frac{2049}{4096}\right)$                   |

| 1000 0000 | ) 0000      | $+VREF\left(\frac{2048}{4096}\right) = \frac{+VREF}{2}$ |

| 0111 1111 | 1111        | +VREF $\left(\frac{2047}{4096}\right)$                  |

| 0000 0000 | 0001        | $+VREF\left(\frac{1}{4096}\right)$                      |

| 0000 0000 | 0000        | ov`′                                                    |

Figure 4. Suggested PCB Layout for Minimizing Crosstalk

Figure 5. Unipolar Output Circuit

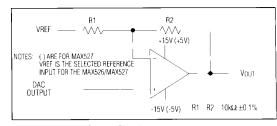

### **Bipolar Output**

The MAX526/MAX527 outputs may be configured for bipolar output operation using Figure 6's circuit. One op amp and two resistors are required per channel. With R1=R2:

$$VOUT = VREF ((2NB / 4096) - 1)$$

where NB is the numeric value of the DAC's binary input code

Table 4 shows the digital code vs. output voltage for the circuit in Figure 6.

ノレノノメノノレ

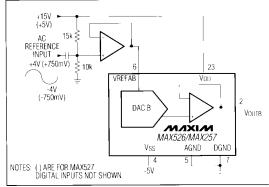

### Using an AC Reference

In applications where VREF has AC signal components, the MAX526/MAX527 have multiplying capability within the VREF input range specifications. Figure 7 shows a technique for applying a sine wave signal to the reference input where the AC signal is offset before being applied to VREF. Note that VREF must never be more negative than DGND.

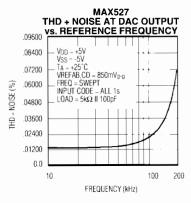

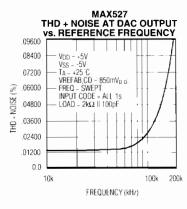

Total harmonic distortion plus noise (THD + N) of the MAX526 is typically less than 0.012% with input frequencies up to 35kHz for 5V<sub>p-p</sub> swing; up to 50kHz for 2V swing. The typical -3dB frequency is 700kHz, as shown in the *Typical Operating Characteristics* graphs.

For the MAX527, THD + N is typically less than 0.024% with input frequencies up to 100kHz, a signal amplitude of 850mV, and a load of 5k $\Omega$  in parallel with 100pF. With a 2k $\Omega$  load in parallel with 100pF, the MAX527's THD is below 0.024% for input frequencies up to 95kHz.

Table 4. Bipolar Code Table

| DAC CO  | NTENTS<br>LSB | ANALOG OUTPUT                                                                |

|---------|---------------|------------------------------------------------------------------------------|

| 1111 1  | 111 1111      | $+VREF\left(\frac{2047}{2048}\right)$                                        |

| 1000 00 | 000 0001      | +VREF $\left(\frac{1}{2048}\right)$                                          |

| 1000 00 | 0000 0000     | ov ,                                                                         |

| 0111 1  | 111 1111      | -VREF $\left(\frac{1}{2048}\right)$                                          |

| 0000 00 | 000 0001      | $ -VREF\left(\frac{1}{2048}\right) $ $ -VREF\left(\frac{2047}{2048}\right) $ |

| 0000 00 | 0000 0000     | $-VREF\left(\frac{2048}{2048}\right) = -VREF$                                |

|         |               |                                                                              |

NOTE:

$$1LSB = (VREF) \left( \frac{1}{4096} \right)$$

Figure 6. Bipolar Output Circuit

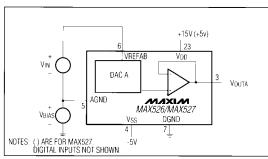

### Offsetting AGND

AGND can be biased above DGND to provide an arbitrary nonzero output voltage for a "0" input code. This application is shown in Figure 8. The output voltage at VOUTA is:

where N<sub>B</sub> is the numeric value of the DAC's binary input code. Since AGND is common to all four DACs, all outputs will be offset by V<sub>BIAS</sub> in the same manner. Note that AGND should not be biased more negative than DGND

Figure 7. AC Reference Input Circuit

### **Supply Voltage and Decoupling**

For full MAX526 performance, VDD should be 4V higher than VREF in the 10.8V to 16.5V range. When using the MAX527, VDD should be at least 2.2V higher than VREF in the 4.75V to 5.5V range. Both VDD and VSS supplies should be bypassed with a  $4.7\mu F$  capacitor in parallel with a  $0.1\mu F$  capacitor to AGND, with short lead lengths as close to the supply pins as possible.

Figure 8. AGND Bias Circuit

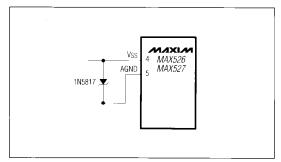

### **Power-Supply Sequencing**

On power-up, Vss should come up first, VDD next, followed by VREFAB or VREFCD. If supply sequencing is not possible, tie an external Schottky diode between Vss and AGND as shown in Figure 9.

Figure 9. When  $V_{SS}$  and  $V_{DD}$  cannot be sequenced, tie a Schottky diode between  $V_{SS}$  and AGND.

### \_Ordering Information (continued)

| Chip Topograp | hy | gra | og | <sup>r</sup> op | 7 | ip | Ch |  |

|---------------|----|-----|----|-----------------|---|----|----|--|

|---------------|----|-----|----|-----------------|---|----|----|--|

| PART       | TEMP.    | RANGE  | PIN-PACKAGE            | INL<br>(LSBs) |

|------------|----------|--------|------------------------|---------------|

| MAX527CCNG | 0°C to   | +70°C  | 24 Narrow Plastic DIP  | ± 1/2         |

| MAX527DCNG | 0°C to   | +70°C  | 24 Narrow Plastic DIP  | ±1            |

| MAX527CCWG | 0°C to   | +70°C  | 24 Wide SO             | ± 1/2         |

| MAX527DCWG | 0°C to   | +70°C  | 24 Wide SO             | ±1            |

| MAX527DC/D | 0°C to   | +70°C  | Dice*                  | ±1            |

| MAX527CENG | -40°C to | +85°C  | 24 Narrow Plastic DIP  | ±1/2          |

| MAX527DENG | -40°C to | +85°C  | 24 Narrow Plastic DIP  | ±1            |

| MAX527CEWG | -40°C to | +85°C  | 24 Wide SO             | ± 1/2         |

| MAX527DEWG | -40°C to | +85°C  | 24 Wide SO             | ±1            |

| MAX527CMYG | -55°C to | +125°C | 24 Narrow Ceramic SB** | ± 1/2         |

| MAX527DMYG | -55°C to | +125°C | 24 Narrow Ceramic SB** | ±1            |

|            |          |        |                        |               |

<sup>\*</sup> Contact factory for dice specifications.

<sup>\*\*</sup> Contact factory for availability and processing to MIL-STD-883.

SUBSTRATE CONNECTS TO V<sub>DD</sub>: TRANSISTOR COUNT: 2720.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

16 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1995 Maxim Integrated Products

Printed USA

MAXIM is a registered trademark of Maxim Integrated Products.