## Serial Input, 14-Bit/16-Bit DAC

AD7849

#### **FEATURES**

14-bit/16-bit multiplying DAC

Guaranteed monotonicity

Output control on power-up and power-down internal or external control

Versatile serial interface

DAC clears to 0 V in both unipolar and bipolar output ranges

#### **APPLICATIONS**

Industrial process controls PC analog I/O boards Instrumentation

#### **GENERAL DESCRIPTION**

The AD7849 is a 14-bit/16-bit serial input multiplying digital-to-analog converter (DAC). The DAC architecture ensures excellent differential linearity performance, and monotonicity is guaranteed to 14 bits for the A grade and to 16 bits for all other grades over the specified temperature ranges.

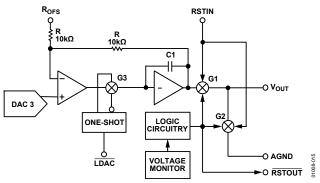

During power-up and power-down sequences (when the supply voltages are changing), the  $V_{\text{OUT}}$  pin is clamped to 0 V via a low impedance path. To prevent the output of A3 from being shorted to 0 V during this time, Transmission Gate G1 is also opened. These conditions are maintained until the power supplies stabilize, and a valid word is written to the DAC register. At this time, G2 opens and G1 closes. Both transmission gates are also externally controllable via the reset in (RSTIN) control input. For instance, if the RSTIN input is driven from a battery supervisor chip, then at power-off or during a brown out, the RSTIN input is driven low to open G1 and close G2. The DAC must be reloaded, with RSTIN high, to reenable the output. Conversely, the on-chip voltage detector output (RSTOUT) is also available to the user to control other parts of the system.

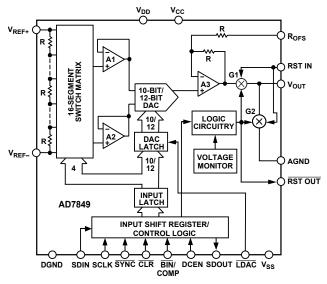

#### **FUNCTIONAL BLOCK DIAGRAM**

Fiaure 1.

The AD7849 has a versatile serial interface structure and can be controlled over three lines to facilitate opto-isolator applications. SDOUT is the output of the on-chip shift register and can be used in a daisy-chain fashion to program devices in the multichannel system. The daisy-chain enable (DCEN) input controls this function.

The  $\overline{\text{BIN}}/\text{COMP}$  pin sets the DAC coding; with  $\overline{\text{BIN}}/\text{COMP}$  set to 0, the coding is straight binary; and with  $\overline{\text{BIN}}/\text{COMP}$  set to 1, the coding is twos complement. This allows the user to reset the DAC to 0 V in both the unipolar and bipolar output ranges.

The part is available in a 20-lead PDIP package and a 20-lead SOIC package.

## **TABLE OF CONTENTS**

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| Functional Block Diagram                    |   |

| General Description                         |   |

| Revision History                            | 2 |

| Specifications                              | 3 |

| Reset Specifications                        | 4 |

| AC Performance Characteristics              | 5 |

| Timing Characteristics                      | 5 |

| Absolute Maximum Ratings                    | 6 |

| ESD Caution                                 | 6 |

| Pin Configuration and Function Descriptions | 7 |

| Typical Performance Characteristics |    |

|-------------------------------------|----|

| Terminology                         | 10 |

| Circuit Description                 | 11 |

| Digital-to-Analog Conversion        | 11 |

| Digital Interface                   | 12 |

| Applying the AD7849                 | 13 |

| Microprocessor Interfacing          | 15 |

| Applications Information            | 17 |

| Opto-Isolated Interface             | 17 |

| Outline Dimensions                  | 18 |

| Ordering Guide                      | 19 |

#### **REVISION HISTORY**

| 3/11—Rev. B to Rev. C                       |               |

|---------------------------------------------|---------------|

| Deleted 20-Lead CERDIP (Q-20) Package and   |               |

| T Version                                   | Universal     |

| Updated Format                              | Universal     |

| Deleted AD7849-to-ADSP-2101/ADSP-2102 Inter | rface Section |

| and Figure 20; Renumbered Sequentially      | 12            |

## **SPECIFICATIONS**

$V_{DD} = 14.25 \text{ V to } 15.75 \text{ V; } V_{SS} = -14.25 \text{ V to } -15.75 \text{ V; } V_{CC} = 4.75 \text{ V to } 5.25 \text{ V; } V_{OUT} \text{ loaded with } 2 \text{ k}\Omega, 200 \text{ pF to } 0 \text{ V; } V_{REF+} = 5 \text{ V; } R_{OFS} \text{ connected to } 0 \text{ V; } T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } T_{MAX} \text{ respectively } T_{MAX}$

Table 1.

| Parameter                                   | A Version                               | B Version                               | C Version                            | Unit               | Test Conditions/Comments                                                                                                               |

|---------------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| RESOLUTION                                  | 14                                      | 16                                      | 16                                   | Bits               | A version: 1 LSB = 2 ( $V_{REF+} - V_{REF-}$ )/2 <sup>14</sup> ;<br>B, C versions: 1 LSB = 2 ( $V_{REF+} - V_{REF-}$ )/2 <sup>16</sup> |

| UNIPOLAR OUTPUT                             |                                         |                                         |                                      |                    | $V_{REF-} = 0 \text{ V}, V_{OUT} = 0 \text{ V to } 10 \text{ V}$                                                                       |

| Relative Accuracy at 25°C                   | ±4                                      | ±6                                      | ±4                                   | LSB typ            |                                                                                                                                        |

| T <sub>MIN</sub> to T <sub>MAX</sub>        | ±5                                      | ±16                                     | ±8                                   | LSB max            |                                                                                                                                        |

| Differential Nonlinearity                   | ±0.25                                   | ±0.9                                    | ±0.5                                 | LSB max            | All grades guaranteed monotonic over temperature                                                                                       |

| Gain Error at 25°C                          | ±1                                      | ±4                                      | ±4                                   | LSB typ            | $V_{OUT}$ load = 10 M $\Omega$                                                                                                         |

| T <sub>MIN</sub> to T <sub>MAX</sub>        | ±4                                      | ±16                                     | ±16                                  | LSB max            |                                                                                                                                        |

| Offset Error at 25°C                        | ±1                                      | ±4                                      | ±4                                   | LSB typ            |                                                                                                                                        |

| T <sub>MIN</sub> to T <sub>MAX</sub>        | ±6                                      | ±24                                     | ±16                                  | LSB max            |                                                                                                                                        |

| Gain Temperature Coefficient <sup>1</sup>   | ±2                                      | ±2                                      | ±2                                   | ppm FSR/<br>°C typ |                                                                                                                                        |

| Offset Temperature Coefficient <sup>1</sup> | ±2                                      | ±2                                      | ±2                                   | ppm FSR/<br>°C typ |                                                                                                                                        |

| BIPOLAR OUTPUT                              |                                         |                                         |                                      |                    | $V_{REF-} = 5 \text{ V}, V_{OUT} = -10 \text{ V} \text{ to } +10 \text{ V}$                                                            |

| Relative Accuracy at 25°C                   | ±2                                      | ±3                                      | ±2                                   | LSB typ            |                                                                                                                                        |

| T <sub>MIN</sub> to T <sub>MAX</sub>        | ±3                                      | ±8                                      | ±4                                   | LSB max            |                                                                                                                                        |

| Differential Nonlinearity                   | ±0.25                                   | ±0.9                                    | ±0.5                                 | LSB max            | All grades guaranteed monotonic over temperature                                                                                       |

| Gain Error at 25°C                          | ±1                                      | ±4                                      | ±4                                   | LSB typ            | $V_{OUT}$ load = 10 M $\Omega$                                                                                                         |

| T <sub>MIN</sub> to T <sub>MAX</sub>        | ±4                                      | ±16                                     | ±16                                  | LSB max            |                                                                                                                                        |

| Offset Error at 25°C                        | ±0.5                                    | ±2                                      | ±2                                   | LSB typ            |                                                                                                                                        |

| T <sub>MIN</sub> to T <sub>MAX</sub>        | ±3                                      | ±12                                     | ±8                                   | LSB max            |                                                                                                                                        |

| Bipolar Zero Error at 25°C                  | ±0.5                                    | ±2                                      | ±2                                   | LSB typ            |                                                                                                                                        |

| T <sub>MIN</sub> to T <sub>MAX</sub>        | ±4                                      | ±12                                     | ±8                                   | LSB max            |                                                                                                                                        |

| Gain Temperature Coefficient <sup>1</sup>   | ±2                                      | ±2                                      | ±2                                   | ppm FSR/<br>°C typ |                                                                                                                                        |

| Offset Temperature Coefficient <sup>1</sup> | ±2                                      | ±2                                      | ±2                                   | ppm FSR/<br>°C typ |                                                                                                                                        |

| Bipolar Zero Temperature<br>Coefficient 1   | ±2                                      | ±2                                      | ±2                                   | ppm FSR/<br>°C typ |                                                                                                                                        |

| REFERENCE INPUT                             |                                         |                                         |                                      |                    |                                                                                                                                        |

| Input Resistance                            | 25                                      | 25                                      | 25                                   | kΩ min             | Resistance from V <sub>REF+</sub> to V <sub>REF-</sub>                                                                                 |

|                                             | 43                                      | 43                                      | 43                                   | kΩ max             | Typically 34 kΩ                                                                                                                        |

| V <sub>REF+</sub> Range                     | $V_{SS} + 6$ to $V_{DD} - 6$            | $V_{SS} + 6$ to $V_{DD} - 6$            | $V_{SS} + 6$ to $V_{DD} - 6$         | V                  |                                                                                                                                        |

| V <sub>REF</sub> _ Range                    | $V_{SS} + 6$ to $V_{DD} - 6$            | $V_{SS} + 6$ to $V_{DD} - 6$            | $V_{SS} + 6$ to $V_{DD} - 6$         | V                  |                                                                                                                                        |

| OUTPUT CHARACTERISTICS                      |                                         |                                         |                                      |                    |                                                                                                                                        |

| Output Voltage Swing                        | $V_{SS} + 4 \text{ to}$<br>$V_{DD} - 4$ | $V_{SS} + 4 \text{ to}$<br>$V_{DD} - 4$ | $V_{SS} + 4 \text{ to}$ $V_{DD} - 4$ | V max              |                                                                                                                                        |

| Resistive Load                              | 2                                       | 2                                       | 2                                    | kΩ min             | To 0 V                                                                                                                                 |

| Capacitive Load                             | 200                                     | 200                                     | 200                                  | pF max             | To 0 V                                                                                                                                 |

| Output Resistance                           | 0.3                                     | 0.3                                     | 0.3                                  | Ω typ              |                                                                                                                                        |

| Short-Circuit Current                       | ±25                                     | ±25                                     | ±25                                  | mA typ             | Voltage range: -10 V to +10 V                                                                                                          |

| Parameter                             | A Version     | B Version     | C Version     | Unit        | Test Conditions/Comments                                           |

|---------------------------------------|---------------|---------------|---------------|-------------|--------------------------------------------------------------------|

| DIGITAL INPUTS                        |               |               |               |             |                                                                    |

| Input High Voltage, V <sub>INH</sub>  | 2.4           | 2.4           | 2.4           | V min       |                                                                    |

| Input Low Voltage, V <sub>INL</sub>   | 0.8           | 0.8           | 0.8           | V max       |                                                                    |

| Input Current, I <sub>INH</sub>       | ±10           | ±10           | ±10           | μA max      |                                                                    |

| Input Capacitance, C <sub>IN</sub>    | 10            | 10            | 10            | pF max      |                                                                    |

| DIGITAL OUTPUTS                       |               |               |               |             |                                                                    |

| Output Low Voltage, Vo∟               | 0.4           | 0.4           | 0.4           | V max       | I <sub>SINK</sub> = 1.6 mA                                         |

| Output High Voltage, V <sub>он</sub>  | 4.0           | 4.0           | 4.0           | V min       | $I_{SOURCE} = 400 \mu A$                                           |

| Floating State Leakage Current        | ±10           | ±10           | ±10           | μA max      |                                                                    |

| Floating State Output                 | 10            | 10            | 10            | pF max      |                                                                    |

| Capacitance                           |               |               |               |             |                                                                    |

| POWER REQUIREMENTS <sup>2</sup>       |               |               |               |             |                                                                    |

| $V_{DD}$                              | 14.25/15.75   | 14.25/15.75   | 14.25/15.75   | V min/V max |                                                                    |

| $V_{SS}$                              | -14.25/-15.75 | -14.25/-15.75 | -14.25/-15.75 | V min/V max |                                                                    |

| V <sub>CC</sub>                       | 4.75/5.25     | 4.75/5.25     | 4.75/5.25     | V min/V max |                                                                    |

| $I_{DD}$                              | 5             | 5             | 5             | mA max      | $V_{OUT}$ unloaded, $V_{INH} = V_{DD} - 0.1 V$ , $V_{INL} = 0.1 V$ |

| I <sub>SS</sub>                       | 5             | 5             | 5             | mA max      | $V_{OUT}$ unloaded, $V_{INH} = V_{DD} - 0.1 V$ , $V_{INL} = 0.1 V$ |

| Icc                                   | 2.5           | 2.5           | 2.5           | mA max      | $V_{INH} = V_{DD} - 0.1 \text{ V}, V_{INL} = 0.1 \text{ V}$        |

| Power Supply Sensitivity <sup>3</sup> | 0.4           | 1.5           | 1.5           | LSB/V max   |                                                                    |

| Power Dissipation                     | 100           | 100           | 100           | mW typ      | V <sub>OUT</sub> unloaded                                          |

#### **RESET SPECIFICATIONS**

These specifications apply when the device goes into reset mode during power-up or power-down sequence.  $V_{\text{OUT}}$  unloaded.

Table 2.

| Parameter                                                                                 | All Versions | Unit   | Test Conditions/Comments                                                                          |

|-------------------------------------------------------------------------------------------|--------------|--------|---------------------------------------------------------------------------------------------------|

| V <sub>A</sub> , <sup>1</sup> Low Threshold Voltage for V <sub>DD</sub> , V <sub>SS</sub> | 1.2          | V max  | This is the lower $V_{DD}/V_{SS}$ threshold voltage for the reset function.                       |

|                                                                                           | 0            | V typ  | Above this, the reset is activated.                                                               |

| $V_B$ , High Threshold Voltage for $V_{DD}$ , $V_{SS}$                                    | 9.5          | V max  | This is the higher V <sub>DD</sub> /V <sub>SS</sub> threshold voltage for the reset function.     |

|                                                                                           | 6.4          | V min  | Below this, the reset is activated. Typically, 8 V.                                               |

| $V_C$ , Low Threshold Voltage for $V_{CC}$                                                | 1            | V max  | This is the lower $V_{CC}$ threshold voltage for the reset function.                              |

|                                                                                           | 0            | V typ  | Above this, the reset is activated.                                                               |

| $V_D$ , High Threshold Voltage for $V_{CC}$                                               | 4            | V max  | This is the higher $V_{CC}$ threshold voltage for the reset function.                             |

|                                                                                           | 2.5          | V min  | Below this, the reset is activated. Typically, 3 V.                                               |

| G2 Ron                                                                                    | 1            | kΩ typ | On resistance of G2; $V_{DD} = 2 \text{ V}$ ; $V_{SS} = -2 \text{ V}$ ; $I_{G2} = 1 \text{ mA}$ . |

$<sup>^1</sup>$  A pull-down resistor (65 k $\!\Omega\!$ ) on  $V_{OUT}$  maintains 0 V output when  $V_{DD}/V_{SS}$  is below  $V_A.$

$<sup>^1</sup>$  Guaranteed by design and characterization, not production tested.  $^2$  The AD7849 is functional with power supplies of  $\pm 12$  V. See the Typical Performance Characteristics section.  $^3$  Sensitivity of gain error, offset error, and bipolar zero error to  $V_{DD}$ ,  $V_{SS}$  variations.

#### **AC PERFORMANCE CHARACTERISTICS**

These characteristics are included for design guidance and are no subject to test.  $V_{REF+} = 5 \text{ V}$ ;  $V_{DD} = 14.25 \text{ V}$  to 15.75 V;  $V_{SS} = -14.25 \text{ V}$  to -15.75 V;  $V_{CC} = 4.75 \text{ V}$  to 5.25 V;  $R_{OFS}$  connected to 0 V.

Table 3.

| Parameter                                      | A, B, C Versions | Unit       | Test Conditions/Comments                                                                                                        |

|------------------------------------------------|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                            |                  |            |                                                                                                                                 |

| Output Settling Time <sup>1</sup>              | 7                | μs typ     | To $0.006\%$ FSR. $V_{OUT}$ loaded. $V_{REF-} = 0$ V.                                                                           |

|                                                | 10               | μs typ     | To 0.003% FSR. $V_{OUT}$ loaded. $V_{REF-} = -5 \text{ V}$ .                                                                    |

| Slew Rate                                      | 4                | V/μs typ   |                                                                                                                                 |

| Digital-to-Analog Glitch Impulse               | 250              | nV-sec typ | DAC alternatively loaded with 00 00 and $\frac{111}{\text{BIN/COMP}}$ set to 1. $\text{V}_{\text{REF}} = -5 \text{ V}$ .        |

|                                                | 150              | nV-sec typ | LDAC frequency = 100 kHz.                                                                                                       |

| AC Feedthrough                                 | 1                | mV p-p typ | $V_{REF-} = 0 \text{ V}$ , $V_{REF+} = 1 \text{ V rm}$ , $10 \text{ kHz}$ sine wave. DAC loaded with all 0s. BIN/COMP set to 0. |

| Digital Feedthrough                            | 5                | nV-sec typ | DAC alternatively loaded with all 1s and 0s. SYNC high.                                                                         |

| Output Noise Voltage Density, 1 kHz to 100 kHz | 80               | nV/√Hz typ | Measured at $V_{OUT}$ . $V_{REF+} = V_{REF-} = 0$ V. BIN/COMP set to 0.                                                         |

$<sup>^{1}</sup>$  LDAC = 0. Settling time does not include deglitching time of 5  $\mu$ s (typical).

#### **TIMING CHARACTERISTICS**

$V_{DD}$  = 14.25 V to 15.75 V;  $V_{SS}$  = -14.25 V to -15.75 V;  $V_{CC}$  = 4.75 V to 5.25 V;  $R_L$  = 2 k $\Omega$ ,  $C_L$  = 200 pF. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Guaranteed by characterization. All input signals are specified tr = tf = 5 ns (10% to 90% of 5 V and timed from a voltage level of 1.6 V.

Table 4.

| Parameter                   | Limit at 25°C (All Versions) | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (All Versions) | Unit   | Test Conditions/Comments       |

|-----------------------------|------------------------------|-------------------------------------------------------------|--------|--------------------------------|

| t <sub>1</sub> 1            | 200                          | 200                                                         | ns min | SCLK cycle time                |

| $t_2$                       | 50                           | 50                                                          | ns min | SYNC-to-SCLK setup time        |

| t <sub>3</sub>              | 70                           | 70                                                          | ns min | SYNC-to-SCLK hold time         |

| t <sub>4</sub>              | 10                           | 10                                                          | ns min | Data setup time                |

| <b>t</b> <sub>5</sub>       | 40                           | 40                                                          | ns min | Data hold time                 |

| t <sub>6</sub> <sup>2</sup> | 80                           | 80                                                          | ns max | SCLK falling edge to SDO valid |

| t <sub>7</sub>              | 80                           | 80                                                          | ns min | LDAC, CLR pulse width          |

| $t_r$                       | 30                           | 30                                                          | μs max | Digital input rise time        |

| t <sub>f</sub>              | 30                           | 30                                                          | μs max | Digital input fall time        |

<sup>&</sup>lt;sup>1</sup> SCLK mark/space ratio range is 40/60 to 60/40.

<sup>&</sup>lt;sup>2</sup> SDO load capacitance is 50 pF.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 5.

| Table 5.                                              |                                              |

|-------------------------------------------------------|----------------------------------------------|

| Parameter                                             | Rating                                       |

| V <sub>DD</sub> to DGND                               | -0.4 V to +17 V                              |

| V <sub>CC</sub> to DGND <sup>1</sup>                  | $-0.4 \text{ V, V}_{DD} + 0.4 \text{ V or}$  |

|                                                       | +7 V (whichever is                           |

|                                                       | lower)                                       |

| V <sub>SS</sub> to DGND                               | −0.4 V to −17 V                              |

| V <sub>REF+</sub> to DGND                             | $V_{DD} + 0.4 V$ , $V_{SS} - 0.4 V$          |

| V <sub>REF</sub> - to DGND                            | $V_{DD} + 0.4 V$ , $V_{SS} - 0.4 V$          |

| V <sub>OUT</sub> to DGND <sup>2</sup>                 | $V_{DD} + 0.4 V$ , $V_{SS} - 0.4 V$          |

|                                                       | or ±10 V (whichever is                       |

|                                                       | lower)                                       |

| R <sub>OFS</sub> to DGND                              | $V_{DD} + 0.4 V, V_{SS} - 0.4 V$             |

| Digital Input Voltage to DGND                         | $-0.4 \text{ V}$ to $V_{CC} + 0.4 \text{ V}$ |

| Input Current to any Pin Except Supplies <sup>3</sup> | ±10 mA                                       |

| Operating Temperature Range                           | -40°C to +85°C                               |

| Storage Temperature Range                             | −65°C to +150°C                              |

| Junction Temperature                                  | 150°C                                        |

| 20-Lead PDIP                                          |                                              |

| Power Dissipation                                     | 875 mW                                       |

| $\theta_{JA}$ Thermal Impedance                       | 102°C/W                                      |

| Lead Temperature (Soldering, 10 sec)                  | 260°C                                        |

| 20-Lead SOIC                                          |                                              |

| Power Dissipation                                     | 875 mW                                       |

| θ <sub>JA</sub> Thermal Impedance                     | 74°C/W                                       |

| Lead Temperature, Soldering                           |                                              |

| Vapor Phase (60 sec)                                  | 215°C                                        |

| Infrared (15 sec)                                     | 220°C                                        |

|                                                       |                                              |

$<sup>^1</sup>$  V<sub>CC</sub> must not exceed V<sub>DD</sub> by more than 0.4 V. If it is possible for this to happen during power-up or power-down (for example, if V<sub>CC</sub> is greater than 0.4 V while V<sub>DD</sub> is still 0 V), the following diode protection scheme ensures protection.

$<sup>^2</sup>$  VOUT can be shorted to DGND,  $+\,10$  V,  $-\,10$  V, provided that the power dissipation of the package is not exceeded.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>3</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

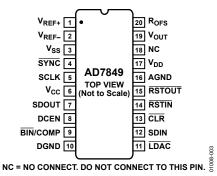

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 6. Pin Function Descriptions**

| Pin No. | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>REF+</sub> | $V_{REF+}$ Input. The DAC is specified for $V_{REF+}$ of 5 V. The DAC is fully multiplying so that the $V_{REF+}$ range is +5 V to -5 V.                                                                                                                                                                                                               |

| 2       | $V_{REF-}$        | $V_{REF-}$ Input. The DAC is specified for $V_{REF-}$ of -5 V. The DAC is fully multiplying so that the $V_{REF-}$ range is -5 V to +5 V.                                                                                                                                                                                                              |

| 3       | Vss               | Negative supply for the analog circuitry. This is nominally –15 V.                                                                                                                                                                                                                                                                                     |

| 4       | SYNC              | Data Synchronization Logic Input. When it goes low, the internal logic is initialized in readiness for a new data-word.                                                                                                                                                                                                                                |

| 5       | SCLK              | Serial Clock Logic Input. Data is clocked into the input register on each SCLK falling edge.                                                                                                                                                                                                                                                           |

| 6       | <b>V</b> cc       | Positive supply for the digital circuitry. This is nominally 5 V.                                                                                                                                                                                                                                                                                      |

| 7       | SDOUT             | Serial Data Output. With DCEN at Logic 1, this output is enabled, and the serial data in the input shift register is clocked out on each rising edge of SCLK.                                                                                                                                                                                          |

| 8       | DCEN              | Daisy-Chain Enable Logic Input. Connect this pin high if a daisy-chain interface is being used; otherwise, this pin must be connected low.                                                                                                                                                                                                             |

| 9       | BIN/COMP          | Logic Input. This input selects the data format to be either binary or twos complement. In the unipolar output range, natural binary format is selected by connecting the input to Logic 0. In the bipolar output range, offset binary is selected by connecting this input to Logic 0, and twos complement is selected by connecting it to a Logic 1. |

| 10      | DGND              | Digital Ground. Ground reference point for the on-chip digital circuitry.                                                                                                                                                                                                                                                                              |

| 11      | LDAC              | Load DAC Logic Input. This input updates the DAC output. The DAC output is updated on the falling edge of this signal, or alternatively, if this input is permanently low, an automatic update mode is selected where the DAC is updated on the 16th falling SCLK edge.                                                                                |

| 12      | SDIN              | Serial Data Input. The 16-bit serial data-word is applied to this input.                                                                                                                                                                                                                                                                               |

| 13      | CLR               | Clear Logic Input. Taking this input low sets V <sub>OUT</sub> to 0 V in both the unipolar output range and the bipolar twos complement output range. It sets V <sub>OUT</sub> to V <sub>REF</sub> in the offset binary bipolar output range.                                                                                                          |

| 14      | RSTIN             | Reset Logic Input. This input allows external access to the internal reset logic. Applying Logic 0 to this input, resets the DAC output to 0 V. In normal operation, it should be tied to Logic 1.                                                                                                                                                     |

| 15      | RSTOUT            | Reset Logic Output. This is the output from the on-chip voltage monitor used in the reset circuit. It can be used to control other system components, if desired.                                                                                                                                                                                      |

| 16      | AGND              | This is the analog ground for the device. It is the point to which the output gets shorted in reset mode.                                                                                                                                                                                                                                              |

| 17      | $V_{DD}$          | Positive Supply for the Analog Circuitry. This is 15 V nominal.                                                                                                                                                                                                                                                                                        |

| 18      | NC                | No Connect. Leave unconnected.                                                                                                                                                                                                                                                                                                                         |

| 19      | V <sub>OUT</sub>  | DAC Output Voltage Pin.                                                                                                                                                                                                                                                                                                                                |

| 20      | Rofs              | Input to Summing Resistor of DAC Output Amplifier. This is used to select the output voltage ranges. Also, see Figure 20 to Figure 23 in the Applying the AD7849 section.                                                                                                                                                                              |

## TYPICAL PERFORMANCE CHARACTERISTICS

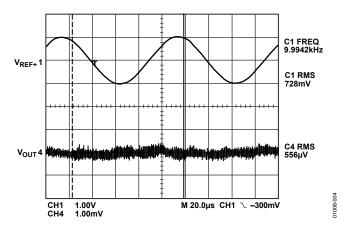

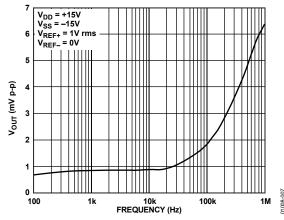

Figure 3. AC Feedthrough

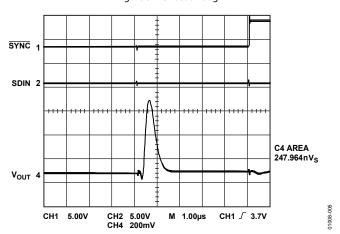

Figure 4. Digital-to-Analog Glitch Impulse Without Internal Deglitcher

Figure 5. Large Signal Frequency Response

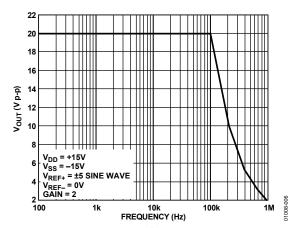

Figure 6. AC Feedthrough vs. Frequency

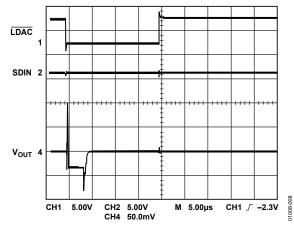

Figure 7. Digital-to-Analog Glitch Impulse With Internal Deglitcher

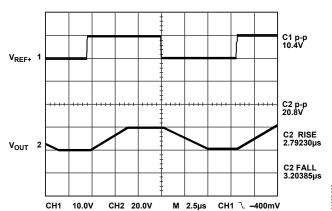

Figure 8. Pulse Response (Large Signal)

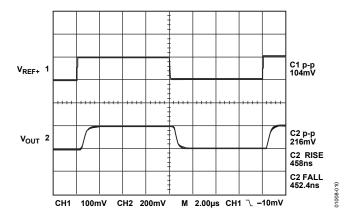

Figure 9. Pulse Response (Small Signal)

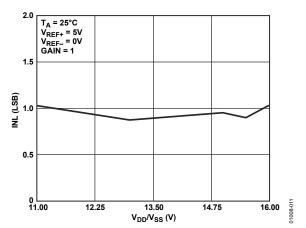

Figure 10. Typical Integral Nonlinearity vs. Supplies

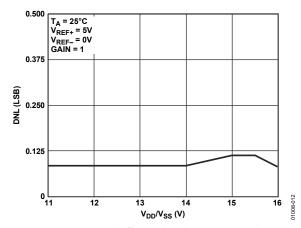

Figure 11. Typical Differential Nonlinearity vs. Supplies

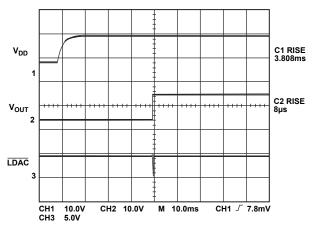

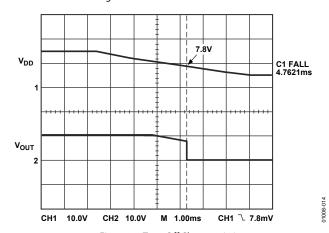

Figure 12. Turn-On Characteristics

Figure 13. Turn-Off Characteristics

### **TERMINOLOGY**

### **Least Significant Bit**

This is the analog weighting of 1 bit of the digital word in a DAC. For the B version and the C versions, 1 LSB =  $(V_{REF+} - V_{REF-})/2^{16}$ . For the A version, 1 LSB =  $(V_{REF+} - V_{REF-})/2^{14}$ .

#### **Relative Accuracy**

Relative accuracy or endpoint nonlinearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for both endpoints (that is, offset and gain errors are adjusted out) and is normally expressed in least significant bits or as a percentage of full-scale range.

#### **Differential Nonlinearity**

Differential nonlinearity is the difference between the measured change and the ideal change between any two adjacent codes. A specified differential nonlinearity of less than  $\pm 1$  LSB over the operating temperature range ensures monotonicity.

#### **Gain Error**

Gain error is a measure of the output error between an ideal DAC and the actual device output with all 1s loaded after offset error has been adjusted out. Gain error is adjustable to zero with an external potentiometer.

#### **Offset Error**

This is the error present at the device output with all 0s loaded in the DAC. It is due to the op amp input offset voltage and bias current and the DAC leakage current.

#### **Bipolar Zero Error**

When the AD7849 is connected for bipolar output and (100 ... 000) is loaded to the DAC, the deviation of the analog output from the ideal midscale of 0 V is called the bipolar zero error.

#### Digital-to-Analog Glitch Impulse

This is the amount of charge injected from the digital inputs to the analog output when the inputs change state. Normally, this is specified as the area of the glitch in nV-secs.

#### **Multiplying Feedthrough Error**

This is an ac error due to capacitive feedthrough from either of the  $V_{\text{REF}}$  terminals to  $V_{\text{OUT}}$  when the DAC is loaded with all 0s.

#### Digital Feedthrough

When the DAC is not selected  $\overline{(\text{SYNC})}$  is held high), high frequency logic activity on the digital inputs is capacitively coupled through the device to show up as noise on the  $V_{\text{OUT}}$  pin. This noise is digital feedthrough.

## **CIRCUIT DESCRIPTION**

#### **DIGITAL-TO-ANALOG CONVERSION**

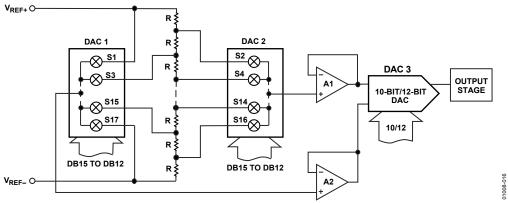

Figure 15 shows the digital-to-analog section of the AD7849. There are three on-chip DACs, each of which has its own buffer amplifier. DAC1 and DAC2 are 4-bit DACs. They share a 16-resistor string, but they have their own analog multiplexers. The voltage reference is applied to the resistor string. DAC3 is a 12-bit voltage mode DAC with its own output stage.

The four MSBs of the 16-bit digital input code drive DAC1 and DAC2, while the 12 LSBs control DAC3. Using DAC1 and DAC2, the MSBs select a pair of adjacent nodes on the resistor string and present that voltage to the positive and negative inputs of DAC3. This DAC interpolates between these two voltages to produce the analog output voltage.

To prevent nonmonotonicity in the DAC due to amplifier offset voltages, DAC1 and DAC2 leap-frog along the resistor string. For example, when switching from Segment 1 to Segment 2, DAC1 switches from the bottom of Segment 1 to the top of Segment 2 while DAC 2 remains connected to the top of Segment 1. The code driving DAC3 is automatically complemented to compensate for the inversion of its inputs. This means that any linearity effects due to amplifier offset voltages remain unchanged when switching from one segment to the next, and 16-bit monotonicity is ensured if DAC3 is monotonic. Therefore, 12-bit resistor matching in DAC3 guarantees overall 16-bit monotonicity. This is much more achievable than the 16-bit matching that a conventional R-2R structure would need.

#### **Output Stage**

The output stage of the AD7849 is shown in Figure 14. It is capable of driving a 2 k $\Omega$  load in parallel with 200 pF. The feedback and offset resistors allow the output stage to be configured for gains of 1 or 2. Additionally, the offset resistor can be used to shift the output range. The AD7849 has a special feature to ensure output stability during power-up and power-down sequences. This feature is available for control applications where actuators must not be allowed to move in an uncontrolled fashion.

Figure 14. Output Stage

When the supply voltages are changing, the V<sub>OUT</sub> pin is clamped to 0 V via a low impedance path. To prevent the output of A3 from being shorted to 0 V during this time, Transmission Gate G1 is opened. These conditions are maintained until the power supplies stabilize, and a valid word is written to the DAC register. At this time, G2 opens and G1 closes. Both transmission gates are also externally controllable via the reset in (RSTIN) control input. For instance, if the RSTIN input is driven from a battery supervisor chip, then at power-off or during a brownout, the RSTIN input will be driven low to open G1 and closeG2. The DAC has to be reloaded, with RSTIN high, to reenable the output. Conversely, the on-chip voltage detector output (RSTOUT) is also available to the user to control other parts of the system.

The AD7849 output buffer is configured as a track-and-hold amplifier. Although normally tracking its input, this amplifier isplaced in hold mode for approximately 5  $\mu s$  after the leading edge of  $\overline{LDAC}$ . This short state keeps the DAC output at its previous voltage while the AD7849 is internally changing to its new value. therefore, any glitches that occur in the transition are not seen at the output. In systems where  $\overline{LDAC}$  is permanently low, deglitching is not in operation.

Figure 15. Digital-to-Analog Conversion

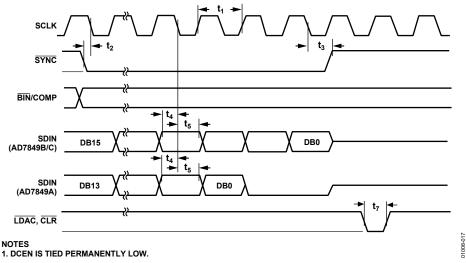

Figure 16. Timing Diagram (Standalone Mode)

#### **DIGITAL INTERFACE**

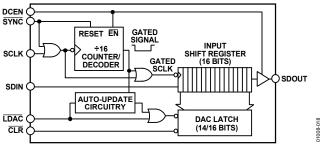

The AD7849 contains an input serial-to-parallel shift register and a DAC latch. A simplified diagram of the input loading circuitry is shown in Figure 16. Serial data on the SDIN input is loaded to the input register under control of DCEN, SYNC and SCLK. When a complete word is held in the shift register, it can then be loaded into the DAC latch under control of LDAC. Only the data in the DAC latch determines the analog output on the AD7849.

The daisy-chain enable (DCEN) input is used to select either the standalone mode or the daisy-chain mode. The loading format is slightly different depending on which mode is selected.

#### Serial Data Loading Format (Standalone Mode)

When DCEN is at Logic 0, standalone mode is selected. In this mode, a low \$\overline{SYNC}\$ input provides the frame synchronization signal that tells the AD7849 that valid serial data on the SDIN input is available for the next 16 falling edges of SCLK. An internal counter/decoder circuit provides a low gating signal so that only 16 data bits are clocked into the input shift register. After 16 SCLK pulses, the internal gating signal goes inactive (high), thus locking out any further clock pulses. Therefore, either a continuous clock or a burst clock source can be used to clock in data.

The  $\overline{\text{SYNC}}$  input is taken high after the complete 16-bit word is loaded in.

The B version and C version are 16-bit resolution DACs and have a straight 16-bit load format, with the MSB (DB15) being loaded first. The A version is a 14-bit DAC; however, the loading structure is still 16 bit. The MSB (DB13) is loaded first, and the final two bits of the 16-bit stream must be 0s.

The DAC latch, and hence the analog output, can be updated in two ways. The status of the LDAC input is examined after SYNC is taken low. Depending on its status, one of two update modes is selected.

If  $\overline{LDAC} = 0$ , then automatic update mode is selected. In this mode, the DAC latch and analog output are updated automatically when the last bit in the serial data stream is clocked in. The update thus takes place on the 16th falling SCLK edge.

If  $\overline{LDAC}=1$ , then automatic update mode is disabled. The DAC latch update and output update are now separate. The DAC latch is updated on the falling edge of  $\overline{LDAC}$ . However, the output update is delayed for a further 5  $\mu$ s by means of an internal track-and-hold amplifier in the output stage. This function results in a lower digital-to-analog glitch impulse at the DAC output. Note that the  $\overline{LDAC}$  input must be taken back high again before the next data transfer is initiated.

Figure 17. Simplified Loading Structure

Figure 18. Timing Diagram (Daisy-Chain Mode)

#### Serial Data Loading Format (Daisy-Chain Mode)

By connecting DCEN high, daisy-chain mode is enabled. This mode of operation is designed for multiDAC systems where several AD7849s can be connected in cascade. In this mode, the internal gating circuitry on SCLK is disabled, and a serial data output facility is enabled. The internal gating signal is permanently active (low) so that the SCLK signal is continuously applied to the input shift register when SYNC is low. The data is clocked into the register on each falling SCLK edge after SYNC goes low. If more than 16 clock pulses are applied, the data ripples out of the shift register and appears on the SDOUT line. By connecting this line to the SDIN input on the next AD7849 in the chain, a multiDAC interface can be constructed. Sixteen SCLK pulses are required for each DAC in the system. Therefore, the total number of clock cycles must equal 16 × N, where N is the total number of devices in the chain. When the serial transfer to all devices is complete, SYNC is taken high, which prevents any further data from being clocked into the input register.

A continuous SCLK source can be used if  $\overline{\text{SYNC}}$  is held low for the correct number of clock cycles. Alternatively, a burst clock containing the exact number of clock cycles can be used and  $\overline{\text{SYNC}}$  taken high some time later.

When the transfer to all input registers is complete, a common  $\overline{\text{LDAC}}$  signal updates all DAC latches with the data in each input register. All analog outputs are therefore updated simultaneously, 5  $\mu$ s after the falling edge of  $\overline{\text{LDAC}}$ .

#### Clear Function (CLR)

The clear function bypasses the input shift register and loads the DAC latch with all 0s. It is activated by taking  $\overline{CLR}$  low. In all ranges, except the offset binary bipolar range (–5 V to +5 V), the output voltage is reset to 0 V. In the offset binary bipolar range, the output is set to  $V_{REF}$ . This clear function is distinct and separate from the automatic power-on reset feature of the device.

#### **APPLYING THE AD7849**

#### **Power Supply Sequencing and Decoupling**

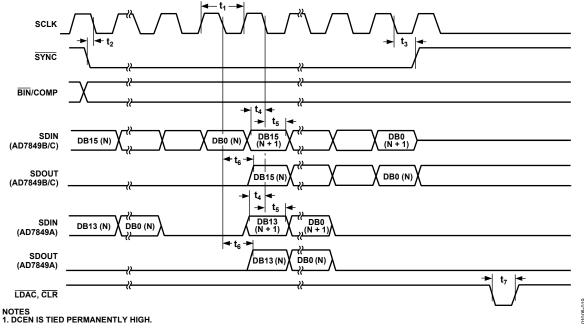

In the AD7849,  $V_{\rm CC}$  should not exceed  $V_{\rm DD}$  by more than 0.4 V. If this happens, then an internal diode is turned on, and it produces latch-up in the device. Care should be taken to employ the following power supply sequence:  $V_{\rm DD}$ ,  $V_{\rm SS}$ , and then  $V_{\rm CC}$ . In systems where it is possible to have an incorrect power sequence (for example, if  $V_{\rm CC}$  is greater than 0.4 V while  $V_{\rm DD}$  is still 0 V), the circuit shown in Figure 19 can be used to ensure that the Absolute Maximum Ratings are not exceeded.

Figure 19. Power Supply Protection

#### **Unipolar Configuration**

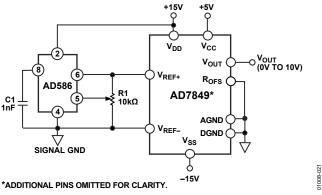

Figure 20 shows the AD7849 in the unipolar binary circuit configuration. The DAC is driven by the AD586, 5 V reference. Because  $R_{\text{OFS}}$  is tied to 0 V, the output amplifier has a gain of  $\times 2$ , and the output range is 0 V to 10 V. If a 0 V to 5 V range is required,  $R_{\text{OFS}}$  should be tied to  $V_{\text{OUT}}$ , configuring the output stage for a gain of  $\times 1$ . Table 7 gives the code table for the circuit shown in Figure 20.

Figure 20. Unipolar Binary Operation

Table 7. Code Table for Figure 20

| Binary Number in DAC Latch |                                   |

|----------------------------|-----------------------------------|

| MSB LSB                    | Analog Output (V <sub>OUT</sub> ) |

| 1111 1111 1111 1111        | 10 (65,535/65,536) V              |

| 1000 0000 0000 0000        | 10 (32,768/65,536) V              |

| 0000 0000 0000 0001        | 10 (1/65,536) V                   |

| 0000 0000 0000 0000        | 0 V                               |

Table 7 assumes a 16-bit resolution; 1 LSB = 10 V/2 $^{16}$  = 10 V/65,536 = 152  $\mu$ V.

Offset and gain can be adjusted in Figure 20 as follows:

- To adjust offset, disconnect the V<sub>REF</sub> input from 0 V, load the DAC with all 0s, and adjust the V<sub>REF</sub> voltage until V<sub>OUT</sub> = 0 V.

- To adjust gain, load the AD7849 with all 1s and adjust R1 until V<sub>OUT</sub> = 10 (65,535/65,536) = 9.9998474 V for the 16-bit, B and C versions. For the 14-bit A version, V<sub>OUT</sub> should be 10 (16,383/16,384) = 9.9993896 V.

If a simple resistor divider is used to vary the  $V_{REF-}$  voltage, it is important that the temperature coefficients of these resistors match that of the DAC input resistance (–300 ppm/°C). Otherwise, extra offset errors will be introduced over temperature. Many circuits do not require these offset and gain adjustments. In these circuits, R1 can be omitted. Pin 5 of the AD586 may be left open circuit, and Pin 2 ( $V_{REF-}$ ) of the AD7849 tied to 0 V.

#### **Bipolar Configuration**

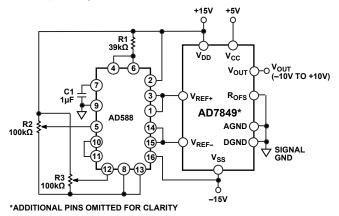

Figure 21 shows the AD7849 set up for  $\pm 10$  V bipolar operation. The AD588 provides precision  $\pm 5$  V tracking outputs that are fed to the V<sub>REF+</sub> and V<sub>REF-</sub> inputs of the AD7849.The code table for the circuit shown in Figure 21 is shown in Table 8.

Full-scale and bipolar-zero adjustment are provided by varying the gain and balance on the AD588. R2 varies the gain on the AD588, while R3 adjusts the +5 V and -5 V outputs together with respect to ground.

Figure 21. Bipolar ±10 V Operation

**Table 8. Code Table for Figure 21**

| <b>Binary Number in DAC Latch</b> |     |                       |

|-----------------------------------|-----|-----------------------|

| MSB                               | LSB | Analog Output (Vout)  |

| 1111 1111 1111 1111               |     | +10 (32,767/32,768) V |

| 1000 0000 0000 0001               |     | +10 (1/32,768) V      |

| 1000 0000 0000 0001               |     | ov                    |

| 0111 1111 1111 1111               |     | -10 (1/32,768) V      |

| 0000 0000 0000 0000               |     | -10 (32,768/32,768) V |

Table 8 assumes a 16-bit resolution; 1 LSB =  $20 \text{ V}/2^{16} = 305 \text{ }\mu\text{V}$ .

For bipolar-zero adjustment on the AD7849, load the DAC with 100 ... 000 and adjust R3 until  $V_{\text{OUT}}$  = 0 V. Full scale is adjusted by loading the DAC with all 1s and adjusting R2 until  $V_{\text{OUT}}$  = 9.999694 V.

When bipolar-zero and full-scale adjustment are not needed, omit R2 and R3, connect Pin 11 to Pin 12 on the AD588 and leave Pin 5 on the AD588 floating.

If a  $\pm 5$  V output range is desired with the circuit shown in Figure 21, tie Pin 20 ( $R_{OFS}$ ) to Pin 19 ( $V_{OUT}$ ), thus reducing the output gain stage to unity and giving an output range of  $\pm 5$  V.

#### **Other Output Voltage Ranges**

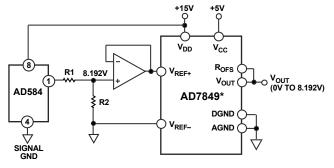

In some cases, users may require output voltage ranges other than those already mentioned. One example is systems that need the output voltage to be a whole number of millivolts (that is,1 mV or 2 mV). If the circuit shown in Figure 22 is used, then the LSB size is 125  $\mu$ V. This makes it possible to program whole millivolt values at the output. Table 9 shows the code table for the circuit shown in Figure 22.

\*ADDITIONAL PINS OMITTED FOR CLARITY.

Figure 22.0 V to 8.192 V Output Range

Table 9. Code Table for Figure 22

| Binary Number in DAC Latch |                                    |

|----------------------------|------------------------------------|

| MSB LSB                    | Analog Output (Vоит)               |

| 1111 1111 1111 1111        | 8.192 V (65,535/65,536) = 8.1919 V |

| 1000 0000 0000 0000        | 8.192 V (32,768/65,536) = 4.096 V  |

| 0000 0000 0000 1000        | 8.192 V (8/65,536) = 0.001 V       |

| 0000 0000 0000 0100        | 8.192 V (4/65,536) = 0.0005 V      |

| 0000 0000 0000 0010        | 8.192 V (2/65,536) = 0.00025 V     |

| 0000 0000 0000 0001        | 8.192 V (1/65,536) = 0.000125 V    |

Table 9 assumes a 16-bit resolution; 1 LSB =  $8.192 \text{ V}/2^{16} = 125 \mu\text{V}$ .

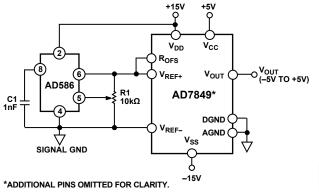

## Generating a ±5 V Output Range from a Single +5 V Reference

Figure 23 shows how to generate a  $\pm 5$  V output range when using a single +5 V reference.  $V_{REF-}$  is connected to 0 V, and  $R_{OFS}$  is connected to  $V_{REF+}$ . The 5 V reference input is applied to these pins. With all 0s loaded to the DAC, the noninverting terminal of the output stage amplifier is at 0 V, and  $V_{OUT}$  is the inverse of  $V_{REF+}$ . With all 1s loaded to the DAC, the noninverting terminal of the output stage amplifier is 5 V and, therefore,  $V_{OUT}$  is also 5 V.

Figure 23. Generating  $a \pm 5 V$  Output Range from a Single +5 V

#### MICROPROCESSOR INTERFACING

Microprocessor interfacing to the AD7849 is via a serial bus that uses standard protocol compatible with DSP processors and microcontrollers. The communications channel requires a 3-wire interface consisting of a clock signal, a data signal, and a synchronization signal. The AD7849 requires a 16-bit data-word with data valid on the falling edge of SCLK. For all the interfaces, the DAC update can be done automatically when all data is clocked in, or it can be done under control of  $\overline{\text{LDAC}}$ .

Figure 24 through Figure 27 show the AD7849 configured for interfacing to a number of popular DSP processors and microcontrollers.

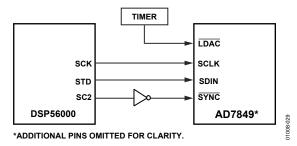

#### AD7849-to-DSP56000 Interface

A serial interface between the AD7849 and the DSP56000 is shown in Figure 24. The DSP56000 is configured for normal mode asynchronous operation with a gated clock. It is also setup for a 16-bit word with SCK and SC2 as outputs and the FSL control bit set to 0. SCK is internally generated on the DSP56000 and applied to the AD7849 SCLK input. Data from the DSP56000 is valid on the falling edge of SCK. The SC2 output provides the framing pulse for valid data. This line must be inverted before being applied to the SYNC input of the AD7849.

In this interface, an LDAC pulse generated from an external timer is used to update the outputs of the DAC. This update can also be produced using a bit programmable control line from the DSP56000.

Figure 24. AD7849-to-DSP56000 Interface

1008-023

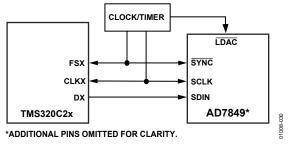

#### AD7849-to-TMS320C2x Interface

Figure 25 shows a serial interface between the AD7849 and the TMS320C2x DSP processor. In this interface, the CLKX and FSX signals for the TMS320C2x should be generated using external clock/timer circuitry. The FSX pin of the TMS320C2x must be configured as an input. Data from the TMS320C2x is valid on the falling edge of CLKX.

Figure 25. AD7849-to-TMS320C2x Interface

The clock/timer circuitry generates the  $\overline{LDAC}$  signal for the AD7849 to synchronize the update of the output with the serial transmission. Alternatively, the automatic update mode can be selected by connecting  $\overline{LDAC}$  to DGND.

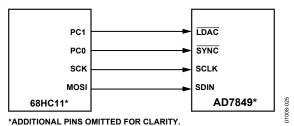

#### AD7849-to-68HC11 Interface

Figure 26 shows a serial interface between the AD7849 and the 68HC11 microcontroller. SCK of the 68HC11 drives SCLK of the AD7849, while the MOSI output drives the serial data line of the AD7849. The  $\overline{\text{SYNC}}$  signal is derived from a port line (PC0 shown).

For correct operation of this interface, the 68HC11 should be configured such that its CPOL bit is a 0 and its CPHA bit is a 1. When data is transmitted to the part, PC0 is taken low. When the 68HC11 is configured like this, data on MOSI is valid on the falling edge of SCK. The 68HC11 transmits its serial data in 8-bit bytes with only eight falling clock edges occurring in the transmit cycle. To load data to the AD7849, PC0 is left low after the first eight bits are transferred, and a second byte of data is then transferred serially to the AD7849. When the second serial transfer is complete, the PC0 line is taken high.

Figure 26 shows the  $\overline{LDAC}$  input of the AD7849 being driven from another bit programmable port line (PC1). As a result, the DAC can be updated by taking  $\overline{LDAC}$  low after the DAC input register has been loaded.

Figure 26. AD7849-to-68HC11 Interface

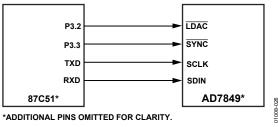

#### AD7849-to-87C51 Interface

A serial interface between the AD7849 and the 87C51 microcontroller is shown in Figure 27. TXD of the 87C51 drives SCLK of the AD7849, while RXD drives the serial data line of the part. The  $\overline{\text{SYNC}}$  signal is derived from the P3.3 port line, and the  $\overline{\text{LDAC}}$  line is driven from the P3.2 port line.

The 87C51 provides the LSB of its SBUF register as the first bit in the serial data stream. Therefore, ensure that the data in the SBUF register is arranged correctly so that the most significant bits are the first to be transmitted to the AD7849, and the last bit to be sent is the LSB of the word to be loaded to the AD7849. When data is transmitted to the part, P3.3 is taken low. Data on RXD is valid on the falling edge of TXD. The 87C51 transmits its serial data in 8-bit bytes, with only eight falling clock edges occurring in the transmit cycle. To load data to the AD7849, P3.3 is left low after the first eight bits are transferred, and a second byte of data is then transferred serially to the AD7849. When the second serial transfer is complete, the P3.3 line is taken high.

Figure 27 shows the  $\overline{\text{LDAC}}$  input of the AD7849 driven from the bit programmable P3.2 port line. As a result, the DAC output can be updated by taking the  $\overline{\text{LDAC}}$  line low following the completion of the write cycle. Alternatively,  $\overline{\text{LDAC}}$  can be hardwired low, and the analog output is updated on the 16th falling edge of TXD after the SYNC signal for the DAC goes low.

Figure 27. AD7849-to-87C51 Interface

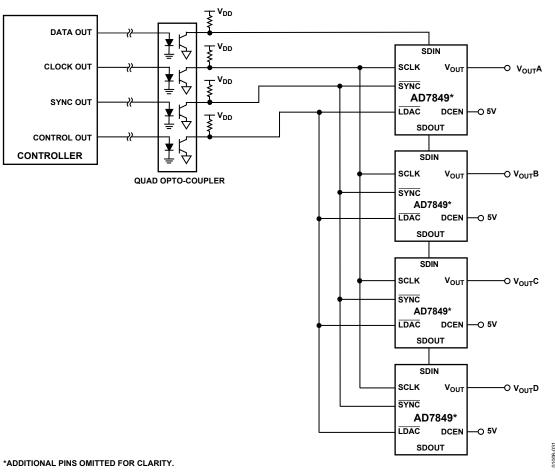

# APPLICATIONS INFORMATION OPTO-ISOLATED INTERFACE

In many process control applications, it is necessary to provide an isolation barrier between the controller and the unit being controlled. Opto-isolators can provide voltage isolation in excess of 3 kV. The serial loading structure of the AD7849 makes it ideal for opto-isolated interfaces because the number of interface lines is kept to a minimum.

Figure 28 shows a 4-channel isolated interface using the AD7849. The DCEN pin must be connected high to enable the daisy-chain facility. Four channels with 14-bit or 16-bit resolution are provided in the circuit shown, but this can be expanded to accommodate any number of DAC channels without any extra isolation circuitry. The only limitation is the output update rate. For example, if an output update rate of 10 kHz is required, then all DACs must be loaded and updated in 100  $\mu s$ . Operating at the maximum clock rate of 5 MHz means that it takes 3.2  $\mu s$  to load a DAC. This means that the total number of channels for this update rate is 31, which leaves 800 ns for the  $\overline{LDAC}$  pulse. Of course, as the update rate requirement decreases, the number of possible channels increases.

The sequence of events to program the output channels in Figure 28 is as follows:

- 1. Take the  $\overline{\text{SYNC}}$  line low.

- 2. Transmit the data as four 16-bit words. A total of 64 clock pulses is required to clock the data through the chain.

- 3. Take the  $\overline{\text{SYNC}}$  line high.

- 4. Pulse the  $\overline{\text{LDAC}}$  line low. This updates all output channels simultaneously on the falling edge of  $\overline{\text{LDAC}}$ .

To reduce the number of optocouplers, the  $\overline{\text{LDAC}}$  line can be driven from one shot that is triggered by the rising edge on the  $\overline{\text{SYNC}}$  line. A low level pulse of 100 ns duration or greater is all that is required to update the outputs.

Figure 28. 4-Channel Opto-Isolated Interface

## **OUTLINE DIMENSIONS**

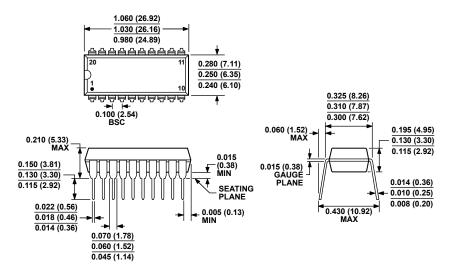

#### **COMPLIANT TO JEDEC STANDARDS MS-001**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 29. 20-Lead Plastic Dual In-Line Package [PDIP] Narrow Body (N-20) Dimensions shown in inches and (millimeters)

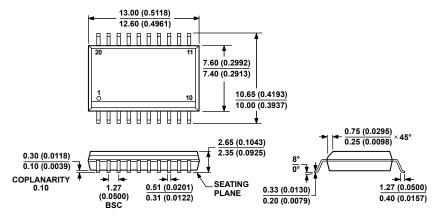

COMPLIANT TO JEDEC STANDARDS MS-013-AC

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 30. 20-Lead Standard Small Outline Package [SOIC\_W] Wide Body (RW-20) Dimensions shown in millimeters and (inches)

Rev. C | Page 18 of 20

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Resolution (Bits) | Bipolar INL (LSB) | Package Description | Package Option |

|--------------------|-------------------|-------------------|-------------------|---------------------|----------------|

| AD7849ANZ          | -40°C to +85°C    | 14                | ±3                | 20-Lead PDIP        | N-20           |

| AD7849BNZ          | -40°C to +85°C    | 16                | ±8                | 20-Lead PDIP        | N-20           |

| AD7849CNZ          | -40°C to +85°C    | 16                | ±4                | 20-Lead PDIP        | N-20           |

| AD7849AR           | −40°C to +85°C    | 14                | ±3                | 20-Lead SOIC_W      | RW-20          |

| AD7849AR-REEL      | −40°C to +85°C    | 14                | ±3                | 20-Lead SOIC_W      | RW-20          |

| AD7849ARZ          | -40°C to +85°C    | 14                | ±3                | 20-Lead SOIC_W      | RW-20          |

| AD7849ARZ-REEL     | -40°C to +85°C    | 14                | ±3                | 20-Lead SOIC_W      | RW-20          |

| AD7849BR           | −40°C to +85°C    | 16                | ±8                | 20-Lead SOIC_W      | RW-20          |

| AD7849BR-REEL      | -40°C to +85°C    | 16                | ±8                | 20-Lead SOIC_W      | RW-20          |

| AD7849BRZ          | -40°C to +85°C    | 16                | ±8                | 20-Lead SOIC_W      | RW-20          |

| AD7849BRZ-REEL     | -40°C to +85°C    | 16                | ±8                | 20-Lead SOIC_W      | RW-20          |

| AD7849CR           | -40°C to +85°C    | 16                | ±4                | 20-Lead SOIC_W      | RW-20          |

| AD7849CR-REEL      | -40°C to +85°C    | 16                | ±4                | 20-Lead SOIC_W      | RW-20          |

| AD7849CRZ          | -40°C to +85°C    | 16                | ±4                | 20-Lead SOIC_W      | RW-20          |

| AD7849CRZ-REEL     | −40°C to +85°C    | 16                | ±4                | 20-Lead SOIC_W      | RW-20          |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

| AD7849 |

|--------|

| AD7849 |

**NOTES**