# LTC1450/LTC1450L

Parallel Input, 12-Bit Rail-to-Rail Micropower DACs in SSOP

### FEATURES

- Guaranteed Monotonic

- Buffered True Rail-to-Rail Voltage Output

- 12-Bit Resolution

- 3V Operation (LTC1450L) I<sub>CC</sub>: 250µA Typ

- 5V Operation (LTC1450) I<sub>CC</sub>: 400μA Typ

- Parallel 12-Bit or 8 + 4-Bit Double Buffered Digital Input

- Internal Reference

- Output Buffer Configurable to Gain of 1 or 2

- Configurable as a Multiplying DAC

- Internal Power-On Reset

- Maximum DNL Error: 0.5LSB

### APPLICATIONS

- Digital Calibration

- Industrial Process Control

- Automatic Test Equipment

- Arbitrary Function Generators

- Battery-Powered Data Conversion Products

- Feedback Control Loops and Gain Control

# DESCRIPTION

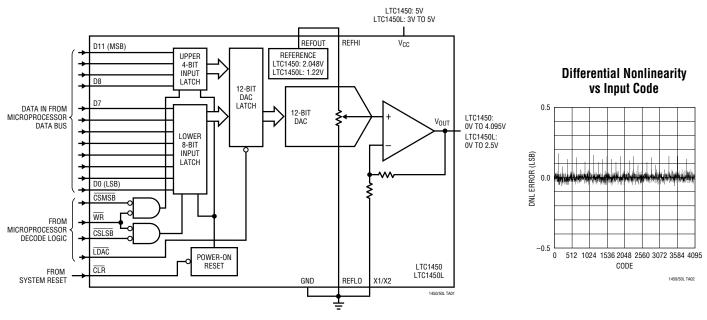

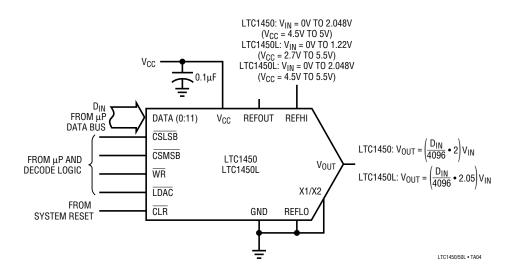

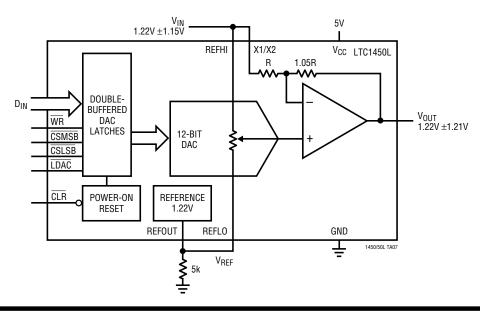

The LTC<sup>®</sup>1450/LTC1450L are complete single supply, railto-rail voltage output, 12-bit digital-to-analog converters (DACs) in a 24-pin SSOP or PDIP package. They include an output buffer amplifier, reference and a double buffered parallel digital interface.

The LTC1450 operates from a 4.5V to 5.5V supply. The output can be pin strapped for 4.095V or 2.048V full-scale. It has a 2.048V internal reference.

The LTC1450L operates from a 2.7V to 5.5V supply. The output can be pin strapped for 2.5V or 1.22V full-scale. It has a 1.22V internal reference.

The LTC1450/LTC1450L offer true stand-alone performance. In addition, the reference output, high and low reference inputs and gain setting resistor are brought to pins for maximum flexibility.

C, LTC and LT are registered trademarks of Linear Technology Corporation.

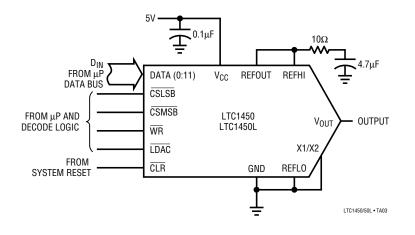

### TYPICAL APPLICATION

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.5V to 7.5V<br>Logic Inputs to GND0.5V to 7.5V |    |

|-----------------------------------------------------------------------|----|

| $V_{OUT}$                                                             |    |

| REFOUT, REFLO, REFHI, X1/X20.5V to V <sub>CC</sub> + 0.5V             |    |

| Maximum Junction Temperature 125°C                                    | уĊ |

| Operating Temperature Range                                           |    |

| Commercial0°C to 70°C                                                 |    |

| Industrial –40°C to 85°C                                              | ,C |

| Storage Temperature Range65°C to 150°C                                |    |

| Lead Temperature (Soldering, 10 sec) 300°C                            | °C |

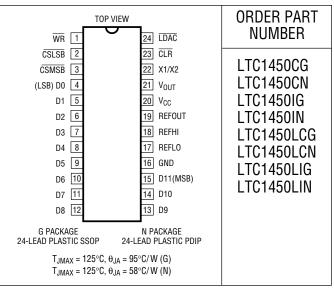

# PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

# **ELECTRICAL CHARACTERISTICS** $V_{CC} = 4.5V$ to 5.5V (LTC1450), 2.7V to 5.5V (LTC1450L), $V_{OUT}$ unloaded,

REFOUT = REFHI, REFLO = GND = X1/X2,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL             | PARAMETER                                  | CONDITIONS                                                |   | MIN   | ТҮР        | MAX       | UNITS  |

|--------------------|--------------------------------------------|-----------------------------------------------------------|---|-------|------------|-----------|--------|

| DAC                | · · · · ·                                  |                                                           |   |       |            |           |        |

|                    | Resolution                                 |                                                           | • | 12    |            |           | Bits   |

| DNL                | Differential Nonlinearity                  | Guaranteed Monotonic (Note 1)                             | • |       |            | ±0.5      | LSB    |

| INL                | Integral Nonlinearity                      | T <sub>A</sub> = 25°C                                     |   |       |            | ±3.5      | LSB    |

|                    |                                            | (Note 1)                                                  | • |       |            | ±4.0      | LSB    |

| V <sub>OS</sub>    | Offset Error                               | $T_A = 25^{\circ}C$                                       |   |       |            | ±12       | mV     |

|                    |                                            |                                                           | • |       |            | ±18       | mV     |

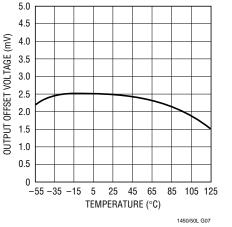

| V <sub>OS</sub> TC | Offset Error Temperature Coefficient       |                                                           |   |       | ±15        |           | μV/°C  |

| V <sub>FS</sub>    | Full-Scale Voltage                         | Using Internal Reference, LTC1450, T <sub>A</sub> = 25°C  |   | 4.065 | 4.095      | 4.125     | V      |

|                    |                                            | Using Internal Reference, LTC1450                         | • | 4.045 | 4.095      | 4.145     | V      |

|                    |                                            | External 2.048V Reference, LTC1450                        | • | 4.075 | 4.095      | 4.115     | V      |

|                    |                                            | Using Internal Reference, LTC1450L, T <sub>A</sub> = 25°C |   | 2.470 | 2.500      | 2.530     | V      |

|                    |                                            | Using Internal Reference, LTC1450L                        | • | 2.460 | 2.500      | 2.540     | V      |

|                    |                                            | External 1.22V Reference, LTC1450L                        | • | 2.480 | 2.500      | 2.520     | V      |

| V <sub>FS</sub> TC | Full-Scale Voltage Temperature Coefficient | Using Internal Reference, LTC1450                         |   |       | ±0.10      |           | LSB/°C |

|                    |                                            | Using External Reference, LTC1450/LTC1450L                |   |       | $\pm 0.02$ |           | LSB/°C |

|                    |                                            | Using Internal Reference, LTC1450L                        |   |       | ±0.10      |           | LSB/°C |

| Referenc           | e Output (REFOUT)                          |                                                           |   |       |            |           |        |

|                    | Reference Output Voltage                   | LTC1450L                                                  | • | 1.195 | 1.220      | 1.245     | V      |

|                    |                                            | LTC1450                                                   | • | 2.008 | 2.048      | 2.088     | V      |

|                    | Reference Output Temperature Coefficient   |                                                           |   |       | $\pm 0.08$ |           | LSB/°C |

|                    | Reference Line Regulation                  |                                                           | • |       | 0.7        | ±2        | LSB/V  |

|                    | Reference Load Regulation                  | $0 \le I_{OUT} \le 100 \mu A$ , LTC1450L                  | • |       | 0.6        | $\pm 3.0$ | LSB    |

|                    |                                            | LTC1450                                                   | • |       | 0.2        | ±1.5      | LSB    |

|                    | Short-Circuit Current                      | REFOUT Shorted to GND                                     | • |       |            | 80        | mA     |

2

# **ELECTRICAL CHARACTERISTICS** $V_{CC} = 4.5V$ to 5.5V (LTC1450), 2.7V to 5.5V (LTC1450L), $V_{OUT}$ unloaded, REFOUT = REFHI, REFLO = GND = X1/X2, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.

| SYMBO             | PARAMETER                    | CONDITIONS                                                                                                                                   |   | MIN        | ТҮР                | MAX        | UNITS    |

|-------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---|------------|--------------------|------------|----------|

| Referen           | ce Input (REFLO = GND)       |                                                                                                                                              |   |            |                    | I          |          |

|                   | REFHI Input Range            | $V_{\text{REFHI}} \le V_{\text{CC}} - 1.5V$                                                                                                  | • |            |                    | $V_{CC}/2$ | V        |

|                   | REFHI Input Resistance       |                                                                                                                                              | • | 8          | 18                 | 30         | kΩ       |

|                   | REFHI Input Capacitance      |                                                                                                                                              |   |            | 15                 |            | pF       |

| Power S           | upply                        |                                                                                                                                              |   |            |                    |            |          |

| V <sub>CC</sub>   | Positive Supply Voltage      | For Specified Performance, LTC1450L<br>LTC1450                                                                                               | • | 2.7<br>4.5 |                    | 5.5<br>5.5 | V<br>V   |

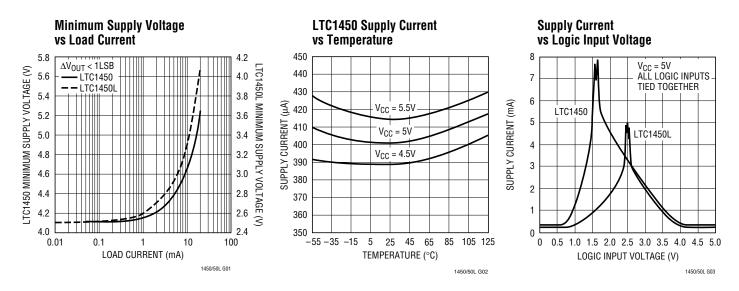

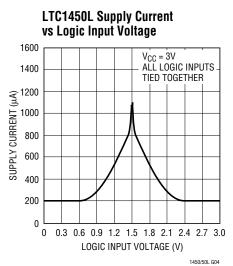

| I <sub>CC</sub>   | Supply Current               | $\begin{array}{l} 4.5V \leq V_{CC} \leq 5.5V \mbox{ (Note 4) } LTC1450 \\ 2.7V \leq V_{CC} \leq 5.5V \mbox{ (Note 4) } LTC1450L \end{array}$ | • | 300<br>150 | 400<br>250         | 620<br>500 | μΑ<br>μΑ |

| Op Amp            | DC Performance               |                                                                                                                                              | · |            |                    |            |          |

|                   | Short-Circuit Current Low    | V <sub>OUT</sub> Shorted to GND                                                                                                              | • |            |                    | 100        | mA       |

|                   | Short-Circuit Current High   | V <sub>OUT</sub> Shorted to V <sub>CC</sub>                                                                                                  | • |            |                    | 120        | mA       |

|                   | Output Impedance to GND      | Input Code = 0                                                                                                                               | • |            | 40                 | 120        | Ω        |

| AC Perf           | ormance                      |                                                                                                                                              |   |            |                    |            |          |

|                   | Voltage Output Slew Rate     | (Note 2)                                                                                                                                     | • | 0.5        | 1.0                |            | V/µs     |

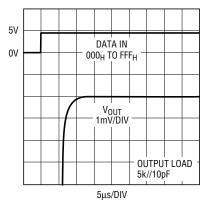

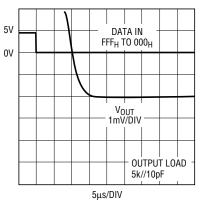

|                   | Voltage Output Settling Time | (Notes 2, 3) to ±0.5LSB                                                                                                                      |   |            | 14                 |            | μs       |

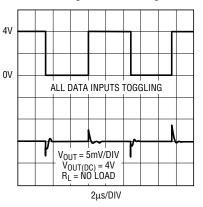

|                   | Digital Feedthrough          | LDAC = 1                                                                                                                                     |   |            | 5                  |            | (nV)(s)  |

|                   | AC Feedthrough               | REFHI = 1kHz, $2V_{P-P}$                                                                                                                     |   |            | -95                |            | dB       |

| SINAD             | Signal-to-Noise + Distortion | REFHI = 1kHz, 2V <sub>P-P</sub> (Code: All 1's)                                                                                              |   |            | 85                 |            | dB       |

| Digital I         | nputs                        |                                                                                                                                              |   |            |                    |            |          |

| V <sub>IH</sub>   | Digital Input High Voltage   | V <sub>CC</sub> = 3V, LTC1450L<br>V <sub>CC</sub> = 5V, LTC1450                                                                              | • | 2.2<br>2.4 |                    |            | V<br>V   |

| V <sub>IL</sub>   | Digital Input Low Voltage    | V <sub>CC</sub> = 3V, LTC1450L<br>V <sub>CC</sub> = 5V, LTC1450                                                                              | • |            |                    | 0.8<br>0.8 | V<br>V   |

| V <sub>LTH</sub>  | Logic Threshold Voltage      | LTC1450L                                                                                                                                     |   |            | V <sub>CC</sub> /2 |            | V        |

| I <sub>LEAK</sub> | Digital Input Leakage        | $V_{CC} = 5V, V_{IN} = GND \text{ to } V_{CC}$                                                                                               | • | -10        |                    | 10         | μA       |

| CIN               | Digital Input Capacitance    | Guaranteed by Design. Not Subject to Test                                                                                                    | • |            |                    | 10         | pF       |

### **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 4.5V to 5.5V (LTC1450),  $V_{CC}$  = 2.7V to 3.6V (LTC1450L),  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| SYMBOL            | PARAMETER                   | CONDITIONS                                                                                                            |   | MIN      | ТҮР              | MAX | UNITS          |

|-------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|---|----------|------------------|-----|----------------|

| Switchin          | g Characteristics (Note 5)  | ·                                                                                                                     |   |          |                  |     |                |

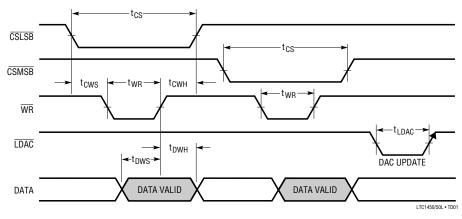

| t <sub>CS</sub>   | CS (MSB or LSB) Pulse Width |                                                                                                                       | • | 40       |                  |     | ns             |

| t <sub>WR</sub>   | WR Pulse Width              |                                                                                                                       | • | 40       |                  |     | ns             |

| t <sub>CWS</sub>  | CS to WR Setup              |                                                                                                                       | • | 0        |                  |     | ns             |

| t <sub>CWH</sub>  | CS to WR Hold               |                                                                                                                       | • | 0        |                  |     | ns             |

| t <sub>DWS</sub>  | Data Valid to WR Setup      | $V_{CC} = 4.5V \text{ to } 5.5V (LTC1450)$<br>$V_{CC} = 2.7V \text{ to } 3.6V (LTC1450L)$<br>$V_{CC} = 5V (LTC1450L)$ | • | 40<br>40 | 15<br>15<br>10   |     | ns<br>ns<br>ns |

| t <sub>DWH</sub>  | Data Valid to WR Hold       | $V_{CC} = 4.5V \text{ to } 5.5V (LTC1450)$<br>$V_{CC} = 2.7V \text{ to } 3.6V (LTC1450L)$<br>$V_{CC} = 5V (LTC1450L)$ | • | 0<br>0   | -10<br>-10<br>-5 |     | ns<br>ns<br>ns |

| t <sub>LDAC</sub> | LDAC Pulse Width            |                                                                                                                       | • | 40       |                  |     | ns             |

| t <sub>CLR</sub>  | CLR Pulse Width             |                                                                                                                       | • | 40       |                  |     | ns             |

The  $\bullet$  denotes specifications which apply over the full operating temperature range.

**Note 1:** Nonlinearity is defined from the first code that is greater than or equal to the maximum offset specification to code 4095 (full-scale). **Note 2:** Load is  $5k\Omega$  in parallel with 100pF.

Note 3: DAC switched all 1's and the code corresponding to  $V_{OS(\mbox{MAX})}$  for the part.

Note 4: Digital inputs at 0V or  $V_{CC}$ .

Note 5: Digital inputs swing 10% to 90% of V<sub>CC</sub>,  $t_r$  =  $t_f$  = 5ns and timing measurements are from V<sub>CC</sub>/2.

## TYPICAL PERFORMANCE CHARACTERISTICS

### TYPICAL PERFORMANCE CHARACTERISTICS

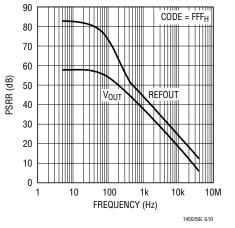

Power Supply Rejection vs Frequency

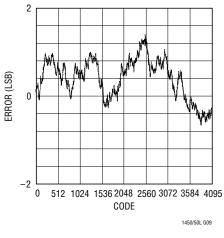

**Differential Nonlinearity (DNL)**

512 1024 1536 2048 2560 3072 3584 4095

1450/50L G08

CODE

Distortion + Noise vs Frequency

LTC1450 Total Harmonic

1k

10k

FREQUENCY (Hz)

100k

1450/50L G11

LTC1450

0.2

**DNL ERROR (LSB)**

0

-0.2

40

-50

-60

-70

-80

-90

-100 └ 100

FOTAL HARMONIC DISTORTION + NOISE (dB)

$V_{CC} = 5\dot{V}$

V<sub>REFHI</sub> = 2V<sub>P-P</sub> V<sub>OUT</sub> = 4V<sub>P-P</sub>

0

LTC1450 Pull-Down Voltage vs Output Sink Current Capability

LTC1450 Integral Nonlinearity (INL)

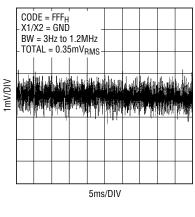

LTC1450 Broadband Output Noise

1450/50L G12

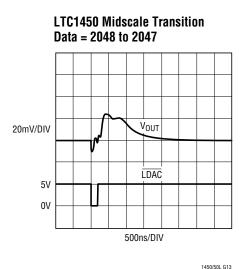

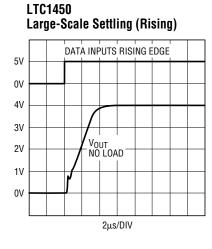

### TYPICAL PERFORMANCE CHARACTERISTICS

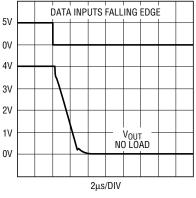

#### LTC1450 Large-Scale Settling (Falling)

1450/50L G14

**Output Voltage Full-Scale Settling**

1450/50L G16

#### **Output Voltage Zero-Scale Settling**

#### LTC1450 Digital Feedthrough

1450/50L G17

1450/50L G18

1450/50L G15

### PIN FUNCTIONS

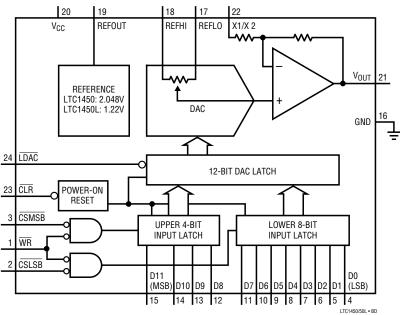

**WR** (Pin 1): Write Input (Active Low). Used with CSMSB and/or CSLSB to load data into the input latches. While WR and CSMSB and/or CSLSB are held low the <u>enabled</u> input latches are transparent. The rising edge of WR will latch data into all input latches.

**CSLSB** (Pin 2): Chip Select Least Significant Byte (Active Low). Used with WR to load data into the eight LSB input latches. While WR and CSLSB are held low the eight LSB input latches are transparent. The rising edge will latch data into the eight LSB input latches. Can be connected to CSMSB for simultaneous loading of both sets of input latches on a 12-bit bus.

**CSMSB (Pin 3):** Chip Select Most Significant Byte (Active Low). Used with WR to load data into the four MSB input latches. While WR and CSMSB are held low the four MSB input latches are transparent. The rising edge will latch data into the four MSB input latches. Can be connected to CSLSB for simultaneous loading of both sets of input latches on a 12-bit bus.

**D0 to D7 (Pins 4 to 11):** Input data for the Least Significant Byte. Loaded into LSB input latch when  $\overline{WR} = 0$  and  $\overline{CSLSB} = 0$ .

**D8**, **D9**, **D10**, **D11** (Pins 12, 13, 14, 15): Input data for the Most Significant Byte. Loaded into MSB input latch when WR = 0 and  $\overline{CSMSB} = 0$ . Can be connected to D0 to D3 for multiplexed operation on an 8-bit bus.

GND (Pin 16): Ground.

**REFLO (Pin 17):** Lower input terminal of the DAC's internal resistor string. Typically connected to Analog Ground.

An input code of  $(000_H)$  will connect the positive input of the output buffer to this end. Can be used to offset the zero scale above ground.

**REFHI (Pin 18):** Upper input terminal of the DAC's internal resistor string. Typically connected to REFOUT. An input code of ( $FFF_H$ ) will connect the positive input of the output buffer to 1LSB from this end.

**REFOUT (Pin 19):** Output of the internal 2.048V/1.22V reference. Typically connected to REFHI to drive internal DAC resistor string.

**V<sub>CC</sub> (Pin 20):** Positive Power Supply Input.  $4.5V \le V_{CC} \le 5.5V$  (LTC1450) and  $2.7V \le V_{CC} \le 5.5V$  (LTC1450L). Requires a bypass capacitor to ground.

Vout (Pin 21): Buffered DAC Output.

**X1/X2 (Pin 22):** Gain Setting Resistor Pin. Connect to GND for G = 2 or to  $V_{OUT}$  for G = 1. Should always be tied to a low impedance source, such as ground or  $V_{OUT}$ , to ensure stability of the output buffer when driving capacitive loads.

**CLR (Pin 23):** Clear Input (Asynchronous Active Low). A low on this pin asynchronously resets all internal latches to 0s.

**LDAC (Pin 24):** Load DAC (Asynchronous Active Low). Used to asynchronously transfer the contents of the input latches to the DAC latches which updates the output voltage. The rising edge latches the data into the DAC latches. If held low the DAC latches are transparent and data from the input latches will immediately update V<sub>OUT</sub>.

### DIGITAL INTERFACE TRUTH TABLE

| CLR | CSMSB      | CSLSB      | WR | LDAC | FUNCTION                                                |

|-----|------------|------------|----|------|---------------------------------------------------------|

| Н   | Н          | L          | L  | Н    | Loads the eight LSBs into the input latch               |

| Н   | Н          | L          | 1  | Н    | Latches the eight LSBs into the input latch             |

| Н   | Н          | $\uparrow$ | L  | Н    | Latches the eight LSBs into the input latch             |

| Н   | L          | Н          | L  | Н    | Loads the four MSBs into the input latch                |

| Н   | L          | Н          | ↑  | Н    | Latches the four MSBs into the input latch              |

| Н   | $\uparrow$ | Н          | L  | Н    | Latches the four MSBs into the input latch              |

| Н   | Н          | Н          | Н  | L    | Loads the input latch data into the DAC latch           |

| Н   | Н          | Н          | Н  | 1    | Latches the input latch data into the DAC latch         |

| Н   | L          | L          | L  | L    | Loads input data into DAC latches (latches transparent) |

| Н   | L          | L          | L  | 1    | Latches input data into DAC latches                     |

| L   | Х          | Х          | Х  | Х    | All zeros loaded into input and DAC latches             |

#### TIMING DIAGRAM

#### **BLOCK DIAGRAM**

### DEFINITIONS

**Resolution (n):** Resolution is defined as the number of digital input bits (n). It defines the number of DAC output states  $(2^n)$  that divide the full-scale range. The resolution does not imply linearity.

Full-Scale Voltage ( $V_{FS}$ ): This is the output of the DAC when all bits are set to 1.

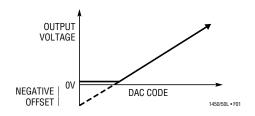

**Voltage Offset Error (V**<sub>OS</sub>): The theoretical voltage at the output when the DAC is loaded with all zeros. The output amplifier can have a true negative offset, but because the part is operated from a single supply, the output cannot go below zero. If the offset is negative, the output will remain near OV resulting in the transfer curve shown in Figure 1.

The offset of the part is measured at the code that corresponds to the maximum offset specification:

$V_{OS} = V_{OUT} - [(Code)(V_{FS})/(2^n - 1)]$

**Least Significant Bit (LSB):** One LSB is the ideal voltage difference between two successive codes.

$${\rm LSB} = ({\rm V}_{\rm FS} - {\rm V}_{\rm OS})/(2^n-1) = ({\rm V}_{\rm FS} - {\rm V}_{\rm OS})/4095$$

Nominal LSBs:

| LTC1450  | LSB = 4.095V/4095 = 1mV   |

|----------|---------------------------|

| LTC1450L | LSB = 2.5V/4095 = 0.610mV |

**Integral Nonlinearity (INL):** End-point INL is the maximum deviation from a straight line passing through the end points of the DAC transfer curve. Because the part operates from a single supply and the output cannot go below zero, the linearity is measured between full scale and the code corresponding to the maximum offset specification. The INL error at a given input code is calculated as follows:

**Differential Nonlinearity (DNL):** DNL is the difference between the measured change and the ideal one LSB change between any two adjacent codes. The DNL error between any two codes is calculated as follows:

DNL =  $(\Delta V_{OUT} - LSB)/LSB$

$\Delta V_{OUT}$  = The measured voltage difference between two adjacent codes

**Digital Feedthrough:** The glitch that appears at the analog output caused by AC coupling from the digital inputs when they change state. The area of the glitch is specified in (nV)(s).

Figure 1. Effect of Negative Offset

### OPERATION

#### Parallel Interface

The data on the input of the DAC is loaded into the DAC's input latches when Chip Select (CSLSB and/or CSMSB) and WR are at a logic low. The data that is loaded into the input latches will depend on which of the Chip Selects are at a logic low (see Digital Interface Truth Table). If WR and CSLSB are both low and CSMSB is high, then only data on the eight LSBs (D0 to D7) is loaded into the input latches. Similarly if WR and CSMSB are both low and CSMSB are both low and CSLSB is high then only data on the four MSBs (D8 to D11) is loaded into the input latches. Data is loaded into both the Least Significant Data Bits (D0 to D7) and the Most Significant Bits (D8 to D11) at the same time if WR, CSLSB and CSMSB are low.

The input data is latched into the input latches on the rising edge of either the  $\overline{WR}$  or one of the Chip Selects. The  $\overline{WR}$  transition high will latch the data in both input latches. A rising edge on  $\overline{CSMSB}$  will latch data bits D8 to D11. A rising edge on  $\overline{CSLSB}$  will latch data bits D0 to D7.

Once data is loaded into the input latches, it can be loaded into the DAC latch. This will update the analog voltage output of the DAC. The DAC latch is loaded by a logic low on LDAC. The data that is loaded into the DAC latch will be latched on the rising edge of LDAC.

When  $\overline{WR}$ ,  $\overline{CSLSB}$ ,  $\overline{CSMSB}$  and  $\overline{LDAC}$  are all low the latches are transparent and data on pins D0 to D11 loads directly into the DAC latch.

#### **Power-On Reset**

The LTC1450/LTC1450L have an internal power-on reset that resets all internal latches to 0's on power-up (equivalent to the  $\overline{\text{CLR}}$  pin function).

#### Reference

The LTC1450 includes an internal 2.048V reference, giving the LTC1450 a full-scale range of 4.095V in the gain of 2 configuration. The LTC1450L has an internal 1.22V reference with a full-scale range of 2.5V and a gain of 2.05 in the gain of 2 configuration. The onboard reference in the LTC1450 and LTC1450L is not internally connected to the DAC's reference resistor string but is provided on an adjacent pin for flexibility. Because the internal reference is not internally connected to the DAC resistor string, an external reference can be used or the resistor string can be driven with an external source in multiplying configuration. The external reference or source must be capable of driving the 8k minimum DAC ladder resistance.

The reference output noise can be reduced with a bypass capacitor to ground. (Note: The reference does not require a bypass capacitor to ground for proper operation.) When bypassing the reference a small value resistor in series with the capacitor is recommended to help reduce peaking on the output. A  $10\Omega$  resistor in series with a  $4.7\mu$ F capacitor is optimum for reducing reference generated noise.

#### **DAC Ladder Resistor String**

The high and low end of the DAC ladder resistor string (REFHI and REFLO respectively) are not connected internally on this part. Typically REFHI will be connected to REFOUT and REFLO will be connected to GND. This will give the LTC1450 a full-scale range of 4.095V. The fullscale range for the LTC1450L will be 2.5V

Either of these pins can be driven up to  $V_{CC} - 1.5V$  when using the buffer in the gain of 1 configuration. The resistor string pins can be driven to  $V_{CC}/2$  when the buffer is in the gain of 2 configuration (2.05 for the LTC1450L). The resistance between these two pins is typically 18k (8k min).

#### Voltage Output

The output buffer for the LTC1450/LTC1450L can be configured for two different gain settings. By tying the X1/X2 pin to GND the gain is set to 2 (2.05 for the LTC1450L). By tying the X1/X2 pin to  $V_{OUT}$  the gain is set to one.

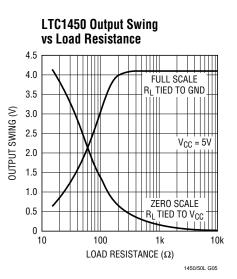

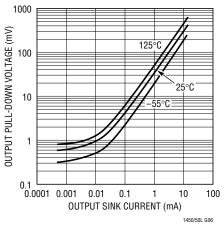

The LTC1450 family's rail-to-rail buffered output can source or sink 5mA over the entire operating temperature range while pulling to within 300mV of the positive supply voltage or GND. The output swings to within a few millivolts of either supply rail when unloaded and has an equivalent output resistance of  $40\Omega$  when driving a load to the rails.

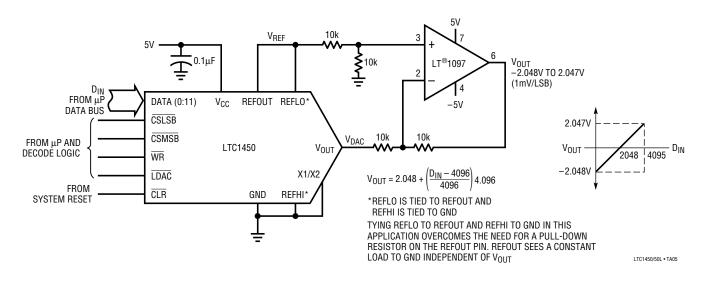

#### **TYPICAL APPLICATIONS**

Filter V<sub>REF</sub> to Lower Output Noise (0.18mV<sub>RMS</sub> at V<sub>OUT</sub>)

#### **Digitally Programmable Noninverting Amplifier**

### TYPICAL APPLICATIONS

**Bipolar Output 12-Bit DAC**

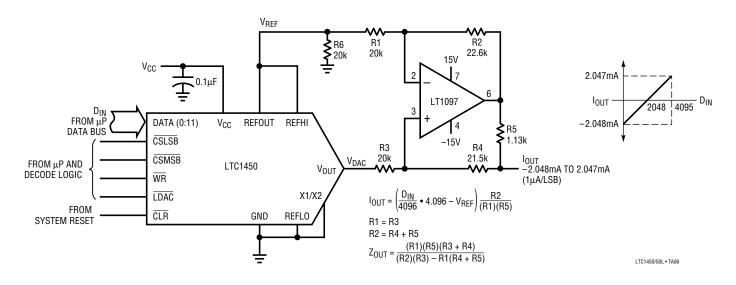

#### **Digitally Programmable Bilateral Current Source/Sink**

#### TYPICAL APPLICATIONS

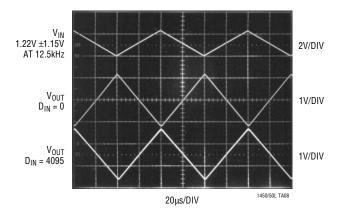

#### 4-Quadrant Multiplying DAC Application

This application shows the LTC1450L configured as a single supply 4-quadrant multiplying DAC. It uses a 5V supply and only one external component, a 5k resistor tied from REFOUT to ground. (The LTC1450 can be used in a similar fashion.) The multiplying DAC allows the user to digitally change the amplitude and polarity of an AC input signal whose voltage is centered around an offset signal ground provided by the 1.22V reference voltage. The transfer function is shown in the following equations.

$$V_{OUT} = (V_{IN} - V_{REF}) \left[ Gain \left( \frac{D_{IN}}{4096} - 1 \right) + 1 \right] + V_{REF}$$

For the LTC1450L Gain = 2.05 and  $V_{REF}$  = 1.22V

$$V_{OUT} = (V_{IN} - 1.22V) \left[ 2.05 \left( \frac{D_{IN}}{4096} \right) - 1.05 \right] + 1.22V$$

Table 1 shows the expressions for  $V_{OUT}$  as a function of  $V_{IN}$ ,  $V_{REF}$  and  $D_{IN}$ . The scope photo shows a 12.5kHz, 2.3V<sub>P-P</sub> triangle wave input signal and the corresponding output waveforms for zero-scale and full-scale DAC codes.

Table 1. Binary Code Table for 4-Quadrant, Multiplying DAC

Application

| whhite                                          | Application |      |                                                                     |  |  |  |

|-------------------------------------------------|-------------|------|---------------------------------------------------------------------|--|--|--|

| BINARY DIGITAL<br>Input code in<br>Dac register |             | EIN  | ANALOG OUTPUT (V <sub>out</sub> )                                   |  |  |  |

| MSB                                             |             | LSB  |                                                                     |  |  |  |

| 1111                                            | 1111        | 1111 | (4094/4096)(V <sub>IN</sub> – V <sub>REF</sub> ) + V <sub>REF</sub> |  |  |  |

| 1100                                            | 0001        | 1001 | $0.5(V_{IN} - V_{REF}) + V_{REF}$                                   |  |  |  |

| 1000                                            | 0011        | 0010 | V <sub>REF</sub>                                                    |  |  |  |

| 0100                                            | 0100        | 1011 | $-0.5(V_{IN} - V_{REF}) + V_{REF}$                                  |  |  |  |

| 0000                                            | 0110        | 0100 | $-1.0(V_{IN} - V_{REF}) + V_{REF}$                                  |  |  |  |

| 0000                                            | 0000        | 0000 | $-1.05(V_{IN} - V_{REF}) + V_{REF}$                                 |  |  |  |

#### Clean 4-Quadrant Multiplying Is Shown in the Output Waveforms for Zero-Scale and Full-Scale DAC Settings

Internal Reference, REFLO/REFHI Pins, Gain Adjust and Wide Supply Voltage Range Allow 4-Quadrant Mulitplying on a 5V Single Supply

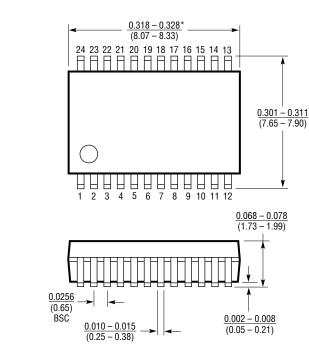

#### **PACKAGE DESCRIPTION** Dimensions in Inches (millimeters) unless otherwise noted.

G Package 24-Lead Plastic SSOP (0.209) (LTC DWG # 05-08-1640)

\*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE \*\*DIMENSIONS DO NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

G24 SSOP 0595

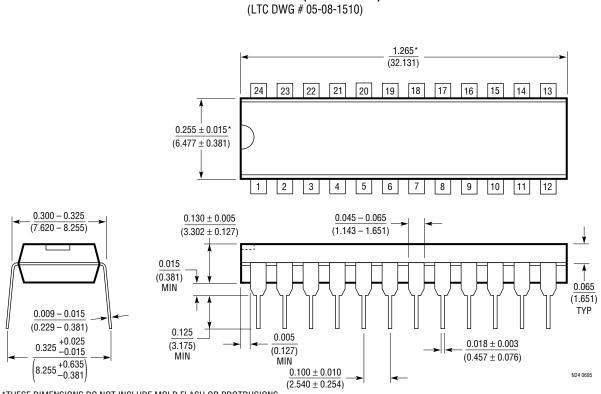

#### **PACKAGE DESCRIPTION** Dimensions in inches (millimeters) unless otherwise noted.

N Package 24-Lead PDIP (Narrow 0.300)

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

### **RELATED PARTS**

| PART NUMBER             | DESCRIPTION                                                                       | COMMENTS                                                                                                                |

|-------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| LTC1257                 | Complete Serial I/O V <sub>OUT</sub> 12-Bit DAC                                   | 5V to 15V Single Supply in 8-Pin SO and PDIP                                                                            |

| LTC1451/LTC1452/LTC1453 | Complete Serial I/O V <sub>OUT</sub> 12-Bit DACs                                  | 3V/5V Single Supply, Rail-to-Rail in 8-Pin SO and PDIP                                                                  |

| LTC1446/LTC1446L        | Dual 12-Bit V <sub>OUT</sub> DACs in SO-8 Package                                 | LTC1446: $V_{CC}$ = 4.5V TO 5.5V, $V_{OUT}$ = 0V TO 4.095V<br>LTC1446L: $V_{CC}$ = 2.7V to 5.5V, $V_{OUT}$ = 0V to 2.5V |

| LTC1454/LTC1454L        | Dual 12-Bit V <sub>OUT</sub> DACs in a 16-Pin SO Package with Added Functionality | LTC1454: $V_{CC}$ = 4.5V to 5.5V, $V_{OUT}$ = 0V TO 4.095V<br>LTC1454L: $V_{CC}$ = 2.7V to 5.5V, $V_{OUT}$ = 0V to 2.5V |

| LTC1458/LTC1458L        | Quad 12-Bit V <sub>OUT</sub> DACs in 28-Lead SW and SSOP<br>Packages              | LTC1458: $V_{CC}$ = 4.5V to 5.5V, $V_{OUT}$ = 0V to 4.095V<br>LTC1458L: $V_{CC}$ = 2.7V to 5.5V, $V_{OUT}$ = 0V to 2.5V |

| LTC7541A                | Parallel I/O Multiplying 12-Bit DAC                                               | 12-Bit Wide Input                                                                                                       |

| LTC7543/LTC8143         | Serial Multiplying 12-Bit DACs                                                    | Daisy-Chainable, Flexible Analog and Digital Interface                                                                  |

| LTC7545A                | Parallel Latched Input Multiplying 12-Bit DAC                                     | 12-Bit Wide Latched Input                                                                                               |

| LTC8043                 | Serial Multiplying 12-Bit DAC                                                     | 8-Pin SO and PDIP                                                                                                       |