### LTC2435/LTC2435-1

CGY 20-Bit No Latency ΔΣ<sup>™</sup> ADCs with Differential Input and Differential Reference

#### FEATURES

- 2× Speed Up Version of the LTC2430: 15Hz Output Rate, 60Hz Notch—LTC2435; 13.75Hz Output Rate, Simultaneous 50Hz/60Hz Notch—LTC2435-1

- Differential Input and Differential Reference with GND to V<sub>CC</sub> Common Mode Range

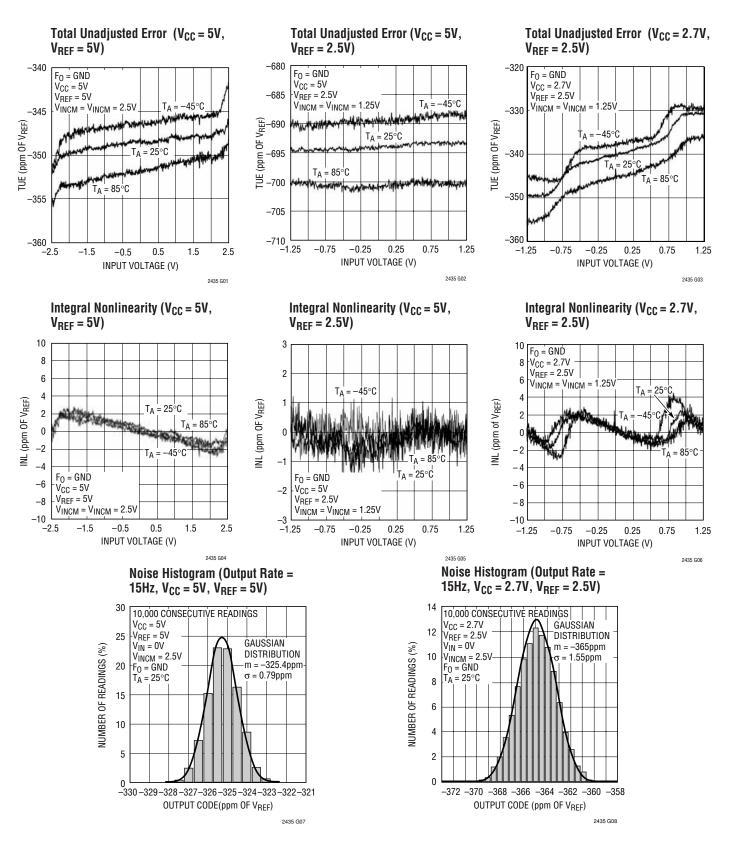

- 3ppm INL, No Missing Codes

- 10ppm Gain Error

- 0.8ppm Noise

- Single Conversion Settling Time for Multiplexed Applications

- Internal Oscillator—No External Components Required

- Single Supply 2.7V to 5.5V Operation

- Low Supply Current (200µA,4µA in Auto Sleep)

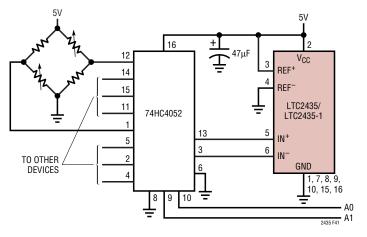

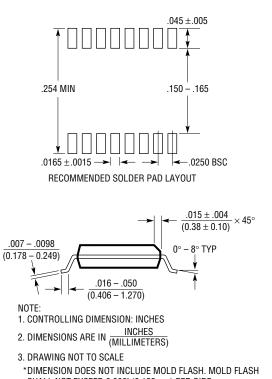

- 20-Bit ADC in Narrow SSOP-16 Package (SO-8 Footprint)

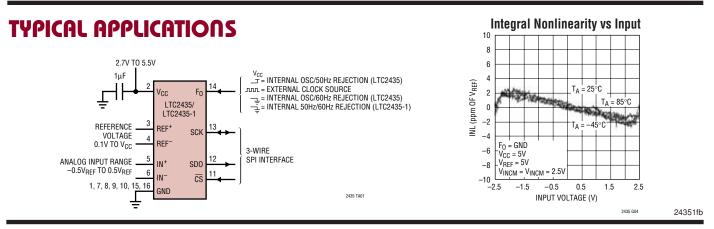

#### **APPLICATIONS**

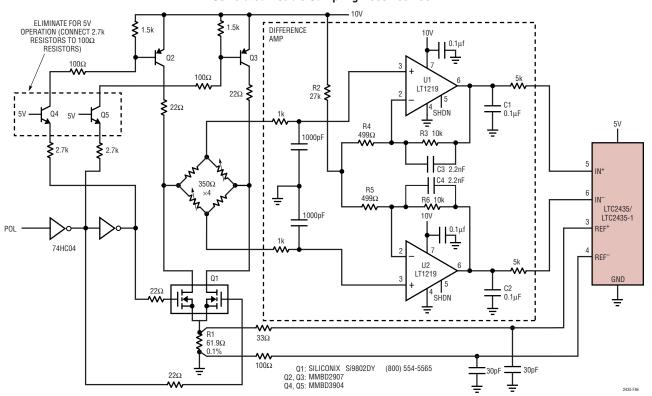

- Direct Sensor Digitizer

- Weight Scales

- Direct Temperature Measurement

- Gas Analyzers

- Strain Gage Transducers

- Instrumentation

- Data Acquisition

- Industrial Process Control

- 6-Digit DVMs

### DESCRIPTION

The LTC<sup>®</sup>2435/2435-1 are 2.7V to 5.5V micropower 20-bit differential  $\Delta\Sigma$  analog to digital converters with integrated oscillator, 3ppm INL and 0.8ppm RMS noise. They use delta-sigma technology and provide single cycle settling time for multiplexed applications. Through a single pin, the LTC2435 can be configured for better than 110dB input differential mode rejection at 50Hz or 60Hz  $\pm 2\%$ , or it can be driven by an external oscillator for a user defined rejection frequency. The LTC2435-1 can be configured for better than 87dB input differential mode rejection over the range of 49Hz to 61.2Hz (50Hz and 60Hz  $\pm 2\%$  simultaneously). The internal oscillator requires no external frequency setting components.

The converters accept any external differential reference voltage from 0.1V to  $V_{CC}$  for flexible ratiometric and remote sensing measurement configurations. The full-scale differential input range is from  $-0.5V_{REF}$  to  $0.5V_{REF}$ . The reference common mode voltage,  $V_{REFCM}$ , and the input common mode voltage,  $V_{INCM}$ , may be independently set anywhere within the GND to  $V_{CC}$  range of the LTC2435/LTC2435-1. The DC common mode input rejection is better than 120dB.

The LTC2435/LTC2435-1 communicate through a flexible 3-wire digital interface which is compatible with SPI and MICROWIRE<sup>TM</sup> protocols.

$\Delta T$ , LT, LTC and LTM are registered trademarks of Linear Technology Corporation. No Latency  $\Delta \Sigma$  is a trademark of Linear Technology Corporation. Protected by U.S. Patents including 6140950, 6169506.

### **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 2)

| Supply Voltage ( $V_{CC}$ ) to GND0.3V to 7V<br>Analog Input Pins Voltage to GND0.3V to ( $V_{CC}$ + 0.3V) |

|------------------------------------------------------------------------------------------------------------|

| Reference Input Pins Voltage                                                                               |

| to GND $-0.3V$ to (V <sub>CC</sub> + 0.3V)                                                                 |

| Digital Input Voltage to GND $-0.3V$ to (V <sub>CC</sub> + 0.3V)                                           |

| Digital Output Voltage to GND $\dots -0.3V$ to (V <sub>CC</sub> + 0.3V)                                    |

| Operating Temperature Range                                                                                |

| LTC2435C/LTC2435-1C0°C to 70°C                                                                             |

| LTC2435I/LTC2435-1I –40°C to 85°C                                                                          |

| Storage Temperature Range –65°C to 150°C                                                                   |

| Lead Temperature (Soldering, 10 sec) 300°C                                                                 |

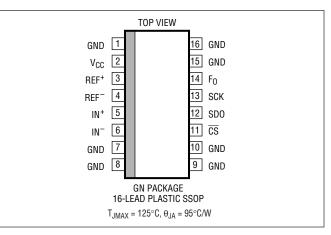

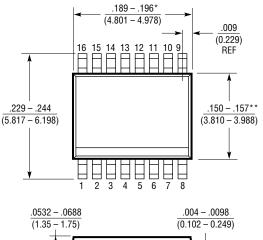

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

|------------------|--------------------|--------------|----------------------|-------------------|

| LT2435CGN#PBF    | LTC2435CGN#TRPBF   | 2435         | 16-Lead Plastic SSOP | 0°C to 70°C       |

| LT2435IGN#PBF    | LTC2435CGN#TRPBF   | 24351        | 16-Lead Plastic SSOP | -40°C to 85°C     |

| LT2435-1CGN#PBF  | LTC2435-1CGN#TRPBF | 24351        | 16-Lead Plastic SSOP | 0°C to 70°C       |

| LT2435-1IGN#PBF  | LTC2435-1IGN#TRPBF | 243511       | 16-Lead Plastic SSOP | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Notes 3, 4)

| PARAMETER                     | CONDITIONS                                                                                                                                |   | MIN | ТҮР          | MAX | UNITS                                                                         |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---|-----|--------------|-----|-------------------------------------------------------------------------------|

| Resolution (No Missing Codes) | $0.1V \le V_{REF} \le V_{CC}$ , $-0.5 \bullet V_{REF} \le V_{IN} \le 0.5 \bullet V_{REF}$ , (Note 5)                                      |   | 20  |              |     | Bits                                                                          |

| Integral Nonlinearity         |                                                                                                                                           | • |     | 2<br>3<br>10 | 20  | ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub><br>ppm of V <sub>REF</sub> |

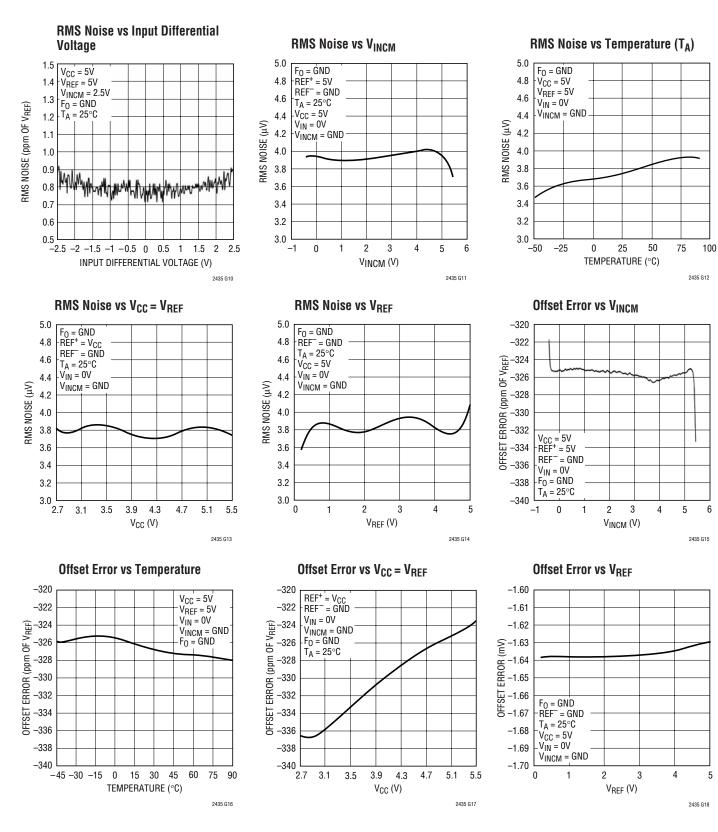

| Offset Error                  | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>GND $\le IN^+ = IN^- \le V_{CC}$ , (Note 14)                                             | • |     | 2            | 5   | mV                                                                            |

| Offset Error Drift            | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>GND $\le IN^+ = IN^- \le V_{CC}$                                                         |   |     | 100          |     | nV/°C                                                                         |

| Positive Gain Error           | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>IN <sup>+</sup> = 0.75REF <sup>+</sup> , IN <sup>-</sup> = 0.25 • REF <sup>+</sup>       | • |     | 10           | 25  | ppm of V <sub>REF</sub>                                                       |

| Positive Gain Error Drift     | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>IN <sup>+</sup> = 0.75REF <sup>+</sup> , IN <sup>-</sup> = 0.25 • REF <sup>+</sup>       |   |     | 0.1          |     | ppm of V <sub>REF</sub> /°C                                                   |

| Negative Gain Error           | $2.5V \le REF^+ \le V_{CC}, REF^- = GND,$<br>IN <sup>+</sup> = 0.25 • REF <sup>+</sup> , IN <sup>-</sup> = 0.75 • REF <sup>+</sup>        | • |     | 10           | 25  | ppm of V <sub>REF</sub>                                                       |

| Negative Gain Error Drift     | $2.5V \le REF^+ \le V_{CC}$ , $REF^- = GND$ ,<br>IN <sup>+</sup> = 0.25 • $REF^+$ , IN <sup>-</sup> = 0.75 • $REF^+$                      |   |     | 0.1          |     | ppm of V <sub>REF</sub> /°C                                                   |

| Output Noise                  | $ \begin{split} & 5V \leq V_{CC} \leq 5.5V, \ REF^+ = 5V, \ REF^- = GND, \\ & GND \leq IN^- = IN^+ \leq V_{CC}, \ (Note 13) \end{split} $ |   |     | 4            |     | μV <sub>RMS</sub>                                                             |

|                               |                                                                                                                                           |   |     |              |     | 24351fb                                                                       |

2

## **CONVERTER CHARACTERISTICS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Notes 3, 4)

| PARAMETER                                                                  | CONDITIONS                                                                                                                         |   | MIN | ТҮР | MAX | UNITS |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|-------|

| Input Common Mode Rejection DC                                             | $\begin{array}{l} 2.5V \leq REF^+ \leq V_{CC}, \ REF^- = GND, \\ GND \leq IN^- = IN^+ \leq V_{CC} \ (Note \ 5) \end{array}$        | • | 110 | 120 |     | dB    |

| Input Common Mode Rejection<br>60Hz ±2% (LTC2435)                          | $\begin{array}{l} 2.5V \leq REF^+ \leq V_{CC}, \ REF^- = GND, \\ GND \leq IN^- = IN^+ \leq V_{CC}, \ (Notes \ 5, \ 7) \end{array}$ | • | 140 |     |     | dB    |

| Input Common Mode Rejection<br>50Hz ±2% (LTC2435)                          | $\begin{array}{l} 2.5V \leq REF^+ \leq V_{CC}, \ REF^- = GND, \\ GND \leq IN^- = IN^+ \leq V_{CC}, \ (Notes \ 5, \ 8) \end{array}$ | • | 140 |     |     | dB    |

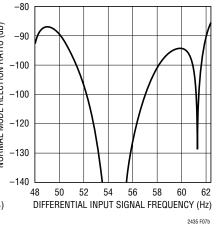

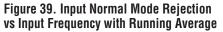

| Input Normal Mode Rejection<br>60Hz ±2% (LTC2435)                          | (Notes 5, 7)                                                                                                                       | • | 110 | 120 |     | dB    |

| Input Normal Mode Rejection<br>50Hz ±2% (LTC2435)                          | (Notes 5, 8)                                                                                                                       | • | 110 | 120 |     | dB    |

| Input Common Mode Rejection<br>49Hz to 61.2Hz (LTC2435-1)                  | $\begin{array}{l} 2.5V \leq REF^+ \leq V_{CC}, \ REF^- = GND, \\ GND \leq IN^- = IN^+ \leq V_{CC}, \ (Notes\ 5,\ 7) \end{array}$   | • | 120 |     |     | dB    |

| Input Normal Mode Rejection<br>49Hz to 61.2Hz (LTC2435-1)                  | F <sub>0</sub> = GND (Note 5)                                                                                                      | • | 87  |     |     | dB    |

| Input Normal Mode Rejection<br>External Clock f <sub>EOSC</sub> /2560 ±14% | External Oscillator (Note 5)                                                                                                       | • | 87  |     |     | dB    |

| Input Normal Mode Rejection<br>External Clock f <sub>EOSC</sub> /2560 ±4%  | External Oscillator (Note 5)                                                                                                       | • | 110 | 120 |     | dB    |

| Reference Common Mode<br>Rejection DC                                      | $2.5V \le REF^+ \le V_{CC}$ , $GND \le REF^- \le 2.5V$ ,<br>$V_{REF} = 2.5V$ , $IN^- = IN^+ = GND$ (Note 5)                        | • | 130 | 140 |     | dB    |

| Power Supply Rejection, DC                                                 | $REF^+ = V_{CC}, REF^- = GND, IN^- = IN^+ = GND$                                                                                   |   |     | 100 |     | dB    |

| Power Supply Rejection, 60Hz $\pm 2\%$                                     | $REF^+ = 2.5V, REF^- = GND, IN^- = IN^+ = GND, (Note 7)$                                                                           |   |     | 120 |     | dB    |

| Power Supply Rejection, 50Hz ±2%                                           | $REF^+ = 2.5V, REF^- = GND, IN^- = IN^+ = GND, (Note 8)$                                                                           |   |     | 120 |     | dB    |

# **ANALOG INPUT AND REFERENCE** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 3)

| SYMBOL                                   | PARAMETER                                                                      | CONDITIONS                                                                         |   | MIN                  | ТҮР | MAX                    | UNITS |

|------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---|----------------------|-----|------------------------|-------|

| IN <sup>+</sup>                          | Absolute/Common Mode IN <sup>+</sup> Voltage                                   |                                                                                    | • | GND – 0.3V           |     | V <sub>CC</sub> + 0.3V | V     |

| IN <sup>-</sup>                          | Absolute/Common Mode IN <sup>-</sup> Voltage                                   |                                                                                    | • | GND – 0.3V           |     | V <sub>CC</sub> + 0.3V | V     |

| V <sub>IN</sub>                          | Input Differential Voltage Range $(IN^+ - IN^-)$                               |                                                                                    | • | -V <sub>REF</sub> /2 |     | V <sub>REF</sub> /2    | V     |

| REF <sup>+</sup>                         | Absolute/Common Mode REF <sup>+</sup> Voltage                                  |                                                                                    |   | 0.1                  |     | V <sub>CC</sub>        | V     |

| REF <sup>-</sup>                         | Absolute/Common Mode REF <sup>-</sup> Voltage                                  |                                                                                    | • | GND                  |     | $V_{CC} - 0.1V$        | V     |

| V <sub>REF</sub>                         | Reference Differential Voltage Range<br>(REF <sup>+</sup> – REF <sup>-</sup> ) |                                                                                    | • | 0.1                  |     | V <sub>CC</sub>        | V     |

| C <sub>S</sub> (IN <sup>+</sup> )        | IN <sup>+</sup> Sampling Capacitance                                           |                                                                                    |   |                      | 1.5 |                        | pF    |

| C <sub>S</sub> (IN <sup>-</sup> )        | IN <sup>-</sup> Sampling Capacitance                                           |                                                                                    |   |                      | 1.5 |                        | pF    |

| C <sub>S</sub> (REF <sup>+</sup> )       | REF <sup>+</sup> Sampling Capacitance                                          |                                                                                    |   |                      | 1.5 |                        | pF    |

| C <sub>S</sub> (REF <sup>-</sup> )       | REF <sup>-</sup> Sampling Capacitance                                          |                                                                                    |   |                      | 1.5 |                        | pF    |

| I <sub>DC_LEAK</sub> (IN <sup>+</sup> )  | IN <sup>+</sup> DC Leakage Current                                             | $\overline{CS} = V_{CC}, IN^+ = GND$                                               | • | -10                  | 1   | 10                     | nA    |

| I <sub>DC_LEAK</sub> (IN <sup>-</sup> )  | IN <sup>-</sup> DC Leakage Current                                             | $\overline{CS} = V_{CC}, IN^- = V_{CC}$                                            | • | -10                  | 1   | 10                     | nA    |

| I <sub>DC_LEAK</sub> (REF <sup>+</sup> ) | REF <sup>+</sup> DC Leakage Current                                            | $\overline{\text{CS}} = \text{V}_{\text{CC}}, \text{REF}^+ = \text{V}_{\text{CC}}$ | • | -10                  | 1   | 10                     | nA    |

| I <sub>DC_LEAK</sub> (REF <sup>-</sup> ) | REF <sup>-</sup> DC Leakage Current                                            | $\overline{\text{CS}} = \text{V}_{\text{CC}}, \text{REF}^- = \text{GND}$           | • | -10                  | 1   | 10                     | nA    |

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 3)

| SYMBOL          | PARAMETER                                                     | CONDITIONS                                                                                                                    |   | MIN            | ТҮР | MAX        | UNITS  |

|-----------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---|----------------|-----|------------|--------|

| V <sub>IH</sub> | High Level Input Voltage CS, F <sub>0</sub>                   | $\begin{array}{c} 2.7V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 3.3V \end{array}$                                       | • | 2.5<br>2.0     |     |            | V<br>V |

| V <sub>IL</sub> | Low Level Input Voltage $\overline{\text{CS}}$ , $\text{F}_0$ | $\begin{array}{c} 4.5V \leq V_{CC} \leq 5.5V \\ 2.7V \leq V_{CC} \leq 5.5V \end{array}$                                       | • |                |     | 0.8<br>0.6 | V<br>V |

| V <sub>IH</sub> | High Level Input Voltage<br>SCK                               | $\begin{array}{c} 2.7V \leq V_{CC} \leq 5.5V \; (\text{Note 9}) \\ 2.7V \leq V_{CC} \leq 3.3V \; (\text{Note 9}) \end{array}$ | • | 2.5<br>2.0     |     |            | V<br>V |

| V <sub>IL</sub> | Low Level Input Voltage<br>SCK                                |                                                                                                                               | • |                |     | 0.8<br>0.6 | V<br>V |

| I <sub>IN</sub> | Digital Input Current<br>CS, F <sub>0</sub>                   | $0V \le V_{IN} \le V_{CC}$                                                                                                    | • | -10            |     | 10         | μΑ     |

| I <sub>IN</sub> | Digital Input Current<br>SCK                                  | $0V \le V_{IN} \le V_{CC}$ (Note 9)                                                                                           | • | -10            |     | 10         | μΑ     |

| C <sub>IN</sub> | Digital Input Capacitance<br>CS, F <sub>0</sub>               |                                                                                                                               |   |                | 10  |            | pF     |

| C <sub>IN</sub> | Digital Input Capacitance<br>SCK                              | (Note 9)                                                                                                                      |   |                | 10  |            | pF     |

| V <sub>OH</sub> | High Level Output Voltage<br>SDO                              | I <sub>0</sub> = -800μA                                                                                                       | • | $V_{CC} - 0.5$ |     |            | V      |

| V <sub>OL</sub> | Low Level Output Voltage<br>SDO                               | I <sub>0</sub> = 1.6mA                                                                                                        | • |                |     | 0.4        | V      |

| V <sub>OH</sub> | High Level Output Voltage<br>SCK                              | I <sub>0</sub> = -800μA (Note 10)                                                                                             | • | $V_{CC} - 0.5$ |     |            | V      |

| V <sub>OL</sub> | Low Level Output Voltage<br>SCK                               | I <sub>0</sub> = 1.6mA (Note 10)                                                                                              | • |                |     | 0.4        | V      |

| I <sub>OZ</sub> | Hi-Z Output Leakage<br>SDO                                    |                                                                                                                               | • | -10            |     | 10         | μA     |

## **POWER REQUIREMENTS** The $\bullet$ denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 3)

| SYMBOL          | PARAMETER                                                     | CONDITIONS                                                                                                                                                                                            |   | MIN | ТҮР           | MAX       | UNITS          |

|-----------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---------------|-----------|----------------|

| V <sub>CC</sub> | Supply Voltage                                                |                                                                                                                                                                                                       | • | 2.7 |               | 5.5       | V              |

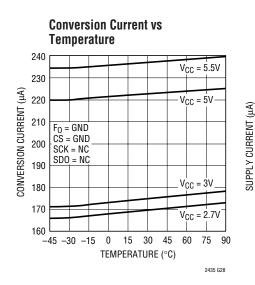

| I <sub>CC</sub> | Supply Current<br>Conversion Mode<br>Sleep Mode<br>Sleep Mode | $\label{eq:cs} \begin{array}{l} \overline{CS} = 0V \mbox{ (Note 12)} \\ \overline{CS} = V_{CC} \mbox{ (Note 12)} \\ \overline{CS} = V_{CC}, 2.7V \leq V_{CC} \leq 3.3V \mbox{ (Note 12)} \end{array}$ | • |     | 200<br>4<br>2 | 300<br>10 | μΑ<br>μΑ<br>μΑ |

TIMING CHARACTERISTICS The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . (Note 3)

| SYMBOL                 | PARAMETER                                                  | CONDITIONS                                                                                                                         |   | MIN                 | ТҮР                                        | MAX                  | UNITS             |

|------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---|---------------------|--------------------------------------------|----------------------|-------------------|

| f <sub>EOSC</sub>      | External Oscillator Frequency Range                        |                                                                                                                                    | • | 5                   |                                            | 2000                 | kHz               |

| t <sub>HEO</sub>       | External Oscillator High Period                            |                                                                                                                                    | • | 0.25                |                                            | 200                  | μs                |

| t <sub>LEO</sub>       | External Oscillator Low Period                             |                                                                                                                                    | • | 0.25                |                                            | 200                  | μs                |

| t <sub>CONV</sub>      | Conversion Time (LTC2435)                                  | $F_0 = 0V$<br>$F_0 = V_{CC}$<br>External Oscillator (Note 11)                                                                      | • | 65.6<br>78.7<br>102 | 66.9<br>80.3<br>278/f <sub>EOSC</sub> (in  | 68.3<br>81.9<br>kHz) | ms<br>ms<br>ms    |

|                        | Conversion Time (LTC2435-1)                                | F <sub>0</sub> = 0V<br>External Oscillator (Note 11)                                                                               | • | 72<br>102           | 73.5<br>278/f <sub>EOSC</sub> (in          | 75<br>kHz)           | ms<br>ms          |

| f <sub>ISCK</sub>      | Internal SCK Frequency                                     | Internal Oscillator (Note 10), LTC2435<br>Internal Oscillator (Note 10), LTC2435-1<br>External Oscillator (Notes 10, 11)           |   |                     | 19.2<br>17.5<br>f <sub>EOSC</sub> /8       |                      | kHz<br>kHz<br>kHz |

| D <sub>ISCK</sub>      | Internal SCK Duty Cycle                                    | (Note 10)                                                                                                                          | • | 45                  |                                            | 55                   | %                 |

| f <sub>ESCK</sub>      | External SCK Frequency Range                               | (Note 9)                                                                                                                           | • |                     |                                            | 2000                 | kHz               |

| t <sub>LESCK</sub>     | External SCK Low Period                                    | (Note 9)                                                                                                                           | • | 250                 |                                            |                      | ns                |

| t <sub>HESCK</sub>     | External SCK High Period                                   | (Note 9)                                                                                                                           | • | 250                 |                                            |                      | ns                |

| t <sub>dout_isck</sub> | Internal SCK 24-Bit Data Output Time                       | Internal Oscillator (Notes 10, 12), LTC2435<br>Internal Oscillator (Notes 10, 12), LTC2435-1<br>External Oscillator (Notes 10, 11) | • | 1.22<br>1.34<br>19  | 1.25<br>1.37<br>92/f <sub>EOSC</sub> (in k | 1.28<br>1.40<br>:Hz) | ms<br>ms<br>ms    |

| t <sub>DOUT_ESCK</sub> | External SCK 24-Bit Data Output Time                       | (Note 9)                                                                                                                           | • | 2                   | 4/f <sub>ESCK</sub> (in kl                 | Hz)                  | ms                |

| t <sub>1</sub>         | $\overline{\text{CS}} \downarrow$ to SDO Low Z             |                                                                                                                                    | • | 0                   |                                            | 200                  | ns                |

| t2                     | CS ↑ to SDO High Z                                         |                                                                                                                                    | • | 0                   |                                            | 200                  | ns                |

| t3                     | $\overline{\text{CS}} \downarrow \text{to SCK} \downarrow$ | (Note 10)                                                                                                                          | • | 0                   |                                            | 200                  | ns                |

| t4                     | $\overline{\text{CS}}\downarrow$ to SCK $\uparrow$         | (Note 9)                                                                                                                           | • | 50                  |                                            |                      | ns                |

| t <sub>KQMAX</sub>     | SCK $\downarrow$ to SDO Valid                              |                                                                                                                                    | • |                     |                                            | 220                  | ns                |

| t <sub>KQMIN</sub>     | SDO Hold After SCK $\downarrow$                            | (Note 5)                                                                                                                           | • | 15                  |                                            |                      | ns                |

| t <sub>5</sub>         | SCK Set-Up Before $\overline{\text{CS}}\downarrow$         |                                                                                                                                    |   | 50                  |                                            |                      | ns                |

| t <sub>6</sub>         | SCK Hold After $\overline{\text{CS}}\downarrow$            |                                                                                                                                    |   |                     |                                            | 50                   | ns                |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All voltage values are with respect to GND.

Note 3:  $V_{CC} = 2.7$  to 5.5V unless otherwise specified.  $V_{REF} = REF^+ - REF^-$ ,  $V_{REFCM} = (REF^+ + REF^-)/2$ ;

$V_{IN} = IN^+ - IN^-, V_{INCM} = (IN^+ + IN^-)/2.$

Note 4:  $F_0$  pin tied to GND or to  $V_{CC}$  or to external conversion clock source with  $f_{EOSC} = 153600$  Hz unless otherwise specified.

Note 5: Guaranteed by design, not subject to test.

Note 6: Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

Note 7:  $F_0 = 0V$  (internal oscillator) or  $f_{EOSC} = 153600$ Hz  $\pm 2\%$ (external oscillator) for the LTC2435 or  $f_{EOSC} = 139800$ Hz  $\pm 2\%$  for the LTC2435-1.

Note 8:  $F_0 = V_{CC}$  (internal oscillator) or  $f_{EOSC} = 128000 Hz \pm 2\%$ (external oscillator).

Note 9: The converter is in external SCK mode of operation such that the SCK pin is used as digital input. The frequency of the clock signal driving SCK during the data output is  $f_{\mbox{ESCK}}$  and is expressed in kHz.

Note 10: The converter is in internal SCK mode of operation such that the SCK pin is used as digital output. In this mode of operation the SCK pin has a total equivalent load capacitance  $C_{LOAD} = 20$  pF.

Note 11: The external oscillator is connected to the  $F_0$  pin. The external oscillator frequency, f<sub>EOSC</sub>, is expressed in kHz.

Note 12: The converter uses the internal oscillator.

$F_0 = 0V \text{ or } F_0 = V_{CC}.$

Note 13: The output noise includes the contribution of the internal calibration operations.

Note 14: Refer to Offset Accuracy and Drift in the Applications Information section.

Downloaded from Elcodis.com electronic components distributor

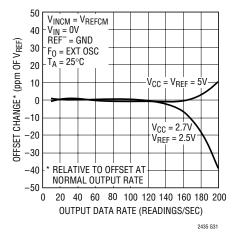

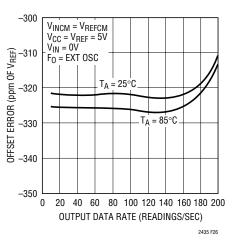

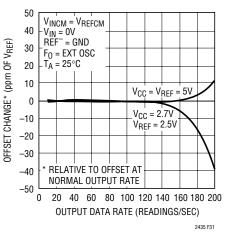

Offset Change\* vs Output Data Rate

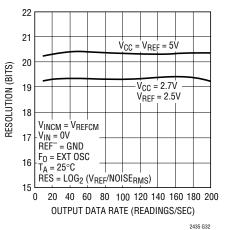

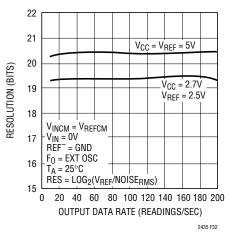

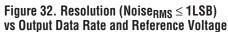

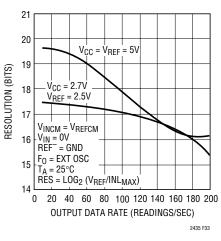

Resolution (Noise\_{RMS}  $\leq$  1LSB) vs Output Data Rate

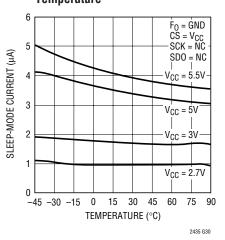

Sleep-Mode Current vs Temperature

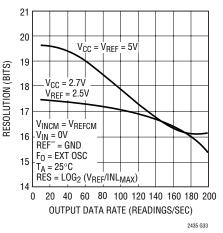

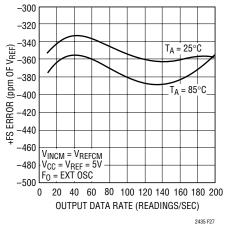

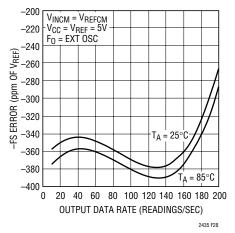

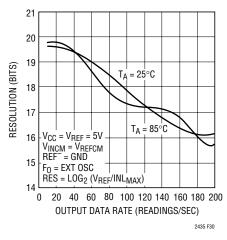

Resolution (INL\_{MAX} \leq 1LSB) vs Output Data Rate

### PIN FUNCTIONS

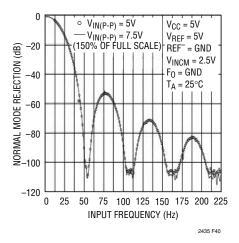

**GND (Pins 1, 7, 8, 9, 10, 15, 16):** Ground. Multiple ground pins internally connected for optimum ground current flow and  $V_{CC}$  decoupling. Connect each one of these pins to a ground plane through a low impedance connection. All seven pins must be connected to ground for proper operation.

**V<sub>CC</sub> (Pin 2):** Positive Supply Voltage. Bypass to GND (Pin 1) with a  $10\mu$ F tantalum capacitor in parallel with  $0.1\mu$ F ceramic capacitor as close to the part as possible.

**REF<sup>+</sup> (Pin 3), REF<sup>-</sup> (Pin 4):** Differential Reference Input. The voltage on these pins can have any value between GND and  $V_{CC}$  as long as the reference positive input, REF<sup>+</sup>, is maintained more positive than the reference negative input, REF<sup>-</sup>, by at least 0.1V.

**IN<sup>+</sup> (Pin 5), IN<sup>-</sup> (Pin 6):** Differential Analog Input. The voltage on these pins can have any value between GND – 0.3V and V<sub>CC</sub> + 0.3V. Within these limits the converter bipolar input range ( $V_{IN} = IN^+ - IN^-$ ) extends from – 0.5 • ( $V_{REF}$ ) to 0.5 • ( $V_{REF}$ ). Outside this input range the converter produces unique overrange and underrange output codes.

**CS** (Pin 11): Active LOW Digital Input. A LOW on this pin enables the SDO digital output and wakes up the ADC. Following each conversion, the ADC automatically enters the Sleep mode and remains in this low power state as long as  $\overline{CS}$  is HIGH. A LOW-to-HIGH transition on  $\overline{CS}$ during the Data Output transfer aborts the data transfer and starts a new conversion. **SDO (Pin 12):** Three-State Digital Output. During the Data Output period, this pin is used as serial data output. When the chip select  $\overline{CS}$  is HIGH ( $\overline{CS} = V_{CC}$ ) the SDO pin is in a high impedance state. During the Conversion and Sleep periods, this pin is used as the conversion status output. The conversion status can be observed by pulling  $\overline{CS}$  LOW.

**SCK (Pin 13):** Bidirectional Digital Clock Pin. In Internal Serial Clock Operation mode, SCK is used as digital output for the internal serial interface clock during the Data Output period. In External Serial Clock Operation mode, SCK is used as digital input for the external serial interface clock during the Data Output period. A weak internal pullup is automatically activated in Internal Serial Clock Operation mode. The Serial Clock Operation mode is determined by the logic level applied to the SCK pin at power up or during the most recent falling edge of CS.

**F**<sub>0</sub> (Pin 14): Frequency Control Pin. Digital input that controls the ADC's notch frequencies and conversion time. When the F<sub>0</sub> pin is connected to V<sub>CC</sub> (LTC2435 only), the converter uses its internal oscillator and the digital filter first null is located at 50Hz. When the F<sub>0</sub> pin is connected to GND (F<sub>0</sub> = 0V), the converter uses its internal oscillator and the digital filter first null is located at 60Hz (LTC2435) or simultaneous 50Hz/60Hz (LTC2435-1). When F<sub>0</sub> is driven by an external clock signal with a frequency f<sub>EOSC</sub>, the converter uses this signal as its system clock and the digital filter first null is located at a frequency f<sub>EOSC</sub>/2560.

V<sub>CC</sub>

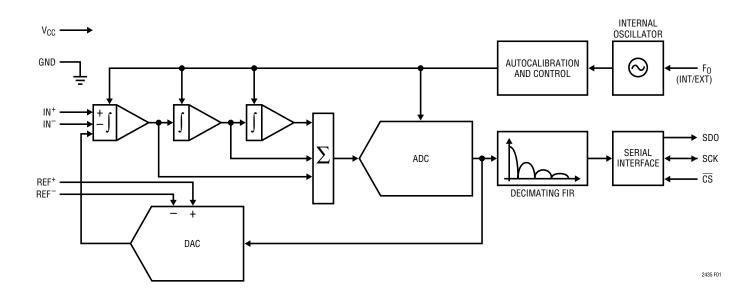

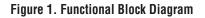

### FUNCTIONAL BLOCK DIAGRAM

**TEST CIRCUITS**

#### **CONVERTER OPERATION**

#### **Converter Operation Cycle**

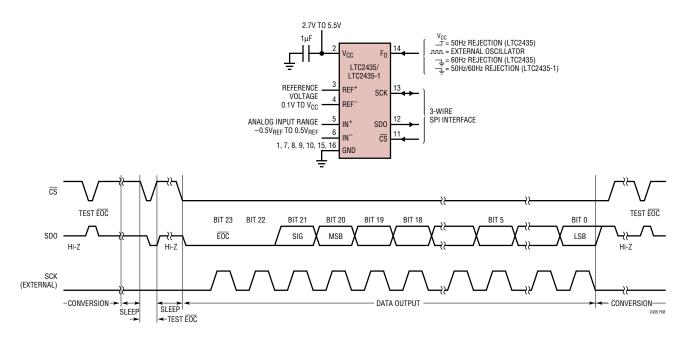

The LTC2435/LTC2435-1 are low power, delta-sigma analog-to-digital converters with an easy to use 3-wire serial interface (see Figure 1). Their operation is made up of three states. The converter operating cycle begins with the conversion, followed by the sleep state and ends with the data output (see Figure 2). The 3-wire interface consists of serial data output (SDO), serial clock (SCK) and chip select (CS).

Figure 2. LTC2435 State Transition Diagram

Initially, the LTC2435/LTC2435-1 perform a conversion. Once the conversion is complete, the device enters the sleep state. While in this sleep state, power consumption is reduced by an order of magnitude if  $\overline{CS}$  is HIGH. The part remains in the sleep state as long as  $\overline{CS}$  is HIGH. The conversion result is held indefinitely in a static shift register while the converter is in the sleep state.

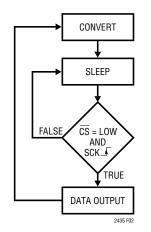

Once  $\overline{CS}$  is pulled LOW, the device exits the low power sleep mode and enters the data output state. If  $\overline{CS}$  is pulled HIGH before the first rising edge of SCK, the device returns to the sleep mode and the conversion result is still held in the internal static shift register. If CS remains LOW after the first rising edge of SCK, the device begins outputting the conversion result. Taking  $\overline{CS}$  HIGH at this point will terminate the data output state and start a new conversion. There is no latency in the conversion result. The data output corresponds to the conversion just performed. This result is shifted out on the serial data out pin (SDO) under the control of the serial clock (SCK). Data is updated on the falling edge of SCK allowing the user to reliably latch data on the rising edge of SCK (see Figure 3). The data output state is concluded once 24 bits are read out of the ADC or when  $\overline{CS}$  is brought HIGH. The device automatically initiates a new conversion and the cycle repeats.

Through timing control of the  $\overline{CS}$  and SCK pins, the LTC2435/LTC2435-1 offer several flexible modes of operation (internal or external SCK and free-running conversion modes). These various modes do not require programming configuration registers; moreover, they do not disturb the cyclic operation described above. These modes of operation are described in detail in the Serial Interface Timing Modes section.

#### **Conversion Clock**

A major advantage the delta-sigma converter offers over conventional type converters is an on-chip digital filter (commonly implemented as a Sinc or Comb filter). For high resolution, low frequency applications, this filter is typically designed to reject line frequencies of 50Hz or 60Hz plus their harmonics. The filter rejection performance is directly related to the accuracy of the converter system clock. The LTC2435/LTC2435-1 incorporate a highly accurate on-chip oscillator. This eliminates the need for external frequency setting components such as crystals or oscillators. Clocked by the on-chip oscillator, the LTC2435 achieves a minimum of 110dB rejection at the line frequency (50Hz or 60Hz  $\pm$ 2%), while the LTC2435-1 achieves a minimum of 87db rejection at 50Hz  $\pm 2\%$  and 60Hz  $\pm 2\%$  simultaneously.

#### Ease of Use

The LTC2435/LTC2435-1 data output has no latency. filter settling delay or redundant data associated with the conversion cycle. There is a one-to-one correspondence between the conversion and the output data. Therefore, multiplexing multiple analog voltages is easy.

The LTC2435/LTC2435-1 perform a full-scale calibration every conversion cycle. This calibration is transparent to the user and has no effect on the cyclic operation described above. The advantage of continuous calibration is extreme stability of full-scale readings with respect to time, supply voltage change and temperature drift.

Unlike the LTC2430, the LTC2435 and LTC2435-1 do not perform an offset calibration every conversion cycle. This enables the LTC2435/LTC2435-1 to double their output rate while maintaining line frequency rejection. The initial offset of the LTC2435/LTC2435-1 is within 5mV independent of  $V_{REF}$ . Based on the LTC2435/LTC2435-1 new modulator architecture, the temperature drift of the offset is less than 100nV/°C. More information on the LTC2435/LTC2435-1 offset is described in the Offset Accuracy and Drift section of this data sheet.

#### **Power-Up Sequence**

The LTC2435/LTC2435-1 automatically enter an internal reset state when the power supply voltage  $V_{CC}$  drops below approximately 2.2V. This feature guarantees the integrity of the conversion result and of the serial interface mode selection. (See the 2-wire I/O sections in the Serial Interface Timing Modes section.)

When the V<sub>CC</sub> voltage rises above this critical threshold, the converter creates an internal power-on-reset (POR) signal with a duration of approximately 1ms. The POR signal clears all internal registers. Following the POR signal, the LTC2435/LTC2435-1 start a normal conversion cycle and follow the succession of states described above. The first conversion result following POR is accurate within the specifications of the device if the power supply voltage is restored within the operating range (2.7V to 5.5V) before the end of the POR time interval.

#### **Reference Voltage Range**

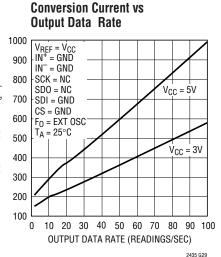

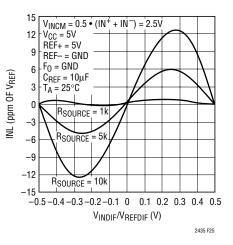

These converters accept a truly differential external reference voltage. The absolute/common mode voltage specification for the REF<sup>+</sup> and REF<sup>-</sup> pins covers the entire range from GND to  $V_{CC}$ . For correct converter operation, the REF<sup>+</sup> pin must always be more positive than the REF<sup>-</sup> pin. The LTC2435/LTC2435-1 can accept a differential reference voltage from 0.1V to  $V_{CC}$ . The converter output noise is determined by the thermal noise of the front-end circuits, and as such, its value is nearly constant with reference voltage. A decrease in reference voltage will not significantly improve the converter's effective resolution. On the other hand, a reduced reference voltage will improve the converter's overall INL performance. A reduced reference voltage will also improve the converter performance when operated with an external conversion clock (external  $F_0$  signal) at substantially higher output data rates (see the Output Data Rate section).

#### Input Voltage Range

The analog input is truly differential with an absolute/ common mode range for the IN<sup>+</sup> and IN<sup>-</sup> input pins extending from GND – 0.3V to V<sub>CC</sub> + 0.3V. Outside these limits, the ESD protection devices begin to turn on and the errors due to input leakage current increase rapidly. Within these limits, the LTC2435/LTC2435-1 convert the bipolar differential input signal, V<sub>IN</sub> = IN<sup>+</sup> – IN<sup>-</sup>, from –FS =  $-0.5 \cdot V_{REF}$  to +FS =  $0.5 \cdot V_{REF}$  where V<sub>REF</sub> = REF<sup>+</sup> – REF<sup>-</sup>. Outside this range, the converters indicate the overrange or the underrange condition using distinct output codes.

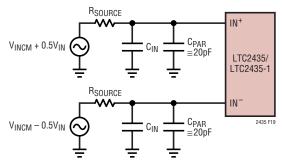

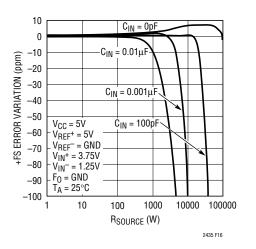

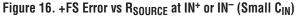

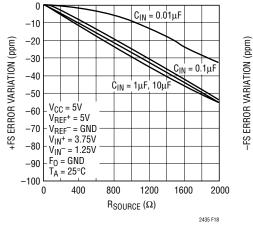

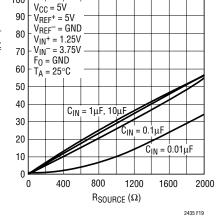

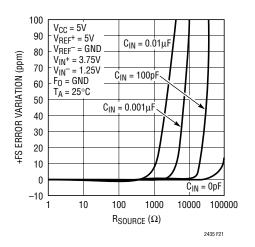

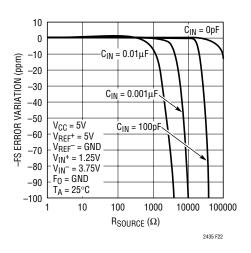

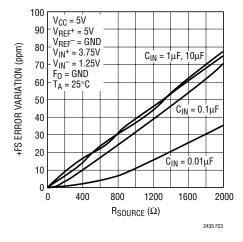

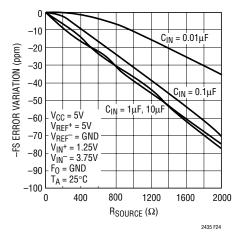

Input signals applied to IN<sup>+</sup> and IN<sup>-</sup> pins may extend by 300mV below ground and above V<sub>CC</sub>. In order to limit any fault current, resistors of up to 5k may be added in series with the IN<sup>+</sup> and IN<sup>-</sup> pins without affecting the performance of the device. In the physical layout, it is important to maintain the parasitic capacitance of the connection between these series resistors and the corresponding pins as low as possible; therefore, the resistors should be located as close as practical to the pins. The effect of the series resistance on the converter accuracy can be evaluated from the curves presented in the Input Current/ Reference Current sections. In addition, series resistors will introduce a temperature dependent offset error due to the input leakage current. A 1nA input leakage current will develop a 1ppm offset error on a 5k resistor if  $V_{\text{RFF}} = 5V$ . This error has a very strong temperature dependency.

#### **Output Data Format**

The LTC2435/LTC2435-1 serial output data stream is 24 bits long. The first 3 bits represent status information indicating the sign and conversion state. The next 21 bits are the conversion result, MSB first. The third and fourth bit together are also used to indicate an underrange condition (the differential input voltage is below –FS) or an overrange condition (the differential input voltage is above +FS).

Bit 23 (first output bit) is the end of conversion ( $\overline{EOC}$ ) indicator. This bit is available at the SDO pin during the conversion and sleep states whenever the  $\overline{CS}$  pin is LOW. This bit is HIGH during the conversion and goes LOW when the conversion is complete.

Bit 22 (second output bit) is a dummy bit (DMY) and is always LOW.

Bit 21 (third output bit) is the conversion result sign indicator (SIG). If V<sub>IN</sub> is >0, this bit is HIGH. If V<sub>IN</sub> is <0, this bit is LOW.

Bit 20 (fourth output bit) is the most significant bit (MSB) of the result. This bit in conjunction with Bit 21 also provides the underrange or overrange indication. If both Bit 21 and Bit 20 are HIGH, the differential input voltage is above +FS. If both are LOW, the differential input voltage is below –FS.

The function of these bits is summarized in Table 1.

| Input Range                            | Bit 23<br>EOC | Bit 22<br>DMY | Bit 21<br>SIG | Bit 20<br>MSB |

|----------------------------------------|---------------|---------------|---------------|---------------|

| $V_{IN} \ge 0.5 \bullet V_{REF}$       | 0             | 0             | 1             | 1             |

| $0V \le V_{IN} < 0.5 \bullet V_{REF}$  | 0             | 0             | 1             | 0             |

| $-0.5 \bullet V_{REF} \le V_{IN} < 0V$ | 0             | 0             | 0             | 1             |

| $V_{IN} < -0.5 \bullet V_{REF}$        | 0             | 0             | 0             | 0             |

#### Table 1. LTC2435/LTC2435-1 Status Bits

Bits 20-0 are the 21-bit conversion result MSB first.

Bit 0 is the least significant bit (LSB).

Data is shifted out of the SDO pin under control of the serial clock (SCK), see Figure 3. Whenever  $\overline{CS}$  is HIGH, SDO remains high impedance and any externally generated

SCK clock pulses are ignored by the internal data out shift register.

In order to shift the conversion result out of the device,  $\overline{CS}$  must first be driven LOW. EOC is seen at the SDO pin of the device once  $\overline{CS}$  is pulled LOW. EOC changes real time from HIGH to LOW at the completion of a conversion. This signal may be used as an interrupt for an external microcontroller. Bit 23 (EOC) can be captured on the first rising edge of SCK. Bit 22 is shifted out of the device on the first falling edge of SCK. The final data bit (Bit 0) is shifted out on the falling edge of the 24th SCK pulse. On the falling edge of the 24th SCK pulse. On the falling edge of the 24th SCK pulse as EOC (Bit 23) for the next conversion cycle. This bit serves as EOC (Bit 23) for the next conversion cycle. Table 2 summarizes the output data format.

As long as the voltage on the IN<sup>+</sup> and IN<sup>-</sup> pins is maintained within the -0.3V to ( $V_{CC} + 0.3V$ ) absolute maximum operating range, a conversion result is generated for any differential input voltage  $V_{IN}$  from  $-FS = -0.5 \cdot V_{REF}$  to  $+FS = 0.5 \cdot V_{REF}$ . For differential input voltages greater than +FS, the conversion result is clamped to the value corresponding to the +FS. For differential input voltages below -FS, the conversion result is clamped to the value corresponding to -FS - 1LSB.

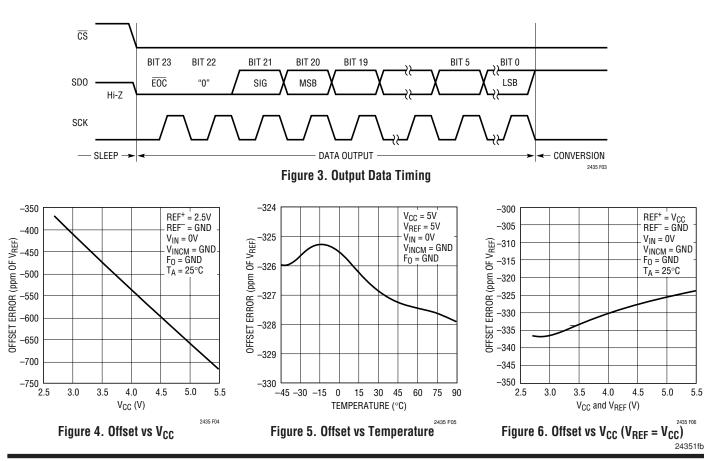

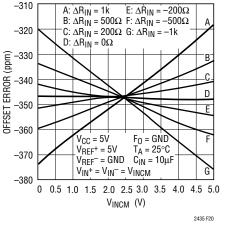

#### **Offset Accuracy and Drift**

Unlike the LTC2430 and most of the LTC2400 family, the LTC2435/LTC2435-1 do not perform an offset calibration every cycle. The reason for this is to increase the data output rate while maintaining line frequency rejection.

While the initial accuracy of the LTC2435/LTC2435-1 offset is within 5mV (see Figure 4), several unique properties of the LTC2435/LTC2435-1 architecture nearly eliminate the drift of the offset error with respect to temperature and supply.

As shown in Figure 5, the offset variation with temperature is less than 3ppm over the complete temperature range of  $-50^{\circ}$ C to  $100^{\circ}$ C. This corresponds to a temperature drift of 0.022ppm/°C.

While the variation in offset with supply voltage is propor-

tional to  $V_{CC}$  (see Figure 4), several characteristics of this variation can be used to eliminate the effects. First, the variation with respect to supply voltage is linear. Second, the magnitude of the offset error decreases with decreased supply voltage. Third, the offset error in microvolts is almost independent with reference and therefore

the offset in ppm is inverse proportional to reference voltage. As a result, by tying  $V_{CC}$  to  $V_{REF}$ , the variation with supply can be reduced, see Figure 6. The variation with supply is less than 15ppm over the entire 2.7V to 5.5V supply range.

Frequency Rejection Selection LTC2435 (F<sub>0</sub>)

| Table 2. L162435/L162435                        |               | ala Furina    | 11            |               |        |        |        |           |

|-------------------------------------------------|---------------|---------------|---------------|---------------|--------|--------|--------|-----------|

| Differential Input Voltage<br>V <sub>IN</sub> * | Bit 23<br>EOC | Bit 22<br>DMY | Bit 21<br>SIG | Bit 20<br>MSB | Bit 19 | Bit 18 | Bit 17 | <br>Bit O |

| $V_{IN}^* \ge 0.5 \bullet V_{REF}^{**}$         | 0             | 0             | 1             | 1             | 0      | 0      | 0      | <br>0     |

| 0.5 • V <sub>REF</sub> ** – 1LSB                | 0             | 0             | 1             | 0             | 1      | 1      | 1      | <br>1     |

| 0.25 • V <sub>REF</sub> **                      | 0             | 0             | 1             | 0             | 1      | 0      | 0      | <br>0     |

| 0.25 • V <sub>REF</sub> ** – 1LSB               | 0             | 0             | 1             | 0             | 0      | 1      | 1      | <br>1     |

| 0                                               | 0             | 0             | 1             | 0             | 0      | 0      | 0      | <br>0     |

| -1LSB                                           | 0             | 0             | 0             | 1             | 1      | 1      | 1      | <br>1     |

| -0.25 • V <sub>REF</sub> **                     | 0             | 0             | 0             | 1             | 1      | 0      | 0      | <br>0     |

| –0.25 • V <sub>REF</sub> ** – 1LSB              | 0             | 0             | 0             | 1             | 0      | 1      | 1      | <br>1     |

| -0.5 • V <sub>REF</sub> **                      | 0             | 0             | 0             | 1             | 0      | 0      | 0      | <br>0     |

| V <sub>IN</sub> * < -0.5 • V <sub>REF</sub> **  | 0             | 0             | 0             | 0             | 1      | 1      | 1      | <br>1     |

| Table | 2.       | LTC2435/I | TC2435-1 | Output | Data | Format  |

|-------|----------|-----------|----------|--------|------|---------|

| 10010 | <u> </u> | LI0L400/1 |          | output | Dutu | i ormat |

\*The differential input voltage  $V_{IN} = IN^+ - IN^-$ .

\*\*The differential reference voltage  $V_{REF} = REF^+ - REF^-$ .

Downloaded from Elcodis.com electronic components distributor

15

The LTC2435 internal oscillator provides better than 110dB normal mode rejection at the line frequency and its harmonics for 50Hz  $\pm 2\%$  or 60Hz  $\pm 2\%$ . For 60Hz rejection, F<sub>0</sub> should be connected to GND while for 50Hz rejection the F<sub>0</sub> pin should be connected to V<sub>CC</sub>.

The selection of 50Hz or 60Hz rejection can also be made by driving  $F_0$  to an appropriate logic level. A selection change during the sleep or data output states will not disturb the converter operation. If the selection is made during the conversion state, the result of the conversion in progress may be outside specifications but the following conversions will not be affected.

When a fundamental rejection frequency different from 50Hz or 60Hz is required or when the converter must be synchronized with an outside source, the LTC2435 can operate with an external conversion clock. The converter automatically detects the presence of an external clock signal at the F<sub>0</sub> pin and turns off the internal oscillator. The frequency  $f_{EOSC}$  of the external signal must be at least 5kHz to be detected. The external clock signal duty cycle is not significant as long as the minimum and maximum specifications for the high and low periods  $t_{HE0}$  and  $t_{LE0}$  are observed.

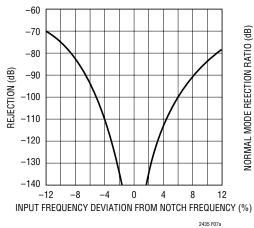

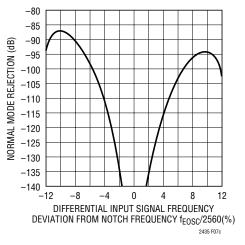

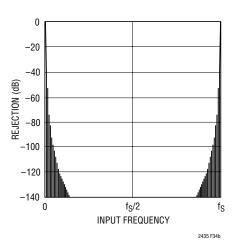

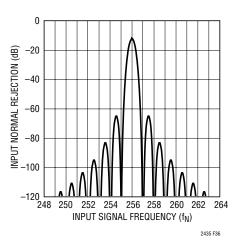

While operating with an external conversion clock of a frequency  $f_{EOSC}$ , the LTC2435 provides better than 110dB normal mode rejection in a frequency range  $f_{EOSC}/2560 \pm 4\%$  and its harmonics. The normal mode rejection as a function of the input frequency deviation from  $f_{EOSC}/2560$  is shown in Figure 7a.

Whenever an external clock is not present at the  $F_0$  pin, the converter automatically activates its internal oscillator and enters the Internal Conversion Clock mode. The LTC2435 operation will not be disturbed if the change of conversion clock source occurs during the sleep state or during the data output state while the converter uses an external serial clock. If the change occurs during the conversion state, the result of the conversion in progress may be outside specifications but the following conversions will not be affected.

If the change occurs during the data output state and the converter is in the Internal SCK mode, the serial clock duty cycle may be affected but the serial data stream will remain valid.

Table 3a summarizes the duration of each state and the achievable output data rate as a function of  $\mathrm{F}_{\mathrm{O}}.$

#### Frequency Rejection Selection LTC2435-1 (F<sub>0</sub>)

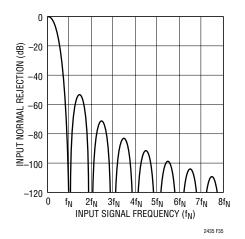

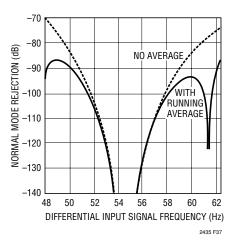

The LTC2435-1 internal oscillator provides better than 87dB normal mode rejection over the range of 49Hz to 61.2Hz as shown in Figure 7b. For simultaneous 50Hz/60Hz rejection,  $F_0$  should be connected to GND.

In order to achieve 87dB normal mode rejection of 50Hz  $\pm 2\%$  and 60Hz  $\pm 2\%$ , two consecutive conversions must be averaged. By performing a continuous running average of the two most current results, both simultaneous rejection is achieved and a nearly 2× increase in throughput is realized relative to the LTC2430 (see Normal Mode Rejection, Ouput Rate and Running Averages sections of this data sheet).

When a fundamental rejection frequency different from the range 49Hz to 61.2Hz is required or when the converter must be synchronized with an outside source, the LTC2435-1 can operate with an external conversion clock. The performance of the LTC2435-1 is the same as the LTC2435 when driven by an external conversion clock at the  $F_0$  pin.

Table 3b summarizes the duration of each state and the achievable output data rate as a function of  ${\sf F}_0.$

#### Serial Interface Pins

The LTC2435/LTC2435-1 transmit the conversion results and receive the start of conversion command through a synchronous 3-wire interface. During the conversion and sleep states, this interface can be used to assess the converter status and during the data output state it is used to read the conversion result.

Figure 7a. LTC2435/LTC2435-1 Normal Mode Rejection When Using an External Oscillator of Frequency f<sub>EOSC</sub> without Running Averages

Figure 7b. LTC2435-1 Normal Mode Rejection When Using an Internal Oscillator with Running Averages

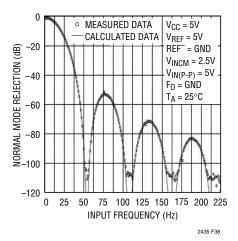

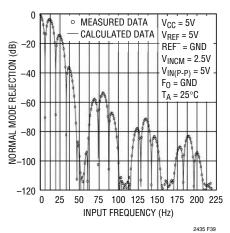

Figure 7c. LTC2435/LTC2435-1 Normal Mode Rejection When Using an External Oscillator of Frequency f<sub>EOSC</sub> with Running Averages

| Table 3a. | LTC2435 | State | Duration |

|-----------|---------|-------|----------|

|           |         |       |          |

| State       | Operating Mode                                            |                                                                                        | Duration                                                                                      |

|-------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| CONVERT     | Internal Oscillator                                       | $F_0 = LOW$ , (60Hz Rejection)                                                         | 67ms, Output Data Rate ≤ 15 Readings/s                                                        |

|             |                                                           | F <sub>0</sub> = HIGH, (50Hz Rejection)                                                | 80ms, Output Data Rate ≤ 12.4 Readings/s                                                      |

|             | External Oscillator                                       | $F_0$ = External Oscillator with Frequency $f_{EOSC}$ kHz ( $f_{EOSC}/2560$ Rejection) | 10278/ $f_{EOSC}$ s, Output Data Rate $\leq f_{EOSC}$ /10278 Readings/s                       |

| SLEEP       |                                                           |                                                                                        | As Long As $\overline{CS}$ = HIGH                                                             |

| DATA OUTPUT | Internal Serial Clock                                     | $F_0 = LOW/HIGH$ , (Internal Oscillator)                                               | As Long As $\overline{CS}$ = LOW But Not Longer Than 1.25ms (24 SCK cycles)                   |

|             |                                                           | F <sub>O</sub> = External Oscillator with<br>Frequency f <sub>EOSC</sub> kHz           | As Long As $\overline{CS}$ = LOW But Not Longer Than 192/f <sub>EOSC</sub> ms (24 SCK cycles) |

|             | External Serial Clock with Frequency f <sub>SCK</sub> kHz |                                                                                        | As Long As $\overline{CS}$ = LOW But Not Longer Than 24/f <sub>SCK</sub> ms (24 SCK cycles)   |

#### Table 3b. LTC2435-1 State Duration

| State       | Operating Mode                                            |                                                                                        | Duration                                                                                      |

|-------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| CONVERT     | Internal Oscillator                                       | F <sub>0</sub> = LOW<br>Simultaneous 50Hz/60Hz Rejection                               | 73ms, Output Data Rate ≤ 14 Readings/s                                                        |

|             | External Oscillator                                       | $F_0$ = External Oscillator with Frequency $f_{EOSC}$ kHz ( $f_{EOSC}/2560$ Rejection) | 10278/ $f_{EOSC}$ s, Output Data Rate $\leq f_{EOSC}$ /10278 Readings/s                       |

| SLEEP       |                                                           | ·                                                                                      | As Long As $\overline{CS}$ = HIGH                                                             |

| DATA OUTPUT | Internal Serial Clock                                     | F <sub>0</sub> = LOW (Internal Oscillator)                                             | As Long As $\overline{CS}$ = LOW But Not Longer Than 1.4ms (24 SCK cycles)                    |

|             |                                                           | F <sub>O</sub> = External Oscillator with<br>Frequency f <sub>EOSC</sub> kHz           | As Long As $\overline{CS}$ = LOW But Not Longer Than 192/f <sub>EOSC</sub> ms (24 SCK cycles) |

|             | External Serial Clock with Frequency f <sub>SCK</sub> kHz |                                                                                        | As Long As $\overline{CS}$ = LOW But Not Longer Than 24/f <sub>SCK</sub> ms (24 SCK cycles)   |

#### Serial Clock Input/Output (SCK)

The serial clock signal present on SCK (Pin 13) is used to synchronize the data transfer. Each bit of data is shifted out the SDO pin on the falling edge of the serial clock.

In the Internal SCK mode of operation, the SCK pin is an output and the LTC2435/LTC2435-1 create their own serial clock by dividing the internal conversion clock by 8. In the External SCK mode of operation, the SCK pin is used as input. The internal or external SCK mode is selected on power-up and then reselected every time a HIGH-to-LOW transition is detected at the  $\overline{\text{CS}}$  pin. If SCK is HIGH or floating at power-up or during this transition, the converter enters the internal SCK mode. If SCK is LOW at power-up or during this transition, the external SCK mode.

#### Serial Data Output (SDO)

The serial data output pin, SDO (Pin 12), provides the result of the last conversion as a serial bit stream (MSB first) during the data output state. In addition, the SDO pin is used as an end of conversion indicator during the conversion and sleep states.

When  $\overline{CS}$  (Pin 11) is HIGH, the SDO driver is switched to a high impedance state. This allows sharing the serial interface with other devices. If  $\overline{CS}$  is <u>LOW</u> during the convert or sleep state, SDO will output EOC. If  $\overline{CS}$  is LOW during the conversion phase, the EOC bit appears HIGH on the SDO pin. Once the conversion is complete, EOC goes LOW.

#### Table 4. LTC2435/LTC2435-1 Interface Timing Modes

#### Chip Select Input $(\overline{CS})$

The active LOW chip select,  $\overline{CS}$  (Pin 11), is used to test the conversion status and to enable the data output transfer as described in the previous sections.

In addition, the  $\overline{\text{CS}}$  signal can be used to trigger a new conversion cycle before the entire serial data transfer has been completed. The LTC2435/LTC2435-1 will abort any serial data transfer in progress and start a new conversion cycle anytime a LOW-to-HIGH transition is detected at the  $\overline{\text{CS}}$  pin after the converter has entered the data output state (i.e., after the first rising edge of SCK occurs with  $\overline{\text{CS}}$  = LOW).

Finally,  $\overline{CS}$  can be used to control the free-running modes of operation, see Serial Interface Timing Modes section. Grounding  $\overline{CS}$  will force the ADC to continuously convert at the maximum output rate selected by F<sub>0</sub>.

#### SERIAL INTERFACE TIMING MODES

The LTC2435/LTC2435-1 3-wire interface is SPI and MICROWIRE compatible. This interface offers several flexible modes of operation. These include internal/external serial clock, 2- or 3-wire I/O, single cycle conversion and autostart. The following sections describe each of these serial interface timing modes in detail. In all these cases, the converter can use the internal oscillator ( $F_0$  = LOW or  $F_0$  = HIGH) or an external oscillator connected to the  $F_0$  pin. Refer to Table 4 for a summary.

| Configuration                                   | SCK<br>Source | Conversion<br>Cycle<br>Control     | Data<br>Output<br>Control          | Connection<br>and<br>Waveforms |

|-------------------------------------------------|---------------|------------------------------------|------------------------------------|--------------------------------|

| External SCK, Single Cycle Conversion           | External      | CS and SCK                         | CS and SCK                         | Figures 8, 9                   |

| External SCK, 2-Wire I/O                        | External      | SCK                                | SCK                                | Figure 10                      |

| Internal SCK, Single Cycle Conversion           | Internal      | $\overline{\texttt{CS}}\downarrow$ | $\overline{\texttt{CS}}\downarrow$ | Figures 11, 12                 |

| Internal SCK, 2-Wire I/O, Continuous Conversion | Internal      | Continuous                         | Internal                           | Figure 13                      |

## External Serial Clock, Single Cycle Operation (SPI/MICROWIRE Compatible)

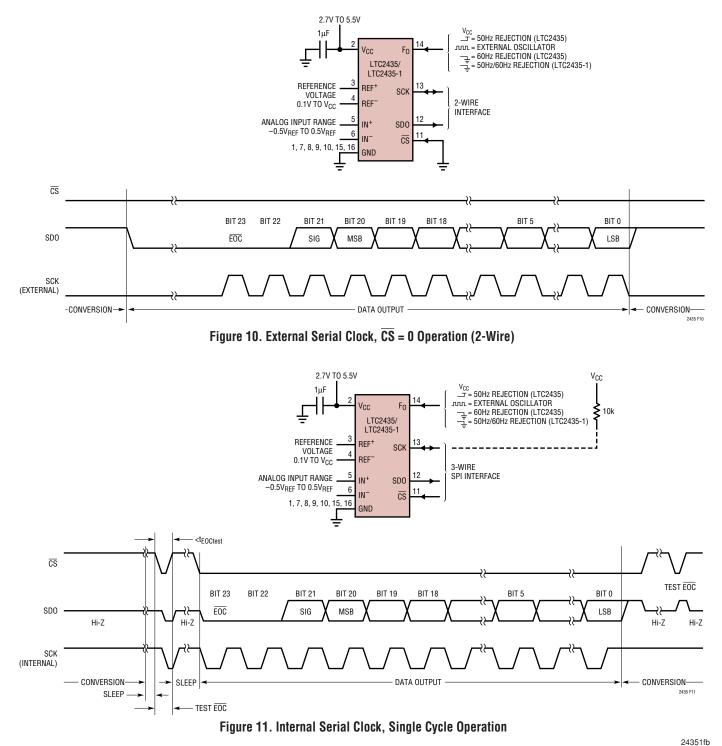

This timing mode uses an external serial clock to shift out the conversion result and a  $\overline{CS}$  signal to monitor and control the state of the conversion cycle, see Figure 8.

The serial clock mode is selected on the falling edge of  $\overline{CS}$ . To select the external serial clock mode, the serial clock pin (SCK) must be LOW during each  $\overline{CS}$  falling edge.

The serial data output pin (SDO) is Hi-Z as long as  $\overline{CS}$  is HIGH. At any time during the conversion cycle,  $\overline{CS}$  may be pulled LOW in order to monitor the state of the converter. While  $\overline{CS}$  is pulled LOW,  $\overline{EOC}$  is output to the SDO pin.  $\overline{EOC} = 1$  while a conversion is in progress and  $\overline{EOC} = 0$  if the conversion is over. With  $\overline{CS}$  HIGH, the device automatically enters the sleep state once the conversion is complete.

When  $\overline{\text{CS}}$  is low, the device enters the data output mode. The result is held in the internal static shift register until the first SCK rising edge is seen while  $\overline{\text{CS}}$  is LOW. Data is shifted out the SDO pin on each falling edge of SCK. This enables external circuitry to latch the output on the rising edge of SCK.  $\overline{\text{EOC}}$  can be latched on the first rising edge of SCK and the last bit of the conversion result can be latched on the 24th rising edge of SCK. On the 24th falling edge of SCK, the device begins a new conversion. SDO goes HIGH ( $\overline{EOC} = 1$ ) indicating a conversion is in progress.

At the conclusion of the data cycle,  $\overline{\text{CS}}$  may remain LOW and  $\overline{\text{EOC}}$  monitored as an end-of-conversion interrupt. Alternatively,  $\overline{\text{CS}}$  may be driven HIGH setting SDO to Hi-Z. As described above,  $\overline{\text{CS}}$  may be pulled LOW at any time in order to monitor the conversion status.

Typically,  $\overline{CS}$  remains LOW during the data output state. However, the data output state may be aborted by pulling  $\overline{CS}$  HIGH anytime between the first rising edge and the 24th falling edge of SCK, see Figure 9. On the rising edge of  $\overline{CS}$ , the device aborts the data output state and immediately initiates a new conversion. This is useful for systems not requiring all 24 bits of output data, aborting an invalid conversion cycle or synchronizing the start of a conversion.

#### External Serial Clock, 2-Wire I/O

This timing mode utilizes a 2-wire serial I/O interface. The conversion result is shifted out of the device by an externally generated serial clock (SCK) signal, see Figure 10.  $\overline{CS}$  may be permanently tied to ground, simplifying the user interface or isolation barrier.

Figure 9. External Serial Clock, Reduced Data Output Length

The external serial clock mode is selected at the end of the power-on reset (POR) cycle. The POR cycle is concluded approximately 1ms after  $V_{CC}$  exceeds 2.2V. The level applied to SCK at this time determines if SCK is internal or external. SCK must be driven LOW prior to the end of POR in order to enter the external serial clock timing mode.

Since  $\overline{CS}$  is tied LOW, the end-of-conversion ( $\overline{EOC}$ ) can be continuously monitored at the SDO pin during the convert and sleep states.  $\overline{EOC}$  may be used as an interrupt to an external controller indicating the conversion result is ready.  $\overline{EOC} = 1$  while the conversion is in progress and  $\overline{EOC} = 0$  once the conversion is over. On the falling edge of  $\overline{EOC}$ , the conversion result is loaded into an internal static shift register. Data is shifted out the SDO pin on each falling edge of SCK enabling external circuitry to latch data on the rising edge of SCK. EOC can be latched on the first rising edge of SCK. On the 24th falling edge of SCK, SDO goes HIGH ( $\overline{EOC} = 1$ ) indicating a new conversion has begun.

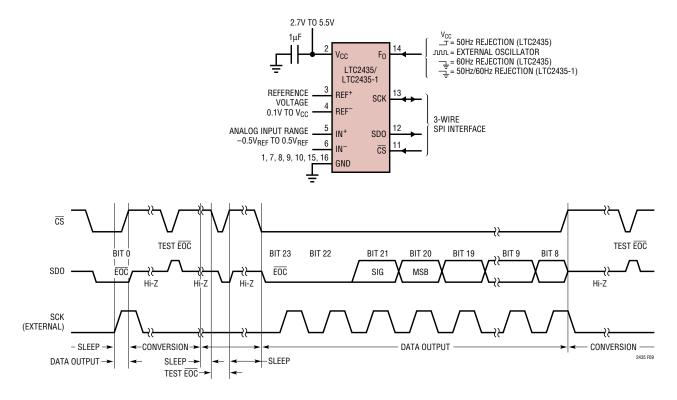

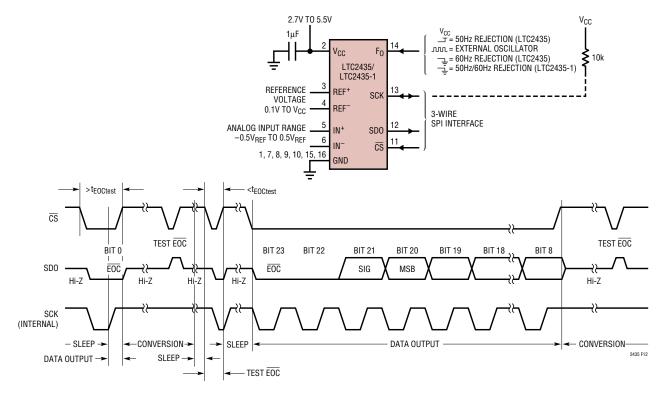

#### Internal Serial Clock, Single Cycle Operation

This timing mode uses an internal serial clock to shift out the conversion result and a  $\overline{CS}$  signal to monitor and control the state of the conversion cycle, see Figure 11.

In order to select the internal serial clock timing mode, the serial clock pin (SCK) must be floating (Hi-Z) or pulled HIGH prior to the falling edge of  $\overline{CS}$ . The device will not enter the internal serial clock mode if SCK is driven LOW on the falling edge of  $\overline{CS}$ . An internal weak pull-up resistor is active on the SCK pin during the falling edge of  $\overline{CS}$ ; therefore, the internal serial clock timing mode is automatically selected if SCK is not externally driven.

The serial data output pin (SDO) is Hi-Z as long as  $\overline{CS}$  is HIGH. At any time during the conversion cycle,  $\overline{CS}$  may be pulled LOW in order to monitor the state of the converter. Once  $\overline{CS}$  is pulled LOW, SCK goes LOW and  $\overline{EOC}$  is output to the SDO pin.  $\overline{EOC} = 1$  while a conversion is in progress and  $\overline{EOC} = 0$  if the conversion is over.

When testing  $\overline{EOC}$ , if the conversion is complete ( $\overline{EOC} = 0$ ), the device will exit the sleep state and enter the data output state. In order to allow the device to return to the sleep state,  $\overline{CS}$  must be pulled HIGH before the first rising edge of SCK. In the internal SCK timing mode, SCK goes HIGH

and the device begins outputting data at time  $t_{EOCtest}$  after the falling edge of  $\overline{CS}$  (if EOC = 0) or  $t_{EOCtest}$  after  $\overline{EOC}$  goes LOW (if  $\overline{CS}$  is LOW during the falling edge of  $\overline{EOC}$ ). The value of  $t_{EOCtest}$  is 23µs (LTC2435), 26µs (LTC2435-1) if the device is using its internal oscillator (F<sub>0</sub> = logic LOW or

HIGH). If F<sub>0</sub> is driven by an external oscillator of frequency  $f_{EOSC}$ , then  $t_{EOCtest}$  is 3.6/ $f_{EOSC}$ . If CS is pulled HIGH before time  $t_{EOCtest}$ , the device returns to the sleep state. The conversion result is held in the internal static shift register.

If  $\overline{\text{CS}}$  remains LOW longer than  $t_{\text{EOCtest}}$ , the first rising edge of SCK will occur and the conversion result is serially shifted out of the SDO pin. The data output cycle begins on this first rising edge of SCK and concludes after the 24th rising edge. Data is shifted out the SDO pin on each falling edge of SCK. The internally generated serial clock is output to the SCK pin. This signal may be used to shift the conversion result into external circuitry. EOC can be latched on the first rising edge of SCK and the last bit of the conversion result on the 24th rising edge of SCK. After the 24th rising edge, SDO goes HIGH (EOC = 1), SCK stays HIGH and a new conversion starts.

Typically,  $\overline{CS}$  remains LOW during the data output state. However, the data output state may be aborted by pulling  $\overline{CS}$  HIGH anytime between the first and 24th rising edge of SCK, see Figure 12. On the rising edge of  $\overline{CS}$ , the device aborts the data output state and immediately initiates a new conversion. This is useful for systems not requiring all 24 bits of output data, aborting an invalid conversion cycle, or synchronizing the start of a conversion. If  $\overline{CS}$  is pulled HIGH while the converter is driving SCK LOW, the internal pull-up is not available to restore SCK to a logic HIGH state. This will cause the device to exit the internal serial clock mode on the next falling edge of  $\overline{CS}$ . This can be avoided by adding an external 10k pull-up resistor to the SCK pin or by never pulling  $\overline{CS}$  HIGH when SCK is LOW.

Whenever SCK is LOW, the LTC2435/LTC2435-1 internal pull-up at pin SCK is disabled. Normally, SCK is not externally driven if the device is in the internal SCK timing mode. However, certain applications may require an external driver on SCK. If this driver goes Hi-Z after outputting a LOW signal, the LTC2435/LTC2435-1 internal pull-up remains disabled. Hence, SCK remains LOW. On the next falling edge of  $\overline{CS}$ , the device is switched to the external SCK timing mode. By adding an external 10k pull-up resistor to SCK, this pin goes HIGH once the external driver goes Hi-Z. On the next  $\overline{CS}$  falling edge, the device will remain in the internal SCK timing mode.

Figure 12. Internal Serial Clock, Reduced Data Output Length

24351fb

22

A similar situation may occur during the sleep state when  $\overline{CS}$  is pulsed HIGH-LOW-HIGH in order to test the conversion status. If the device is in the sleep state ( $\overline{EOC} = 0$ ), SCK will go LOW. Once  $\overline{CS}$  goes HIGH (within the time period defined above as  $t_{EOCtest}$ ), the internal pull-up is activated. For a heavy capacitive load on the SCK pin, the internal pull-up may not be adequate to return SCK to a HIGH level before  $\overline{CS}$  goes low again. This is not a concern under normal conditions where  $\overline{CS}$  remains LOW after detecting  $\overline{EOC} = 0$ . This situation is easily overcome by adding an external 10k pull-up resistor to the SCK pin.

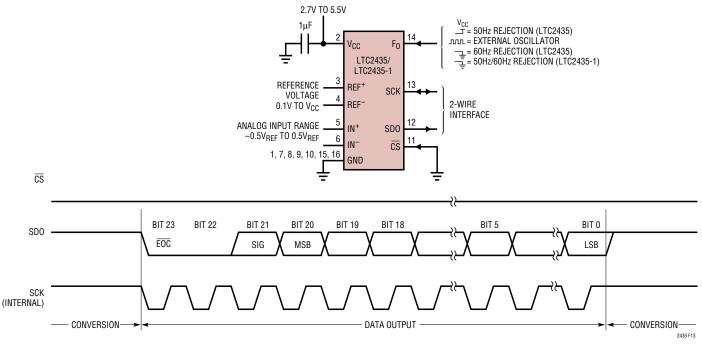

#### Internal Serial Clock, 2-Wire I/O, Continuous Conversion

This timing mode uses a 2-wire, all output (SCK and SDO) interface. The conversion result is shifted out of the device by an internally generated serial clock (SCK) signal, see Figure 13.  $\overrightarrow{\text{CS}}$  may be permanently tied to ground, simplifying the user interface or isolation barrier.

The internal serial clock mode is selected at the end of the power-on reset (POR) cycle. The POR cycle is concluded

approximately 1ms after  $V_{CC}$  exceeds 2.2V. An internal weak pull-up is active during the POR cycle; therefore, the internal serial clock timing mode is automatically selected if SCK is not externally driven LOW (if SCK is loaded such that the internal pull-up cannot pull the pin HIGH, the external SCK mode will be selected).

During the conversion, the SCK and the serial data output pin (SDO) are HIGH ( $\overline{EOC} = 1$ ). Once the conversion is complete, SCK and SDO go LOW ( $\overline{EOC} = 0$ ) indicating the conversion has finished. The data output cycle begins on the first rising edge of SCK and ends after the 24th rising edge. Data is shifted out the SDO pin on each falling edge of SCK. The internally generated serial clock is output to the SCK pin. This signal may be used to shift the conversion result into external circuitry. EOC can be latched on the first rising edge of SCK and the last bit of the conversion result can be latched on the 24th rising edge of SCK. After the 24th rising edge, SDO goes HIGH ( $\overline{EOC}$ = 1) indicating a new conversion is in progress. SCK

Figure 13. Internal Serial Clock, Continuous Operation

#### PRESERVING THE CONVERTER ACCURACY

The LTC2435/LTC2435-1 are designed to reduce as much as possible conversion result sensitivity to device decoupling, PCB layout, antialiasing circuits, line frequency perturbations and so on. Nevertheless, in order to preserve the extreme accuracy capability of this part, some simple precautions are desirable.

#### **Digital Signal Levels**

The LTC2435/LTC2435-1 digital interface is easy to use. Its digital inputs ( $F_0$ ,  $\overline{CS}$  and SCK in External SCK mode of operation) accept standard TTL/CMOS logic levels and the internal hysteresis receivers can tolerate edge rates as slow as 100µs. However, some considerations are required to take advantage of the exceptional accuracy and low supply current of this converter.

The digital output signals (SDO and SCK in Internal SCK mode of operation) are less of a concern because they are not generally active during conversion.

While a digital input signal is in the range 0.5V to  $(V_{CC} - 0.5V)$ , the CMOS input receiver draws additional current from the power supply. It should be noted that, when any one of the digital input signals ( $F_0$ ,  $\overline{CS}$  and SCK in External SCK mode of operation) is within this range, the LTC2435/LTC2435-1 power supply current may increase even if the signal in question is at a valid logic level. For micropower operation, it is recommended to drive all digital input signals to full CMOS levels  $[V_{II} < 0.4V]$  and  $V_{OH} > (V_{CC} - 0.4V)].$

During the conversion period, the undershoot and/or overshoot of a fast digital signal connected to the LTC2435/ LTC2435-1 pins may severely disturb the analog to digital conversion process. Undershoot and overshoot can occur because of the impedance mismatch at the converter pin when the transition time of an external control signal is less than twice the propagation delay from the driver to LTC2435/LTC2435-1. For reference, on a regular FR-4 board, signal propagation velocity is approximately 183ps/inch for internal traces and 170ps/inch for surface traces. Thus, a driver generating a control signal with a minimum transition time of 1ns must be connected to the

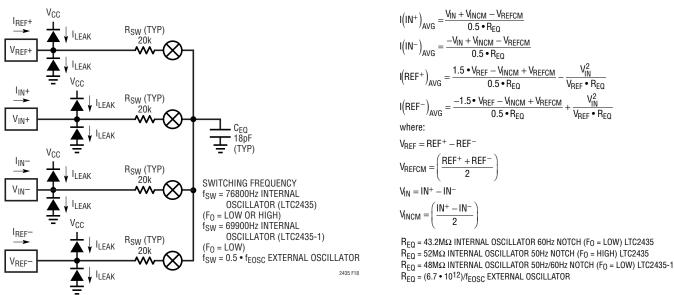

converter pin through a trace shorter than 2.5 inches. This problem becomes particularly difficult when shared control lines are used and multiple reflections may occur. The solution is to carefully terminate all transmission lines close to their characteristic impedance.