## LC<sup>2</sup>MOS Signal Conditioning ADC

AD7712\*

**FEATURES**

Charge Balancing ADC

24 Bits No Missing Codes

±0.0015% Nonlinearity

High Level and Low Level Analog Input Channels

Programmable Gain for Both Inputs

Gains from 1 to 128

Differential Input for Low Level Channel

Low-Pass Filter with Programmable Filter Cutoffs

Ability to Read/Write Calibration Coefficients

Bidirectional Microcontroller Serial Interface

Internal/External Reference Option

Single- or Dual-Supply Operation

Low Power (25 mW typ) with Power-Down Mode

APPLICATIONS

Process Control

Smart Transmitters

Portable Industrial Instruments

### **GENERAL DESCRIPTION**

(100 µW typ)

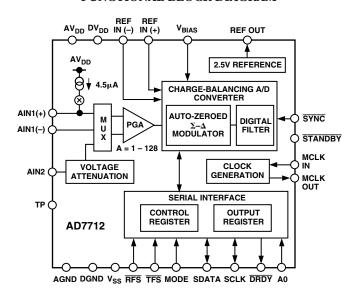

The AD7712 is a complete analog front end for low frequency measurement applications. The device has two analog input channels and accepts either low level signals directly from a transducer or high level ( $\pm 4 \times V_{REF}$ ) signals, and outputs a serial digital word. It employs a sigma-delta conversion technique to realize up to 24 bits of no missing codes performance. The low level input signal is applied to a proprietary programmable gain front end based around an analog modulator. The high level analog input is attenuated before being applied to the same modulator. The modulator output is processed by an on-chip digital filter. The first notch of this digital filter can be programmed via the on-chip control register, allowing adjustment of the filter cutoff and settling time.

Normally, one of the channels will be used as the main channel with the second channel used as an auxiliary input to periodically measure a second voltage. The part can be operated from a single supply (by tying the  $V_{SS}$  pin to AGND), provided that the input signals on the low level analog input are more positive than  $-30~\rm mV.$  By taking the  $V_{SS}$  pin negative, the part can convert signals down to  $-V_{REF}$  on this low level input. This low level input, as well as the reference input, features differential input capability.

The AD7712 is ideal for use in smart, microcontroller based systems. Input channel selection, gain settings, and signal polarity can be configured in software using the bidirectional serial

\*Protected by U.S. Patent No. 5,134,401.

### REV. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

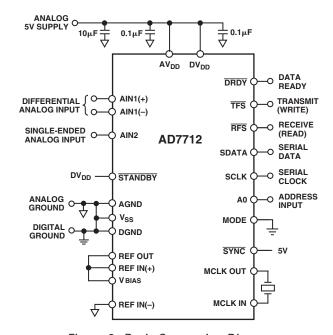

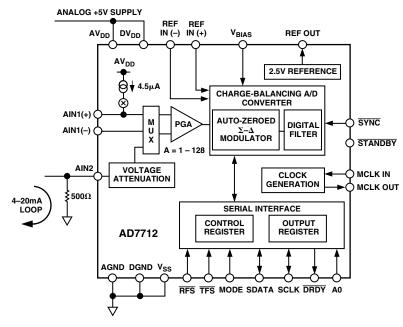

### FUNCTIONAL BLOCK DIAGRAM

port. The AD7712 also contains self-calibration, system calibration, and background calibration options, and allows the user to read and to write the on-chip calibration registers.

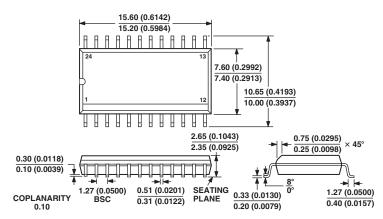

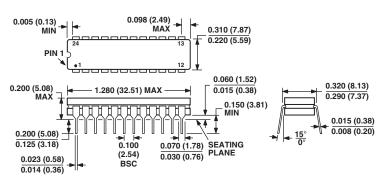

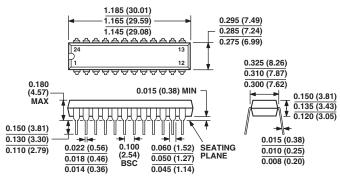

CMOS construction ensures low power dissipation, and a hardware programmable power-down mode reduces the standby power consumption to only 100  $\mu W$  typical. The part is available in a 24-lead, 0.3 inch wide, plastic and hermetic dual-in-line package (DIP), as well as a 24-lead small outline (SOIC) package.

### PRODUCT HIGHLIGHTS

- 1. The low level analog input channel allows the AD7712 to accept input signals directly from a strain gage or transducer, removing a considerable amount of signal conditioning. To maximize the flexibility of the part, the high level analog input accepts signals of  $\pm 4 \times V_{REF}/GAIN$ .

- The AD7712 is ideal for microcontroller or DSP processor applications with an on-chip control register that allows control over filter cutoff, input gain, channel selection, signal polarity, and calibration modes.

- 3. The AD7712 allows the user to read and to write the on-chip calibration registers. This means that the microcontroller has much greater control over the calibration procedure.

- 4. No missing codes ensures true, usable, 23-bit dynamic range coupled with excellent ±0.0015% accuracy. The effects of temperature drift are eliminated by on-chip self-calibration, which removes zero-scale and full-scale errors.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

# **AD7712—SPECIFICATIONS** (AV<sub>DD</sub> = +5 V $\pm$ 5%; DV<sub>DD</sub> = +5 V $\pm$ 5%; V<sub>SS</sub> = 0 V or -5 V $\pm$ 5%; REF IN(+) = +2.5 V; REF IN(-) = AGND; MCLK IN = 10 MHz unless otherwise stated. All specifications T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| Parameter                                             | A, S Versions <sup>1</sup>                       | Unit               | Conditions/Comments                                                                    |

|-------------------------------------------------------|--------------------------------------------------|--------------------|----------------------------------------------------------------------------------------|

| STATIC PERFORMANCE                                    |                                                  |                    |                                                                                        |

| No Missing Codes                                      | 24                                               | Bits min           | Guaranteed by Design. For Filter Notches ≤ 60 Hz                                       |

|                                                       | 22                                               | Bits min           | For Filter Notch = 100 Hz                                                              |

|                                                       | 18                                               | Bits min           | For Filter Notch = 250 Hz                                                              |

|                                                       | 15                                               | Bits min           | For Filter Notch = 500 Hz                                                              |

|                                                       | 12                                               | Bits min           | For Filter Notch = 1 kHz                                                               |

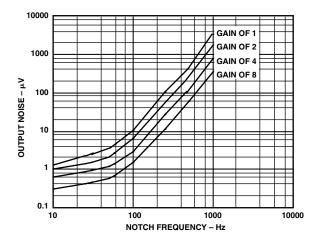

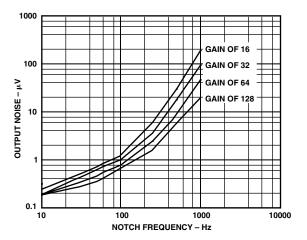

| Output Noise                                          | See Tables I and II                              | Ditto iiiiii       | Depends on Filter Cutoffs and Selected Gain                                            |

| Integral Nonlinearity @ 25°C                          | ±0.0015                                          | % FSR max          | Filter Notches \( \leq 60 \text{ Hz} \)                                                |

| T <sub>MIN</sub> to T <sub>MAX</sub>                  | ±0.0013                                          | % FSR max          | Typically ±0.0003%                                                                     |

| Positive Full-Scale Error <sup>2, 3, 4</sup>          | 10.003                                           | /0 I'SK IIIax      | Excluding Reference                                                                    |

| Full-Scale Drift <sup>5</sup>                         | 1                                                | 11V/0C ++++        | Excluding Reference. For Gains of 1, 2                                                 |

| Full-Scale Drift                                      | 1                                                | μV/°C typ          |                                                                                        |

| 11 1 OCC 1 F 2 4                                      | 0.3                                              | μV/°C typ          | Excluding Reference. For Gains of 4, 8, 16, 32, 64, 128                                |

| Unipolar Offset Error <sup>2, 4</sup>                 |                                                  | ****               |                                                                                        |

| Unipolar Offset Drift <sup>5</sup>                    | 0.5                                              | μV/°C typ          | For Gains of 1, 2                                                                      |

| 2.4                                                   | 0.25                                             | μV/°C typ          | For Gains of 4, 8, 16, 32, 64, 128                                                     |

| Bipolar Zero Error <sup>2, 4</sup>                    |                                                  |                    |                                                                                        |

| Bipolar Zero Drift <sup>5</sup>                       | 0.5                                              | μV/°C typ          | For Gains of 1, 2                                                                      |

|                                                       | 0.25                                             | μV/°C typ          | For Gains of 4, 8, 16, 32, 64, 128                                                     |

| Gain Drift                                            | 2                                                | ppm/°C typ         |                                                                                        |

| Bipolar Negative Full-Scale Error <sup>2</sup> @ 25°C | ±0.003                                           | % FSR max          | Excluding Reference                                                                    |

| $T_{MIN}$ to $T_{MAX}$                                | ±0.006                                           | % FSR max          | Typically ±0.0006%                                                                     |

| Bipolar Negative Full-Scale Drift <sup>5</sup>        | 1                                                | μV/°C typ          | Excluding Reference. For Gains of 1, 2                                                 |

|                                                       | 0.3                                              | μV/°C typ          | Excluding Reference. For Gains of 4, 8, 16, 32, 64, 128                                |

| NALOG INPUTS/REFERENCE INPUTS                         |                                                  |                    |                                                                                        |

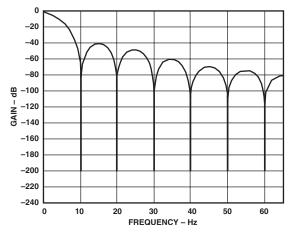

| Normal-Mode 50 Hz Rejection <sup>6</sup>              | 100                                              | dB min             | For Filter Notches of 10 Hz, 25 Hz, 50 Hz, $\pm 0.02 \times f_{NOT}$                   |

| Normal-Mode 60 Hz Rejection <sup>6</sup>              | 100                                              | dB min             | For Filter Notches of 10 Hz, 30 Hz, 60 Hz, $\pm 0.02 \times f_{NOT}$                   |

| AIN1/REF IN                                           | 100                                              | db iiiii           | 1 of 1 liter 1 votenes of 10 112, 50 112, 00 112, ±0.02 × 1 <sub>NO1</sub>             |

| DC Input Leakage Current @ 25°C6                      | 10                                               | pA max             |                                                                                        |

| $T_{ m MIN}$ to $T_{ m MAX}$                          | 1                                                | nA max             |                                                                                        |

| Sampling Capacitance <sup>6</sup>                     | 20                                               | pF max             |                                                                                        |

| Common-Mode Rejection (CMR)                           | 100                                              | dB min             | At dc and $AV_{DD} = 5 \text{ V}$                                                      |

| Common Month Indian (Civility                         | 90                                               | dB min             | At dc and $AV_{DD} = 10 \text{ V}$                                                     |

| Common-Mode 50 Hz Rejection <sup>6</sup>              | 150                                              | dB min             | For Filter Notches of 10 Hz, 25 Hz, 50 Hz, $\pm 0.02 \times f_{NOT}$                   |

| Common-Mode 60 Hz Rejection <sup>6</sup>              | 150                                              | dB min             | For Filter Notches of 10 Hz, 30 Hz, $60 \text{ Hz}$ , $\pm 0.02 \times f_{\text{NOT}}$ |

|                                                       |                                                  | V min to V max     | 101 1 liter Notenes of 10 112, 50 112, 00 112, ±0.02 × 1 <sub>NOT</sub>                |

| Common-Mode Voltage Range <sup>7</sup>                | V <sub>SS</sub> to AV <sub>DD</sub>              | v IIIII to v IIIax |                                                                                        |

| Analog Inputs <sup>8</sup>                            | 6 75 11 111                                      |                    |                                                                                        |

| Input Sampling Rate, f <sub>S</sub>                   | See Table III                                    |                    |                                                                                        |

| AIN1 Input Voltage Range <sup>9</sup>                 | 2 ** ** 10                                       |                    | For Normal Operation. Depends on Gain Selected                                         |

|                                                       | 0 V to V <sub>REF</sub> <sup>10</sup>            | V max              | Unipolar Input Range (B/U Bit of Control Register = 1                                  |

|                                                       | $\pm V_{REF}$                                    | V max              | Bipolar Input Range (B/U Bit of Control Register = 0)                                  |

| AIN2 Input Voltage Range <sup>9</sup>                 |                                                  |                    | For Normal Operation. Depends on Gain Selected                                         |

|                                                       | 0 V to 4 $\times$ V <sub>REF</sub> <sup>10</sup> | V max              | Unipolar Input Range (B/U Bit of Control Register = 1                                  |

|                                                       | $\pm 4 	imes 	ext{V}_{	ext{REF}}$                | V max              | Bipolar Input Range (B/U Bit of Control Register = 0)                                  |

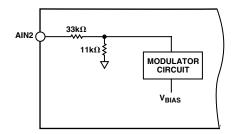

| AIN2 DC Input Impedance                               | 30                                               | kΩ                 |                                                                                        |

| AIN2 Gain Error <sup>11</sup>                         | ±0.05                                            | % typ              | Additional Error Contributed by Resistor Attenuator                                    |

| AIN2 Gain Drift                                       | 1                                                | ppm/°C typ         | Additional Drift Contributed by Resistor Attenuator                                    |

| AIN2 Offset Error <sup>11</sup>                       | 10                                               | mV max             | Additional Error Contributed by Resistor Attenuator                                    |

| AIN2 Offset Drift                                     | 20                                               | μV/°C typ          |                                                                                        |

| Reference Inputs                                      |                                                  |                    |                                                                                        |

| REF IN(+) – REF IN(-) Voltage <sup>12</sup>           | 2.5 to 5                                         | V min to V max     | For Specified Performance. Part Is Functional with Lower $V_{\text{REF}}$ Voltages     |

| Input Sampling Rate, f <sub>S</sub>                   | f <sub>CLK IN</sub> /256                         |                    | KEP 1                                                                                  |

| 1 1                                                   | GLICIN -                                         | 1                  |                                                                                        |

### NOTES

<sup>&</sup>lt;sup>1</sup>Temperature range is as follows: A Version, -40°C to +85°C; S Version -55°C to +125°C. See also Note 18.

<sup>&</sup>lt;sup>2</sup>Applies after calibration at the temperature of interest.

<sup>&</sup>lt;sup>3</sup>Positive full-scale error applies to both unipolar and bipolar input ranges.

<sup>&</sup>lt;sup>4</sup>These errors will be of the order of the output noise of the part as shown in Table I after system calibration. These errors will be 20 μV typical after self-calibration or background calibration.

<sup>&</sup>lt;sup>5</sup>Recalibration at any temperature or use of the background calibration mode will remove these drift errors.

<sup>&</sup>lt;sup>6</sup>These numbers are guaranteed by design and/or characterization.

This common-mode voltage range is allowed, provided that the input voltage on AIN1(+) and AIN1(-) does not exceed AV DD + 30 mV and VSS - 30 mV.

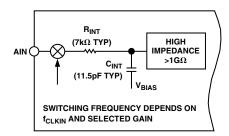

<sup>&</sup>lt;sup>8</sup>The AIN1 analog input presents a very high impedance dynamic load that varies with clock frequency and input sample rate. The maximum recommended source resistance depends on the selected gain (see Tables IV and V).

$<sup>^{9}</sup>$ The analog input voltage range on the AIN1(+) input is given here with respect to the voltage on the AIN1(-) input. The input voltage range on the AIN2 input is with respect to AGND. The absolute voltage on the AIN1 input should not go more positive than AV  $_{DD}$  + 30 mV or more negative than  $V_{SS}$  – 30 mV.  $^{10}V_{REF}$  = REF IN(+) – REF IN(-).

<sup>&</sup>lt;sup>11</sup>This error can be removed using the system calibration capabilities of the AD7712. This error is not removed by the AD7712's self-calibration features. The offset drift on the AIN2 input is 4 times the value given in the Static Performance section.

<sup>&</sup>lt;sup>12</sup>The reference input voltage range may be restricted by the input voltage range requirement on the V<sub>BIAS</sub> input.

## **SPECIFICATIONS** (continued)

| Parameter                                                                        | A, S Versions <sup>1</sup>      | Unit       | Conditions/Comments                                                      |

|----------------------------------------------------------------------------------|---------------------------------|------------|--------------------------------------------------------------------------|

| REFERENCE OUTPUT                                                                 |                                 |            |                                                                          |

| Output Voltage                                                                   | 2.5                             | V nom      |                                                                          |

| Initial Tolerance                                                                | ±1                              | % max      |                                                                          |

| Drift                                                                            | 20                              | ppm/°C typ |                                                                          |

| Output Noise                                                                     | 30                              | μV typ     | pk-pk Noise; 0.1 Hz to 10 Hz Bandwidth                                   |

| Line Regulation (AV <sub>DD</sub> )                                              | 1                               | mV/V max   |                                                                          |

| Load Regulation                                                                  | 1.5                             | mV/mA max  | Maximum Load Current 1 mA                                                |

| External Current                                                                 | 1                               | mA max     |                                                                          |

| V <sub>BIAS</sub> INPUT <sup>13</sup>                                            |                                 |            |                                                                          |

| Input Voltage Range                                                              | $AV_{DD} - 0.85 \times V_{REF}$ |            | See V <sub>BIAS</sub> Input Section                                      |

| input voltage Range                                                              | or AV <sub>DD</sub> – 3.5       | V max      | Whichever Is Smaller: +5 V/–5 V or +10 V/0 V                             |

|                                                                                  | Of AVDD - 3.3                   | VIIIdX     |                                                                          |

|                                                                                  | an AV 2.1                       | V mary     | Nominal AV <sub>DD</sub> /V <sub>SS</sub>                                |

|                                                                                  | or AV <sub>DD</sub> – 2.1       | V max      | Whichever Is Smaller: +5 V/0 V Nominal AV <sub>DD</sub> /V <sub>SS</sub> |

|                                                                                  | $V_{SS} + 0.85 \times V_{REF}$  |            | See V <sub>BIAS</sub> Input Section                                      |

|                                                                                  | or $V_{SS} + 3$                 | V min      | Whichever Is Greater: +5 V/–5 V or +10 V/0 V                             |

|                                                                                  | **                              |            | Nominal AV <sub>DD</sub> /V <sub>SS</sub>                                |

|                                                                                  | or $V_{SS} + 2.1$               | V min      | Whichever Is Greater: +5 V/0 V Nominal AV <sub>DD</sub> /V <sub>SS</sub> |

| V <sub>BIAS</sub> Rejection                                                      | 65 to 85                        | dB typ     | Increasing with Gain                                                     |

| LOGIC INPUTS                                                                     |                                 |            |                                                                          |

| Input Current                                                                    | ±10                             | μA max     |                                                                          |

| All Inputs except MCLK IN                                                        |                                 |            |                                                                          |

| V <sub>INL</sub> , Input Low Voltage                                             | 0.8                             | V max      |                                                                          |

| V <sub>INH</sub> , Input High Voltage                                            | 2.0                             | V min      |                                                                          |

| MCLK IN Only                                                                     |                                 |            |                                                                          |

| V <sub>INI.</sub> , Input Low Voltage                                            | 0.8                             | V max      |                                                                          |

| V <sub>INH</sub> , Input High Voltage                                            | 3.5                             | V min      |                                                                          |

|                                                                                  | 3.3                             | , mm       |                                                                          |

| LOGIC OUTPUTS                                                                    |                                 |            |                                                                          |

| V <sub>OL</sub> , Output Low Voltage                                             | 0.4                             | V max      | $I_{SINK} = 1.6 \text{ mA}$                                              |

| V <sub>OH</sub> , Output High Voltage                                            | 4.0                             | V min      | $I_{SOURCE} = 100 \mu\text{A}$                                           |

| Floating State Leakage Current                                                   | ±10                             | μA max     |                                                                          |

| Floating State Output Capacitance <sup>14</sup>                                  | 9                               | pF typ     |                                                                          |

| FRANSDUCER BURNOUT                                                               |                                 |            |                                                                          |

| Current                                                                          | 4.5                             | μA nom     |                                                                          |

| Initial Tolerance                                                                | ±10                             | % typ      |                                                                          |

| Drift                                                                            | 0.1                             | %/°C typ   |                                                                          |

| SYSTEM CALIBRATION                                                               |                                 |            |                                                                          |

| AIN1                                                                             |                                 |            |                                                                          |

| Positive Full-Scale Calibration Limit <sup>15</sup>                              | $(1.05 \times V_{REF})/GAIN$    | V max      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

| Negative Full-Scale Calibration Limit <sup>15</sup>                              | $-(1.05 \times V_{REF})/GAIN$   | V max      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

| Offset Calibration Limit <sup>16, 17</sup>                                       | $-(1.05 \times V_{REF})/GAIN$   | V max      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

| Input Span <sup>15</sup>                                                         | $0.8 \times V_{REF}/GAIN$       | V min      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

| input opuii                                                                      | $(2.1 \times V_{REF})/GAIN$     | V max      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

| AIN2                                                                             | (2.1 / V REF)/GAIIV             | V IIIAA    | Grant is the selected I Gra Gain (Between I and 126)                     |

| Positive Full-Scale Calibration Limit <sup>15</sup>                              | $(4.2 \times V_{REF})/GAIN$     | V max      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

| Negative Full-Scale Calibration Limit  Negative Full-Scale Calibration Limit  15 | $-(4.2 \times V_{REF})/GAIN$    | V max      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

| Offset Calibration Limit 17                                                      |                                 | V max      | ,                                                                        |

|                                                                                  | $-(4.2 \times V_{REF})/GAIN$    |            | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

| Input Span <sup>15</sup>                                                         | $3.2 \times V_{REF}/GAIN$       | V min      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

|                                                                                  | $(8.4 \times V_{REF})/GAIN$     | V max      | GAIN Is the Selected PGA Gain (Between 1 and 128)                        |

#### NOTES

REV. F –3–

$<sup>^{13}</sup>$  The AD7712 is tested with the following  $V_{BIAS}$  voltages. With AV  $_{DD}$  = 5 V and  $V_{SS}$  = 0 V,  $V_{BIAS}$  = 2.5 V; with AV  $_{DD}$  = 10 V and  $V_{SS}$  = 0 V,  $V_{BIAS}$  = 5 V and with AV  $_{DD}$  = 5 V and  $V_{SS}$  = -5 V,  $V_{BIAS}$  = 0 V.

<sup>&</sup>lt;sup>14</sup>Guaranteed by design, not production tested.

<sup>&</sup>lt;sup>15</sup>After calibration, if the analog input exceeds positive full scale, the converter will output all 1s. If the analog input is less than negative full scale, then the device will output all 0s

$<sup>^{16}</sup>$ These calibration and span limits apply provided the absolute voltage on the AIN1 analog inputs does not exceed AV  $_{DD}$  + 30 mV or does not go more negative than  $V_{SS}$  – 30 mV.

<sup>&</sup>lt;sup>17</sup>The offset calibration limit applies to both the unipolar zero point and the bipolar zero point.

## AD7712—SPECIFICATIONS

| Parameter                               | A, S Versions <sup>1</sup> | Unit   | Conditions/Comments                                                                                          |

|-----------------------------------------|----------------------------|--------|--------------------------------------------------------------------------------------------------------------|

| POWER REQUIREMENTS                      |                            |        |                                                                                                              |

| Power Supply Voltages                   |                            |        |                                                                                                              |

| AV <sub>DD</sub> Voltage <sup>18</sup>  | +5 to +10                  | V nom  | ±5% for Specified Performance                                                                                |

| DV <sub>DD</sub> Voltage <sup>19</sup>  | +5                         | V nom  | ±5% for Specified Performance                                                                                |

| $AV_{DD} - V_{SS}$ Voltage              | +10.5                      | V max  | For Specified Performance                                                                                    |

| Power Supply Currents                   |                            |        | •                                                                                                            |

| AV <sub>DD</sub> Current                | 4                          | mA max |                                                                                                              |

| DV <sub>DD</sub> Current                | 4.5                        | mA max |                                                                                                              |

| V <sub>SS</sub> Current                 | 1.5                        | mA max | $V_{SS} = -5 \text{ V}$                                                                                      |

| Power Supply Rejection <sup>20</sup>    |                            |        | Rejection w.r.t. AGND; Assumes V <sub>BIAS</sub> Is Fixed                                                    |

| Positive Supply $(AV_{DD})^{21}$        |                            | dB typ |                                                                                                              |

| Negative Supply (V <sub>SS</sub> )      | 90                         | dB typ |                                                                                                              |

| Power Dissipation                       |                            |        |                                                                                                              |

| Normal Mode                             | 45                         | mW max | $AV_{DD} = DV_{DD} = +5 \text{ V}, V_{SS} = 0 \text{ V}; \text{Typically 25 mW}$                             |

| Normal Mode                             | 52.5                       | mW max | $AV_{DD} = DV_{DD} = +5 \text{ V}, V_{SS} = -5 \text{ V}; \text{Typically } 30 \text{ mW}$                   |

| Standby (Power-Down) Mode <sup>22</sup> | 200                        | μW max | $AV_{DD} = DV_{DD} = +5 \text{ V}, V_{SS} = 0 \text{ V or } -5 \text{ V}; \text{Typically } 100 \mu\text{W}$ |

#### NOTES

Specifications subject to change without notice.

### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_A = 25^{\circ}C, \text{ unless otherwise noted.})$                       |

|------------------------------------------------------------------------------|

| $AV_{DD}$ to $DV_{DD}$ 0.3 V to +12 V                                        |

| AV <sub>DD</sub> to V <sub>SS</sub>                                          |

| $AV_{DD}$ to $AGND$ 0.3 V to +12 V                                           |

| $AV_{DD}$ to DGND0.3 V to +12 V                                              |

| $DV_{DD}$ to AGND0.3 V to +6 V                                               |

| $DV_{DD}$ to $DGND$                                                          |

| $V_{SS}$ to AGND                                                             |

| $V_{SS}$ to DGND                                                             |

| AIN1 Input Voltage to AGND $V_{SS}$ – 0.3 V to AV <sub>DD</sub> + 0.3 V      |

| Reference Input Voltage to AGND $V_{SS}$ – 0.3 V to AV <sub>DD</sub> + 0.3 V |

| REF OUT to AGND                                                              |

|                                                                              |

| Digital Input Voltage to DGND . | $-0.3$ V to AV <sub>DD</sub> + $0.3$ V |

|---------------------------------|----------------------------------------|

| Digital Output Voltage to DGND  | $-0.3~V$ to $DV_{DD}$ + 0.3 $V$        |

| Operating Temperature Range     |                                        |

| operating remperature runnge               |       |

|--------------------------------------------|-------|

| Commercial (A Version)40°C to              | +85°C |

| Extended (S Version)                       | 125°C |

| Storage Temperature Range65°C to +         | 150°C |

| Lead Temperature (Soldering, 10 secs)      | 300°C |

| Power Dissipation (Any Package) to 75°C 45 | i0 mW |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ORDERING GUIDE**

| Model          | Temperature Range | Package Options* |

|----------------|-------------------|------------------|

| AD7712AN       | −40°C to +85°C    | N-24             |

| AD7712AR       | −40°C to +85°C    | RW-24            |

| AD7712AR-REEL  | −40°C to +85°C    | RW-24            |

| AD7712AR-REEL7 | −40°C to +85°C    | RW-24            |

| AD7712AQ       | −40°C to +85°C    | Q-24             |

| AD7712SQ       | −55°C to +125°C   | Q-24             |

| EVAL-AD7712EB  | Evaluation Board  |                  |

<sup>\*</sup>N = PDIP, Q = CERDIP; RW = SOIC.

### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7712 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

–4– REV. F

$<sup>^{18}</sup>$  The AD7712 is specified with a 10 MHz clock for AV  $_{DD}$  voltages of +5 V  $\pm$  5%. It is specified with an 8 MHz clock for AV  $_{DD}$  voltages greater than 5.25 V and less than 10.5 V. Operating with AV  $_{DD}$  voltages in the range 5.25 V to 10.5 V is guaranteed only over the 0°C to 70°C temperature range.

$<sup>^{19}\</sup>text{The} \pm 5\%$  tolerance on the DV  $_{DD}$  input is allowed provided that DV  $_{DD}$  does not exceed AV  $_{DD}$  by more than 0.3 V.

<sup>&</sup>lt;sup>20</sup>Measured at dc and applies in the selected passband. PSRR at 50 Hz will exceed 120 dB with filter notches of 10 Hz, 25 Hz, or 50 Hz. PSRR at 60 Hz will exceed 120 dB with filter notches of 10 Hz, 30 Hz, or 60 Hz.

<sup>&</sup>lt;sup>21</sup>PSRR depends on gain: gain of 1 = 70 dB typ; gain of 2 = 75 dB typ; gain of 4 = 80 dB typ; gains of 8 to 128 = 85 dB typ. These numbers can be improved (to 95 dB typ) by deriving the V<sub>BIAS</sub> voltage (via Zener diode or reference) from the AV<sub>DD</sub> supply.

<sup>&</sup>lt;sup>22</sup>Using the hardware STANDBY pin. Standby power dissipation using the software standby bit (PD) of the Control Register is 8 mW typ.

## TIMING CHARACTERISTICS 1, 2 (DV<sub>DD</sub> = +5 V $\pm$ 5%; AV<sub>DD</sub> = +5 V or +10 V³ $\pm$ 5%; V<sub>SS</sub> = 0 V or -5 V $\pm$ 5%; AGND = DGND = 0 V; f<sub>CLKIN</sub> =10 MHz; Input Logic 0 = 0 V, Logic 1 = DV<sub>DD</sub>, unless otherwise noted.)

| Parameter                                       | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (A, S Versions) | Unit    | Conditions/Comments                                                                                       |

|-------------------------------------------------|--------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------|

| f <sub>CLK IN</sub> <sup>4, 5</sup>             |                                                              |         | Master Clock Frequency: Crystal Oscillator or                                                             |

|                                                 |                                                              |         | Externally Supplied                                                                                       |

|                                                 | 400                                                          | kHz min | $AV_{DD} = 5 \text{ V} \pm 5\%$                                                                           |

|                                                 | 10                                                           | MHz max | For Specified Performance                                                                                 |

|                                                 | 8                                                            | MHz     | $AV_{DD} = 5.25 \text{ V}$ to 10.5 V                                                                      |

| t <sub>CLK IN LO</sub>                          | $0.4 \times t_{ m CLKIN}$                                    | ns min  | Master Clock Input Low Time; $t_{CLK IN} = 1/f_{CLK IN}$                                                  |

| t <sub>CLK</sub> IN HI                          | $0.4 	imes t_{ m CLKIN}$                                     | ns min  | Master Clock Input High Time                                                                              |

| $t_r^6$ $t_f^6$                                 | 50                                                           | ns max  | Digital Output Rise Time; Typically 20 ns                                                                 |

| $t_f^6$                                         | 50                                                           | ns max  | Digital Output Fall Time; Typically 20 ns                                                                 |

| $t_1$                                           | 1000                                                         | ns min  | SYNC Pulse Width                                                                                          |

| Self-Clocking Mode                              |                                                              |         |                                                                                                           |

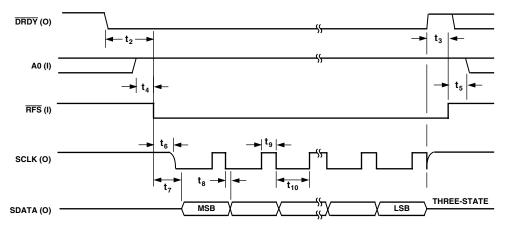

| $t_2$                                           | 0                                                            | ns min  | $\overline{\text{DRDY}}$ to $\overline{\text{RFS}}$ Setup Time; $t_{\text{CLK IN}} = 1/f_{\text{CLK IN}}$ |

| $t_3$                                           | 0                                                            | ns min  | DRDY to RFS Hold Time                                                                                     |

| $t_4$                                           | $2 \times t_{\text{CLK IN}}$                                 | ns min  | A0 to RFS Setup Time                                                                                      |

| t <sub>5</sub>                                  | 0                                                            | ns min  | A0 to RFS Hold Time                                                                                       |

| $t_6$                                           | $4 \times t_{\text{CLK IN}} + 20$                            | ns max  | RFS Low to SCLK Falling Edge                                                                              |

| t <sub>6</sub><br>t <sub>7</sub> <sup>7</sup> _ | $4 \times t_{\text{CLK IN}} + 20$                            | ns max  | Data Access Time (RFS Low to Data Valid)                                                                  |

| $t_8^{7}$                                       | t <sub>CLK IN</sub> /2                                       | ns min  | SCLK Falling Edge to Data Valid Delay                                                                     |

|                                                 | $t_{\text{CLK IN}}/2 + 30$                                   | ns max  |                                                                                                           |

| $t_9$                                           | t <sub>CLK IN</sub> /2                                       | ns nom  | SCLK High Pulse Width                                                                                     |

| t <sub>10</sub>                                 | $3 \times t_{\text{CLK IN}}/2$                               | ns nom  | SCLK Low Pulse Width                                                                                      |

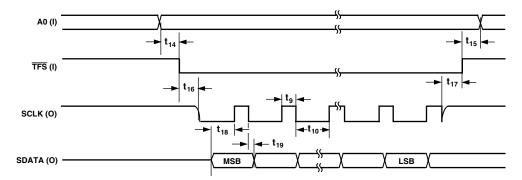

| $t_{14}$                                        | 50                                                           | ns min  | A0 to TFS Setup Time                                                                                      |

| t <sub>15</sub>                                 | 0                                                            | ns min  | A0 to $\overline{\text{TFS}}$ Hold Time                                                                   |

| t <sub>16</sub>                                 | $4 \times t_{\text{CLK IN}} + 20$                            | ns max  | TFS to SCLK Falling Edge Delay Time                                                                       |

| t <sub>17</sub>                                 | $4 \times t_{\text{CLK IN}}$                                 | ns min  | TFS to SCLK Falling Edge Hold Time                                                                        |

| t <sub>18</sub>                                 | 0                                                            | ns min  | Data Valid to SCLK Setup Time                                                                             |

| t <sub>19</sub>                                 | 10                                                           | ns min  | Data Valid to SCLK Hold Time                                                                              |

### NOTES

REV. F -5-

$<sup>^1</sup>$ Guaranteed by design, not production tested. Sample tested during initial release and after any redesign or process change that may affect this parameter. All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

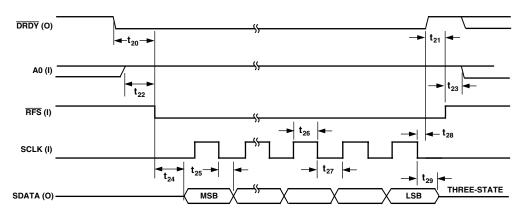

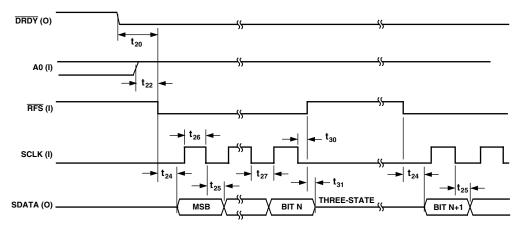

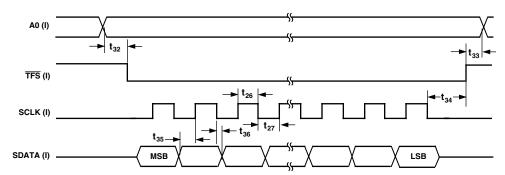

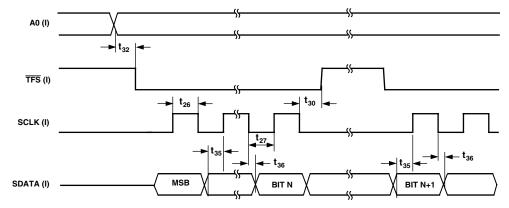

<sup>&</sup>lt;sup>2</sup>See Figures 11 to 14.

$<sup>^3</sup>$ The AD7712 is specified with a 10 MHz clock for AV $_{DD}$  voltages of 5 V  $\pm$  5%. It is specified with an 8 MHz clock for AV $_{DD}$  voltages greater than 5.25 V and less than 10 5 V

<sup>&</sup>lt;sup>4</sup>CLK IN duty cycle range is 45% to 55%. CLK IN must be supplied whenever the AD7712 is not in STANDBY mode. If no clock is present in this case, the device can draw higher current than specified and possibly become uncalibrated.

$<sup>^{5}</sup>$ The AD7712 is production tested with f<sub>CLK IN</sub> at 10 MHz (8 MHz for AV<sub>DD</sub> < 5.25 V). It is guaranteed by characterization to operate at 400 kHz.

$<sup>^6</sup>Specified using 10\%$  and 90% points on waveform of interest.

<sup>&</sup>lt;sup>7</sup>These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross 0.8 V or 2.4 V.

## TIMING CHARACTERISTICS (continued)

| Parameter                    | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> (A, S Versions) | Unit    | Conditions/Comments                      |

|------------------------------|--------------------------------------------------------------|---------|------------------------------------------|

| External Clocking Mode       |                                                              |         |                                          |

| $f_{SCLK}$                   | f <sub>CLK IN</sub> /5                                       | MHz max | Serial Clock Input Frequency             |

| $t_{20}$                     | 0                                                            | ns min  | DRDY to RFS Setup Time                   |

| $t_{21}$                     | 0                                                            | ns min  | DRDY to RFS Hold Time                    |

| $t_{22}$                     | $2 \times t_{\text{CLK IN}}$                                 | ns min  | A0 to RFS Setup Time                     |

| t <sub>23</sub>              | 0                                                            | ns min  | A0 to RFS Hold Time                      |

| ${\sf t_{24}}^7$             | $4 \times t_{\text{CLK IN}}$                                 | ns max  | Data Access Time (RFS Low to Data Valid) |

| t <sub>25</sub> <sup>7</sup> | 10                                                           | ns min  | SCLK Falling Edge to Data Valid Delay    |

|                              | $2 \times t_{\text{CLK IN}} + 20$                            | ns max  |                                          |

| t <sub>26</sub>              | $2 \times t_{\text{CLK IN}}$                                 | ns min  | SCLK High Pulse Width                    |

| t <sub>27</sub>              | $2 \times t_{\text{CLK IN}}$                                 | ns min  | SCLK Low Pulse Width                     |

| t <sub>28</sub>              | $t_{\text{CLK IN}} + 10$                                     | ns max  | SCLK Falling Edge to DRDY High           |

| $t_{29}^{8}$                 | 10                                                           | ns min  | SCLK to Data Valid Hold Time             |

|                              | $t_{\text{CLK IN}} + 10$                                     | ns max  |                                          |

| t <sub>30</sub>              | 10                                                           | ns min  | RFS/TFS to SCLK Falling Edge Hold Time   |

| t <sub>31</sub> <sup>8</sup> | $5 \times t_{\text{CLK IN}}/2 + 50$                          | ns max  | RFS to Data Valid Hold Time              |

| t <sub>32</sub>              | 0                                                            | ns min  | A0 to TFS Setup Time                     |

| t <sub>33</sub>              | 0                                                            | ns min  | A0 to TFS Hold Time                      |

| t <sub>34</sub>              | $4 \times t_{\text{CLK IN}}$                                 | ns min  | SCLK Falling Edge to TFS Hold Time       |

| t <sub>35</sub>              | $2 \times t_{\text{CLK IN}} - \text{SCLK High}$              | ns min  | Data Valid to SCLK Setup Time            |

| t <sub>36</sub>              | 30                                                           | ns min  | Data Valid to SCLK Hold Time             |

### NOTES

Specifications subject to change without notice.

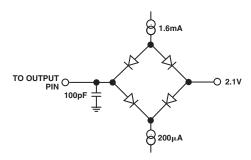

Figure 1. Load Circuit for Access Time and Bus Relinquish Time

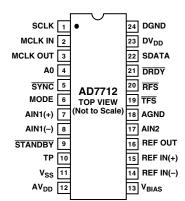

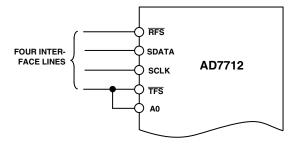

## PIN CONFIGURATION DIP and SOIC

–6– REV. F

<sup>&</sup>lt;sup>8</sup>These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove effects of charging or discharging the 100 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances.

### PIN FUNCTION DESCRIPTION

| Pin | Mnemonic      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SCLK          | Serial Clock. Logic input/output, depending on the status of the MODE pin. When MODE is high, the device is in its self-clocking mode, and the SCLK pin provides a serial clock output. This SCLK becomes active when RFS or TFS goes low, and it goes high impedance when either RFS or TFS returns high or when the device has completed transmission of an output word. When MODE is low, the device is in its external clocking mode, and the SCLK pin acts as an input. This input serial clock can be a continuous clock with all |

|     |               | data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to the AD7712 in smaller batches of data.                                                                                                                                                                                                                                                                                                                                                       |

| 2   | MCLK IN       | Master Clock Signal for the Device. This can be provided in the form of a crystal or external clock. A crystal can be tied across the MCLK IN and MCLK OUT pins. Alternatively, the MCLK IN pin can be driven with a CMOS-compatible clock and MCLK OUT left unconnected. The clock input frequency is nominally 10 MHz.                                                                                                                                                                                                                |

| 3   | MCLK OUT      | When the master clock for the device is a crystal, the crystal is connected between MCLK IN and MCLK OUT.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4   | A0            | Address Input. With this input low, reading and writing to the device is to the control register. With this input high, access is to either the data register or the calibration registers.                                                                                                                                                                                                                                                                                                                                             |

| 5   | SYNC          | Logic Input. Allows for synchronization of the digital filters when using a number of AD7712s. It resets the nodes of the digital filter.                                                                                                                                                                                                                                                                                                                                                                                               |

| 6   | MODE          | Logic Input. When this pin is high, the device is in its self-clocking mode. With this pin low, the device is in its external clocking mode.                                                                                                                                                                                                                                                                                                                                                                                            |

| 7   | AIN1(+)       | Analog Input Channel 1. Positive input of the programmable gain differential analog input. The AIN1(+) input is connected to an output current source that can be used to check that an external transducer has burned out or gone open circuit. This output current source can be turned on/off via the control register.                                                                                                                                                                                                              |

| 8   | AIN1(-)       | Analog Input Channel 1. Negative input of the programmable gain differential analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9   | STANDBY       | Logic Input. Taking this pin low shuts down the internal analog and digital circuitry, reducing power consumption to less than $50 \mu W$ .                                                                                                                                                                                                                                                                                                                                                                                             |

| 10  | TP            | Test Pin. Used when testing the device. Do not connect anything to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11  | $V_{SS}$      | Analog Negative Supply, 0 V to $-5$ V. Tied to AGND for single-supply operation. The input voltage on AIN1 should not go > 30 mV negative w.r.t. $V_{SS}$ for correct operation of the device.                                                                                                                                                                                                                                                                                                                                          |

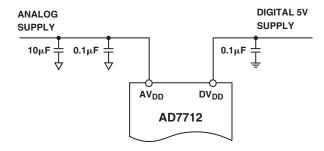

| 12  | $AV_{DD}$     | Analog Positive Supply Voltage, 5 V to 10 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13  | $V_{ m BIAS}$ | Input Bias Voltage. This input voltage should be set such that $V_{BIAS} + 0.85 \times V_{REF} < AV_{DD}$ and $V_{BIAS} - 0.85 \times V_{REF} > V_{SS}$ where $V_{REF}$ is REF IN(+) – REF IN(-). Ideally, this should be tied halfway between $AV_{DD}$ and $V_{SS}$ . Thus, with $AV_{DD} = +5$ V and $V_{SS} = 0$ V, it can be tied to REF OUT; with $AV_{DD} = +5$ V and $V_{SS} = -5$ V, it can be tied to AGND, while with $AV_{DD} = +10$ V, it can be tied to +5 V.                                                             |

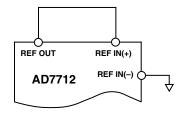

| 14  | REF IN(-)     | Reference Input. The REF IN(-) can lie anywhere between $AV_{DD}$ and $V_{SS}$ provided REF IN(+) is greater than REF IN(-).                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15  | REF IN(+)     | Reference Input. The reference input is differential providing that REF IN(+) is greater than REF IN(-). REF IN(+) can lie anywhere between $AV_{\rm DD}$ and $V_{\rm SS}$ .                                                                                                                                                                                                                                                                                                                                                            |

| 16  | REF OUT       | Reference Output. The internal 2.5 V reference is provided at this pin. This is a single-ended output that is referred to AGND.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17  | AIN2          | Analog Input Channel 2. High level analog input that accepts an analog input voltage range of $\pm 4 \times V_{REF}/GAIN$ . At the nominal $V_{REF}$ of $\pm 2.5$ V and a gain of 1, the AIN2 input voltage range is $\pm 10$ V.                                                                                                                                                                                                                                                                                                        |

| 18  | AGND          | Ground Reference Point for Analog Circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 19  | TFS           | Transmit Frame Synchronization. Active low logic input used to write serial data to the device with serial data expected after the falling edge of this pulse. In the self-clocking mode, the serial clock becomes active after TFS goes low. In the external clocking mode, TFS must go low before the first bit of the data-word is written to the part.                                                                                                                                                                              |

| 20  | RFS           | Receive Frame Synchronization. Active low logic input used to access serial data from the device. In the self-clocking mode, both the SCLK and SDATA lines become active after $\overline{RFS}$ goes low. In the external clocking mode, the SDATA line becomes active after $\overline{RFS}$ goes low.                                                                                                                                                                                                                                 |

REV. F -7-

| Pin | Mnemonic                    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | DRDY                        | Logic Output. A falling edge indicates that a new output word is available for transmission. The $\overline{DRDY}$ pin will return high upon completion of transmission of a full output word. $\overline{DRDY}$ is also used to indicate when the AD7712 has completed its on-chip calibration sequence.                                                                                                                                                                                                                                                                              |

| 22  | SDATA                       | Serial Data. Input/output with serial data being written to either the control register or the calibration registers and serial data being accessed from the control register, calibration registers, or the data register. During an output data read operation, serial data becomes active after $\overline{RFS}$ goes low (provided $\overline{DRDY}$ is low). During a write operation, valid serial data is expected on the rising edges of SCLK when $\overline{TFS}$ is low. The output data coding is natural binary for unipolar inputs and offset binary for bipolar inputs. |

| 23  | $\mathrm{DV}_{\mathrm{DD}}$ | Digital Supply Voltage, 5 V. $DV_{DD}$ should not exceed $AV_{DD}$ by more than 0.3 V in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 24  | DGND                        | Ground Reference Point for Digital Circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### **TERMINOLOGY**

#### **Integral Nonlinearity**

This is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero-scale (not to be confused with bipolar zero), a point 0.5 LSB below the first code transition (000...000 to 000...001) and full scale, a point 0.5 LSB above the last code transition (111...110 to 111...111). The error is expressed as a percentage of full scale.

### Positive Full-Scale Error

Positive full-scale error is the deviation of the last code transition (111 . . . 110 to 111 . . . 111) from the ideal input full-scale voltage. For AIN1(+), the ideal full-scale input voltage is (AIN1(-) +  $\rm V_{REF}/GAIN - 3/2\ LSBs)$ ; for AIN2, the ideal full-scale voltage is +4  $\times$   $\rm V_{REF}/GAIN - 3/2\ LSBs$ . Positive full-scale error applies to both unipolar and bipolar analog input ranges.

### Unipolar Offset Error

Unipolar offset error is the deviation of the first code transition from the ideal voltage. For AIN1(+), the ideal input voltage is (AIN1(-) + 0.5 LSB); for AIN2, the ideal input is 0.5 LSB when operating in the unipolar mode.

### Bipolar Zero Error

This is the deviation of the midscale transition (0111...111 to 1000...000) from the ideal input voltage. For AIN1(+), the ideal input voltage is (AIN1(-) - 0.5 LSB); for AIN2, the ideal input is -0.5 LSB when operating in the bipolar mode.

#### Bipolar Negative Full-Scale Error

This is the deviation of the first code transition from the ideal input voltage. For AIN1(+), the ideal input voltage is (AIN1(-) –  $V_{REF}/GAIN$  + 0.5 LSB); for AIN2, the ideal input voltage is (–4 ×  $V_{REF}/GAIN$  + 0.5 LSB) when operating in the bipolar mode.

### Positive Full-Scale Overrange

Positive full-scale overrange is the amount of overhead available to handle input voltages on AIN1(+) input greater than (AIN1(-) +  $V_{REF}/GAIN$ ) or on the AIN2 of greater than +4  $\times$   $V_{REF}/GAIN$  (for example, noise peaks or excess voltages due to system gain errors in system calibration routines) without introducing errors due to overloading the analog modulator or to overflowing the digital filter.

### Negative Full-Scale Overrange

This is the amount of overhead available to handle voltages on AIN1(+) below (AIN1(-) –  $V_{REF}/GAIN)$  or on AIN2 below  $-4 \times V_{REF}/GAIN$  without overloading the analog modulator or overflowing the digital filter. Note that the analog input will accept negative voltage peaks on AIN1(+) even in the unipolar mode provided that AIN1(+) is greater than AIN1(-) and greater than  $V_{SS}-30\ mV.$

### Offset Calibration Range

In the system calibration modes, the AD7712 calibrates its offset with respect to the analog input. The offset calibration range specification defines the range of voltages that the AD7712 can accept and still accurately calibrate offset.

#### **Full-Scale Calibration Range**

This is the range of voltages that the AD7712 can accept in the system calibration mode and still correctly calibrate full scale.

### Input Span

In system calibration schemes, two voltages applied in sequence to the AD7712's analog input define the analog input range. The input span specification defines the minimum and maximum input voltages from zero to full scale that the AD7712 can accept and still accurately calibrate gain.

–8– REV. F

### Control Register (24 Bits)

A write to the device with the A0 input low writes data to the control register. A read to the device with the A0 input low accesses the contents of the control register. The control register is 24 bits wide and when writing to the register 24 bits of data must be written otherwise the data will not be loaded to the control register. In other words, it is not possible to write just the first 12 bits of data into the control register. If more than 24 clock pulses are provided before TFS returns high, then all clock pulses after the 24th clock pulse are ignored. Similarly, a read operation from the control register should access 24 bits of data.

### **MSB**

| MD2             | MD1  | MD0 | G2  | G1  | G0  | CH  | PD  | WL  | X   | ВО  | B/U |

|-----------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| FS11            | FS10 | FS9 | FS8 | FS7 | FS6 | FS5 | FS4 | FS3 | FS2 | FS1 | FS0 |

| X = Don't Care. |      |     |     |     |     |     |     |     |     | LSB |     |

| <b>Operating Mode</b> |     | Iode |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD2                   | MD1 | MD0  | Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0                     | 0   | 0    | Normal Mode. This is the normal mode of operation of the device whereby a read to the device accesses data from the data register. This is the default condition of these bits after the internal power-on reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0                     | 0   | 1    | Activate Self-Calibration. This activates self-calibration on the channel selected by CH. This is a one-step calibration sequence, and when complete, the part returns to normal mode (with MD2, MD1, MD0 of the control registers returning to $0, 0, 0$ ). The $\overline{DRDY}$ output indicates when this self-calibration is complete. For this calibration type, the zero-scale calibration is done internally on shorted (zeroed) inputs, and the full-scale calibration is done on $V_{REF}$ .                                                                                                                                                                                                                                             |

| 0                     | 1   | 0    | Activate System Calibration. This activates system calibration on the channel selected by CH. This is a two-step calibration sequence, with the zero-scale calibration done first on the selected input channel and $\overline{DRDY}$ indicating when this zero-scale calibration is complete. The part returns to normal mode at the end of this first step in the two-step sequence.                                                                                                                                                                                                                                                                                                                                                             |

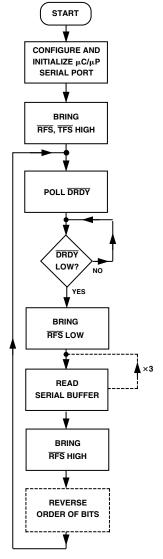

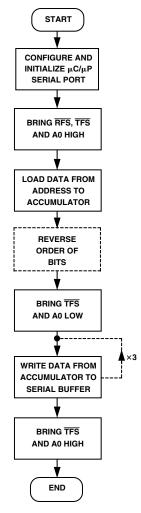

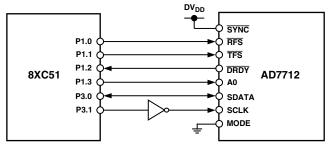

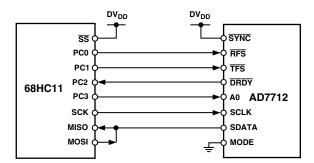

| 0                     | 1   | 1    | Activate System Calibration. This is the second step of the system calibration sequence with full-scale calibration being performed on the selected input channel. Once again, $\overline{DRDY}$ indicates when the full-scale calibration is complete. When this calibration is complete, the part returns to normal mode.                                                                                                                                                                                                                                                                                                                                                                                                                        |