## 3.3 V 1:8 LVCMOS PLL Clock Generator

# The MPC9653A is a 3.3 V compatible, 1:8 PLL based clock generator and zero-delay buffer targeted for high performance low-skew clock distribution in mid-range to high-performance telecom, networking and computing applications. With output frequencies up to 125 MHz and output skews less than 150 ps the device meets the needs of the most demanding clock applications.

#### Features

- 1:8 PLL based low-voltage clock generator

- Supports zero-delay operation

- 3.3 V power supply

- Generates clock signals up to 125 MHz

- PLL guaranteed to lock down to 145 MHz, output frequency = 36.25 MHz

- Maximum output skew of 150 ps

- Differential LVPECL reference clock input

- External PLL feedback

- Drives up to 16 clock lines

- 32-lead LQFP packaging

- 32-lead Pb-free Package Available

- Ambient temperature range 0°C to +70°C

- Pin and function compatible to the MPC953 and MPC9653

#### **Functional Description**

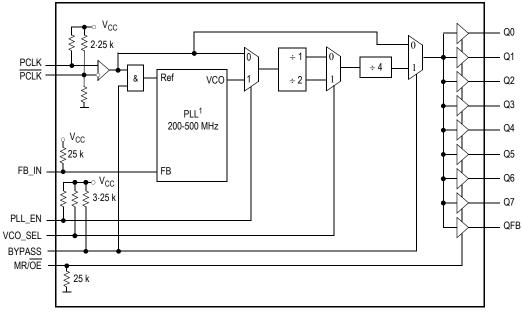

The MPC9653A utilizes PLL technology to frequency lock its outputs onto an input reference clock. Normal operation of the MPC9653A requires the connection of the QFB output to the feedback input to close the PLL feedback path (external feedback). With the PLL locked, the output frequency is equal to the reference frequency of the device and VCO\_SEL selects the operating frequency range of 25 to 62.5 MHz or 50 to 125 MHz. The two available post-PLL dividers selected by VCO\_SEL (divide-by-4 or divide-by-8) and the reference clock frequency determine the VCO frequency. Both must be selected to match the VCO frequency range. The internal VCO of the MPC9653A is running at either 4x or 8x of the reference clock frequency. The MPC9653A is guaranteed to lock in a low power PLL mode in the high frequency range (VCO\_SEL = 0) down to PLL = 145 MHz or  $F_{ref}$  = 36.25 MHz.

The MPC9653A has a differential LVPECL reference input along with an external feedback input. The device is ideal for use as a zero delay, low skew fanout buffer. The device performance has been tuned and optimized for zero delay performance.

The PLL\_EN and BYPASS controls select the PLL bypass configuration for test and diagnosis. In this configuration, the selected input reference clock is bypassing the PLL and routed either to the output dividers or directly to the outputs. The PLL bypass configurations are fully static and the minimum clock frequency specification and all other PLL characteristics do not apply. The outputs can be disabled (high-impedance) and the device reset by asserting the MR/OE pin. Asserting MR/OE also causes the PLL to loose lock due to missing feedback signal presence at FB\_IN. Deasserting MR/OE will enable the outputs and close the phase locked loop, enabling the PLL to recover to normal operation.

The MPC9653A is fully 3.3 V compatible and requires no external loop filter components. The inputs (except PCLK) accept LVC-MOS signals while the outputs provide LVCMOS compatible levels with the capability to drive terminated 50  $\Omega$  transmission lines. For series terminated transmission lines, each of the MPC9653A outputs can drive one or two traces giving the devices an effective fanout of 1:16. The device is packaged in a 7x7 mm<sup>2</sup> 32-lead LQFP package.

IDT<sup>™</sup> 3.3 V 1:8 LVCMOS PLL Clock Generator

# DATA SHEET

MPC9653A

AC SUFFIX 32-LEAD LQFP PACKAGE CASE 873A-03

LOW VOLTAGE 3.3 V LVCMOS 1:8 PLL CLOCK GENERATOR

Note 1. PLL will lock @ 145 MHz

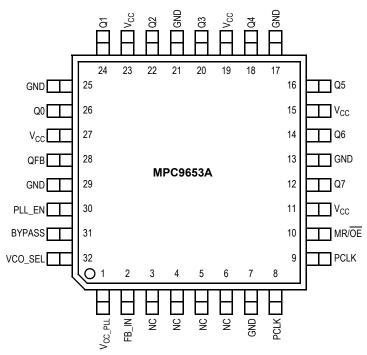

### Table 1. Pin Configuration

| Pin                 | I/O    | Туре            | Function                                                                                                                                                                                       |

|---------------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK, PCLK          | Input  | LVPECL          | PECL reference clock signal                                                                                                                                                                    |

| FB_IN               | Input  | LVCMOS          | PLL feedback signal input, connect to QFB                                                                                                                                                      |

| VCO_SEL             | Input  | LVCMOS          | Operating frequency range select                                                                                                                                                               |

| BYPASS              | Input  | LVCMOS          | PLL and output divider bypass select                                                                                                                                                           |

| PLL_EN              | Input  | LVCMOS          | PLL enable/disable                                                                                                                                                                             |

| MR/OE               | Input  | LVCMOS          | Output enable/disable (high-impedance tristate) and device reset                                                                                                                               |

| Q0–7                | Output | LVCMOS          | Clock outputs                                                                                                                                                                                  |

| QFB                 | Output | LVCMOS          | Clock output for PLL feedback, connect to FB_IN                                                                                                                                                |

| GND                 | Supply | Ground          | Negative power supply (GND)                                                                                                                                                                    |

| V <sub>CC_PLL</sub> | Supply | V <sub>CC</sub> | PLL positive power supply (analog power supply). It is recommended to use an external RC filter for the analog power supply pin $V_{CC\_PLL}$ . Refer to APPLICATIONS INFORMATION for details. |

| V <sub>CC</sub>     | Supply | V <sub>CC</sub> | Positive power supply for I/O and core. All $V_{CC}$ pins must be connected to the positive power supply for correct operation                                                                 |

#### **Table 2. Function Table**

| Control | Default | 0                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                            |

|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL_EN  | 1       | Test mode with PLL bypassed. The reference clock (PCLK) is substituted for the internal VCO output. MPC9653A is fully static and no minimum frequency limit applies. All PLL related AC characteristics are not applicable.            | Selects the VCO output <sup>1</sup>                                                                                                                                                                                                          |

| BYPASS  | 1       | Test mode with PLL and output dividers bypassed. The reference clock (PCLK) is directly routed to the outputs. MPC9653A is fully static and no minimum frequency limit applies. All PLL related AC characteristics are not applicable. | Selects the output dividers.                                                                                                                                                                                                                 |

| VCO_SEL | 1       | VCO $\div$ 1 (High frequency range). f <sub>REF</sub> = f <sub>Q0-7</sub> = 4 $\cdot$ f <sub>VCO</sub>                                                                                                                                 | VCO $\div$ 2 (Low output range). f <sub>REF</sub> = f <sub>Q0-7</sub> = 8 $\cdot$ f <sub>VCO</sub>                                                                                                                                           |

| MR/OE   | 0       | Outputs enabled (active)                                                                                                                                                                                                               | Outputs disabled (high-impedance state) and reset of the device. During reset the PLL feedback loop is open. The VCO is tied to its lowest frequency. The length of the reset pulse should be greater than one reference clock cycle (PCLK). |

1. PLL operation requires  $\overline{\text{BYPASS}} = 1$  and PLL\_EN = 1.

Downloaded from Elcodis.com electronic components distributor

#### **Table 3. General Specifications**

| Symbol          | Characteristics                   | Min  | Тур             | Max | Unit | Condition  |

|-----------------|-----------------------------------|------|-----------------|-----|------|------------|

| $V_{TT}$        | Output Termination Voltage        |      | $V_{CC} \div 2$ |     | V    |            |

| MM              | ESD Protection (Machine Model)    | 200  |                 |     | V    |            |

| HBM             | ESD Protection (Human Body Model) | 2000 |                 |     | V    |            |

| LU              | Latch-Up Immunity                 | 200  |                 |     | mA   |            |

| C <sub>PD</sub> | Power Dissipation Capacitance     |      | 10              |     | pF   | Per output |

| C <sub>IN</sub> | Input Capacitance                 |      | 4.0             |     | pF   | Inputs     |

#### Table 4. Absolute Maximum Ratings<sup>1</sup>

| Symbol           | Characteristics     | Min  | Мах                   | Unit | Condition |

|------------------|---------------------|------|-----------------------|------|-----------|

| V <sub>CC</sub>  | Supply Voltage      | -0.3 | 3.9                   | V    |           |

| V <sub>IN</sub>  | DC Input Voltage    | -0.3 | V <sub>CC</sub> + 0.3 | V    |           |

| V <sub>OUT</sub> | DC Output Voltage   | -0.3 | V <sub>CC</sub> + 0.3 | V    |           |

| I <sub>IN</sub>  | DC Input Current    |      | ±20                   | mA   |           |

| I <sub>OUT</sub> | DC Output Current   |      | ±50                   | mA   |           |

| Τ <sub>S</sub>   | Storage Temperature | -65  | 125                   | °C   |           |

Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

#### Table 5. DC Characteristics (V<sub>CC</sub> = $3.3 \text{ V} \pm 5\%$ , T<sub>A</sub> = $0^{\circ}$ C to $70^{\circ}$ C)

| Symbol                        | Characteristics                   | Min | Тур     | Мах                   | Unit   | Condition                                          |

|-------------------------------|-----------------------------------|-----|---------|-----------------------|--------|----------------------------------------------------|

| V <sub>IH</sub>               | Input high voltage                | 2.0 |         | V <sub>CC</sub> + 0.3 | V      | LVCMOS                                             |

| V <sub>IL</sub>               | Input low voltage                 |     |         | 0.8                   | V      | LVCMOS                                             |

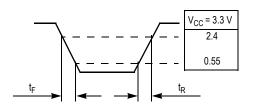

| V <sub>PP</sub>               | Peak-to-peak input voltage (PCLK) | 300 |         |                       | mV     | LVPECL                                             |

| V <sub>CMR</sub> <sup>1</sup> | Common Mode Range (PCLK)          | 1.0 |         | V <sub>CC</sub> – 0.6 | V      | LVPECL                                             |

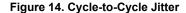

| V <sub>OH</sub>               | Output High Voltage               | 2.4 |         |                       | V      | $I_{OH} = -24 \text{ mA}^2$                        |

| V <sub>OL</sub>               | Output Low Voltage                |     |         | 0.55<br>0.30          | V<br>V | I <sub>OL</sub> = 24 mA<br>I <sub>OL</sub> = 12 mA |

| Z <sub>OUT</sub>              | Output impedance                  |     | 14 – 17 |                       | Ω      |                                                    |

| I <sub>IN</sub>               | Input Current <sup>3</sup>        |     |         | ±200                  | μA     | $V_{IN} = V_{CC}$ or GND                           |

| I <sub>CC_PLL</sub>           | Maximum PLL Supply Current        |     | 5.0     | 10                    | mA     | V <sub>CC_PLL</sub> Pin                            |

| I <sub>CCQ</sub> <sup>4</sup> | Maximum Quiescent Supply Current  |     |         | 10                    | mA     | All $V_{CC}$ Pins                                  |

1. V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the V<sub>PP</sub> (DC) specification.

2. The MPC9653A is capable of driving 50  $\Omega$  transmission lines on the incident edge. Each output drives one 50  $\Omega$  parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, the device drives up to two 50  $\Omega$  series terminated transmission lines. The MPC9653A meets the V<sub>OH</sub> and V<sub>OL</sub> specification of the MPC953 (V<sub>OH</sub> > V<sub>CC</sub> -0.6 V at I<sub>OH</sub> = -20 mA and V<sub>OL</sub> > 0.6 V at I<sub>OL</sub> = 20 mA).

3. Inputs have pull-down or pull-up resistors affecting the input current.

4. OE/MR = 1 (outputs in high-impedance state).

| Symbol                          | Characteristics                                                                                                                 | Min        | Тур | Max                    | Unit       | Condition                |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------|-----|------------------------|------------|--------------------------|

| f <sub>REF</sub>                | Input Reference Frequency         ÷ 4 feedback <sup>2</sup> PLL Mode, External Feedback         ÷ 8 feedback <sup>3</sup>       | 50<br>25   |     | 125<br>62.5            | MHz<br>MHz | PLL locked<br>PLL locked |

|                                 | Input reference frequency in PLL bypass mode <sup>4</sup>                                                                       | 0          |     | 200                    | MHz        |                          |

| f <sub>VCO</sub>                | VCO Operating Frequency Range <sup>5, 6</sup>                                                                                   | 200        |     | 500                    | MHz        |                          |

| f <sub>VCOlock</sub>            | VCO Lock Frequency Range <sup>7</sup>                                                                                           | 145        |     | 500                    | MHz        |                          |

| f <sub>MAX</sub>                | Output Frequency $\div 4 \text{ feedback}^2 \\ \div 8 \text{ feedback}^3$                                                       | 50<br>25   |     | 125<br>62.5            | MHz<br>MHz | PLL locked<br>PLL locked |

| V <sub>PP</sub>                 | Peak-to-Peak Input Voltage PCLK                                                                                                 | 450        |     | 1000                   | mV         | LVPECL                   |

| V <sub>CMR</sub> <sup>8</sup>   | Common Mode Range PCLK                                                                                                          | 1.2        |     | V <sub>CC</sub> – 0.75 | V          | LVPECL                   |

| t <sub>PW, MIN</sub>            | Input Reference Pulse Width <sup>9</sup>                                                                                        | 2          |     |                        | ns         |                          |

| t <sub>(∅)</sub>                | Propagation Delay (static phase offset) <sup>10</sup> PCLK to FB_IN                                                             | -75        |     | 125                    | ps         | PLL locked               |

| t <sub>PD</sub>                 | Propagation Delay<br>PLL and divider bypass (BYPASS = 0), PCLK to Q0–7<br>PLL disable (BYPASS = 1 and PLL_EN = 0), PCLK to Q0–7 | 1.2<br>3.0 |     | 3.3<br>7.0             | ns<br>ns   |                          |

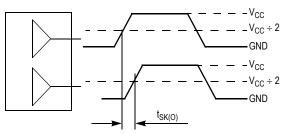

| t <sub>sk(O)</sub>              | Output-to-Output Skew <sup>11</sup>                                                                                             |            |     | 150                    | ps         |                          |

| t <sub>sk(PP)</sub>             | Device-to-Device Skew in PLL and Divider Bypass <sup>12</sup>                                                                   |            |     | 1.5                    | ns         | BYPASS = 0               |

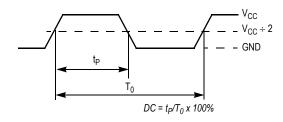

| DC                              | Output Duty Cycle                                                                                                               | 45         | 50  | 55                     | %          | PLL locked               |

| t <sub>R</sub> , t <sub>F</sub> | Output Rise/Fall Time                                                                                                           | 0.1        |     | 1.0                    | ns         | 0.55 to 2.4 V            |

| t <sub>PLZ, HZ</sub>            | Output Disable Time                                                                                                             |            |     | 7.0                    | ns         |                          |

| t <sub>PZL, LZ</sub>            | Output Enable Time                                                                                                              |            |     | 6.0                    | ns         |                          |

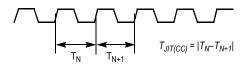

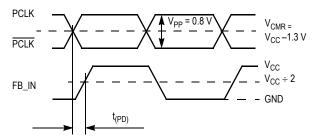

| t <sub>JIT(CC)</sub>            | Cycle-to-Cycle jitter                                                                                                           |            |     | 100                    | ps         |                          |

| $t_{\text{JIT}(\text{PER})}$    | Period Jitter                                                                                                                   |            |     | 100                    | ps         |                          |

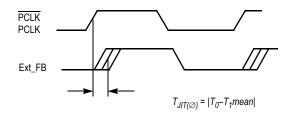

| t <sub>JIT(∅)</sub>             | I/O Phase Jitter <sup>13</sup> RMS (1σ)                                                                                         |            |     | 25                     | ps         |                          |

| BW                              | PLL closed loop bandwidth <sup>14</sup> ÷ 4 feedback <sup>2</sup>                                                               |            |     | 0.8 - 4                | MHz        |                          |

|                                 | ${\sf PLL} \ {\sf mode}, \ {\sf external} \ {\sf feedback} \qquad \qquad \div \ 8 \ {\sf feedback}^3$                           |            |     | 0.5 – 1.3              | MHz        |                          |

| t <sub>LOCK</sub>               | Maximum PLL Lock Time                                                                                                           |            |     | 10                     | ms         |                          |

#### Table 6. AC Characteristics $(V_{CC} = 3.3 \text{ V} \pm 5\%, T_A = 0^{\circ}\text{C to } 70^{\circ}\text{C})^1$

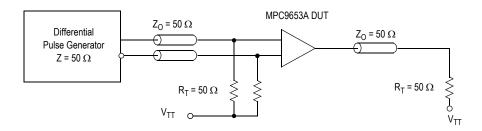

1. AC characteristics apply for parallel output termination of 50  $\Omega$  to V<sub>TT</sub>.

$\div$  4 PLL feedback (high frequency range) requires VCO\_SEL = 0, PLL\_EN = 1, BYPASS = 1 and MR/OE = 0. 2.

3. ÷8 PLL feedback (low frequency range) requires VCO\_SEL = 1, PLL\_EN = 1, BYPASS = 1 and MR/OE = 0.

4. In bypass mode, the MPC9653A divides the input reference clock.

5. The input frequency  $f_{REF}$  must match the VCO frequency range divided by the feedback divider ratio FB:  $f_{REF} = f_{VCO} \div FB$ .

6. f<sub>VCO</sub> is frequency range where AC parameters are guaranteed.

7.  $f_{VCOlock}$  is frequency range that the PLL guaranteed to lock, AC parameters only guaranteed over  $f_{VCO}$ .

8. V<sub>CMR</sub> (AC) is the crosspoint of the differential input signal. Normal AC operation is obtained when the crosspoint is within the V<sub>CMR</sub> range and the input swing lies within the VPP (AC) specification. Violation of VCMR or VPP impacts static phase offset to

Calculation of reference duty cycle limits:  $DC_{REF,MIN} = t_{PW,MIN} \cdot f_{REF} \cdot 100\%$  and  $DC_{REF,MAX} = 100\% - DC_{REF,MIN}$ . For example, at  $f_{REF} = 100$  MHz the input duty cycle range is 20% < DC < 80%. 9.

10. Valid for  $f_{REF}$  = 50 MHz and FB = ÷ 8 (VCO\_SEL = 1). For other reference frequencies:  $t_{(O)}$  [ps] = 50 ps ± (1 ÷ (120 · f\_{REF})).

11. Refer to the Application Information section for part-to-part skew calculation in PLL zero-delay mode.

12. For a specified temperature and voltage, includes output skew.

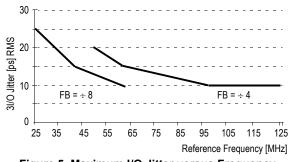

13. I/O phase jitter is reference frequency dependent. Refer to APPLICATIONS INFORMATION section for details.

14. -3 dB point of PLL transfer characteristics.

#### **APPLICATIONS INFORMATION**

#### Programming the MPC9653A

The MPC9653A supports output clock frequencies from 25 to 125 MHz. Two different feedback divider configurations can be used to achieve the desired frequency operation range. The feedback divider (VCO\_SEL) should be used to situate the VCO in the frequency lock range between 200 and 500 MHz for stable and optimal operation. Two operating frequency ranges

are supported: 25 to 62.5 MHz and 50 to 125 MHz. Table 7 illustrates the configurations supported by the MPC9653A. PLL zero-delay is supported if BYPASS = 1, PLL\_EN = 1 and the input frequency is within the specified PLL reference frequency range.

| DVDACC |        | 1400 OF | <b>2</b>                          | Frequency                   |                                   |                             |  |

|--------|--------|---------|-----------------------------------|-----------------------------|-----------------------------------|-----------------------------|--|

| BYPASS | PLL_EN | VCO_SEL | Operation                         | Ratio                       | Output Range (f <sub>Q0-7</sub> ) | VCO                         |  |

| 0      | Х      | Х       | Test mode: PLL and divider bypass | $f_{Q0-7} = f_{REF}$        | 0 – 200 MHz                       | n/a                         |  |

| 1      | 0      | 0       | Test mode: PLL bypass             | $f_{Q0-7} = f_{REF} \div 4$ | 0 – 50 MHz                        | n/a                         |  |

| 1      | 0      | 1       | Test mode: PLL bypass             | $f_{QO-7} = f_{REF} \div 8$ | 0 – 25 MHz                        | n/a                         |  |

| 1      | 1      | 0       | PLL mode (high frequency range)   | $f_{Q0-7} = f_{REF}$        | 50 to 125 MHz                     | $f_{VCO} = f_{REF} \cdot 4$ |  |

| 1      | 1      | 1       | PLL mode (low frequency range)    | $f_{Q0-7} = f_{REF}$        | 25 to 62.5 MHz                    | $f_{VCO} = f_{REF} \cdot 8$ |  |

#### Table 7. MPC9653A Configurations (QFB connected to FB\_IN)

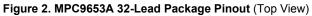

#### **Power Supply Filtering**

The MPC9653A is a mixed analog/digital product. Its analog circuitry is naturally susceptible to random noise, especially if this noise is seen on the power supply pins. Random noise on the  $V_{\text{CCA\_PLL}}$  power supply impacts the device characteristics, for instance I/O jitter. The MPC9653A provides separate power supplies for the output buffers ( $V_{CC}$ ) and the phase-locked loop  $(V_{CCA\ PLL})$  of the device. The purpose of this design technique is to isolate the high switching noise digital outputs from the relatively sensitive internal analog phase-locked loop. In a digital system environment where it is more difficult to minimize noise on the power supplies a second level of isolation may be required. The simple but effective form of isolation is a power supply filter on the  $V_{CC\ PLL}$  pin for the MPC9653A. Figure 3 illustrates a typical power supply filter scheme. The MPC9653A frequency and phase stability is most susceptible to noise with spectral content in the 100 kHz to 20 MHz range. Therefore, the filter should be designed to target this range. The key parameter that needs to be met in the final filter design is the DC voltage drop across the series filter resistor R<sub>F</sub>. From the data sheet the I<sub>CCA</sub> current (the current sourced through the V<sub>CC\_PLL</sub> pin) is typically 5 mA (10 mA maximum), assuming that a minimum of 2.985 V must be maintained on the V<sub>CC PLL</sub> pin.

Figure 3. V<sub>CC PLL</sub> Power Supply Filter

The minimum values for  $R_F$  and the filter capacitor  $C_F$  are defined by the required filter characteristics: the RC filter should provide an attenuation greater than 40 dB for noise whose spectral content is above 100 kHz. In the example RC filter shown in Figure 3, the filter cut-off frequency is around 4 kHz and the noise attenuation at 100 kHz is better than 42 dB.

As the noise frequency crosses the series resonant point of an individual capacitor its overall impedance begins to look inductive and thus increases with increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the bandwidth of the PLL. Although the MPC9653A has several design features to minimize the susceptibility to power supply noise (isolated power and grounds and fully differential PLL) there still may be applications in which overall performance is being degraded due to system power supply noise. The power supply filter schemes discussed in this section should be adequate to eliminate power supply noise related problems in most designs.

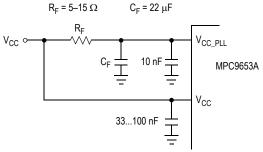

#### Using the MPC9653A in Zero-Delay Applications

Nested clock trees are typical applications for the MPC9653A. Designs using the MPC9653A as LVCMOS PLL fanout buffer with zero insertion delay will show significantly lower clock skew than clock distributions developed from CMOS fanout buffers. The external feedback option of the MPC9653A clock driver allows for its use as a zero-delay buffer. The PLL aligns the feedback clock output edge with the clock input reference edge resulting a near zero delay through the device (the propagation delay through the device is virtually eliminated). The maximum insertion delay of the device in zero-delay applications is measured between the reference clock input and any output. This effective delay consists of the static phase offset, I/O jitter (phase or long-term jitter), feedback path delay and the output-to-output skew error relative to the feedback output.

#### **Calculation of Part-to-Part Skew**

The MPC9653A zero delay buffer supports applications where critical clock signal timing can be maintained across several devices. If the reference clock inputs of two or more MPC9653As are connected together, the maximum overall timing uncertainty from the common PCLK input to any output is:

$t_{SK(PP)} = t_{(\mathcal{O})} + t_{SK(O)} + t_{PD, LINE(FB)} + t_{JIT(\mathcal{O})} \cdot CF$

This maximum timing uncertainty consist of 4 components: static phase offset, output skew, feedback board trace delay and I/O (phase) jitter:

Figure 4. MPC9653A Maximum Device-to-Device Skew

Due to the statistical nature of I/O jitter a RMS value (1  $\sigma$ ) is specified. I/O jitter numbers for other confidence factors (CF) can be derived from Table 8.

#### **Table 8. Confidence Factor CF**

| CF            | Probability of clock edge within the distribution |

|---------------|---------------------------------------------------|

| ±1σ           | 0.68268948                                        |

| $\pm 2\sigma$ | 0.95449988                                        |

| $\pm 3\sigma$ | 0.99730007                                        |

| $\pm 4\sigma$ | 0.99993663                                        |

| $\pm5\sigma$  | 0.99999943                                        |

| $\pm 6\sigma$ | 0.99999999                                        |

The feedback trace delay is determined by the board layout and can be used to fine-tune the effective delay through each device. In the following example calculation a I/O jitter confidence factor of 99.7% ( $\pm$  3 $\sigma$ ) is assumed, resulting in a worst case timing uncertainty from input to any output of –197 ps to 297 ps (at 125 MHz reference frequency) relative to PCLK:

$$\begin{split} t_{SK(PP)} = [-17ps...117ps] + [-150ps...150ps] + \\ [(10ps @ -3)...(10ps @ 3)] + t_{PD, \ LINE(FB)} \end{split}$$

$t_{SK(PP)} = [-197ps...297ps] + t_{PD, LINE(FB)}$

Due to the frequency dependence of the I/O jitter, Figure 5, can be used for a more precise timing performance analysis.

Figure 5. Maximum I/O Jitter versus Frequency

#### **Driving Transmission Lines**

The MPC9653A clock driver was designed to drive high speed signals in a terminated transmission line environment. To provide the optimum flexibility to the user the output drivers were designed to exhibit the lowest impedance possible. With an output impedance of less than 20  $\Omega$  the drivers can drive either parallel or series terminated transmission lines. For more information on transmission lines the reader is referred to Motorola application note AN1091. In most high performance clock networks point-to-point distribution of signals is the method of choice. In a point-to-point scheme either series terminated or parallel terminated transmission lines can be used. The parallel technique terminates the signal at the end of the line with a 50  $\Omega$  resistance to V<sub>CC</sub> ÷ 2.

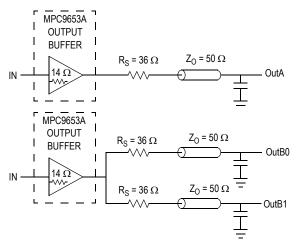

This technique draws a fairly high level of DC current and thus only a single terminated line can be driven by each output of the MPC9653A clock driver. For the series terminated case however there is no DC current draw, thus the outputs can drive multiple series terminated lines. Figure 5, illustrates an output driving a single series terminated line versus two series terminated lines in parallel. When taken to its extreme the fanout of the MPC9653A clock driver is effectively doubled due to its capability to drive multiple lines.

Figure 6. Single versus Dual Transmission Lines

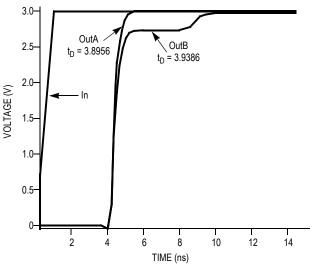

The waveform plots in Figure 7 show the simulation results of an output driving a single line versus two lines. In both cases the drive capability of the MPC9653A output buffer is more than sufficient to drive 50  $\Omega$  transmission lines on the incident edge. Note from the delay measurements in the simulations a delta of only 43 ps exists between the two differently loaded outputs. This suggests that the dual line driving need not be used exclusively to maintain the tight output-to-output skew of the MPC9653A. The output waveform in Figure 7 shows a step in the waveform, this step is caused by the impedance mismatch seen looking into the driver. The parallel combination of the 36  $\Omega$  series resistor plus the output impedance does not match the parallel combination of the line impedances. The voltage wave launched down the two lines will equal:

$$V_{L} = V_{S} (Z_{0} \div (R_{S} + R_{0} + Z_{0}))$$

$$Z_{0} = 50 \Omega || 50 \Omega$$

$$R_{S} = 36 \Omega || 36 \Omega$$

$$R_{0} = 14 \Omega$$

$$V_{L} = 3.0 (25 \div (18 + 14 + 25))$$

$$= 1.31 V$$

At the load end the voltage will double, due to the near unity reflection coefficient, to 2.6 V. It will then increment towards the quiescent 3.0 V in steps separated by one round trip delay (in this case 4.0 ns).

Figure 7. Single versus Dual Waveforms

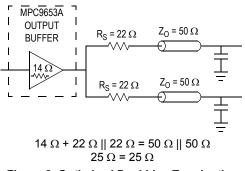

Since this step is well above the threshold region it will not cause any false clock triggering, however designers may be uncomfortable with unwanted reflections on the line. To better match the impedances when driving multiple lines the situation in Figure 8, should be used. In this case the series terminating resistors are reduced such that when the parallel combination is added to the output buffer impedance the line impedance is perfectly matched.

Figure 8. Optimized Dual Line Termination

Figure 9. MPC9653A AC Test Reference

IDT<sup>™</sup> 3.3 V 1:8 LVCMOS PLL Clock Generator

The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device

Figure 10. Output-to-Output Skew t<sub>SK(O)</sub>

The time from the PLL controlled edge to the non controlled edge, divided by the time between PLL controlled edges, expressed as a percentage

Figure 12. Output Duty Cycle (DC)

The variation in cycle time of a signal between adjacent cycles, over a random sample of adjacent cycle pairs

Figure 16. Output Transition Time Test Reference

Figure 11. Propagation delay (t<sub>(PD)</sub>, static phase offset) Test Reference

The deviation in  $t_0$  for a controlled edge with respect to a  $T_0$  mean in a random sample of cycles

Figure 13. I/O Jitter

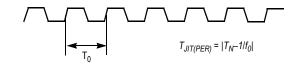

The deviation in cycle time of a signal with respect to the ideal period over a random sample of cycles

Figure 15. Period Jitter

Downloaded from Elcodis.com electronic components distributor

## Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA