# **Oscillator Frequency Upconverter**

AD9552

### **FEATURES**

Converts a low frequency input reference signal to a high frequency output signal

Input frequencies from 6.6 MHz to 112.5 MHz

Output frequencies up to 900 MHz

Preset pin programmable frequency translation ratios

Arbitrary frequency translation ratios via SPI port

**On-chip VCO**

Accepts a crystal resonator and/or an external oscillator as a reference frequency source

Secondary output (either integer-related to the primary output or a copy of the reference input)

RMS jitter: <0.5 ps

SPI-compatible, 3-wire programming interface

Single supply (3.3 V)

Very low power: <400 mW (under most conditions)

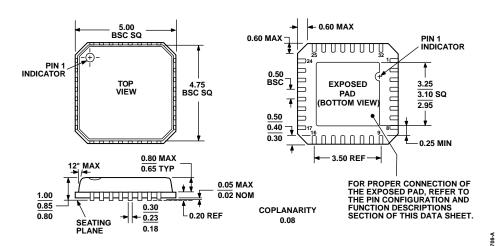

Small package size (5 mm × 5 mm)

### **APPLICATIONS**

Cost effective replacement of high frequency VCXO, OCXO, and SAW resonators

Extremely flexible frequency translation with low jitter for SONET/SDH (including FEC), 10 Gb Ethernet, Fibre Channel, and DRFI/DOCSIS

High-definition video frequency translation

Wireless infrastructure

Test and measurement (including handheld devices)

#### GENERAL DESCRIPTION

The AD9552 is a fractional-N phase locked loop (PLL) based clock generator designed specifically to replace high frequency crystal oscillators and resonators. The device employs a sigmadelta  $(\Sigma - \Delta)$  modulator (SDM) to accommodate fractional frequency synthesis. The user supplies an input reference signal by connecting a single-ended clock signal directly to the REF pin or by connecting a crystal resonator across the XTAL pins.

The AD9552 is pin programmable, providing one of 64 standard output frequencies based on one of eight common input frequencies. The device also has a 3-wire SPI interface, enabling the user to program custom input-to-output frequency ratios.

The AD9552 relies on an external capacitor to complete the loop filter of the PLL. The output is compatible with LVPECL, LVDS, or single-ended CMOS logic levels, although the AD9552 is implemented in a strictly CMOS process.

The AD9552 is specified to operate over the extended industrial temperature range of -40°C to +85°C.

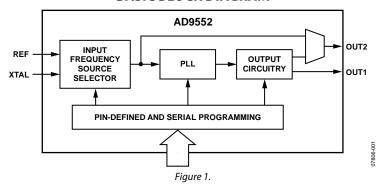

### **BASIC BLOCK DIAGRAM**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Fax: 781.461.3113 ©2009-2010 Analog Devices, Inc. All rights reserved.

| TABLE OF CONTENTS                                                                                                     |                                                      |    |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----|

| Features                                                                                                              | Preset Frequency Ratios                              | 1  |

| Applications1                                                                                                         | Component Blocks                                     | 1  |

| General Description                                                                                                   | Part Initialization and Automatic Power-On Reset     | 1  |

| Basic Block Diagram 1                                                                                                 | Output/Input Frequency Relationship                  | 1  |

| Revision History                                                                                                      | Calculating Divider Values                           | 1  |

| Specifications                                                                                                        | Low Dropout (LDO) Regulators                         | 18 |

| Crystal Input Characteristics                                                                                         | Applications Information                             | 19 |

| Output Characteristics4                                                                                               | Thermal Performance                                  | 19 |

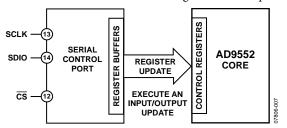

| Jitter Characteristics5                                                                                               | Serial Control Port                                  | 20 |

| Serial Control Port6                                                                                                  | Serial Control Port Pin Descriptions                 | 20 |

| Serial Control Port Timing6                                                                                           | Operation of the Serial Control Port                 | 20 |

| Absolute Maximum Ratings                                                                                              | Instruction Word (16 Bits)                           | 2  |

| ESD Caution                                                                                                           | MSB/LSB First Transfers                              | 2  |

| Pin Configuration and Function Descriptions 8                                                                         | Register Map                                         | 23 |

| Typical Performance Characteristics                                                                                   | Register Map Descriptions                            | 2  |

| Input/Output Termination Recommendations                                                                              | Outline Dimensions                                   | 30 |

| Theory of Operation                                                                                                   | Ordering Guide                                       | 30 |

| REVISION HISTORY                                                                                                      |                                                      |    |

| 7/10—Rev. B to Rev. C                                                                                                 | Changes to PLL Section, Output Dividers Section, and |    |

| Changed Crystal Load Capacitance to 15 pF Throughout                                                                  | Input-to-OUT2 Option Section                         |    |

| Added Conditions Statement to Specifications Section, Supply Voltage Specifications, and Input Voltage Specifications | Changes to Table 22                                  |    |

| Reformatted Specifications Section (Renumbered Sequentially)3                                                         | Changes to Table 26                                  | 20 |

| Added Input/Output Termination Recommendations Section,                                                               | 9/09—Rev. 0 to Rev. A                                |    |

| Figure 17, and Figure 18 (Renumbered Sequentially)                                                                    | Changes to Table 4                                   |    |

| Moved Preset Frequency Ratios Section                                                                                 | Changes to Table 5                                   |    |

| Changes to Component Blocks Section                                                                                   | Added Table 6; Renumbered Sequentially               |    |

| Reset Section                                                                                                         | Changes to Figure 5                                  |    |

|                                                                                                                       | Changes to PLL Section                               |    |

| 4/10—Rev. A to Rev. B                                                                                                 | Changes to Table 22                                  |    |

| Changes to Preset Frequency Ratios Section                                                                            | Changes to Table 25                                  | 2  |

| Moved Table 15 and Changes to Table 15                                                                                | 7/09—Revision 0: Initial Version                     |    |

# **SPECIFICATIONS**

Minimum (min) and maximum (max) values apply for the full range of supply voltage and operating temperature variations. Typical (typ) values apply for VDD = 3.3 V;  $T_A = 25 ^{\circ}\text{C}$ , unless otherwise noted.

Table 1.

| Parameter                             | Min   | Тур  | Max   | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                       |

|---------------------------------------|-------|------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLY VOLTAGE                        | 3.135 | 3.30 | 3.465 | V    | Pin 7, Pin 18, Pin 21, Pin 28                                                                                                                                                                                                                                                                  |

| POWER CONSUMPTION                     |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| Total Current                         |       | 149  | 169   | mA   | At maximum output frequency with both output channels active                                                                                                                                                                                                                                   |

| VDD Current By Pin                    |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| Pin 7                                 |       | 2    | 3     | mA   |                                                                                                                                                                                                                                                                                                |

| Pin 18                                |       | 77   | 86    | mA   |                                                                                                                                                                                                                                                                                                |

| Pin 21                                |       | 35   | 41    | mA   |                                                                                                                                                                                                                                                                                                |

| Pin 28                                |       | 35   | 41    | mA   |                                                                                                                                                                                                                                                                                                |

| LVPECL Output Driver                  |       | 36   | 41    | mA   | 900 MHz with 100 $\Omega$ termination between both pins of the output driver                                                                                                                                                                                                                   |

| LOGIC INPUT PINS                      |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| INPUT CHARACTERISTICS <sup>1</sup>    |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| Logic 1 Voltage, V⊪                   | 1.0   |      |       | V    | For the CMOS inputs, a static Logic 1 results from either a pull-up resistor or no connection                                                                                                                                                                                                  |

| Logic 0 Voltage, V <sub>I</sub> L     |       |      | 0.8   | V    |                                                                                                                                                                                                                                                                                                |

| Logic 1 Current, I <sub>IH</sub>      |       |      | 3     | μΑ   |                                                                                                                                                                                                                                                                                                |

| Logic 0 Current, I <sub>⊥</sub>       |       |      | 17    | μΑ   |                                                                                                                                                                                                                                                                                                |

| LOGIC OUTPUT PINS                     |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| Output Characteristics                |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| Output Voltage High, V <sub>OH</sub>  | 2.7   |      |       | V    |                                                                                                                                                                                                                                                                                                |

| Output Voltage Low, Vol               |       |      | 0.4   | V    |                                                                                                                                                                                                                                                                                                |

| RESET PIN                             |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| Input Characteristics <sup>2</sup>    |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| Input Voltage High, V <sub>H</sub>    | 1.8   |      |       | V    |                                                                                                                                                                                                                                                                                                |

| Input Voltage Low, V∟                 |       |      | 1.3   | V    |                                                                                                                                                                                                                                                                                                |

| Input Current High, I <sub>INH</sub>  |       | 0.3  | 12.5  | μΑ   |                                                                                                                                                                                                                                                                                                |

| Input Current Low, I <sub>INL</sub>   |       | 31   | 43    | μΑ   |                                                                                                                                                                                                                                                                                                |

| Minimum Pulse Width High              | 2     |      |       | ns   |                                                                                                                                                                                                                                                                                                |

| REFERENCE CLOCK INPUT CHARACTERISTICS |       |      |       |      |                                                                                                                                                                                                                                                                                                |

| Frequency Range                       | 7.94  |      |       | MHz  | $N^3 = 255$ ; 2× frequency multiplier enabled; valid for all VCO bands                                                                                                                                                                                                                         |

|                                       | 6.57  |      |       | MHz  | $N^3=255$ ; 2× frequency multiplier enabled; $f_{VCO}=3.35$ GHz, which constrains the frequency at OUT1 to be an integer sub-multiple of 3.35 GHz (that is, $f_{OUT1}=3.35 \div M$ GHz, where M is the product of the $P_0$ and $P_1$ output divider values)                                   |

|                                       |       |      | 93.06 | MHz  | SDM <sup>4</sup> disabled; $N^3 = 36^5$ ; valid for all VCO bands                                                                                                                                                                                                                              |

|                                       |       |      | 71.28 | MHz  | SDM <sup>4</sup> enabled; $N^3 = 47^6$ ; valid for all VCO bands                                                                                                                                                                                                                               |

|                                       |       |      | 112.5 | MHz  | SDM <sup>4</sup> disabled; N <sup>3</sup> = 36 <sup>5</sup> ; $f_{VCO}$ = 4.05 GHz, which constrains the frequency at OUT1 to be an integer sub-multiple of 4.05 GHz (that is, $f_{OUT1}$ = 4.05÷M GHz, where M is the product of the P <sub>0</sub> and P <sub>1</sub> output divider values) |

|                                       |       |      | 86.17 | MHz  | SDM <sup>4</sup> enabled; $N^3 = 47^6$ ; $f_{VCO} = 4.05$ GHz, which constrains the frequence at OUT1 to be an integer sub-multiple of 4.05 GHz (that is, $f_{OUT1} = 4.05 \div M$ GHz, where M is the product of the $P_0$ and $P_1$ output divider values)                                   |

| Parameter                           | Min  | Тур  | Max  | Unit  | Test Conditions/Comments                                                                                                                                  |

|-------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Capacitance                   |      | 3    |      | pF    |                                                                                                                                                           |

| Input Resistance                    |      | 130  |      | kΩ    |                                                                                                                                                           |

| Duty Cycle                          | 40   |      | 60   | %     |                                                                                                                                                           |

| Input Voltage                       |      |      |      |       |                                                                                                                                                           |

| Input High Voltage, V⊪              | 0.52 |      |      | V     |                                                                                                                                                           |

| Input Low Voltage, V <sub>I</sub> ∟ |      |      | 1.62 | V     |                                                                                                                                                           |

| Input Threshold Voltage             |      | 1.0  |      | V     | When ac coupling to the input receiver, the user must dc bias the input to 1 V                                                                            |

| VCO CHARACTERISTICS                 |      |      |      |       |                                                                                                                                                           |

| Frequency Range                     |      |      |      |       |                                                                                                                                                           |

| Upper Bound                         |      | 4050 |      | MHz   |                                                                                                                                                           |

| Lower Bound                         |      | 3350 |      | MHz   |                                                                                                                                                           |

| VCO Gain                            |      | 45   |      | MHz/V |                                                                                                                                                           |

| VCO Tracking Range                  | ±300 |      |      | ppm   |                                                                                                                                                           |

| VCO Calibration Time                |      | 140  |      | μs    | $f_{PFD}^{7} = 77.76$ MHz; time between completion of the VCO calibration command (the rising edge of CS (Pin 12)) to the rising edge of LOCKED (Pin 20). |

### **CRYSTAL INPUT CHARACTERISTICS**

Table 2.

| Parameter                   | Min | Тур | Max | Unit | Test Conditions/Comments                                                                                                                                                               |

|-----------------------------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CRYSTAL FREQUENCY           |     |     |     |      |                                                                                                                                                                                        |

| Range                       | 10  | 26  | 52  | MHz  |                                                                                                                                                                                        |

| Tolerance                   |     |     | 20  | ppm  |                                                                                                                                                                                        |

| CRYSTAL MOTIONAL RESISTANCE |     |     | 100 | Ω    |                                                                                                                                                                                        |

| CRYSTAL LOAD CAPACITANCE    |     | 15  |     | pF   | Using a crystal with a specified load capacitance other than 15 pF (8 pF to 24 pF) is possible, but necessitates using the SPI port to configure the AD9552 crystal input capacitance. |

### **OUTPUT CHARACTERISTICS**

Table 3.

| Parameter                                | Min        | Тур        | Max        | Unit | Test Conditions/Comments                                       |

|------------------------------------------|------------|------------|------------|------|----------------------------------------------------------------|

| LVPECL MODE                              |            |            |            |      |                                                                |

| Differential Output Voltage Swing        | 690        | 765        | 889        | mV   | Output driver static                                           |

| Common-Mode Output Voltage               | VDD – 1.77 | VDD – 1.66 | VDD - 1.20 | V    | Output driver static                                           |

| Frequency Range                          | 0          |            | 900        | MHz  |                                                                |

| Duty Cycle                               | 40         |            | 60         | %    | Up to 805 MHz output frequency                                 |

| Rise/Fall Time <sup>1</sup> (20% to 80%) |            | 255        | 305        | ps   | $100\Omega$ termination between both pins of the output driver |

$<sup>^1</sup>$  The A[2:0], Y[5:0], and OUTSEL pins have 100 k $\Omega$  internal pull-up resistors.  $^2$  The RESET pin has a 100 k $\Omega$  internal pull-up resistor, so the default state of the device is reset.  $^3$  N is the integer part of the feedback divider.

<sup>4</sup> Sigma-delta modulator.

5 The minimum allowable feedback divider value with the SDM disabled.

6 The minimum allowable feedback divider value with the SDM enabled.

$<sup>^{\</sup>rm 7}$  The frequency at the input to the phase-frequency detector.

| Parameter                                | Min   | Тур | Max   | Unit | Test Conditions/Comments                                                                       |

|------------------------------------------|-------|-----|-------|------|------------------------------------------------------------------------------------------------|

| LVDS MODE                                |       |     |       |      |                                                                                                |

| Differential Output Voltage Swing        |       |     |       |      |                                                                                                |

| Balanced, V <sub>OD</sub>                | 247   |     | 454   | mV   | Voltage swing between output pins; output driver static                                        |

| Unbalanced, ΔV <sub>OD</sub>             |       |     | 25    | mV   | Absolute difference between voltage swing of normal pin and inverted pin; output driver static |

| Offset Voltage                           |       |     |       |      |                                                                                                |

| Common Mode, Vos                         | 1.125 |     | 1.375 | V    | Output driver static                                                                           |

| Common-Mode Difference, ΔVos             |       |     | 25    | mV   | Voltage difference between output pins; output driver static                                   |

| Short-Circuit Output Current             |       | 17  | 24    | mA   |                                                                                                |

| Frequency Range                          | 0     |     | 900   | MHz  |                                                                                                |

| Duty Cycle                               | 40    |     | 60    | %    | Up to 805 MHz output frequency                                                                 |

| Rise/Fall Time <sup>1</sup> (20% to 80%) |       | 285 | 355   | ps   | $100\Omega$ termination between both pins of the output driver                                 |

| CMOS MODE                                |       |     |       |      |                                                                                                |

| Output Voltage High, V <sub>OH</sub>     |       |     |       |      | Output driver static; standard drive strength setting                                          |

| $I_{OH} = 10 \text{ mA}$                 | 2.8   |     |       | V    |                                                                                                |

| $I_{OH} = 1 \text{ mA}$                  | 2.8   |     |       | V    |                                                                                                |

| Output Voltage Low, V <sub>OL</sub>      |       |     |       |      | Output driver static; standard drive strength setting                                          |

| $I_{OL} = 10 \text{ mA}$                 |       |     | 0.5   | V    |                                                                                                |

| $I_{OL} = 1 \text{ mA}$                  |       |     | 0.3   | V    |                                                                                                |

| Frequency Range                          | 0     |     | 200   | MHz  | 3.3 V CMOS; standard drive strength setting                                                    |

| Duty Cycle                               | 45    |     | 55    | %    | At maximum output frequency                                                                    |

| Rise/Fall Time <sup>1</sup> (20% to 80%) |       | 500 | 745   | ps   | 3.3 V CMOS; standard drive strength setting; 15 pF load                                        |

$<sup>^{\</sup>rm 1}$  The listed values are for the slower edge (rise or fall).

# **JITTER CHARACTERISTICS**

Table 4.

| Parameter                 | Min | Тур  | Max | Unit   | Test Conditions/Comments                            |

|---------------------------|-----|------|-----|--------|-----------------------------------------------------|

| JITTER GENERATION         |     |      |     |        | Input = 19.44 MHz crystal resonator                 |

| 12 kHz to 20 MHz          |     | 0.64 |     | ps rms | $f_{OUT} = 622.08 \text{ MHz}$ (integer mode)       |

|                           |     | 0.70 |     | ps rms | f <sub>OUT</sub> = 625 MHz (fractional mode)        |

| 50 kHz to 80 MHz          |     | 0.47 |     | ps rms | f <sub>OUT</sub> = 622.08 MHz (integer mode)        |

|                           |     | 0.50 |     | ps rms | f <sub>OUT</sub> = 625 MHz (fractional mode)        |

| 4 MHz to 80 MHz           |     | 0.11 |     | ps rms | f <sub>OUT</sub> = 622.08 MHz (integer mode)        |

|                           |     | 0.12 |     | ps rms | $f_{OUT} = 625 \text{ MHz}$ (fractional mode)       |

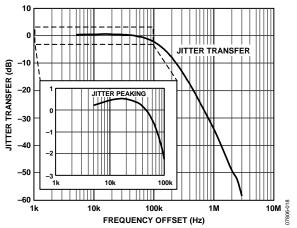

| JITTER TRANSFER BANDWIDTH |     | 100  |     | kHz    | See the Typical Performance Characteristics section |

| JITTER TRANSFER PEAKING   |     | 0.3  |     | dB     | See the Typical Performance Characteristics section |

# **SERIAL CONTROL PORT**

Table 5.

| Parameter              | Min | Тур | Max  | Unit | Test Conditions/Comments |

|------------------------|-----|-----|------|------|--------------------------|

| CS                     |     |     |      |      |                          |

| Input Logic 1 Voltage  | 1.6 |     |      | V    |                          |

| Input Logic 0 Voltage  |     |     | 0.5  | V    |                          |

| Input Logic 1 Current  |     |     | 0.03 | μΑ   |                          |

| Input Logic 0 Current  |     | 2   |      | μΑ   |                          |

| Input Capacitance      |     | 2   |      | рF   |                          |

| SCLK                   |     |     |      |      |                          |

| Input Logic 1 Voltage  | 1.6 |     |      | V    |                          |

| Input Logic 0 Voltage  |     |     | 0.5  | V    |                          |

| Input Logic 1 Current  |     | 2   |      | μΑ   |                          |

| Input Logic 0 Current  |     |     | 0.03 | μΑ   |                          |

| Input Capacitance      |     | 2   |      | рF   |                          |

| SDIO                   |     |     |      |      |                          |

| Input                  |     |     |      |      |                          |

| Input Logic 1 Voltage  | 1.6 |     |      | V    |                          |

| Input Logic 0 Voltage  |     |     | 0.5  | V    |                          |

| Input Logic 1 Current  |     | 1   |      | μΑ   |                          |

| Input Logic 0 Current  |     | 1   |      | μΑ   |                          |

| Input Capacitance      |     | 2   |      | рF   |                          |

| Output                 |     |     |      |      |                          |

| Output Logic 1 Voltage | 2.8 |     |      | V    | 1 mA load current        |

| Output Logic 0 Voltage |     |     | 0.3  | V    | 1 mA load current        |

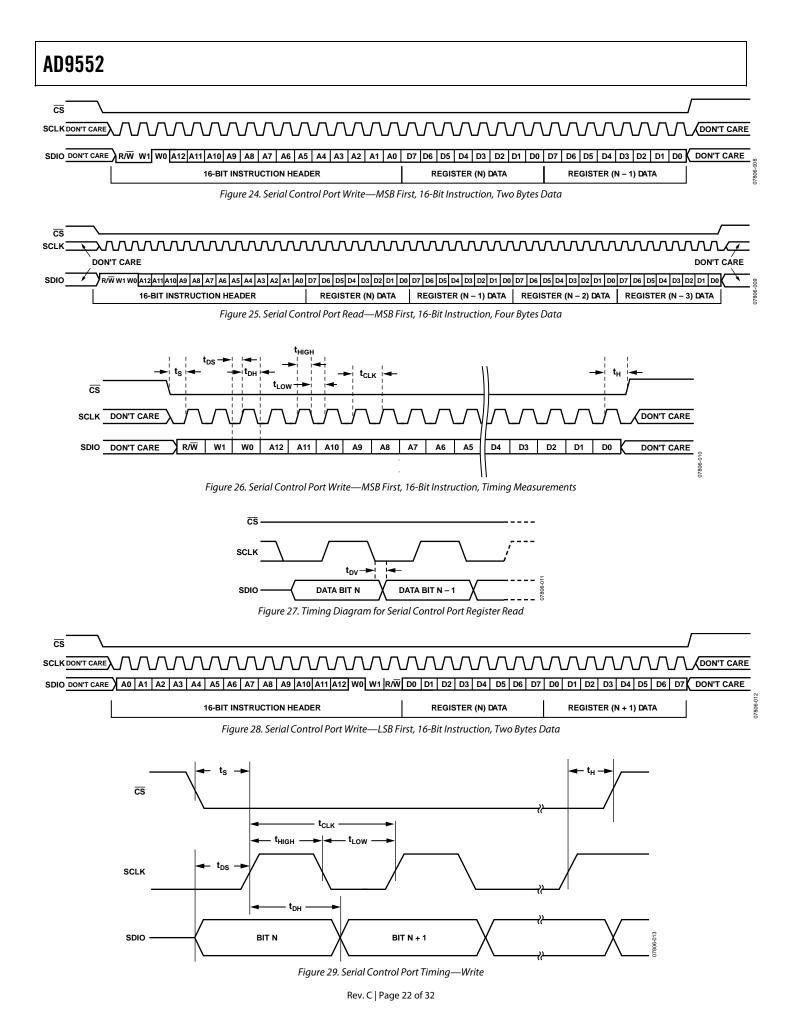

# **SERIAL CONTROL PORT TIMING**

Table 6.

| Parameter                                                         | Limit | Unit    |

|-------------------------------------------------------------------|-------|---------|

| SCLK                                                              |       |         |

| Clock Rate, 1/t <sub>CLK</sub>                                    | 50    | MHz max |

| Pulse Width High, t <sub>HIGH</sub>                               | 3     | ns min  |

| Pulse Width Low, t <sub>LOW</sub>                                 | 3     | ns min  |

| SDIO to SCLK Setup, t <sub>DS</sub>                               | 4     | ns min  |

| SCLK to SDIO Hold, t <sub>DH</sub>                                | 0     | ns min  |

| SCLK to Valid SDIO, t <sub>DV</sub>                               | 13    | ns max  |

| $\overline{\text{CS}}$ to SCLK Setup ( $t_s$ ) and Hold ( $t_H$ ) | 0     | ns min  |

| CS Minimum Pulse Width High                                       | 6.4   | ns min  |

# **ABSOLUTE MAXIMUM RATINGS**

### Table 7.

| Parameter                            | Rating                |

|--------------------------------------|-----------------------|

| Supply Voltage (VDD)                 | 3.6 V                 |

| Maximum Digital Input Voltage        | -0.5 V to VDD + 0.5 V |

| Storage Temperature                  | −65°C to +150°C       |

| Operating Temperature Range          | −40°C to +85°C        |

| Lead Temperature (Soldering, 10 sec) | 300°C                 |

| Junction Temperature                 | 150°C                 |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

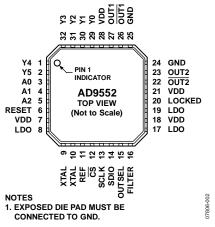

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin No.                 | Mnemonic                  | Type <sup>1</sup> | Description                                                                                                                                                                                                                                          |

|-------------------------|---------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29, 30, 31,<br>32, 1, 2 | Y0, Y1, Y2, Y3, Y4,<br>Y5 | I                 | Control Pins. These pins select preset values for the PLL feedback divider and the OUT1 dividers based on the input reference frequency selected via the A[0:2] pins and have internal 100 k $\Omega$ pull-up resistors.                             |

| 3, 4, 5                 | A0, A1, A2                | 1                 | Control Pins. These pins select the input reference frequency and have internal 100 k $\Omega$ pullup resistors.                                                                                                                                     |

| 6                       | RESET                     | 1                 | Digital Input, Active High. Resets internal logic to default states. This pin has an internal 100 k $\Omega$ pull-up resistor, so the default state of the device is reset.                                                                          |

| 7, 18, 21, 28           | VDD                       | Р                 | Power Supply Connection: 3.3 V Analog Supply.                                                                                                                                                                                                        |

| 8, 17, 19               | LDO                       | P/O               | LDO Decoupling Pins. Connect a 0.47 µF decoupling capacitor from each of these pins to ground.                                                                                                                                                       |

| 9, 10                   | XTAL                      | 1                 | Crystal Resonator Input. Connect a crystal resonator across these pins.                                                                                                                                                                              |

| 11                      | REF                       | 1                 | Reference Clock Input. Connect this pin to an active clock input signal, or connect it to VDD when using a crystal resonator across the XTAL pins.                                                                                                   |

| 12                      | CS                        | 1                 | Digital Input, Active Low, Chip Select.                                                                                                                                                                                                              |

| 13                      | SCLK                      | 1                 | Serial Data Clock.                                                                                                                                                                                                                                   |

| 14                      | SDIO                      | I/O               | Digital Serial Data Input/Output.                                                                                                                                                                                                                    |

| 15                      | OUTSEL                    | I                 | Logic 0 selects LVDS and Logic 1 selects LVPECL-compatible levels for both OUT1 and OUT2 when the outputs are not under SPI port control. Can be overridden via the programming registers. This pin has an internal 100 k $\Omega$ pull-up resistor. |

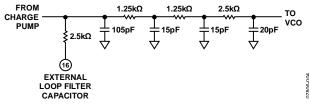

| 16                      | FILTER                    | I/O               | Loop Filter Node for the PLL. Connect an external 12 nF capacitor from this pin to Pin 17 (LDO).                                                                                                                                                     |

| 20                      | LOCKED                    | 0                 | Active High Locked Status Indicator for the PLL.                                                                                                                                                                                                     |

| 26, 22                  | OUT1, OUT2                | 0                 | Complementary Square Wave Clocking Outputs.                                                                                                                                                                                                          |

| 27, 23                  | OUT1, OUT2                | 0                 | Square Wave Clocking Outputs.                                                                                                                                                                                                                        |

| 24, 25                  | GND                       | Р                 | Analog Ground.                                                                                                                                                                                                                                       |

| EP                      | Exposed Die Pad           |                   | The exposed die pad must be connected to GND.                                                                                                                                                                                                        |

$<sup>^{1}</sup>$  I = input, I/O = input/output, O = output, P = power, P/O = power/output.

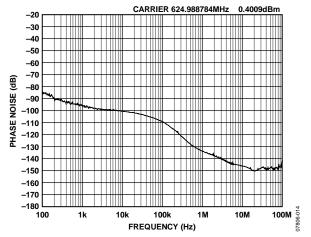

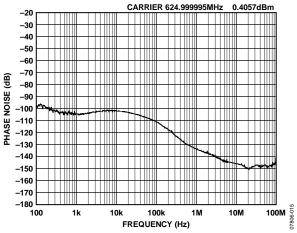

# TYPICAL PERFORMANCE CHARACTERISTICS

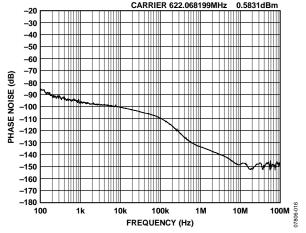

Figure 3. Phase Noise, Fractional-N, Pin Programmed  $(f_{XTAL} = 19.44 \text{ MHz}, f_{OUT1} = 625 \text{ MHz})$

Figure 4. Phase Noise, Fractional-N, Pin Programmed  $(f_{REF} = 19.44 \text{ MHz}, f_{OUT1} = 625 \text{ MHz})$

Figure 5. Jitter Transfer and Jitter Peaking

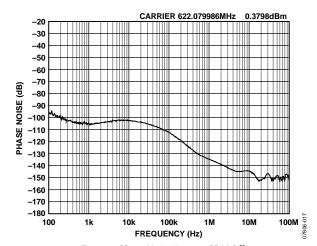

Figure 6. Phase Noise, Integer, SDM Off  $(f_{XTAL} = 19.44 \text{ MHz}, f_{OUT1} = 622.08 \text{ MHz})$

Figure 7. Phase Noise, Integer, SDM Off (f<sub>REF</sub> = 19.44 MHz, f<sub>OUT1</sub> = 622.08 MHz)

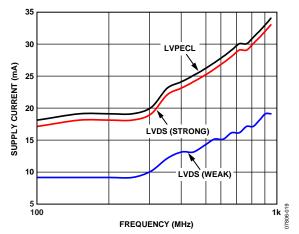

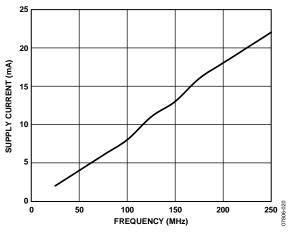

Figure 8. Supply Current vs. Output Frequency, LVPECL and LVDS (15 pF Load)

Figure 9. Supply Current vs. Output Frequency, CMOS (15 pF Load)

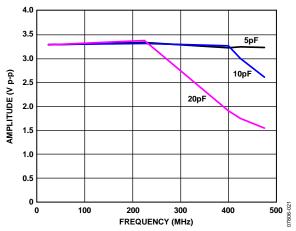

Figure 10. Peak-to-Peak Output Voltage vs. Frequency, CMOS

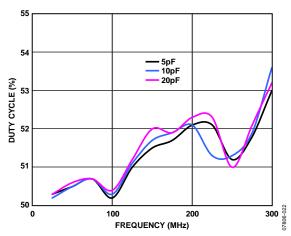

Figure 11. Duty Cycle vs. Output Frequency, CMOS

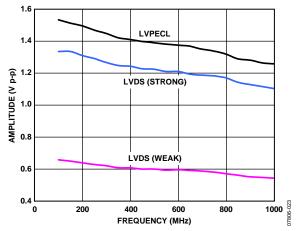

Figure 12. Peak-to-Peak Output Voltage vs. Frequency, LVPECL and LVDS (15 pF Load)

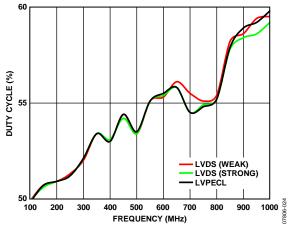

Figure 13. Duty Cycle vs. Output Frequency, LVPECL and LVDS (15 pF Load)

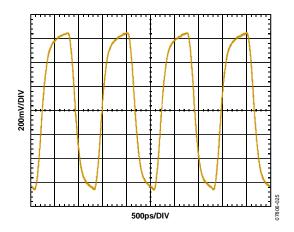

Figure 14. Typical Output Waveform, LVPECL (805 MHz)

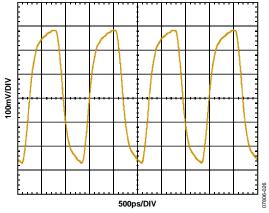

Figure 15. Typical Output Waveform, LVDS (805 MHz, 3.5 mA Drive Current)

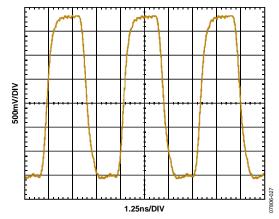

Figure 16. Typical Output Waveform, CMOS (250 MHz, 15 pF Load)

# INPUT/OUTPUT TERMINATION RECOMMENDATIONS

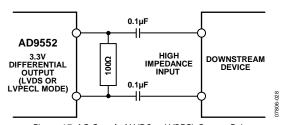

Figure 17. AC-Coupled LVDS or LVPECL Output Driver

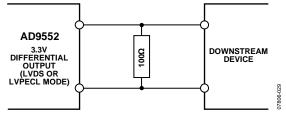

Figure 18. DC-Coupled LVDS or LVPECL Output Driver

# THEORY OF OPERATION

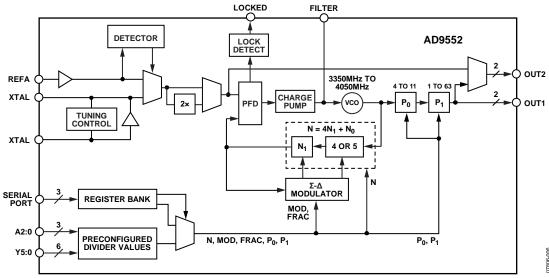

Figure 19. Detailed Block Diagram

### PRESET FREQUENCY RATIOS

The frequency selection pins (A[2:0] and Y[5:0]) allow the user to hardwire the device for preset input and output divider values based on the pin logic states (see Figure 19). The pins decode ground or open connections as Logic 0 or Logic 1, respectively. Use the serial I/O port to change the divider values from the preset values provided by the A[2:0] and Y[5:0] pins.

The A[2:0] pins select one of eight input reference frequencies (see Table 9). The user supplies the input reference frequency by connecting a single-ended clock signal to the REF pin or a crystal resonator across the XTAL pins. If the A[2:0] pins select 10 MHz, 12 MHz, 12.8 MHz, or 16 MHz, the input frequency to the AD9552 doubles internally. Alternatively, if Register 0x1D[2] is set to 1, the input frequency doubles.

Table 9. Input Reference Frequency Selection Pins

| A2 | A1 | A0 | Reference Frequency (MHz) |

|----|----|----|---------------------------|

| 0  | 0  | 0  | 10.00                     |

| 0  | 0  | 1  | 12.00                     |

| 0  | 1  | 0  | 12.80                     |

| 0  | 1  | 1  | 16.00                     |

| 1  | 0  | 0  | 19.20                     |

| 1  | 0  | 1  | 19.44                     |

| 1  | 1  | 0  | 20.00                     |

| 1  | 1  | 1  | 26.00                     |

The Y[5:0] pins select the appropriate feedback and output dividers to synthesize the output frequencies (see Table 10). The output frequencies provided in Table 10 are exact; that is, the number of decimal places displayed is sufficient to maintain full precision. Where a decimal representation is not practical, a fractional multiplier is used.

The VCO and output frequency shift in frequency by a ratio of the reference frequency used vs. the frequency specified in Table 9. Note that the VCO frequency must stay within the minimum and maximum range specified in Table 1. Typically, the selection of the VCO frequency band, as well as the gain adjustment, by the external pin strap occurs as part of the device's automatic VCO calibration process, which initiates at power up (or reset). If the user changes the VCO frequency band via the SPI interface, however, a forced VCO calibration should be initiated by first enabling SPI control of the VCO calibration (Register 0x0E[2] = 1) and then writing a 1 to the calibrate VCO bit (Register 0x0E[7]).

**Table 10. Output Frequency Selection Pins**

| Ys         Ya         Y3         Y2         Y1         Y0         VCO Frequency (MHz)         Output (MHz)           0         0         0         0         0         373248         51.84           0         0         0         0         0         1         3888         54           0         0         0         0         1         0         3840         60           0         0         0         1         1         0         3840         60           0         0         0         1         0         0         3352.16         61.44           0         0         0         1         0         1         3733.296         66.666           0         0         0         1         1         0         3560.439         74.17582           0         0         0         1         1         1         3564         74.25           0         0         1         0         0         3332.16         98.304         77.76           0         0         1         0         0         1         33932.16         98.304         98.304           0                                      |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 0         0         0         0         1         3888         54           0         0         0         0         1         0         3840         60           0         0         0         0         1         1         3932.16         61.44           0         0         0         1         0         0         3750         62.5           0         0         0         1         0         1         3732.296         66.666           0         0         0         1         1         0         3732.296         66.666           0         0         0         1         1         0         3732.48         74.756           0         0         1         0         0         0         3732.48         77.76           0         0         1         0         0         0         1000         100         100           0         0         1         0         1         0         4000         100         100         100         100         100         100         100         120         100         120         120         100         120 <td< th=""><th></th></td<>           |        |

| 0         0         0         0         1         0         3840         60           0         0         0         1         1         3932.16         61.44           0         0         0         1         0         0         3750         62.5           0         0         0         1         0         1         3733.296         66.666           0         0         0         1         1         0         3560.439         74.17582           0         0         0         1         1         1         1         474.25           0         0         1         0         0         3732.48         77.76           0         0         1         0         0         1         3932.16         98.304           0         0         1         0         0         4000         100         100         100         100         100         100         100         100         100         100         120         100         120         100         120         100         120         100         120         100         120         120         100         120                      |        |

| 0         0         0         0         1         1         3932.16         61.44           0         0         0         1         0         0         3750         62.5           0         0         0         1         0         0         3750         62.5           0         0         0         1         1         0         3560439         74.17582           0         0         0         1         1         1         3564         74.25           0         0         0         1         1         1         3564         74.25           0         0         1         0         0         0         3732.48         77.76           0         0         1         0         0         4000         100         100           0         0         1         0         1         0         4000         100         100         100         100         100         100         125         106.25         106.25         106.25         106.25         100         125         106.25         100         125         100         125         100         125         133         <         |        |

| 0         0         0         1         0         0         3750         62.5           0         0         0         1         0         1         3732.96         66.666           0         0         0         1         1         1         0         3560.439         74.17582           0         0         0         1         1         1         3564         74.25           0         0         1         0         0         0         3732.48         77.76           0         0         1         0         0         1         3932.16         98.304           0         0         1         0         1         0         4000         100           0         0         1         0         1         0         4000         100           0         0         1         1         0         0         3840         120           0         0         1         1         0         0         3840         120           0         0         1         1         1         0         3724         133           0         0         1                                                       |        |

| 0         0         0         1         0         1         3733.296         66.666           0         0         0         1         1         0         3560.439         74.17582           0         0         0         1         1         1         3564         74.25           0         0         1         0         0         3732.48         77.76           0         0         1         0         0         4000         100           0         0         1         0         4000         100         100           0         0         1         0         4000         100         125           0         0         1         1         0         3840         120           0         0         1         1         0         3840         120           0         0         1         1         0         3724         133           0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         3750         156.25           0         1                                                             |        |

| 0         0         0         1         1         0         3560.439         74.17582           0         0         0         1         1         1         3564         74.25           0         0         1         0         0         0         3732.48         77.76           0         0         1         0         0         1         3932.16         98.304           0         0         1         0         0         1         3932.16         98.304           0         0         1         0         1         0         4000         100           0         0         1         1         0         0         3840         120           0         0         1         1         0         0         3724         133           0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         3750         156.25           0         1         0         0         0         3867.188         161.1328125           0         1         0         0                                                       |        |

| 0         0         0         1         1         1         3564         74.25           0         0         1         0         0         3732.48         77.76           0         0         1         0         0         1         3932.16         98.304           0         0         1         0         1         0         4000         100           0         0         1         0         1         0         4000         100           0         0         1         1         0         0         3840         120           0         0         1         1         0         0         3840         120           0         0         1         1         0         0         3840         120           0         0         1         1         0         0         3724         133           0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         3750         156.25           0         1         0         0         3867.188         1                                                       |        |

| 0         0         1         0         0         3732,48         77.76           0         0         1         0         0         1         3932,16         98,304           0         0         1         0         1         0         4000         100           0         0         1         0         1         1         3825         106,25           0         0         1         1         0         0         3840         120           0         0         1         1         0         0         3840         120           0         0         1         1         0         3724         133         133           0         0         1         1         1         1         3732,48         155,52           0         1         0         0         0         3750         156,25           0         1         0         0         0         3750         156,25           0         1         0         0         3867,188         161,1328125           0         1         0         0         3867,188         161,1328125                                                         |        |

| 0         0         1         0         0         1         3932.16         98.304           0         0         1         0         1         0         4000         100           0         0         1         0         1         1         3825         106.25           0         0         1         1         0         0         3840         120           0         0         1         1         0         1         4000         125           0         0         1         1         0         1         4000         125           0         0         1         1         1         0         3724         133           0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         3750         156.25           0         1         0         0         3750         156.25           0         1         0         3867.188         161.1328125           0         1         0         0         3999.086         155.52 × (15/14)           0                                                         |        |

| 0         0         1         0         1         0         4000         100           0         0         1         0         1         1         3825         106.25           0         0         1         1         0         0         3840         120           0         0         1         1         0         1         4000         125           0         0         1         1         1         0         3724         133           0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         3750         156.25           0         1         0         0         0         3750         156.25           0         1         0         0         1         3825.188         161.1328125           0         1         0         0         1         3944.531         10518.7564           0         1         0         0         3999.086         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (255/237)                                             |        |

| 0         0         1         0         1         0         4000         100           0         0         1         0         1         1         3825         106.25           0         0         1         1         0         0         3840         120           0         0         1         1         0         1         4000         125           0         0         1         1         1         0         3724         133           0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         3750         156.25           0         1         0         0         0         3750         156.25           0         1         0         0         1         3825         159.375           0         1         0         0         1         3944.531         10518.7564           0         1         0         0         3999.086         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (255/23) <t< td=""><td></td></t<>                             |        |

| 0         0         1         0         1         1         3825         106.25           0         0         1         1         0         0         3840         120           0         0         1         1         0         1         4000         125           0         0         1         1         1         0         3724         133           0         0         1         1         1         1         1         155.52           0         1         0         0         0         0         3750         156.25           0         1         0         0         0         1         3825         159.375           0         1         0         0         1         3825         159.375           0         1         0         0         3867.188         161.1328125           0         1         0         0         3999.086         155.52 x (15/14)           0         1         0         1         0         155.52 x (15/14)           0         1         0         1         401.599         155.52 x (15/14)           0                                                |        |

| 0         0         1         1         0         0         3840         120           0         0         1         1         0         1         4000         125           0         0         1         1         1         0         3724         133           0         0         1         1         1         1         3750         156.25           0         1         0         0         0         3750         156.25           0         1         0         0         0         3825         159.375           0         1         0         0         1         3825         159.375           0         1         0         0         3867.188         161.1328125           0         1         0         0         3994.531         10518.7564           0         1         0         0         3999.86         155.52 × (15/14)           0         1         0         1         0         1         0518.75/64           0         1         0         1         0         1         4023.878         167.6616           0         1         <                                         |        |

| 0         0         1         1         4000         125           0         0         1         1         1         0         3724         133           0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         0         3750         156.25           0         1         0         0         0         1         3825         159.375           0         1         0         0         1         3825         159.375           0         1         0         0         3867.188         161.1328125           0         1         0         0         3994.531         10518.75/64           0         1         0         0         3999.086         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (15/14)           0         1         0         1         1         3354.742         177.7371           0         1         1         0                                    |        |

| 0         0         1         1         1         0         3724         133           0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         3750         156.25           0         1         0         0         1         3825         159.375           0         1         0         0         1         3867.188         161.1328125           0         1         0         0         1         3944.531         10518.75/64           0         1         0         0         3999.086         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         4023.878         167.6616           0         1         0         1         1         3554.742         177.7371           0         1         1         0         0         3932.16         245.76           0         1         1         0 <td></td>           |        |

| 0         0         1         1         1         1         3732.48         155.52           0         1         0         0         0         3750         156.25           0         1         0         0         1         3825         159.375           0         1         0         0         1         0         3867.188         161.1328125           0         1         0         0         1         1         3944.531         10518.75/64           0         1         0         0         3999.086         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         1         0         4023.878         167.6616           0         1         1         0         0         3932.16         245.76         245.76           0         1         1         0         0         3732.48         311.04         31 |        |

| 0         1         0         0         0         3750         156.25           0         1         0         0         0         1         3825         159.375           0         1         0         0         1         0         3867.188         161.1328125           0         1         0         0         1         1         3944.531         10518.75/64           0         1         0         1         0         3999.086         155.52 x (15/14)           0         1         0         1         4015.959         155.52 x (255/237)           0         1         0         1         1         4015.959         155.52 x (255/237)           0         1         0         1         1         0         4023.878         167.6616           0         1         0         1         1         3554.742         177.7371           0         1         1         0         0         3932.16         245.76           0         1         1         0         3732.48         311.04           0         1         1         0         4000         3747.4         433.925 <td></td>    |        |

| 0         1         0         0         0         1         3825         159.375           0         1         0         0         1         0         3867.188         161.1328125           0         1         0         0         1         1         3944.531         10518.75/64           0         1         0         1         0         3999.086         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         1         0         4023.878         167.6616           0         1         0         1         1         1         3554.742         177.7371           0         1         1         0         0         3932.16         245.76           0         1         1         0         0         3732.48         311.04           0         1         1         0         1         3840         320           0         1         1         1         0         4000         400           0         1         1         1         0         3718.75         531.25                   |        |

| 0         1         0         0         1         0         3867.188         161.1328125           0         1         0         0         1         1         3944.531         10518.75/64           0         1         0         1         0         3999.086         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         1         0         4023.878         167.6616           0         1         0         1         1         1         3554.742         177.7371           0         1         1         0         0         3932.16         245.76           0         1         1         0         0         3732.48         311.04           0         1         1         0         1         4000         250           0         1         1         0         0         4000         3732.48         311.04           0         1         1         1         0         0         4000         400         400           0         1         1         1         0 <td></td>             |        |

| 0       1       0       0       1       1       3944.531       10518.75/64         0       1       0       1       0       3999.086       155.52 × (15/14)         0       1       0       1       4015.959       155.52 × (255/237)         0       1       0       1       1       0       4023.878       167.6616         0       1       0       1       1       1       3554.742       177.7371         0       1       1       0       0       3932.16       245.76         0       1       1       0       0       3932.16       245.76         0       1       1       0       0       3732.48       311.04         0       1       1       0       1       4000       250         0       1       1       0       0       4000       320         0       1       1       1       0       4000       400         0       1       1       1       0       3718.75       531.25         0       1       1       1       1       1       3732.48       622.08         1                                                                                                                                    |        |

| 0         1         0         1         0         3999.086         155.52 × (15/14)           0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         1         0         4023.878         167.6616           0         1         0         1         1         1         3554.742         177.7371           0         1         1         0         0         3932.16         245.76           0         1         1         0         0         1         4000         250           0         1         1         0         0         1         4000         250           0         1         1         0         1         3732.48         311.04           0         1         1         0         0         4000         400           0         1         1         1         0         4000         400           0         1         1         1         0         3718.75         531.25           0         1         1         1         1         3732.48         622.08           1 <td></td>                             |        |

| 0         1         0         1         4015.959         155.52 × (255/237)           0         1         0         1         1         0         4023.878         167.6616           0         1         0         1         1         1         3554.742         177.7371           0         1         1         0         0         0         3932.16         245.76           0         1         1         0         0         1         4000         250           0         1         1         0         0         1         4000         250           0         1         1         0         1         3732.48         311.04           0         1         1         0         0         4000         320           0         1         1         1         0         4000         400         400           0         1         1         1         0         3718.75         531.25         531.25           0         1         1         1         1         1         3763.2         537.6           1         0         0         0         0         37                                     |        |

| 0       1       0       1       1       0       4023.878       167.6616         0       1       0       1       1       1       3554.742       177.7371         0       1       1       0       0       0       3932.16       245.76         0       1       1       0       0       1       4000       250         0       1       1       0       1       0       3732.48       311.04         0       1       1       0       1       1       3840       320         0       1       1       1       0       0       4000       400         0       1       1       1       0       0       4000       400         0       1       1       1       0       3718.75       531.25       531.25         0       1       1       1       1       1       3763.2       537.6         1       0       0       0       3984.375       569.1964         1       0       0       0       3748.229       624.7048         1       0       0       0       3748.229       624.7048                                                                                                                                      | `      |

| 0         1         0         1         1         1         3554.742         177.7371           0         1         1         0         0         0         3932.16         245.76           0         1         1         0         0         1         4000         250           0         1         1         0         1         0         3732.48         311.04           0         1         1         0         1         1         3840         320           0         1         1         1         0         0         4000         400           0         1         1         1         0         0         4000         400           0         1         1         1         0         3718.75         531.25           0         1         1         1         1         3763.2         537.6           1         0         0         0         3984.375         569.1964           1         0         0         0         3748.229         624.7048           1         0         0         0         3748.229         624.7048           1 <td>)</td>                                      | )      |

| 0       1       1       0       0       0       3932.16       245.76         0       1       1       0       0       1       4000       250         0       1       1       0       1       0       3732.48       311.04         0       1       1       0       1       1       3840       320         0       1       1       1       0       0       4000       400         0       1       1       1       0       0       4000       400         0       1       1       1       0       0       4000       400         0       1       1       1       0       3718.75       531.25       531.25         0       1       1       1       1       1       3763.2       537.6       537.6         1       0       0       0       0       3984.375       569.1964         1       0       0       0       1       3732.48       622.08         1       0       0       0       1       3748.229       624.7048         1       0       0       0       3748.2                                                                                                                                               |        |