# ASSP

Single Serial Input PLL Frequency Synthesizer On-chip 2.5 GHz Prescaler

# **MB15E07SL**

# DESCRIPTION

The Fujitsu MB15E07SL is a serial input Phase Locked Loop (PLL) frequency synthesizer with a 2.5 GHz prescaler. The 2.5 GHz prescaler has a dual modulus division ratio of 32/33 or 64/65 enabling pulse swallowing operation.

The supply voltage range is between 2.4 V and 3.6 V. The MB15E07SL uses the latest BiCMOS process, as a result the supply current is typically 3.5 mA at 2.7 V. A refined charge pump supplies well-balanced output currents of 1.5 mA and 6 mA. The charge pump current is selectable by serial data.

MB15E07SL is ideally suited for wireless mobile communications, such as GSM (Global System for Mobile Communications) and PCS.

# ■ FEATURES

- High frequency operation: 2.5 GHz Max

- Low power supply voltage: Vcc = 2.4 to 3.6 V

- Ultra Low power supply current: Icc = 3.5 mA Typ (Vcc = Vp = 2.7 V, Ta = +25°C, in locking state)

$I_{CC}$  = 4.0 mA Typ ( $V_{CC}$  =  $V_P$  = 3.0 V, Ta = +25°C, in locking state)

• Direct power saving function: Power supply current in power saving mode Typ 0.1  $\mu$ A (Vcc = Vp = 3.0 V, Ta = +25°C), Max 10  $\mu$ A (Vcc = Vp = 3.0 V)

(Continued)

FUJITSU

#### (Continued)

- Dual modulus prescaler: 32/33 or 64/65

- Serial input 14-bit programmable reference divider: R = 3 to 16,383

- Serial input programmable divider consisting of:

- Binary 7-bit swallow counter: 0 to 127

- Binary 11-bit programmable counter: 3 to 2,047

- Software selectable charge pump current

- On-chip phase control for phase comparator

- Operating temperature: Ta = -40 to +85°C

- Pin compatible with MB15E07, MB15E07L

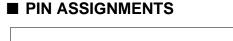

# ■ PIN DESCRIPTIONS

| Pin  | no. | Pin     | I/O | Descriptions                                                                                                                                                                                                                                                 |

|------|-----|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSOP | BCC | name    | 1/0 | Descriptions                                                                                                                                                                                                                                                 |

| 1    | 16  | OSCIN   | I   | Programmable reference divider input. Connection to a TCXO.                                                                                                                                                                                                  |

| 2    | 1   | OSCOUT  | 0   | Oscillator output.                                                                                                                                                                                                                                           |

| 3    | 2   | VP      | _   | Power supply voltage input for the charge pump.                                                                                                                                                                                                              |

| 4    | 3   | Vcc     | _   | Power supply voltage input.                                                                                                                                                                                                                                  |

| 5    | 4   | Do      | 0   | Charge pump output.<br>Phase of the charge pump can be selected via programming of the FC bit.                                                                                                                                                               |

| 6    | 5   | GND     | _   | Ground.                                                                                                                                                                                                                                                      |

| 7    | 6   | Xfin    | I   | Prescaler complementary input, which should be grounded via a capacitor.                                                                                                                                                                                     |

| 8    | 7   | fin     | I   | Prescaler input.<br>Connection to an external VCO should be done via AC coupling.                                                                                                                                                                            |

| 9    | 8   | Clock   | I   | Clock input for the 19-bit shift register.<br>Data is shifted into the shift register on the rising edge of the clock.<br>(Open is prohibited.)                                                                                                              |

| 10   | 9   | Data    | I   | Serial data input using binary code.<br>The last bit of the data is a control bit. (Open is prohibited.)                                                                                                                                                     |

| 11   | 10  | LE      | I   | Load enable signal input. (Open is prohibited.)<br>When LE is set high, the data in the shift register is transferred to a latch<br>according to the control bit in the serial data.                                                                         |

| 12   | 11  | PS      | I   | Power saving mode control. This pin must be set at "L" at Power-ON.<br>(Open is prohibited.)<br>PS = "H"; Normal mode<br>PS = "L"; Power saving mode                                                                                                         |

| 13   | 12  | ZC      | I   | Forced high-impedance control for the charge pump (with internal pull up resistor.)<br>ZC = "H"; Normal Do output.<br>ZC = "L"; Do becomes high impedance.                                                                                                   |

| 14   | 13  | LD/fout | 0   | Lock detect signal output (LD)/phase comparator monitoring output (fout).<br>The output signal is selected via programming of the LDS bit.<br>LDS = "H"; outputs fout (fr/fp monitoring output)<br>LDS = "L"; outputs LD ("H" at locking, "L" at unlocking.) |

| 15   | 14  | φP      | 0   | Phase comparator N-channel open drain output for an external charge pump. Phase can be selected via programming of the FC bit.                                                                                                                               |

| 16   | 15  | φR      | 0   | Phase comparator CMOS output for an external charge pump. Phase can be selected via programming of the FC bit.                                                                                                                                               |

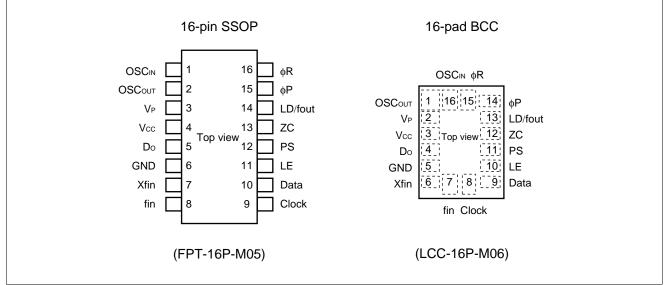

■ BLOCK DIAGRAM

| Parameter            | Symbol | Condition | Ra   | ting     | Unit | Remark  |

|----------------------|--------|-----------|------|----------|------|---------|

| Farameter            | Symbol | Condition | Min  | Max      | Unit | Reindik |

| Dowor oupply voltage | Vcc    | _         | -0.5 | 4.0      | V    |         |

| Power supply voltage | VP     | _         | Vcc  | 6.0      | V    |         |

| Input voltage        | Vi     | _         | -0.5 | Vcc +0.5 | V    |         |

| Output valtage       | Vo     | Except Do | GND  | Vcc      | V    |         |

| Output voltage       | Vo     | Do        | GND  | VP       | V    |         |

| Storage temperature  | Tstg   | _         | -55  | +125     | °C   |         |

### ABSOLUTE MAXIMUM RATINGS

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol |     | Value | Unit | Remark |          |

|-----------------------|--------|-----|-------|------|--------|----------|

| Falameter             | Symbol | Min | Тур   | Max  | Unit   | Relliark |

| Power supply voltage  | Vcc    | 2.4 | 3.0   | 3.6  | V      |          |

| Power supply voltage  | VP     | Vcc | -     | 5.5  | V      |          |

| Input voltage         | Vı     | GND | -     | Vcc  | V      |          |

| Operating temperature | Та     | -40 | -     | +85  | °C     |          |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

# ■ ELECTRICAL CHARACTERISTICS

$(V_{CC} = 2.4 \text{ to } 3.6 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

|                                |                             |                           | _                                            |                              |                         | Value        |               |      |    |     |

|--------------------------------|-----------------------------|---------------------------|----------------------------------------------|------------------------------|-------------------------|--------------|---------------|------|----|-----|

| Parameter                      |                             | Symbol                    | Conc                                         | dition                       | Min                     | Тур          | Max           | Unit |    |     |

| Power supply current*1         |                             | Icc*1                     | fin = 2500 MHz,<br>(Vcc = Vp = 3.0 V         | Vcc = Vp = 2.7 V<br>V)       | _                       | 3.5<br>(4.0) | _             | mA   |    |     |

| Power saving current           |                             | IPS                       | ZC = "H" or oper                             | n                            | _                       | 0.1*2        | 10            | μΑ   |    |     |

| Operating frequency            | fin                         | fın                       | -                                            | _                            | 700                     | _            | 2500          | MHz  |    |     |

|                                | OSCIN                       | OSCIN                     | -                                            |                              | _                       |              | 3             | _    | 40 | MHz |

| Input sensitivity              | fin⁺³                       | Pfin                      | 50 Ω system<br>(Refer to the me<br>circuit.) | (Refer to the measurement    |                         |              | +2            | dBm  |    |     |

|                                | $OSC{\scriptstyle IN^{*3}}$ | Vosc                      | -                                            | _                            | 0.5                     | _            | Vcc           | Vp-p |    |     |

| "H" level input voltage        | Data,                       | Vін                       | -                                            | -                            | $V\text{cc} \times 0.7$ | -            | -             |      |    |     |

| "L" level input voltage        | Clock,<br>LE, PS,<br>ZC     | VIL                       | -                                            | _                            | _                       | -            | Vcc 	imes 0.3 | V    |    |     |

| "H" level input current        | Data,                       | <b>I</b> ін <sup>*4</sup> | -                                            | _                            | -1.0                    | _            | +1.0          |      |    |     |

| "L" level input current        | Clock,<br>LE, PS            | IL <sup>*4</sup>          | -                                            | _                            | -1.0                    | _            | +1.0          | μA   |    |     |

| "H" level input current        | current                     |                           | -                                            | _                            | 0                       | _            | +100          |      |    |     |

| "L" level input current        | OSCIN                       | Iı∟*4                     | -                                            | _                            | -100                    | _            | 0             | μA   |    |     |

| "H" level input current        | 70                          | <b>I</b> ін <sup>*4</sup> | -                                            | _                            | -1.0                    | _            | +1.0          |      |    |     |

| "L" level input current        | ZC                          | Iı∟*4                     | Pull up input                                |                              | -100                    | _            | 0             | μA   |    |     |

| "L" level output voltage       | φP                          | Vol                       | Open drain outp                              | out                          | _                       | _            | 0.4           | V    |    |     |

| "H" level output voltage       | <b>φ</b> R,                 | Vон                       | $V_{CC} = V_P = 3.0 V$                       | ′, Іон = –1 mA               | Vcc - 0.4               | _            | _             | V    |    |     |

| "L" level output voltage       | LD/fout                     | Vol                       | $V_{CC} = V_P = 3.0 V$                       | ′, Io∟ = 1 mA                | _                       | _            | 0.4           | V    |    |     |

| "H" level output voltage       | De                          | V <sub>DOH</sub>          | $V_{CC} = V_P = 3.0 V$                       | ′, Іоон = –0.5 mA            | V <sub>P</sub> − 0.4    | _            | _             | V    |    |     |

| "L" level output voltage       | Do                          | Vdol                      | $V_{CC} = V_P = 3.0 V$                       | ′, I <sub>DOL</sub> = 0.5 mA | _                       | _            | 0.4           | V    |    |     |

| High impedance cutoff current  | Do                          | IOFF                      | Vcc = Vp = 3.0 V<br>Voff = 0.5 V to V        | ,                            | _                       | _            | 2.5           | nA   |    |     |

| "L" level output current       | фР                          | lo∟                       | Open drain outp                              | out                          | 1.0                     | _            | _             | mA   |    |     |

| "H" level output current       | φR,                         | Іон                       | -                                            | _                            | _                       | _            | -1.0          |      |    |     |

| "L" level output current       | LD/fout                     | lol                       | -                                            | _                            | 1.0                     | _            | _             | mA   |    |     |

| (1) 17 Laural autout autout at |                             | 1 *4                      | Vcc = 3 V,                                   | CS bit = "H"                 | _                       | -6.0         | _             |      |    |     |

| "H" level output current       | Da                          | DOH <sup>*4</sup>         | $V_{P} = 3 V$ ,                              | CS bit = "L"                 | _                       | -1.5         | _             |      |    |     |

| "I" lovel output ourset        | Do                          | L_                        | $V_{DO} = V_P/2$                             | CS bit = "H"                 | _                       | 6.0          | _             | mA   |    |     |

| "L" level output current       |                             | DOL                       | Ta = +25°C CS bit = "L"                      |                              | _                       | 1.5          | _             |      |    |     |

|                                | Idol/Idoh                   | DOMT <sup>*5</sup>        | $V_{DO} = V_P/2$                             |                              | _                       | 3            | _             | %    |    |     |

| Charge pump current rate       | vs Vdo                      |                           | $0.5 \text{ V} \leq V_{DO} \leq V_{P}$       | v – 0.5 V                    | _                       | 10           | _             | %    |    |     |

|                                | vs Ta                       | DOTA <sup>*7</sup>        | – 40°C ≤ Ta ≤ +                              | 85°C                         | _                       | 10           | _             | %    |    |     |

\*1 : Conditions; fosc = 12 MHz, Ta =  $+25^{\circ}$ C, in locking state.

\*2 : V<sub>CC</sub> = V<sub>P</sub> = 3.0 V, fosc = 12.8 MHz, Ta = +25°C, in power saving mode

\*3 : AC coupling. 1000 pF capacitor is connected under the condition of Min operating frequency.

\*4 : The symbol "--" (minus) means direction of current flow.

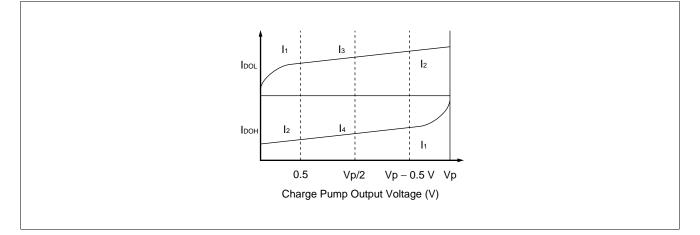

\*5 : Vcc = VP = 3.0 V, Ta = +25°C ( $|I_3| - |I_4|$ ) / [( $|I_3| + |I_4|$ ) /2] × 100(%)

\*6 :  $V_{CC} = V_P = 3.0 \text{ V}$ , Ta = +25°C [(|I<sub>2</sub>| - |I<sub>1</sub>) /2] / [(|I<sub>1</sub>| + |I<sub>2</sub>) /2] × 100(%) (Applied to each Idol, Idoh)

\*7 :  $V_{CC} = V_P = 3.0 \text{ V}, V_{DO} = V_P/2 (|I_{DO(85^\circ C)} - I_{DO(-40^\circ C)}|/2) / (|I_{DO(85^\circ C)} + I_{DO(-40^\circ C)}|/2) \times 100(\%) (Applied to each I_{DOL}, I_{DOH})$

# FUNCTIONAL DESCRIPTION

#### 1. Pulse Swallow Function

The divide ratio can be calculated using the following equation:

$f_{VCO} = [(M \times N) + A] \times f_{OSC} \div R \quad (A < N)$

- fvco: Output frequency of external voltage controlled oscillator (VCO)

- N : Preset divide ratio of binary 11-bit programmable counter (3 to 2,047)

- A : Preset divide ratio of binary 7-bit swallow counter ( $0 \le A \le 127$ )

- fosc : Output frequency of the reference frequency oscillator

- R : Preset divide ratio of binary 14-bit programmable reference counter (3 to 16,383)

- M : Preset divide ratio of modulus prescaler (32 or 64)

#### 2. Serial Data Input

Serial data is processed using the Data, Clock, and LE pins. Serial data controls the programmable reference divider and the programmable divider separately.

Binary serial data is entered through the Data pin.

One bit of data is shifted into the shift register on the rising edge of the Clock. When the LE signal pin is taken high, stored data is latched according to the control bit data as follows:

#### Table 1. Control Bit

| Control bit (CNT) | Destination of serial data             |

|-------------------|----------------------------------------|

| н                 | For the programmable reference divider |

| L                 | For the programmable divider           |

#### (1) Shift Register Configuration

| F                    | Progr           | amma                           | able R                              | efere                                       | nce C                                | Count                                 | er             |              |         |         |         |         |         |         |        |    |                                      |                                  |

|----------------------|-----------------|--------------------------------|-------------------------------------|---------------------------------------------|--------------------------------------|---------------------------------------|----------------|--------------|---------|---------|---------|---------|---------|---------|--------|----|--------------------------------------|----------------------------------|

| LSB<br>↓             |                 |                                |                                     |                                             |                                      |                                       |                | Data         | a Flov  | v —     |         |         | •       |         |        |    | I                                    | MSB<br>↓                         |

| 1                    | 2               | 3                              | 4                                   | 5                                           | 6                                    | 7                                     | 8              | 9            | 10      | 11      | 12      | 13      | 14      | 15      | 16     | 17 | 18                                   | 19                               |

| C<br>N<br>T          | R<br>1          | R<br>2                         | R<br>3                              | R<br>4                                      | R<br>5                               | R<br>6                                | R<br>7         | R<br>8       | R<br>9  | R<br>10 | R<br>11 | R<br>12 | R<br>13 | R<br>14 | sw     | FC | LDS                                  | CS                               |

| SW<br>FC<br>LD<br>CS | to R1<br>V<br>S | 4 : Di<br>: Di<br>: Pi<br>: L[ | vide r<br>nase α<br>D/foυτ<br>harge | atio s<br>atio s<br>contro<br>signa<br>pump | etting<br>I bit fo<br>seleo<br>curre | bit for<br>or the<br>ot bit<br>ont se | the p<br>phase | resca<br>com | ler (32 | 2/33 c  |         |         | nter (3 | 3 to 16 | 5,383) |    | [Tab<br>[Tab<br>[Tab<br>[Tab<br>[Tab | le 2]<br>le 5]<br>le 8]<br>le 7] |

٦

| SB<br>↓                                                                                                                                                                                          |        |        |        |        |        |        |        | Dat    | a Flov | v —    | •      |        |        |        |        |        |         | MS<br>▼ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|---------|

| 1                                                                                                                                                                                                | 2      | 3      | 4      | 5      | 6      | 7      | 8      | 9      | 10     | 11     | 12     | 13     | 14     | 15     | 16     | 17     | 18      | 19      |

| C<br>N<br>T                                                                                                                                                                                      | A<br>1 | A<br>2 | A<br>3 | A<br>4 | A<br>5 | A<br>6 | A<br>7 | N<br>1 | N<br>2 | N<br>3 | N<br>4 | N<br>5 | N<br>6 | N<br>7 | N<br>8 | N<br>9 | N<br>10 | N<br>11 |

| CNT: Control bit[Table 1]N1 to N11 : Divide ratio setting bits for the programmable counter (3 to 2,047)[Table 3]A1 to A7: Divide ratio setting bits for the swallow counter (0 to 127)[Table 4] |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |         |         |

#### Table 2. Binary 14-bit Programmable Reference Counter Data Setting

|                  |     | <u> </u> |     |     |     |    |    |    |    |    |    |    |    |    |

|------------------|-----|----------|-----|-----|-----|----|----|----|----|----|----|----|----|----|

| Divide ratio (R) | R14 | R13      | R12 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 |

| 3                | 0   | 0        | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4                | 0   | 0        | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| •                | •   | •        | •   | •   | •   | •  | •  | •  | •  | •  | •  | •  | •  | •  |

| 16383            | 1   | 1        | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Note : Divide ratio less than 3 is prohibited.

Г

#### Table 3. Binary 11-bit Programmable Counter Data Setting

| Divide ratio (N) | N11 | N10 | N9 | N8 | N7 | N6 | N5 | N4 | N3 | N2 | N1 |

|------------------|-----|-----|----|----|----|----|----|----|----|----|----|

| 3                | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4                | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

|                  | •   | •   | •  | •  | •  | •  | •  | •  | •  | •  | •  |

| 2047             | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Note : Divide ratio less than 3 is prohibited.

#### Table 4. Binary 7-bit Swallow Counter Data Setting

| Divide ratio (A) | A7 | A6 | A5 | A4 | A3 | A2 | A1 |

|------------------|----|----|----|----|----|----|----|

| 0                | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1                | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

|                  | •  | •  | •  | •  | •  | •  | •  |

| 127              | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### Table 5. Prescaler Data Setting

| SW | Prescaler divide ratio |

|----|------------------------|

| Н  | 32/33                  |

| L  | 64/65                  |

#### Table 6. Charge Pump Current Setting

| CS | Current value |

|----|---------------|

| Н  | ±6.0 mA       |

| L  | ±1.5 mA       |

#### Table 7. LD/fout Output Select Data Setting

| LDS | LD/four output signal |  |  |

|-----|-----------------------|--|--|

| Н   | fout signal           |  |  |

| L   | LD signal             |  |  |

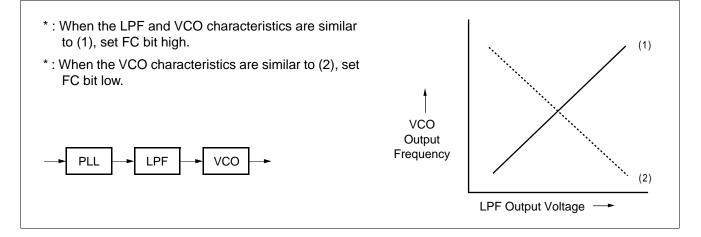

#### (2) Relation between the FC Input and Phase Characteristics

The FC bit changes the phase characteristics of the phase comparator. Both the internal charge pump output level (D<sub>o</sub>) and the phase comparator output ( $\phi$ R,  $\phi$ P) are reversed according to the FC bit. Also, the monitor pin (fout) output is controlled by the FC bit. The relationship between the FC bit and each of Do,  $\phi$ R, and  $\phi$ P is shown below.

#### Table 8. FC Bit Data Setting (LDS = "H")

|         | FC = High |    |    | FC = Low  |    |    |    |           |

|---------|-----------|----|----|-----------|----|----|----|-----------|

|         | Do        | φR | φP | LD/fout   | Do | φR | φP | LD/fout   |

| fr > f⊳ | Н         | L  | L  |           | L  | Н  | Z* |           |

| fr < f⊳ | L         | Н  | Z* | fout = fr | Н  | L  | L  | fout = fp |

| fr = f⊳ | Z*        | L  | Z* |           | Z* | L  | Z* | -         |

\* : High-Z

When designing a synthesizer, the FC pin setting depends on the VCO and LPF characteristics.

### 3. Do Output Control

#### Table 9. ZC Pin Setting

| ZC pin | Do output      |  |  |

|--------|----------------|--|--|

| Н      | Normal output  |  |  |

| L      | High impedance |  |  |

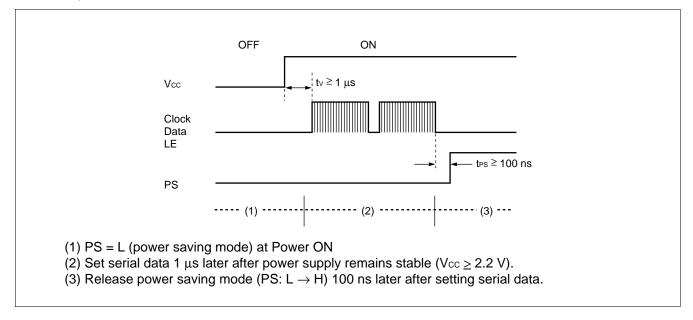

#### 4. Power Saving Mode (Intermittent Mode Control Circuit)

#### Table 10. PS Pin Setting

| PS pin | Status            |  |  |

|--------|-------------------|--|--|

| Н      | Normal mode       |  |  |

| L      | Power saving mode |  |  |

The intermittent mode control circuit reduces the PLL power consumption.

By setting the PS pin low, the device enters into the power saving mode, reducing the current consumption. See the Electrical Characteristics chart for the specific value.

The phase detector output, Do, becomes high impedance.

For the signal PLL, the lock detector, LD, remains high, indicating a locked condition.

Setting the PS pin high, releases the power saving mode, and the device works normally.

The intermittent mode control circuit also ensures a smooth startup when the device returns to normal operation. When the PLL is returned to normal operation, the phase comparator output signal is unpredictable. This is because

of the unknown relationship between the comparison frequency (fp) and the reference frequency (fr) which can cause a major change in the comparator output, resulting in a VCO frequency jump and an increase in lockup time.

To prevent a major VCO frequency jump, the intermittent mode control circuit limits the magnitude of the error signal from the phase detector when it returns to normal operation.

When power (Vcc) is first applied, the device must be in standby mode, PS = Low, for at least 1  $\mu$ s.

Note : PS pin must be set "L" for Power-ON.

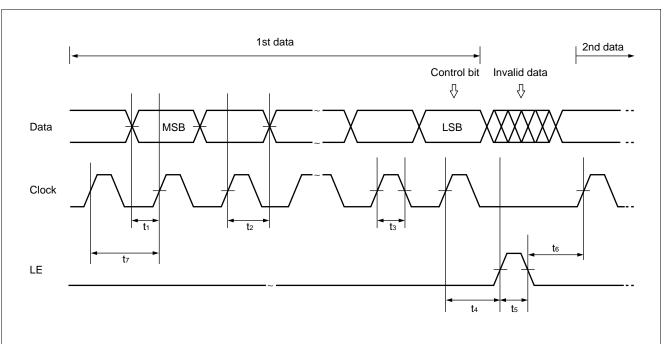

# ■ SERIAL DATA INPUT TIMING

On the rising edge of the clock, one bit of data is transferred into the shift register.

| Parameter | Min | Тур | Max | Unit |

|-----------|-----|-----|-----|------|

| t1        | 20  | -   | -   | ns   |

| t2        | 20  | -   | -   | ns   |

| t3        | 30  | _   | -   | ns   |

| t4        | 30  | _   | _   | ns   |

| Parameter      | Min | Тур | Max | Unit |

|----------------|-----|-----|-----|------|

| t5             | 100 | -   | -   | ns   |

| t <sub>6</sub> | 20  | Ι   | -   | ns   |

| t7             | 100 | I   | -   | ns   |

Note : LE should be "L" when the data is transferred into the shift register.

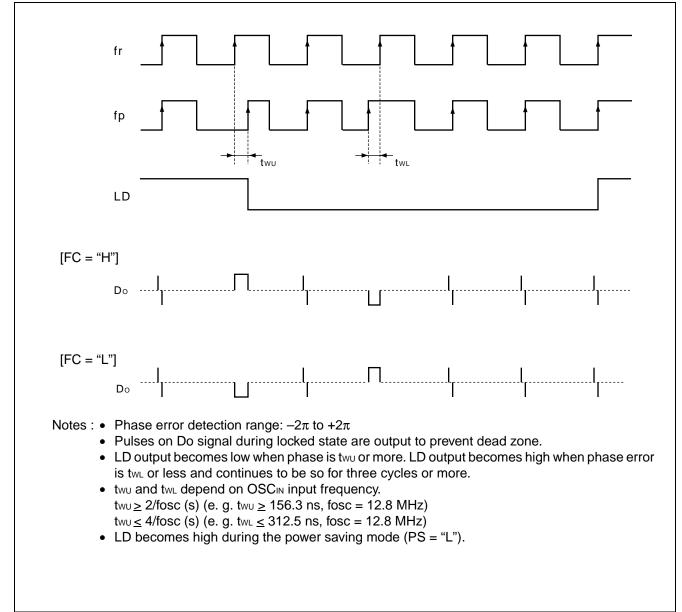

### ■ PHASE COMPARATOR OUTPUT WAVEFORM

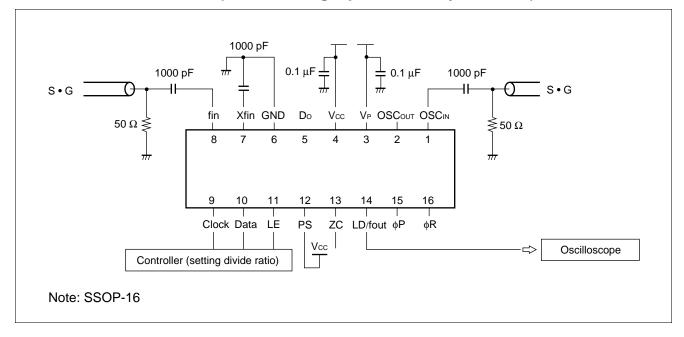

# ■ MEASURMENT CIRCUIT (for Measuring Input Sensitivity fin/OSC<sub>IN</sub>)

# ■ TYPICAL CHARACTERISTICS

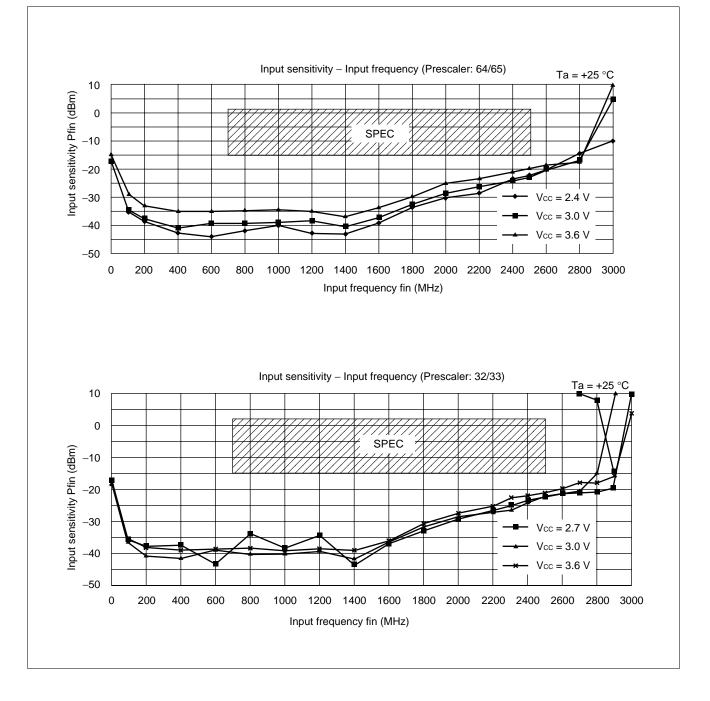

#### 1. fin input sensitivity

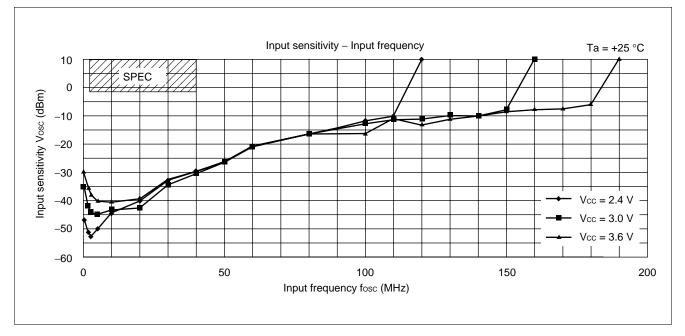

# 2. OSCIN input sensitivity

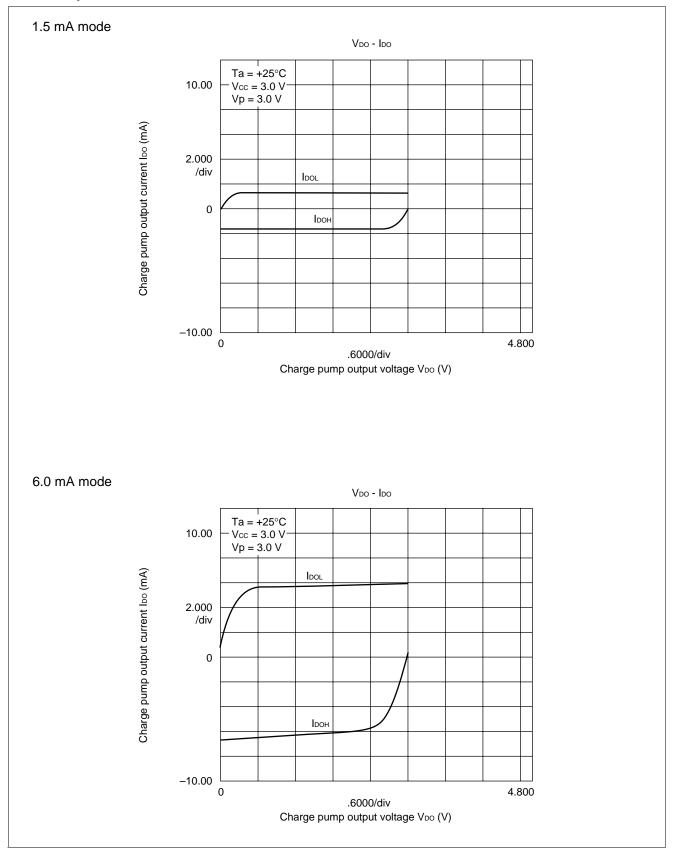

### 3. Do output current

18

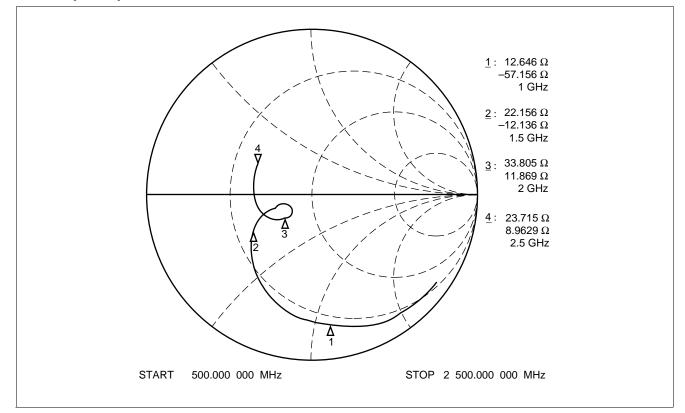

### 4. fin input impedance

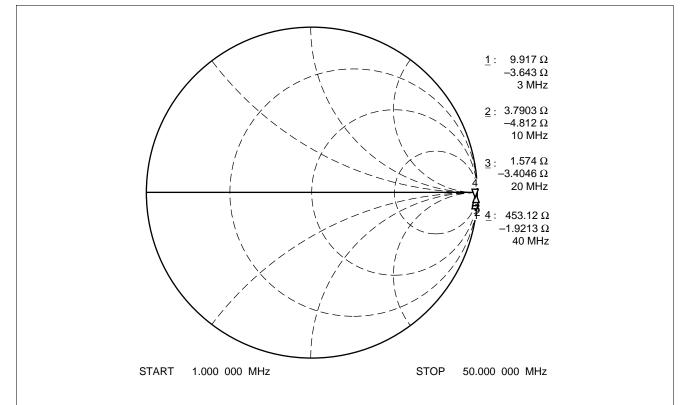

# 5. OSCIN input impedance

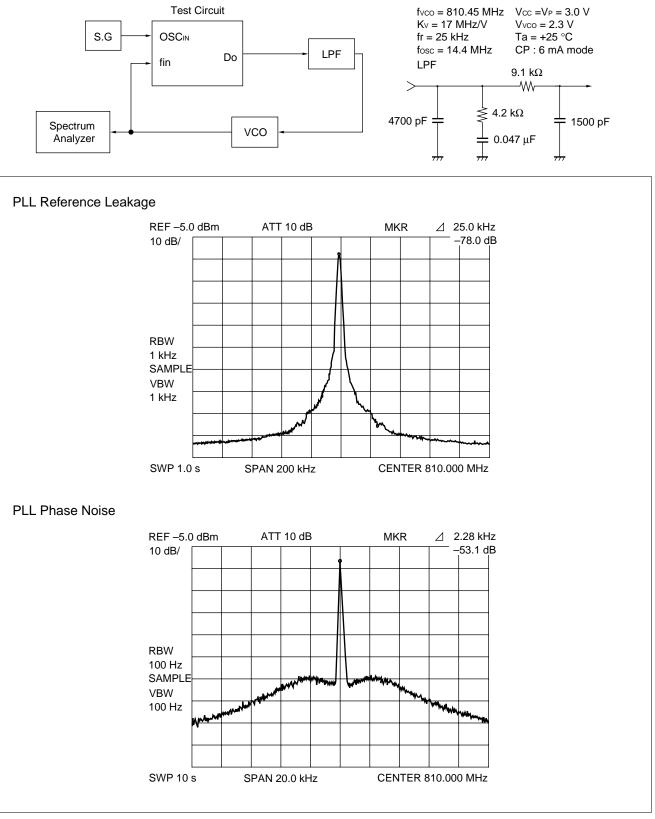

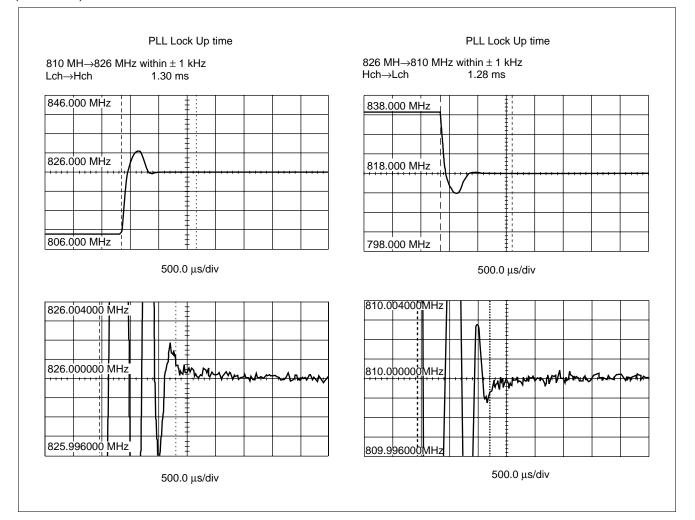

# ■ REFERENCE INFORMATION

#### (Continued)

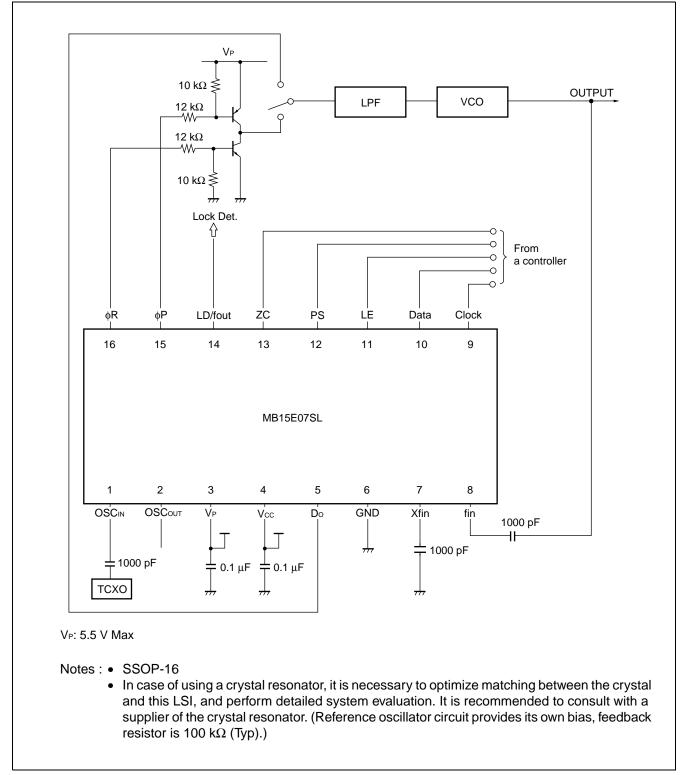

### ■ APPLICATION EXAMPLE

# ■ USAGE PRECAUTIONS

To protect against damage by electrostatic discharge, note the following handling precautions:

-Store and transport devices in conductive containers.

-Use properly grounded workstations, tools, and equipment.

-Turn off power before inserting device into or removing device from a socket.

-Protect leads with a conductive sheet when transporting a board-mounted device.

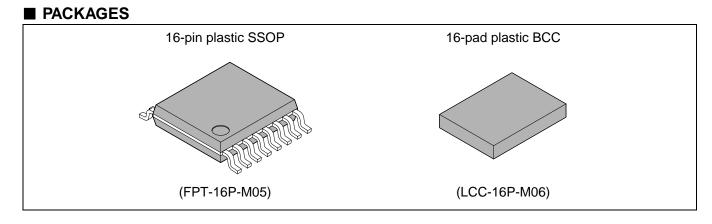

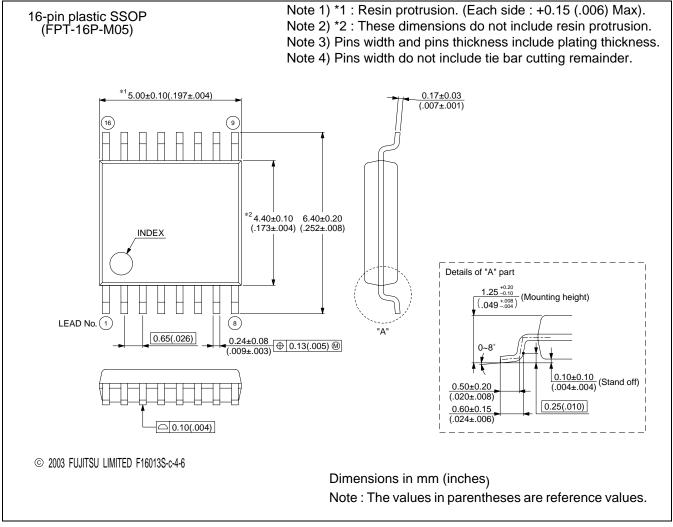

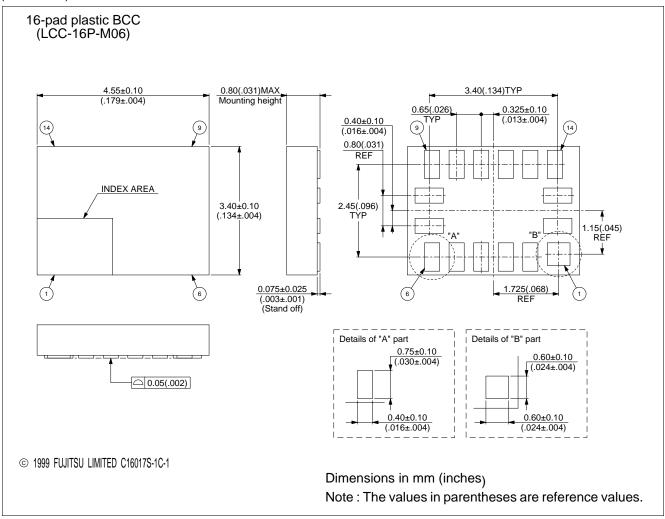

# ORDERING INFORMATION

| Part number   | Package                               | Remarks |

|---------------|---------------------------------------|---------|

| MB15E07SLPFV1 | 16-pin, Plastic SSOP<br>(FPT-16P-M05) |         |

| MB15E07SLPV1  | 16-pad, Plastic BCC<br>(LCC-16P-M06)  |         |

(Continued)

(Continued)

# FUJITSU LIMITED

#### All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

#### F0306 © FUJITSU LIMITED Printed in Japan