## FAIRCHILD

SEMICONDUCTOR

# GTLP6C816 GTLP/TTL 1:6 Clock Driver

## **General Description**

The GTLP6C816 is a clock driver that provides TTL to GTLP signal level translation (and vice versa). The device provides a high speed interface between cards operating at TTL logic levels and a backplane operating at GTLP logic levels. High speed backplane operation is a direct result of GTLP's reduced output swing (<1V), reduced input threshold levels and output edge rate control. The edge rate control minimizes bus settling time. GTLP is a Fairchild Semiconductor derivative of the Gunning Transceiver logic (GTL) JEDEC standard JESD8-3.

Fairchild's GTLP has internal edge-rate control and is process, voltage, and temperature (PVT) compensated. Its function is similar to BTL and GTL but with different output levels and receiver threshold. GTLP output LOW level is typically less than 0.5V, the output level HIGH is 1.5V and the receiver threshold is 1.0V.

#### Features

- Interface between LVTTL and GTLP logic levels

- Designed with edge rate control circuitry to reduce output noise on the GTLP port

June 1998

**Revised December 2000**

- V<sub>REF</sub> pin provides external supply reference voltage for receiver threshold adjustibility

- Special PVT compensation circuitry to provide consistent performance over variations of precess, supply voltage and temperature

- TTL compatible driver and control inputs

- Designed using Fairchild advanced CMOS technologyBushold data inputs on A port to eliminate the need for

- external pull-up resistors for unused inputs

Power up/down and power off high impedance for live insertion

- 5V over voltage tolerance on LVTTL ports

- Open drain on GTLP to support wired-or connection

- A Port source/sink -24mA/+24mA

- B Port sink +50mA

- 1:6 fanout clock driver for TTL port

- 1:2 fanout clock driver for GTLP port

#### **Ordering Code:**

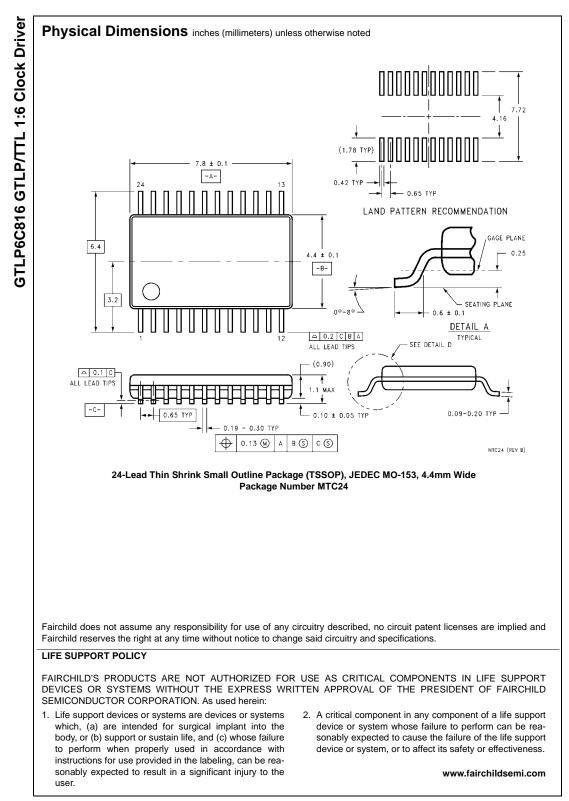

|  | Order Number      Package Number        GTLP6C816MTC      MTC24 | Package Description                                                         |                                                       |

|--|-----------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------|

|  |                                                                 | 24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |                                                       |

|  | Device also available in                                        | Tape and Reel. Specify by                                                   | appending the suffix letter "X" to the ordering code. |

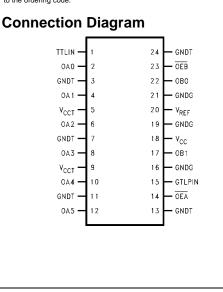

#### **Pin Descriptions**

| Pin Names              | Description                                          |  |  |  |

|------------------------|------------------------------------------------------|--|--|--|

| TTLIN, GTLPIN          | Clock Inputs (TTL and GTLP respectively)             |  |  |  |

| OEB                    | Output Enable (Active LOW)<br>GTLP Port (TTL Levels) |  |  |  |

| OEA                    | Output Enable (Active LOW)<br>TTL Port (TTL Levels)  |  |  |  |

| V <sub>CCT</sub> .GNDT | TTL Output Supplies (5V)                             |  |  |  |

| V <sub>CC</sub>        | Internal Circuitry V <sub>CC</sub> (5V)              |  |  |  |

| GNDG                   | OBn GTLP Output Grounds                              |  |  |  |

| V <sub>REF</sub>       | Voltage Reference Input                              |  |  |  |

| OA0–OA5                | TTL Buffered Clock Outputs                           |  |  |  |

| OB0-OB1                | GTLP Buffered Clock Outputs                          |  |  |  |

© 2000 Fairchild Semiconductor Corporation DS500129

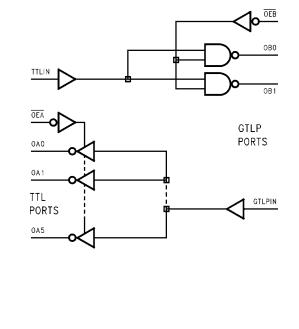

#### **Functional Description**

The GTLP6C816 is a clock driver providing TTL-to-GTLP clock translation, and GTLP-to-TTL clock translation in the same package. The TTL-to-GTLP direction is a 1:2 clock driver path with a single Enable pin (OEB). For the GTLP-to-TTL direction the clock receiver path is a 1:6 buffer with a single Enable control (OEA). Data polarity is inverting for both directions.

#### Truth Tables

| Inpu           | ts        | Outputs        |  |  |  |  |  |

|----------------|-----------|----------------|--|--|--|--|--|

| TTLIN          | OEB       | OBn            |  |  |  |  |  |

| Н              | L         | L              |  |  |  |  |  |

| L              | L         | н              |  |  |  |  |  |

| Х              | н         | High Z         |  |  |  |  |  |

|                |           |                |  |  |  |  |  |

| Inpu           | ts        | Outputs        |  |  |  |  |  |

| Inpu<br>GTLPIN | ts<br>OEA | Outputs<br>OAn |  |  |  |  |  |

| · · ·          |           |                |  |  |  |  |  |

| GTLPIN         |           | OAn            |  |  |  |  |  |

### Logic Diagram

www.fairchildsemi.com

## Absolute Maximum Ratings(Note 1)

|                                            | J ( )                             |            |

|--------------------------------------------|-----------------------------------|------------|

| Supply Voltage (V <sub>CC</sub> )          | -0.5V to +7.0V                    | С          |

| DC Input Voltage (VI)                      | -0.5V to +7.0V                    | S          |

| DC Output Voltage (V <sub>O</sub> )        |                                   | E          |

| Outputs 3-STATE                            | -0.5V to +7.0V                    |            |

| Outputs Active (Note 2)                    | -0.5V to +7.0V                    |            |

| DC Output Sink Current into                |                                   | h          |

| OA Port I <sub>OL</sub>                    | 48 mA                             |            |

| DC Output Source Current                   |                                   | F          |

| from OA Port I <sub>OH</sub>               | -48 mA                            |            |

| DC Output Sink Current into                |                                   | L          |

| OB Port in the LOW State I <sub>OL</sub>   | 80 mA                             |            |

| DC Input Diode Current (IIK)               |                                   |            |

| V <sub>1</sub> < 0V                        | –50 mA                            | C          |

| DC Output Diode Current (I <sub>OK</sub> ) |                                   | Not        |

| V <sub>O</sub> < 0V                        | –50 mA                            | whi<br>con |

| $V_{O} > V_{CC}$                           | +50 mA                            | Fun<br>imp |

| ESD Rating                                 | > 2000V                           | Not        |

| Storage Temperature (T <sub>STG</sub> )    | $-65^{\circ}C$ to $+150^{\circ}C$ | Not        |

|                                            |                                   |            |

# Recommended Operating

| Conditions (Note 3)                                                                                                                              |                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Supply Voltage V <sub>CC</sub>                                                                                                                   | 4.75V to 5.25V                   |

| Bus Termination Voltage (V <sub>TT</sub> )                                                                                                       |                                  |

| GTLP                                                                                                                                             | 1.47V to 1.53V                   |

| V <sub>REF</sub>                                                                                                                                 | 0.98V to 1.02V                   |

| Input Voltage (V <sub>I</sub> ) on INA Port                                                                                                      |                                  |

| and Control Pins                                                                                                                                 | 0.0V to 5.5V                     |

| HIGH Level Output Current (I <sub>OH</sub> )                                                                                                     |                                  |

| OA Port                                                                                                                                          | –24 mA                           |

| LOW Level Output Current (I <sub>OL</sub> )                                                                                                      |                                  |

| OA Port                                                                                                                                          | +24 mA                           |

| OB Port                                                                                                                                          | +34 mA                           |

| Operating Temperature (T <sub>A</sub> )                                                                                                          | $-40^{\circ}C$ to $+85^{\circ}C$ |

| Note 1: Absolute Maximum continuous ratings a<br>which damage to the device may occur. Exposu<br>conditions beyond those indicated may adversely | e to these conditions or         |

GTLP6C816

which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum rated conditions is not implied.

Note 2:  $I_o$  Absolute Maximum Rating must be observed.

Note 3: Unused input must be held HIGH or LOW.

### **DC Electrical Characteristics**

Over Recommended Operating Free-Air Temperature Range,  $V_{REF} = 1.0V$  (unless otherwise noted).

|                        | Symbol       | Test C                | onditions                                      | Min                    | Typ<br>(Note 4) | Max                    | Units |

|------------------------|--------------|-----------------------|------------------------------------------------|------------------------|-----------------|------------------------|-------|

| V <sub>IH</sub> GTLPIN |              |                       |                                                | V <sub>REF</sub> +0.05 |                 | ν <sub>π</sub>         |       |

|                        | Others       |                       |                                                | 2.0                    |                 |                        | V     |

| VIL                    | GTLPIN       |                       |                                                | 0.0                    |                 | V <sub>REF</sub> -0.05 |       |

|                        | Others       |                       |                                                |                        |                 | 0.8                    | V     |

| V <sub>REF</sub>       | GTLP         |                       |                                                |                        | 1.0             |                        |       |

| (Note 5)               | GTL          |                       |                                                |                        | 0.8             |                        | V     |

| V <sub>TT</sub>        | GTLP         |                       |                                                |                        | 1.5             |                        | V     |

| (Note 5)               | GTL          |                       |                                                |                        | 1.2             |                        | v     |

| V <sub>IK</sub>        |              | $V_{CC} = 4.75V$      | I <sub>I</sub> = -18 mA                        |                        |                 | -1.2                   | V     |

| V <sub>OH</sub>        | OAn Port     | $V_{CC} = 4.75V$      | I <sub>OH</sub> = -100 μA                      | V <sub>CC</sub> -0.2   |                 |                        |       |

|                        |              |                       | I <sub>OH</sub> = -18 mA                       | 2.4                    |                 |                        | V     |

|                        |              |                       | $I_{OH} = -24 \text{ mA}$                      | 2.2                    |                 |                        |       |

| V <sub>OL</sub>        | OAn Port     | $V_{CC} = 4.75V$      | I <sub>OL</sub> = 100 μA                       |                        |                 | 0.2                    |       |

|                        |              |                       | I <sub>OL</sub> = 18 mA                        |                        |                 | 0.4                    | V     |

|                        |              |                       | I <sub>OL</sub> = 24 mA                        |                        |                 | 0.5                    |       |

| V <sub>OL</sub>        | OBn Port     | $V_{CC} = 4.75V$      | I <sub>OL</sub> = 100 μA                       |                        |                 | 0.2                    | V     |

|                        |              |                       | $I_{OL} = 34 \text{ mA}$                       |                        |                 | 0.65                   | v     |

| l <sub>l</sub>         | TTLIN/       | $V_{CC} = 5.25V$      | $V_{I} = 5.25V$                                |                        |                 | 5                      | μA    |

|                        | Control Pins |                       | $V_I = 0V$                                     |                        |                 | -5                     | μΑ    |

|                        | GTLPIN       | $V_{CC} = 5.25V$      | $V_I = V_{TT}$                                 |                        |                 | 5                      |       |

|                        |              |                       | $V_I = 0$                                      |                        |                 | -5                     | μA    |

| I <sub>OFF</sub>       | TTLIN        | $V_{CC} = 0$          | $V_1 \text{ or } V_0 = 0 \text{V to}$<br>5.25V |                        |                 | 100                    | μΑ    |

| I <sub>OZH</sub>       | OAn Port     | $V_{CC} = 5.25V$      | V <sub>O</sub> = 5.25V                         |                        |                 | 5                      | μA    |

|                        | OBn Port     |                       | V <sub>O</sub> = 1.5V                          |                        |                 | 5                      | μΛ    |

| I <sub>OZL</sub>       | OAn Port     | $V_{CC} = 5.25V$      | V <sub>O</sub> = 0                             |                        |                 | -5                     | μA    |

| I <sub>CC</sub>        | OAn or       | $V_{CC} = 5.25V$      | Outputs HIGH                                   |                        | 7               | 18                     |       |

|                        | OBn Ports    |                       | Outputs LOW                                    |                        | 7               | 20                     | mA    |

|                        |              | $V_I = V_{CC}$ or GND | Outputs Disabled                               |                        | 7               | 20                     |       |

| Δl <sub>CC</sub>       | TTLIN        | $V_{CC} = 5.25V$      | $V_{I} = V_{CC} - 2.1$                         |                        |                 | 6                      | mA    |

www.fairchildsemi.com

GTLP6C816

## DC Electrical Characteristics (Continued)

| Symbol           |                               | Test Conditions              | Min | Typ<br>(Note 4) | Мах | Units |

|------------------|-------------------------------|------------------------------|-----|-----------------|-----|-------|

| CIN              | Control Pins/GTLPIN/<br>TTLIN | $V_I = V_{CC} \text{ or } 0$ |     | 3.7             |     | pF    |

| C <sub>OUT</sub> | OAn Port                      | $V_I = V_{CC} \text{ or } 0$ |     | 7               |     | pF    |

|                  | OBn Port                      | $V_I = V_{CC} \text{ or } 0$ |     | 7               |     | pi    |

Note 4: All typical values are at  $V_{CC}$  = 5.0V and  $T_A$  = 25°C.

Note 5: GTLP V<sub>REF</sub> and V<sub>TT</sub> are specified to 2% tolerance since signal integrity and noise margin can be significantly degraded if these supplies are noisy. In addition, V<sub>TT</sub> and R<sub>TERM</sub> can be adjusted to accommodate backplane impedances other than 50 $\Omega$ , within the boundaries of not exceeding the DC Absolute I<sub>DL</sub> ratings. Similarly V<sub>REF</sub> can be adjusted to compensate for changes in V<sub>TT</sub>.

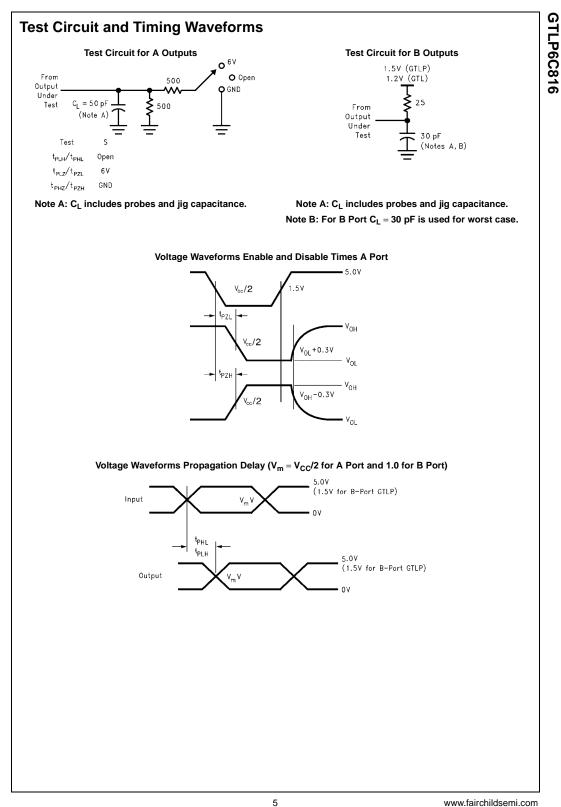

#### **AC Electrical Characteristics**

Over recommended range of supply voltage and operating free air temperature.  $V_{REF}$  = 1.0V (unless otherwise noted).  $C_L$  = 30 pF for OBn Port and  $C_L$  = 50 pF for OAn Port.

| 0 mm h m h                                        | From                                         | То                   | Min | Тур      | Max  | 11-11- |

|---------------------------------------------------|----------------------------------------------|----------------------|-----|----------|------|--------|

| Symbol                                            | (Input)                                      | (Output)             |     | (Note 6) |      | Units  |

| t <sub>PLH</sub>                                  | TTLIN                                        | OBn                  | 1.5 | 3.8      | 6.0  |        |

| t <sub>PHL</sub>                                  |                                              |                      | 1.5 | 2.8      | 5.0  | ns     |

| t <sub>PLH</sub>                                  | OEB                                          | OBn                  | 1.5 | 6.4      | 10.5 |        |

| t <sub>PHL</sub>                                  |                                              |                      | 1.5 | 3.2      | 6.0  | ns     |

| t <sub>RISE</sub>                                 | Transition Time, OB                          | Outputs (20% to 80%) |     | 2.3      |      | ns     |

| t <sub>FALL</sub>                                 | ALL Transition Time, OB outputs (20% to 80%) |                      |     | 2.3      |      | ns     |

| t <sub>RISE</sub>                                 | Transition Time, OA                          | outputs (10% to 90%) |     | 2.0      |      | ns     |

| t <sub>FALL</sub>                                 | Transition Time, OA outputs (10% to 90%)     |                      |     | 2.0      |      | ns     |

| t <sub>PZH</sub> , t <sub>PZL</sub>               | OEA                                          | OAn                  | 0.5 | 3.6      | 6.5  |        |

| t <sub>PLZ</sub> , t <sub>PHZ</sub>               |                                              |                      | 0.5 | 3.8      | 6.5  | ns     |

| t <sub>PLH</sub>                                  | GTLPIN                                       | OAn                  | 1.5 | 4.4      | 6.5  |        |

| t <sub>PHL</sub>                                  |                                              |                      | 1.5 | 4.0      | 6.0  | ns     |

| t <sub>OSHL</sub> , t <sub>OSLH</sub><br>(Note 7) | Common B                                     | Edge Skew            |     | 0.2      | 1.0  | ns     |

Note 6: All typical values are at  $V_{CC}$  = 5.0V and  $T_A$  = 25°C.

Note 7: Skew specs are given for specific worst case V<sub>CC</sub> Temp. Skew values between the OBn outputs could vary on the backplane due to loading and impedance seen by the device.

www.fairchildsemi.com