## Low Voltage 1:4 CMOS Clock Buffer

**MPC94551**

The MPC94551 is a CMOS 1:4 fanout buffer. The MPC94551 is ideal for applications requiring lower voltage.

#### **Features**

- 1:4 CMOS fanout buffer

- 300 ps output to output skew

- I/O frequency up to 160 MHz operation

- Non-inverting output clock

- 3.3 V supply voltage

- · Output Enable mode tri-states outputs

- -40°C to 85°C industrial temperature range

- Standard 8-lead SOIC package

D SUFFIX 8-LEAD SOIC PACKAGE CASE 751-06

EF SUFFIX 8-LEAD SOIC PACKAGE Pb-FREE PACKAGE CASE 751-06

| ORDERING INFORMATION |                |  |  |  |

|----------------------|----------------|--|--|--|

| Device Package       |                |  |  |  |

| MPC94551D            | SO-8           |  |  |  |

| MPC94551DR2          | SO-8           |  |  |  |

| MPC94551EF           | SO-8 (Pb-FREE) |  |  |  |

| MPC94551EFR2         | SO-8 (Pb-FREE) |  |  |  |

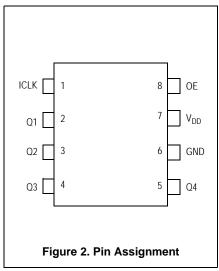

**Table 1. Pin Description**

| Pin Number | Pin Name        | Pin Type | Pin Description                                                       |

|------------|-----------------|----------|-----------------------------------------------------------------------|

| 1          | ICLK            | Input    | Clock input, internal pull-up resistor                                |

| 2          | Q1              | Output   | Clock output <sup>(1)</sup>                                           |

| 3          | Q2              | Output   | Clock output <sup>(1)</sup>                                           |

| 4          | Q3              | Output   | Clock output <sup>(1)</sup>                                           |

| 5          | Q4              | Output   | Clock output <sup>(1)</sup>                                           |

| 6          | GND             | Power    | Connect to ground <sup>(2)</sup>                                      |

| 7          | V <sub>DD</sub> | Power    | Connect to 3.3 V <sup>(2)</sup>                                       |

| 8          | OE              | Input    | Output enable, tri-states outputs when low, internal pull-up resistor |

<sup>1.</sup> A 33  $\Omega$  series terminating resistor may be used on each clock output if the trace is longer than 1 inch.

Table 2. Absolute Maximum Ratings<sup>(1)</sup>

| Parameter                             | Rating                       | Unit |

|---------------------------------------|------------------------------|------|

| Power Supply Voltage, V <sub>DD</sub> | 3.9                          | V    |

| All Inputs and Outputs                | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Ambient Operating Temperature         | -40 to +85                   | °C   |

| Storage Temperature                   | -65 to +150                  | °C   |

| Junction Temperature                  | 175                          | °C   |

| Soldering Temperature                 | 260                          | °C   |

<sup>1.</sup> Stresses above the ratings listed below can cause permanent damage to the device. These ratings are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

Table 3. DC Characteristics ( $V_{DD} = 3.3 \text{ V} \pm 5\%$ ; Ambient Temperature =  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ )

| Parameter                                | Symbol          | Conditions               | Min                      | Тур | Max                      | Unit |

|------------------------------------------|-----------------|--------------------------|--------------------------|-----|--------------------------|------|

| Operating Voltage                        | V <sub>DD</sub> |                          | 3.15                     |     | 3.45                     | V    |

| Input High Voltage <sup>(1)</sup> , ICLK | V <sub>IH</sub> |                          | V <sub>DD</sub> /2 + 0.7 |     | 3.8                      | V    |

| Input Low Voltage <sup>(1)</sup> , ICLK  | $V_{IL}$        |                          |                          |     | V <sub>DD</sub> /2 – 0.7 | V    |

| Input High Voltage, OE                   | V <sub>IH</sub> |                          | 2                        |     | $V_{DD}$                 | V    |

| Input Low Voltage, OE                    | $V_{IL}$        |                          |                          |     | 0.8                      | V    |

| Ouput Low Voltage                        | V <sub>OL</sub> | I <sub>OL</sub> = 12 mA  |                          |     | 0.4                      | V    |

| Output High Voltage                      | V <sub>OH</sub> | I <sub>OH</sub> = -12 mA | 2.4                      |     |                          | V    |

| Operating Supply Current                 | I <sub>DD</sub> | No load, 135 MHz         |                          | 30  |                          | mA   |

| Nominal Output Impedance                 | Z <sub>O</sub>  |                          |                          | 27  |                          | Ω    |

| Internal Pull-up Resistor                | R <sub>PU</sub> | ICLK                     |                          | 31  |                          | kΩ   |

| Input Capacitance                        | C <sub>IN</sub> | OE pin                   |                          | 5   |                          | pF   |

|                                          | C <sub>IN</sub> | ICLK                     |                          | 1   |                          | pF   |

| Short Circuit Current                    | I <sub>OS</sub> |                          |                          | ±50 |                          | mA   |

<sup>1.</sup> Nominal switching threshold is  $V_{DD}/2$ .

<sup>2.</sup> A decoupling capacitor of 0.01  $\mu F$  should be connected between  $V_{DD}$  on pin 7 and GND on pin 6, as close to the device as possible.

Table 4. AC Characteristics ( $V_{DD}$  = 3.3 V ± 5%; Ambient Temperature = -40°C to 85°C)

| Parameter                            | Symbol          | Condition                          | Min | Тур | Max | Unit |

|--------------------------------------|-----------------|------------------------------------|-----|-----|-----|------|

| Input Frequency                      |                 |                                    | 0   |     | 160 | MHz  |

| Output Frequency <sup>(1)</sup>      |                 | 15 pF load                         |     |     | 160 | MHz  |

| Output Clock Rise Time               | t <sub>OR</sub> | 0.8 V to 2.0 V                     |     |     | 1.5 | ns   |

| Output Clock Fall Time               | t <sub>OF</sub> | 2.0 V to 0.8 V                     |     |     | 1.5 | ns   |

| Propagation Delay <sup>(2)</sup>     |                 | 135 MHz                            | 1.5 | 4   | 5   | ns   |

| Output to Output Skew <sup>(3)</sup> |                 | Rising edges at V <sub>DD</sub> /2 |     |     | 300 | ps   |

- 1. Measured with an external series resistor of  $33\Omega$  positioned close to each output pin

- 2. Measured with rail to rail input clock

- 3. Measured between any 2 outputs with equal loading

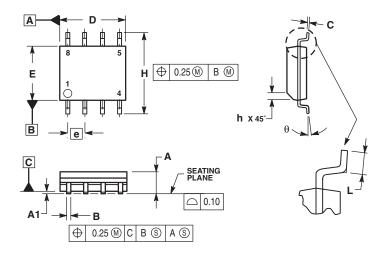

### PACKAGE DIMENSIONS

**D/EF SUFFIX SOIC PACKAGE CASE 751-06 ISSUE T**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. DIMENSIONS ARE IN MILLIMETER.

3. DIMENSION D AND E DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

5. DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 1.35        | 1.75 |  |  |

| A1  | 0.10        | 0.25 |  |  |

| В   | 0.35        | 0.49 |  |  |

| С   | 0.19        | 0.25 |  |  |

| D   | 4.80        | 5.00 |  |  |

| Е   | 3.80        | 4.00 |  |  |

| е   | 1.27 BSC    |      |  |  |

| Н   | 5.80        | 6.20 |  |  |

| h   | 0.25        | 0.50 |  |  |

| L   | 0.40        | 1.25 |  |  |

| А   | U,          | 7°   |  |  |

## Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

For Sales

800-345-7015 408-284-8200

Fax: 408-284-2775

**For Tech Support**

netcom@idt.com 480-763-2056

## **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

## Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

## **Europe**

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA