**DATA SHEET**

## **General Description**

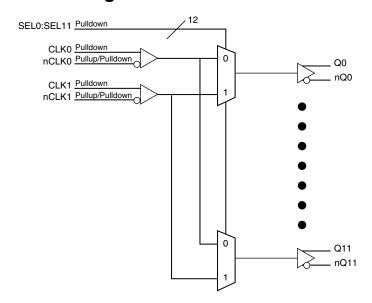

The ICS85352I is a 12 bit, 2-to-1 LVPECL Clock Buffer. Individual input select controls support independent multiplexer operation from a common clock input source. Clock inputs accept most standard differential levels.

The ICS85352I is characterized at full 3.3V or mixed 3.3V core/2.5V output operating supply modes.

#### **Features**

- Twelve, 2-to-1 multiplexers with LVPECL outputs

- · Selectable differential CLKx, nCLKx input pairs

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

- Maximum output frequency: 700MHz

- Individual select control for each multiplexer

- Select inputs accept LVCMOS / LVTTL levels

- Propagation delay: 2ns (maximum)

- Additive Phase Jitter, RMS: 0.21ps (typical), 3.3V

- Full 3.3V or mixed 3.3V core/2.5V output supply

- -40°C to 85°C ambient operating temperature

- Available in both standard (RoHS 5) and lead-free (RoHS 6) packages

## **Block Diagram**

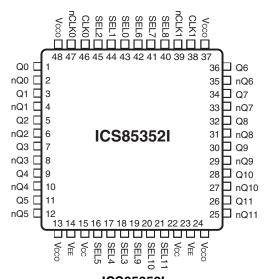

## **Pin Assignment**

ICS85352I

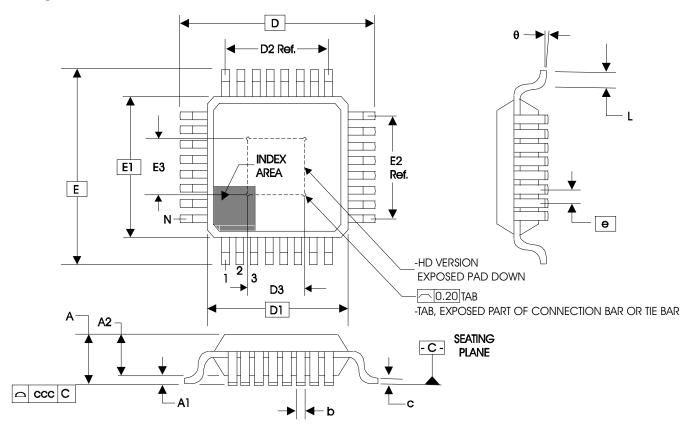

48-Lead TQFP, E-Pad

7mm x 7mm x 1.0mm package body

Y Package

Top View

**Table 1. Pin Descriptions**

| Number                                                                                                      | Name                                                                                                                                 | Т      | уре                 | Description                                                                        |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|------------------------------------------------------------------------------------|

| 1, 2<br>3, 4<br>5, 6<br>7, 8<br>9, 10<br>11, 12<br>25, 26<br>27, 28<br>29, 30<br>31, 32<br>33, 34<br>35, 36 | Q0, nQ0<br>Q1, nQ1<br>Q2, nQ2<br>Q3, nQ3<br>Q4, nQ4<br>Q5, nQ5<br>nQ11, Q11<br>nQ10, Q10<br>nQ9, Q9<br>nQ8, Q8<br>nQ7, Q7<br>nQ6, Q6 | Output |                     | Differential output pairs. LVPECL interface levels.                                |

| 13, 24, 37, 48                                                                                              | V <sub>CCO</sub>                                                                                                                     | Power  |                     | Output power supply pins.                                                          |

| 14, 23                                                                                                      | V <sub>EE</sub>                                                                                                                      | Power  |                     | Negative power supply pins.                                                        |

| 15, 22                                                                                                      | V <sub>CC</sub>                                                                                                                      | Power  |                     | Positive power supply pins.                                                        |

| 16, 17,<br>18, 19,<br>20, 21,<br>40, 41,<br>42, 43,<br>44, 45                                               | SEL5, SEL4,<br>SEL3, SEL9,<br>SEL10, SEL11,<br>SEL8, SEL7,<br>SEL6, SEL0,<br>SEL1, SEL2                                              | Input  | Pulldown            | Clock select inputs. LVCMOS / LVTTL interface levels. See Table 3.                 |

| 38                                                                                                          | CLK1                                                                                                                                 | Input  | Pulldown            | Non-inverting differential clock input.                                            |

| 39                                                                                                          | nCLK1                                                                                                                                | Input  | Pullup/<br>Pulldown | Inverting differential clock input. V <sub>CC</sub> /2 default when left floating. |

| 46                                                                                                          | CLK0                                                                                                                                 | Input  | Pulldown            | Non-inverting differential clock input.                                            |

| 47                                                                                                          | nCLK0                                                                                                                                | Input  | Pullup/<br>Pulldown | Inverting differential clock input. V <sub>CC</sub> /2 default when left floating  |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

## **Table 2. Pin Characteristics**

| Symbol                | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance       |                 |         | 4       |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor   |                 |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |                 |         | 51      |         | kΩ    |

## **Function Table**

**Table 3. Control Input Function Table**

| SELx | Selected Clock inputs |

|------|-----------------------|

| 0    | CLK0, nCLK0           |

| 1    | CLK1, nCLK1           |

## **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                                     | Rating                          |

|----------------------------------------------------------|---------------------------------|

| Supply Voltage, V <sub>CC</sub>                          | 4.6V                            |

| Inputs, V <sub>I</sub>                                   | -0.5V to V <sub>CC</sub> + 0.5V |

| Outputs, I <sub>O</sub> Continuous Current Surge Current | 50mA<br>100mA                   |

| Package Thermal Impedance, $\theta_{JA}$                 | 27.6°C/W (0 lfpm)               |

| Storage Temperature, T <sub>STG</sub>                    | -65°C to 150°C                  |

#### **DC Electrical Characteristics**

Table 4A. Power Supply DC Characteristics,  $V_{CC}$  = 3.3V ± 5%,  $V_{CCO}$  = 2.5V to 3.3V ±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to 85°C

| Symbol           | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|-------------------------|-----------------|---------|---------|---------|-------|

| V <sub>CC</sub>  | Positive Supply Voltage |                 | 3.135   | 3.3     | 3.465   | V     |

| V <sub>CCO</sub> | Output Supply Voltage   |                 | 2.375   | 3.3     | 3.465   | V     |

| I <sub>EE</sub>  | Power Supply Current    |                 |         |         | 170     | mA    |

Table 4B. LVCMOS/LVTTL DC Characteristics,  $V_{CC}$  = 3.3V ± 5%,  $V_{CCO}$  = 2.5V to 3.3V ±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to 85°C

| Symbol          | Parameter          |           | Test Conditions                | Minimum | Typical | Maximum               | Units |

|-----------------|--------------------|-----------|--------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage |           |                                | 2       |         | V <sub>CC</sub> + 0.3 | V     |

| $V_{IL}$        | Input Low Voltage  |           |                                | -0.3    |         | 0.8                   | V     |

| I <sub>IH</sub> | Input High Current | SEL[0:11] | $V_{CC} = V_{IN} = 3.465V$     |         |         | 150                   | μΑ    |

| I <sub>IL</sub> | Input Low Current  | SEL[0:11] | $V_{CC} = 3.465V, V_{IN} = 0V$ | -5      |         |                       | μΑ    |

Table 4C. Differential Input DC Characteristics,  $V_{CC}$  = 3.3V  $\pm$  5%,  $V_{CCO}$  = 2.5V to 3.3V  $\pm$ 5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to 85°C

| Symbol                             | Parameter                            |              | Test Conditions | Minimum               | Typical | Maximum                | Units |

|------------------------------------|--------------------------------------|--------------|-----------------|-----------------------|---------|------------------------|-------|

| I <sub>IH</sub> Input High Current | land think Ourse                     | CLK0, CLK1   |                 |                       |         | 150                    | μΑ    |

|                                    | nCLK0, nCLK1                         |              |                 |                       | 150     | μΑ                     |       |

|                                    | Input Low Current                    | CLK0, CLK1   |                 | -5                    |         |                        | μΑ    |

| ¹IL                                |                                      | nCLK0, nCLK1 |                 | -150                  |         |                        | μA    |

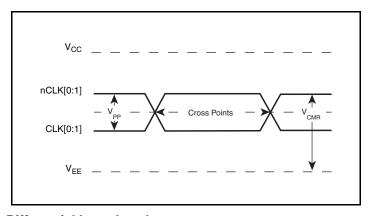

| V <sub>PP</sub>                    | Peak-to-Peak Input Voltage; NOTE 1   |              |                 | 0.15                  |         | 1.0                    | V     |

| V <sub>CMR</sub>                   | Common Mode Input Voltage; NOTE 1, 2 |              |                 | V <sub>EE</sub> + 0.5 |         | V <sub>CC</sub> - 0.85 | V     |

NOTE 1: V<sub>IL</sub> should not be less than -0.3V.

NOTE 2: Common mode input voltage is defined as VIH.

Table 4D. LVPECL DC Characteristics,  $V_{CC}$  = 3.3V  $\pm$  5%,  $V_{CCO}$  = 2.5V to 3.3V  $\pm$ 5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to 85°C

| Symbol             | Parameter                         | Test Conditions | Minimum                | Typical | Maximum                | Units |

|--------------------|-----------------------------------|-----------------|------------------------|---------|------------------------|-------|

| V <sub>OH</sub>    | Output High Voltage; NOTE 1       |                 | V <sub>CCO</sub> – 1.4 |         | V <sub>CCO</sub> - 0.9 | V     |

| V <sub>OL</sub>    | Output Low Voltage; NOTE 1        |                 | V <sub>CCO</sub> - 2.0 |         | V <sub>CCO</sub> - 1.7 | V     |

| V <sub>SWING</sub> | Peak-to-Peak Output Voltage Swing |                 | 0.6                    |         | 1.0                    | V     |

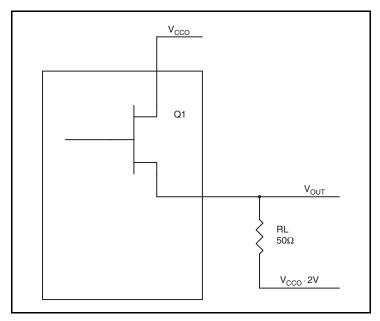

NOTE 1: Outputs terminated with  $50\Omega$  to  $V_{CCO} - 2V$ .

#### **AC Electrical Characteristics**

Table 5A. AC Electrical Characteristics,  $V_{CC} = V_{CCO} = 3.3V \pm 5\%$ ,  $V_{EE} = 0V$ ,  $T_A = -40^{\circ}C$  to 85°C

| Symbol                          | Parameter                                                                 | Test Conditions                                 | Minimum | Typical | Maximum | Units |

|---------------------------------|---------------------------------------------------------------------------|-------------------------------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub>                | Output Frequency                                                          |                                                 |         |         | 700     | MHz   |

| t <sub>PD</sub>                 | Propagation Delay; NOTE 1                                                 |                                                 | 1.0     | 1.5     | 2.0     | ns    |

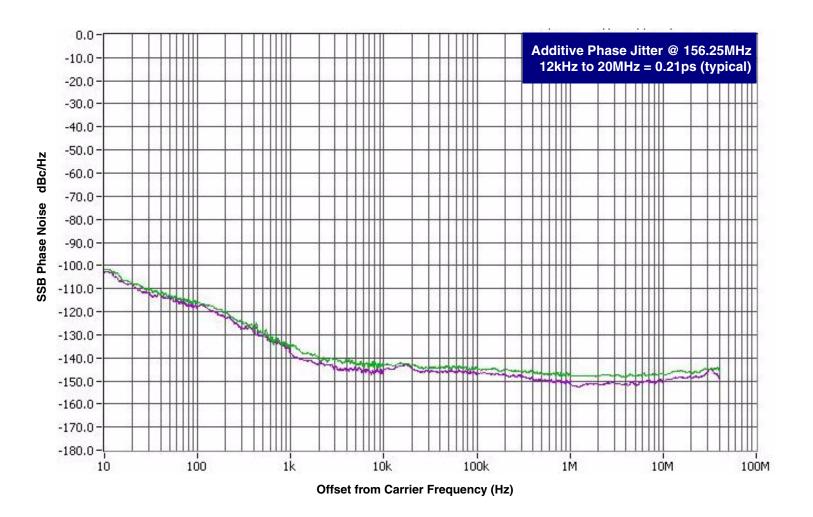

| <i>t</i> jit                    | Buffer Additive Phase Jitter, RMS: refer to additive Phase Jitter Section | 156.25MHz<br>Integration Range: (12kHz – 20MHz) |         | 0.21    |         | ps    |

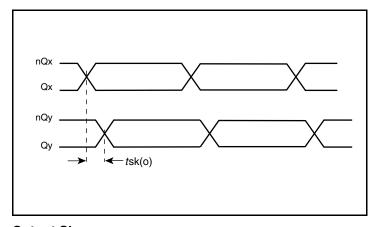

| tsk(o)                          | Output Skew; NOTE 2, 3                                                    |                                                 |         |         | 180     | ps    |

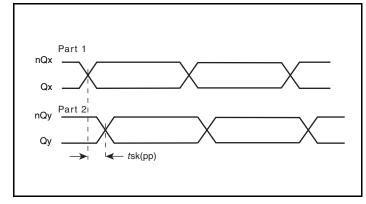

| tsk(pp)                         | Part-to-Part Skew; NOTE 2, 4                                              |                                                 |         |         | 750     | ps    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/ Fall Time                                                    | 20% to 80%                                      | 150     |         | 700     | ps    |

| odc                             | Output Duty Cycle                                                         | <i>f</i> ≤ 622MHz                               | 45      |         | 55      | %     |

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. Device will meet specifications after thermal equilibrium has been reached under these conditions.

NOTE: All parameters measured at f<sub>MAX</sub> unless noted otherwise.

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the differential cross points.

NOTE 4: Defined as skew between outputs on different devices operating at the same supply voltage, same temperature and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

Table 5B. AC Electrical Characteristics,  $V_{CC}$  = 3.3V ± 5%,  $V_{CCO}$  = 2.5V ± 5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to 85°C

| Symbol           | Parameter                         | Test Conditions                                 | Minimum | Typical | Maximum | Units |

|------------------|-----------------------------------|-------------------------------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub> | Output Frequency                  |                                                 |         |         | 700     | MHz   |

| t <sub>PD</sub>  | Propagation Delay; NOTE 1         |                                                 | 1.0     | 1.5     | 2.0     | ns    |

| <i>t</i> jit     | Buffer Additive Phase Jitter, RMS | 156.25MHz<br>Integration Range: (12kHz – 20MHz) |         | 0.23    |         | ps    |

| tsk(o)           | Output Skew; NOTE 2, 3            |                                                 |         |         | 180     | ps    |

| tsk(pp)          | Part-to-Part Skew; NOTE 2, 4      |                                                 |         |         | 750     | ps    |

| $t_R / t_F$      | Output Rise/ Fall Time            | 20% to 80%                                      | 150     |         | 700     | ps    |

| odc              | Output Duty Cycle                 | <i>f</i> ≤ 622MHz                               | 45      |         | 55      | %     |

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. Device will meet specifications after thermal equilibrium has been reached under these conditions.

NOTE: All parameters measured at f<sub>MAX</sub> unless noted otherwise.

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the differential cross points.

NOTE 4: Defined as skew between outputs on different devices operating at the same supply voltage, same temperature and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

#### **Additive Phase Jitter**

The spectral purity in a band at a specific offset from the fundamental compared to the power of the fundamental is called the *dBc Phase Noise*. This value is normally expressed using a Phase noise plot and is most often the specified plot in many applications. Phase noise is defined as the ratio of the noise power present in a 1Hz band at a specified offset from the fundamental frequency to the power value of the fundamental. This ratio is expressed in decibels (dBm) or a ratio

of the power in the 1Hz band to the power in the fundamental. When the required offset is specified, the phase noise is called a *dBc* value, which simply means dBm at a specified offset from the fundamental. By investigating jitter in the frequency domain, we get a better understanding of its effects on the desired application over the entire time record of the signal. It is mathematically possible to calculate an expected bit error rate given a phase noise plot.

As with most timing specifications, phase noise measurements has issues relating to the limitations of the equipment. Often the noise floor of the equipment is higher than the noise floor of the device. This is illustrated above. The device meets the noise floor of what is shown, but can actually be lower. The phase noise is dependent on the input source and measurement equipment.

The source generator "Rohde & Schwarz Signal Generator SMA100A 9kHz – 6GHz as external input to a Hewlett Packard 8133A 3GHz Pulse Generator".

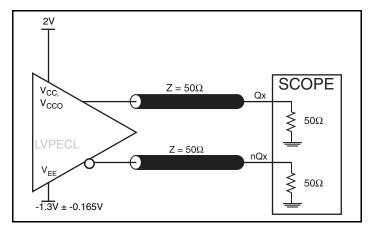

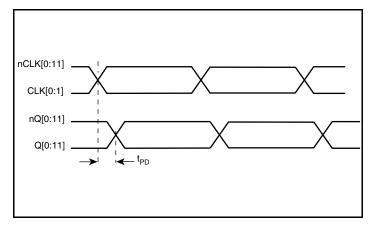

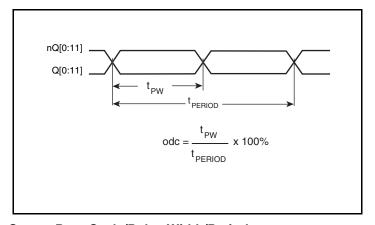

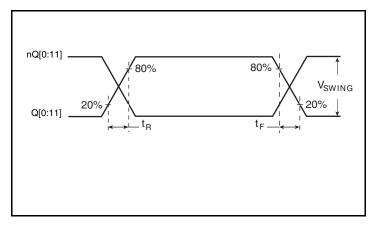

## **Parameter Measurement Information**

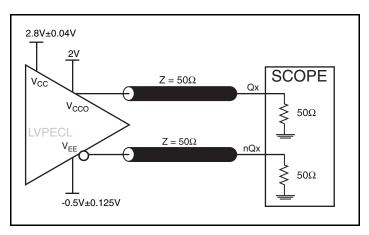

3.3V Core/ 3.3V LVPECL Output Load AC Test Circuit

3.3V Core/ 2.5V LVPECL Output Load AC Test Circuit

**Differential Input Level**

**Part-to-Part Skew**

**Output Skew**

**Propagation Delay**

# **Parameter Measurement Information, continued**

Output Duty Cycle/Pulse Width/Period

**Output Rise/Fall Time**

## **Application Information**

## **Recommendations for Unused Input and Output Pins**

#### Inputs:

#### **LVCMOS Control Pins**

All control pins have internal pullups or pulldowns; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

#### **CLK/nCLK Inputs**

For applications not requiring the use of the differential input, both CLK and nCLK can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from CLK to ground.

#### **Outputs:**

#### **LVPECL Outputs**

The unused LVPECL output pair can be left floating. We recommend that there is no trace attached. Both sides of the differential output pair should either be left floating or terminated.

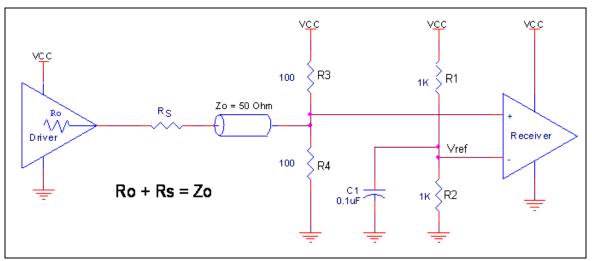

#### Wiring the Differential Input to Accept Single-Ended Levels

Figure 1 shows how a differential input can be wired to accept single ended levels. The reference voltage  $V_{REF} = V_{CC}/2$  is generated by the bias resistors R1 and R2. The bypass capacitor (C1) is used to help filter noise on the DC bias. This bias circuit should be located as close to the input pin as possible. The ratio of R1 and R2 might need to be adjusted to position the  $V_{REF}$  in the center of the input voltage swing. For example, if the input clock swing is 2.5V and  $V_{CC} = 3.3V$ , R1 and R2 value should be adjusted to set  $V_{REF}$  at 1.25V. The values below are for when both the single ended swing and  $V_{CC}$  are at the same voltage. This configuration requires that the sum of the output impedance of the driver (Ro) and the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the input will attenuate the signal in half. This can be done in one of two ways. First, R3 and R4 in parallel should equal the transmission

line impedance. For most  $50\Omega$  applications, R3 and R4 can be  $100\Omega$ . The values of the resistors can be increased to reduce the loading for slower and weaker LVCMOS driver. When using single-ended signaling, the noise rejection benefits of differential signaling are reduced. Even though the differential input can handle full rail LVCMOS signaling, it is recommended that the amplitude be reduced. The datasheet specifies a lower differential amplitude, however this only applies to differential signals. For single-ended applications, the swing can be larger, however  $V_{IL}$  cannot be less than -0.3V and  $V_{IH}$  cannot be more than Vcc + 0.3V. Though some of the recommended components might not be used, the pads should be placed in the layout. They can be utilized for debugging purposes. The datasheet specifications are characterized and guaranteed by using a differential signal.

Figure 1. Recommended Schematic for Wiring a Differential Input to Accept Single-ended Levels

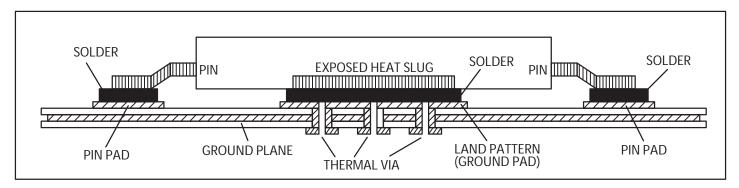

#### **EPAD Thermal Release Path**

In order to maximize both the removal of heat from the package and the electrical performance, a land pattern must be incorporated on the Printed Circuit Board (PCB) within the footprint of the package corresponding to the exposed metal pad or exposed heat slug on the package, as shown in *Figure 2*. The solderable area on the PCB, as defined by the solder mask, should be at least the same size/shape as the exposed pad/slug area on the package to maximize the thermal/electrical performance. Sufficient clearance should be designed on the PCB between the outer edges of the land pattern and the inner edges of pad pattern for the leads to avoid any shorts.

While the land pattern on the PCB provides a means of heat transfer and electrical grounding from the package to the board through a solder joint, thermal vias are necessary to effectively conduct from the surface of the PCB to the ground plane(s). The land pattern must be connected to ground through these vias. The vias act as "heat pipes". The number of vias (i.e. "heat pipes") are application specific

and dependent upon the package power dissipation as well as electrical conductivity requirements. Thus, thermal and electrical analysis and/or testing are recommended to determine the minimum number needed. Maximum thermal and electrical performance is achieved when an array of vias is incorporated in the land pattern. It is recommended to use as many vias connected to ground as possible. It is also recommended that the via diameter should be 12 to 13mils (0.30 to 0.33mm) with 1oz copper via barrel plating. This is desirable to avoid any solder wicking inside the via during the soldering process which may result in voids in solder between the exposed pad/slug and the thermal land. Precautions should be taken to eliminate any solder voids between the exposed heat slug and the land pattern. Note: These recommendations are to be used as a guideline only. For further information, refer to the Application Note on the Surface Mount Assembly of Amkor's Thermally/Electrically Enhance Leadframe Base Package, Amkor Technology.

Figure 2. Assembly for Exposed Pad Thermal Release Path - Side View (drawing not to scale)

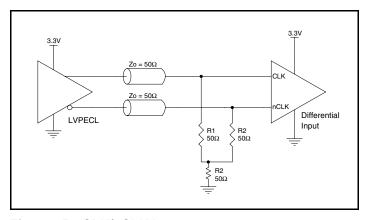

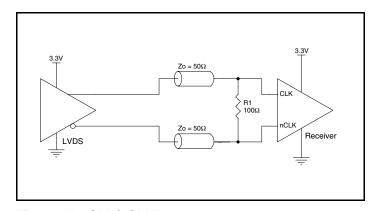

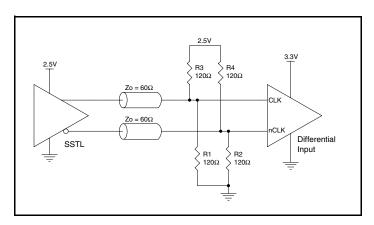

### **Differential Clock Input Interface**

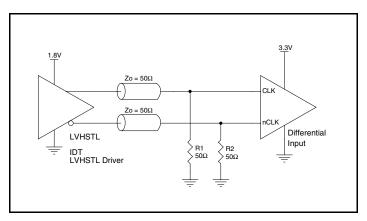

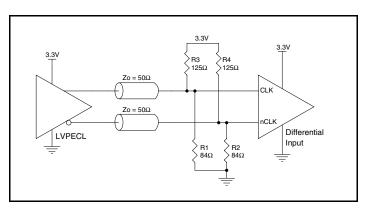

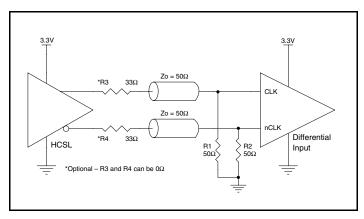

The CLK /nCLK accepts LVDS, LVPECL, LVHSTL, SSTL, HCSL and other differential signals. Both  $V_{\text{SWING}}$  and  $V_{\text{OH}}$  must meet the  $V_{\text{PP}}$  and  $V_{\text{CMR}}$  input requirements. Figures 3A to 3F show interface examples for the CLK/nCLK input driven by the most common driver types. The input interfaces suggested here are examples only. Please consult

with the vendor of the driver component to confirm the driver termination requirements. For example in *Figure 3A*, the input termination applies for IDT LVHSTL drivers. If you are using an LVHSTL driver from another vendor, use their termination recommendation.

Figure 3A. CLK/nCLK Input

Driven by an IDT LVHSTL Driver

Figure 3C. CLK/nCLK Input

Driven by a 3.3V LVPECL Driver

Figure 3E. CLK/nCLK Input

Driven by a 3.3V HCSL Driver

Figure 3B. CLK/nCLK Input

Driven by a 3.3V LVPECL Driver

Figure 3D. CLK/nCLK Input

Driven by a 3.3V LVDS Driver

Figure 3F. CLK/nCLK Input Driven by a 2.5V SSTL Driver

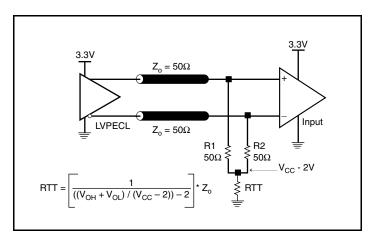

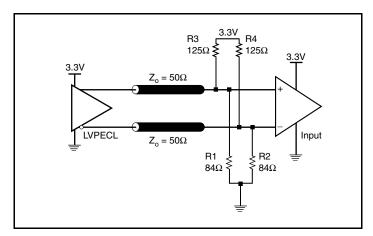

### **Termination for 3.3V LVPECL Outputs**

The clock layout topology shown below is a typical termination for LVPECL outputs. The two different layouts mentioned are recommended only as guidelines.

The differential outputs are low impedance follower outputs that generate ECL/LVPECL compatible outputs. Therefore, terminating resistors (DC current path to ground) or current sources must be used for functionality. These outputs are designed to drive  $50\Omega$

Figure 4A. 3.3V LVPECL Output Termination

transmission lines. Matched impedance techniques should be used to maximize operating frequency and minimize signal distortion. *Figures 4A and 4B* show two different layouts which are recommended only as guidelines. Other suitable clock layouts may exist and it would be recommended that the board designers simulate to guarantee compatibility across all printed circuit and clock component process variations.

Figure 4B. 3.3V LVPECL Output Termination

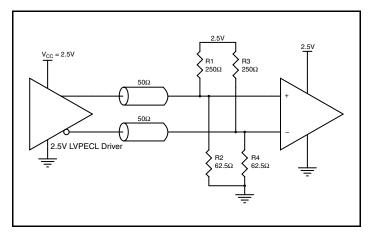

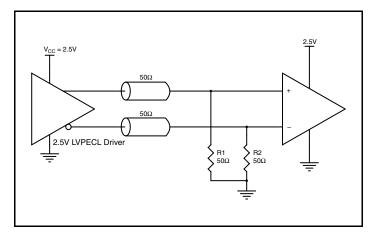

## **Termination for 2.5V LVPECL Outputs**

Figure 5A and Figure 5B show examples of termination for 2.5V LVPECL driver. These terminations are equivalent to terminating  $50\Omega$  to  $V_{CC}$  – 2V. For  $V_{CCO}$  = 2.5V, the  $V_{CCO}$  – 2V is very close to ground

level. The R3 in Figure 5B can be eliminated and the termination is shown in *Figure 5C*.

Figure 5A. 2.5V LVPECL Driver Termination Example

Figure 5B. 2.5V LVPECL Driver Termination Example

Figure 5C. 2.5V LVPECL Driver Termination Example

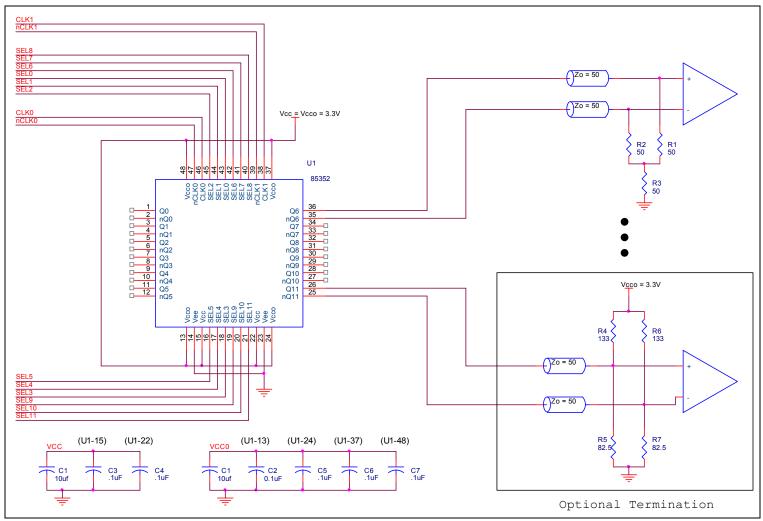

## **Application Schematic Example**

Figure 6 shows an example of ICS85352I application schematic. In this example, the device is operated at  $V_{\rm CC}$  = 3.3V. The decoupling capacitor should be located as close as possible to the power pin. For

the LVPECL output drivers, only two terminations examples are shown in this schematic. Additional termination approaches can be found in the LVPECL Termination Application Note.

Figure 6. ICS85352I Application Schematic

#### **Power Considerations**

This section provides information on power dissipation and junction temperature for the ICS85352I. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The total power dissipation for the ICS85352I is the sum of the core power plus the power dissipated in the load(s).

The following is the power dissipation for  $V_{CC} = 3.3V + 5\% = 3.465V$ , which gives worst case results.

NOTE: Please refer to Section 3 for details on calculating power dissipated in the load.

- Power (core)<sub>MAX</sub> = V<sub>CC MAX</sub> \* I<sub>EE MAX</sub> = 3.465V \* 170mA = 589.05mW

- Power (outputs)<sub>MAX</sub> = 30mW/Loaded Output pair

If all outputs are loaded, the total power is 12 \* 30mW = 360mW

Total Power\_MAX (3.3V, with all outputs switching) = 589.05mW + 360mW = 949.05mW

#### 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and it directly affects the reliability of the device. The maximum recommended junction temperature is 125°C. Limiting the internal transistor junction temperature, Tj, to 125°C ensures that the bond wire and bond pad temperature remains below 125°C.

The equation for Tj is as follows: Tj =  $\theta_{JA}$  \* Pd\_total + T<sub>A</sub>

Tj = Junction Temperature

$\theta_{JA}$  = Junction-to-Ambient Thermal Resistance

Pd\_total = Total Device Power Dissipation (example calculation is in section 1 above)

T<sub>A</sub> = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta_{JA}$  must be used. Assuming a moderate air flow of 200 linear feet per minute and a multi-layer board, the appropriate value is 22.6°C/W per Table 6 below.

Therefore, Tj for an ambient temperature of 85°C with all outputs switching is:

$85^{\circ}\text{C} + 0.949\text{W} * 22.6^{\circ}\text{C/W} = 106.4^{\circ}\text{C}$ . This is below the limit of  $125^{\circ}\text{C}$ .

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow and the type of board (multi-layer).

Table 6. Thermal Resistance  $\theta_{JA}$  for 48 Lead TQFP, Forced Convection

| θ <sub>JA</sub> by Velocity                 |          |          |           |  |  |

|---------------------------------------------|----------|----------|-----------|--|--|

| Linear Feet per Minute                      | 0        | 200      | 500       |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 27.6°C/W | 22.6°C/W | 20.78°C/W |  |  |

#### 3. Calculations and Equations.

The purpose of this section is to calculate the power dissipation for the LVPECL output pairs.

LVPECL output driver circuit and termination are shown in Figure 5.

Figure 5. LVPECL Driver Circuit and Termination

To calculate worst case power dissipation into the load, use the following equations which assume a  $50\Omega$  load, and a termination voltage of  $V_{CCO} - 2V$ .

- For logic high,  $V_{OUT} = V_{OH\_MAX} = V_{CCO\_MAX} 0.9V$  $(V_{CCO\_MAX} - V_{OH\_MAX}) = 0.9V$

- For logic low,  $V_{OUT} = V_{OL\_MAX} = V_{CCO\_MAX} 1.7V$   $(V_{CCO\_MAX} V_{OL\_MAX}) = 1.7V$

Pd\_H is power dissipation when the output drives high.

Pd\_L is the power dissipation when the output drives low.

$$Pd\_H = [(V_{OH\_MAX} - (V_{CCO\_MAX} - 2V))/R_L] * (V_{CCO\_MAX} - V_{OH\_MAX}) = [(2V - (V_{CCO\_MAX} - V_{OH\_MAX}))/R_L] * (V_{CCO\_MAX} - V_{OH\_MAX}) = [(2V - 0.9V)/50\Omega] * 0.9V = 19.8mW$$

$$Pd\_L = [(V_{OL\_MAX} - (V_{CCO\_MAX} - 2V))/R_L] * (V_{COC\_MAX} - V_{OL\_MAX}) = [(2V - (V_{CCO\_MAX} - V_{OL\_MAX}))/R_L] * (V_{CCO\_MAX} - V_{OL\_MAX}) = [(2V - 1.7V)/50\Omega] * 1.7V = \textbf{10.2mW}$$

Total Power Dissipation per output pair = Pd\_H + Pd\_L = 30mW

## **Reliability Information**

## Table 7. $\theta_{\text{JA}}$ vs. Air Flow Table for a 48 Lead TQFP, E-Pad

| $\theta_{JA}$ vs. Air Flow                  |          |          |           |  |  |

|---------------------------------------------|----------|----------|-----------|--|--|

| Linear Feet per Minute                      | 0        | 200      | 500       |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 27.6°C/W | 22.6°C/W | 20.78°C/W |  |  |

#### **Transistor Count**

The transistor count for ICS85352I is: 2252

## **Package Outline and Package Dimensions**

Package Outline - Y Suffix for 48 Lead TQFP, E-Pad

Table 8. Package Dimensions 48 Lead TQFP, E-Pad

| JEDEC Variation: ABC - HD All Dimensions in Millimeters |                         |      |      |  |  |  |  |

|---------------------------------------------------------|-------------------------|------|------|--|--|--|--|

| Symbol                                                  | Minimum Nominal Maximum |      |      |  |  |  |  |

| N                                                       | 48                      |      |      |  |  |  |  |

| Α                                                       |                         |      | 1.20 |  |  |  |  |

| <b>A</b> 1                                              | 0.05                    | 0.10 | 0.15 |  |  |  |  |

| A2                                                      | 0.95                    | 1.00 | 1.05 |  |  |  |  |

| b                                                       | 0.17                    | 0.22 | 0.27 |  |  |  |  |

| С                                                       | 0.09                    |      | 0.20 |  |  |  |  |

| D & E                                                   | 9.00 Basic              |      |      |  |  |  |  |

| D1 & E1                                                 | 7.00 Basic              |      |      |  |  |  |  |

| D2 & E2                                                 | 5.50 Ref.               |      |      |  |  |  |  |

| D3 & E3                                                 |                         | 3.5  |      |  |  |  |  |

| е                                                       | 0.50 Basic              |      |      |  |  |  |  |

| L                                                       | 0.45                    | 0.60 | 0.75 |  |  |  |  |

| θ                                                       | 0°                      |      | 7°   |  |  |  |  |

| ccc                                                     |                         |      | 0.08 |  |  |  |  |

Reference Document: JEDEC Publication 95, MS-026

**Table 9. Ordering Information**

| Part/Order Number | Marking      | Package                        | Shipping Packaging | Temperature   |

|-------------------|--------------|--------------------------------|--------------------|---------------|

| 85352AYI          | ICS85352AYI  | 48 Lead TQFP, E-Pad            | Tray               | -40°C to 85°C |

| 85352AYIT         | ICS85352AYI  | 48 Lead TQFP, E-Pad            | 1000 Tape & Reel   | -40°C to 85°C |

| 85352AYILF        | ICS85352AYIL | Lead-Free, 48 Lead TQFP, E-Pad | Tray               | -40°C to 85°C |

| 85352AYILFT       | ICS85352AYIL | Lead-Free, 48 Lead TQFP, E-Pad | 1000 Tape & Reel   | -40°C to 85°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial and industrial applications. Any other applications, such as those requiring high reliability or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

# **Revision History Sheet**

| Rev       | Table     | Table Page Description of Change                |                                                                                               | Date    |  |

|-----------|-----------|-------------------------------------------------|-----------------------------------------------------------------------------------------------|---------|--|

|           |           | 1                                               | Features Section - added lead-free bullet.                                                    |         |  |

| ۸         |           | 6                                               | Added Recommendations for Unused Input and Output Pins.                                       | 7/6/06  |  |

| A         |           | 7                                               | Added Thermal Release Path.                                                                   | 7/6/06  |  |

|           | Т9        | 15                                              | Ordering Information Table - added lead-free part number, marking and note.                   |         |  |

| В         | T4A       | 3                                               | Power Supply DC Characteristics Table - corrected V <sub>CC</sub> min. from 3.475V to 3.135V. | 9/27/06 |  |

|           | T4C       | 3                                               | Differential DC Characteristics Table - updates notes.                                        |         |  |

| T5A - T5B | 4         | AC Characteristics Tables - added thermal note. |                                                                                               |         |  |

|           |           | 7                                               | Updated Wiring the Differential Input to Accept Single-ended Levels.                          |         |  |

|           |           | 8                                               | Updated EPAD Thermal Release Path.                                                            |         |  |

| В         |           | 9                                               | Differential Clock input Interface - added Figure 3F.                                         | 2/12/10 |  |

|           |           | 12                                              | Termination for 3.3V LVPECL Outputs - updated Figures 4A & 4B.                                |         |  |

|           | T8        | 15                                              | Power Considerations - re-calculated ambient temperature using 0 air flow.                    |         |  |

|           | Т9        | 16                                              | Updated Package Dimensions Table.                                                             |         |  |

|           |           |                                                 | Ordering Information Table - deleted "ICS" prefix from Part/Order Number                      |         |  |

| В         |           | 16                                              | Updated Package Outline.                                                                      | 3/9/10  |  |

| В         |           |                                                 | Corrected title of datasheet from clock generator to clock buffer.                            | 7/6/10  |  |

| С         |           | 1                                               | Features, corrected Propagation Delay bullet from 1.8ns to 2ns maximum.                       |         |  |

|           | T5A - T5B | 4                                               | AC Characteristics Tables - added Additive Phase Jitter spec.                                 | 0/0/10  |  |

|           |           | 5                                               | Added Additive Phase Jitter Plot.                                                             | 8/3/10  |  |

|           | T8        | 17                                              | Package Dimensions, corrected D3/E3 dimensions.                                               |         |  |

|           |           |                                                 |                                                                                               |         |  |

# We've Got Your Timing Solution

6024 Silver Creek Valley Road San Jose, California 95138

ales 00-345-7015 (insid

800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775

www.IDT.com/go/contactIDT

Technical Support

netcom@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

Copyright 2010. All rights reserved.