### **General Description**

The DS1081L is a spread-spectrum clock modulator IC that reduces EMI in high clock-frequency-based, digital electronic equipment.

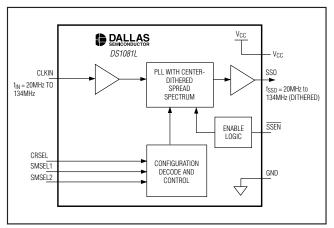

Using an integrated phase-locked loop (PLL), the DS1081L accepts an input clock signal in the range of 20MHz to 134MHz and delivers a spread-spectrum modulated output clock signal. The PLL modulates, or dithers, the output clock about the center input frequency at a pin-selectable magnitude and dither rate, allowing direct EMI control and optimization. In addition, through an enable pin the dithering can be enabled or disabled for easy comparison of system performance during EMI testing. This same input pin also allows the DS1081L output to be tri-stated.

By dithering the system clock, all the address, data, and timing signals generated from this signal are also dithered so that the measured EMI at the fundamental and harmonic frequencies is greatly reduced. This is accomplished without changing clock rise/fall times or adding the space, weight, design time, and cost associated with mechanical shielding.

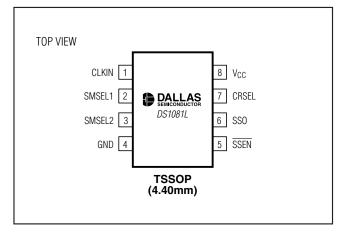

The DS1081L is provided in an 8-pin TSSOP package and operates over a full automotive temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

### **Applications**

LCD Panels for TVs, Desktop Monitors, and Notebook and Tablet PCs

Automotive Telematics and Infotainment

**Printers**

Typical Operating Circuit appears at end of data sheet.

### **Features**

- Modulates a 20MHz to 134MHz Clock with Center Spread-Spectrum Dithering

- **♦** Selectable Spread-Spectrum Modulation Magnitudes of:

±0.5%

±1.0%

±1.5%

±2.0%

- ♦ Low 75ps Cycle-to-Cycle Jitter

- **♦** Spread-Spectrum Disable Mode

- ♦ Pin Compatible with Alliance/PulseCore Semiconductor P2040 Series Devices

- **♦ Clock Output Disable**

- **♦ Low Cost**

- **♦ Low Power Consumption**

- ♦ 3.3V Single Voltage Supply

- ♦ -40°C to +125°C Temperature Range

- ♦ Small 8-Pin TSSOP Package

### **Ordering Information**

| PART       | TEMP RANGE      | PIN-PACKAGE |

|------------|-----------------|-------------|

| DS1081LE+  | -40°C to +125°C | 8 TSSOP     |

| DS1081LE+T | -40°C to +125°C | 8 TSSOP     |

<sup>+</sup>Denotes lead-free package.

#### Pin Configuration **Block Diagram**

Maxim Integrated Products 1

T Denotes tape-and-reel.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on V <sub>CC</sub> Relative to GND0.5V to +3.63V | Storage Temperature Range55°C to +125°C          |

|----------------------------------------------------------------|--------------------------------------------------|

| Voltage Range on Any Lead Relative                             | Soldering TemperatureSee J-STD-020 Specification |

| to GND0.5V to (V <sub>CC</sub> + 0.5V), not to exceed +3.63V   |                                                  |

| Operating Temperature Bange -40°C to +125°C                    |                                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

$(TA = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                       | SYMBOL          | CONDITIONS                             | MIN                       | TYP | MAX                       | UNITS |

|---------------------------------|-----------------|----------------------------------------|---------------------------|-----|---------------------------|-------|

| Supply Voltage                  | V <sub>CC</sub> | (Note 1)                               | 3.0                       |     | 3.6                       | V     |

| Input Logic 1                   | VIH             |                                        | 0.8 x<br>V <sub>C</sub> C |     | V <sub>CC</sub> + 0.3     | V     |

| Input Logic 0                   | VIL             |                                        | -0.3                      |     | 0.2 x<br>V <sub>C</sub> C | V     |

| Input Logic Float (SSEN, CRSEL) | VFLOAT          | 0V < V <sub>IN</sub> < V <sub>CC</sub> |                           |     | ±1                        | μΑ    |

| SSO Load                        | CL              | SSO < 80MHz                            |                           |     | 15                        | pF    |

| SSO Load                        |                 | 80MHz ≤ SSO < 134MHz                   |                           |     | 7                         |       |

| CLKIN Frequency                 | fIN             |                                        | 20                        |     | 134                       | MHz   |

| CLKIN Duty Cycle                | fINDC           |                                        | 40                        |     | 60                        | %     |

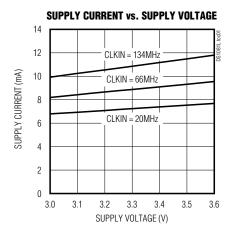

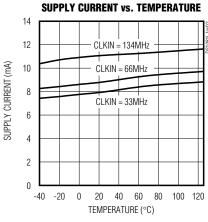

#### DC ELECTRICAL CHARACTERISTICS

( $V_{CC}$  = +3.0V to +3.6V,  $T_A$  = -40°C to +125°C, unless otherwise noted.)

| PARAMETER                         | SYMBOL            | CONDITIONS                             | MIN  | TYP | MAX  | UNITS |

|-----------------------------------|-------------------|----------------------------------------|------|-----|------|-------|

| Supply Current                    | Icc               | $C_L = 7pF$<br>$f_{IN} = 134MHz$       |      |     | 15   | mA    |

| SMSEL1/SMSEL2/CLKIN Input Leakage | I <sub>IL:1</sub> | 0V < V <sub>IN</sub> < V <sub>CC</sub> | -1   |     | +1   | μΑ    |

| CRSEL/SSEN Input Leakage          | I <sub>IL:2</sub> | 0V < V <sub>IN</sub> < V <sub>CC</sub> | -100 |     | +100 | μΑ    |

| Output Leakage (SSO)              | loz               | SSEN = float                           | -1   |     | +1   | μΑ    |

| Low-Level Output Voltage (SSO)    | V <sub>OL</sub>   | I <sub>OL</sub> = 4mA                  |      |     | 0.4  | V     |

| High-Level Output Voltage (SSO)   | VoH               | I <sub>OH</sub> = -4mA                 | 2.4  |     |      | V     |

### **AC ELECTRICAL CHARACTERISTICS**

( $V_{CC}$  = +3.0V to +3.6V,  $T_A$  = -40°C to +125°C, unless otherwise noted.)

| PARAMETER                  | SYMBOL         | CONDITIONS                                                                 | MIN | TYP | MAX | UNITS |

|----------------------------|----------------|----------------------------------------------------------------------------|-----|-----|-----|-------|

| SSO Duty Cycle             | fssodc         | Measured at V <sub>CC</sub> /2                                             | 40  |     | 60  | %     |

| SSO Rise Time              | t <sub>R</sub> | C <sub>L</sub> = 7pF                                                       |     | 1   |     | ns    |

| SSO Fall Time              | tF             | $C_L = 7pF$                                                                |     | 1   |     | ns    |

| Peak Cycle-to-Cycle Jitter | tJ             | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, 10,000 \text{ cycles}$ |     | 75  |     | ps    |

| Power-Up Time              | tpor           | (Note 2)                                                                   |     |     | 50  | ms    |

Note 1: All voltages referenced to ground. Currents into the IC are positive and out of the IC are negative.

**Note 2:** Time between power applied to device and stable output.

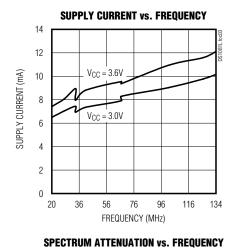

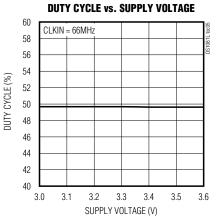

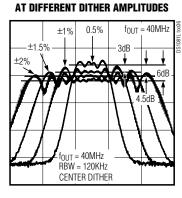

**Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

ATTENUATION (dB)

### **Pin Description**

| PIN | NAME   | FUNCTION                                                                                                                                          |                                                                                                                                       |                                                                             |  |  |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| 1   | CLKIN  | Clock Input. 20MHz to 134MHz clock input (fin).                                                                                                   |                                                                                                                                       |                                                                             |  |  |

| 2   | SMSEL2 | Spread-Spectrum Magnitude Select Inputs. These digital inputs select the desired spread-spectrum magnitude as shown in the table below.           |                                                                                                                                       |                                                                             |  |  |

| _   | 00222  | SMSEL2                                                                                                                                            | SMSEL1                                                                                                                                | MAGNITUDE SELECTED                                                          |  |  |

|     |        | 0                                                                                                                                                 | 0                                                                                                                                     | ±2.0%                                                                       |  |  |

|     |        | 0                                                                                                                                                 | 1                                                                                                                                     | ±1.5%                                                                       |  |  |

| 3   | SMSEL1 | 1                                                                                                                                                 | 0                                                                                                                                     | ±1.0%                                                                       |  |  |

|     |        | 1                                                                                                                                                 | 1                                                                                                                                     | ±0.5%                                                                       |  |  |

| 4   | GND    | Ground                                                                                                                                            |                                                                                                                                       |                                                                             |  |  |

| 5   | SSEN   | Spread-Spectrum Enable. Three-lev  0 = Power-up/spread-spectrum ena                                                                               | el input to enable/disable spread-sp                                                                                                  | ectrum and to tri-state the output.                                         |  |  |

|     | 332.1  | Float = SSO tri-stated.  1 = Power-up/spread-spectrum disa                                                                                        |                                                                                                                                       |                                                                             |  |  |

| 6   | SSO    | 1 = Power-up/spread-spectrum disa                                                                                                                 |                                                                                                                                       | rum version of the clock input at                                           |  |  |

| 6   |        | 1 = Power-up/spread-spectrum disa<br>Spread-Spectrum Clock Output. Ou<br>CLKIN.                                                                   | abled (not a bypass mode).                                                                                                            |                                                                             |  |  |

|     | SSO    | 1 = Power-up/spread-spectrum disa<br>Spread-Spectrum Clock Output. Ou<br>CLKIN.<br>Clock Range and Dither Rate Selec                              | abled (not a bypass mode).<br>tputs a center-dithered spread-specti                                                                   |                                                                             |  |  |

| 6   |        | Power-up/spread-spectrum disased Spread-Spectrum Clock Output. Our CLKIN.  Clock Range and Dither Rate Select Description section for details.    | abled (not a bypass mode).  tputs a center-dithered spread-spection.  St. Three-level input that determines                           | the dither rate. See the <i>Detailed</i>                                    |  |  |

|     | SSO    | Power-up/spread-spectrum disased-spectrum Clock Output. Our CLKIN.  Clock Range and Dither Rate Select Description section for details.  CRSEL    | tputs a center-dithered spread-spectrot. Three-level input that determines  CLKIN RANGE                                               | the dither rate. See the <i>Detailed</i> DITHER RATE                        |  |  |

|     | SSO    | Power-up/spread-spectrum disased-spectrum Clock Output. Our CLKIN.  Clock Range and Dither Rate Select Description section for details.  CRSEL  0 | abled (not a bypass mode).  tputs a center-dithered spread-spection.  Three-level input that determines  CLKIN RANGE  66MHz to 134MHz | the dither rate. See the <i>Detailed</i> DITHER RATE  f <sub>IN</sub> /2048 |  |  |

### **Detailed Description**

The DS1081L modulates an input clock to generate a center-dithered spread-spectrum output. A 20MHz to 134MHz clock is applied to the CLKIN pin. An internal PLL dithers the output clock about its center frequency at a user-selectable magnitude.

### **Spread-Spectrum Dither Magnitude**

The DS1081L can generate dither magnitudes up to ±2%. The desired magnitude is selected using input pins SMSEL1 and SMSEL2 as shown in Table 1.

Table 1.

| SMSEL2 | SMSEL1 | MAGNITUDE |  |

|--------|--------|-----------|--|

| 0      | 0      | ±2.0%     |  |

| 0      | 1      | ±1.5%     |  |

| 1      | 0      | ±1.0%     |  |

| 1      | 1      | ±0.5%     |  |

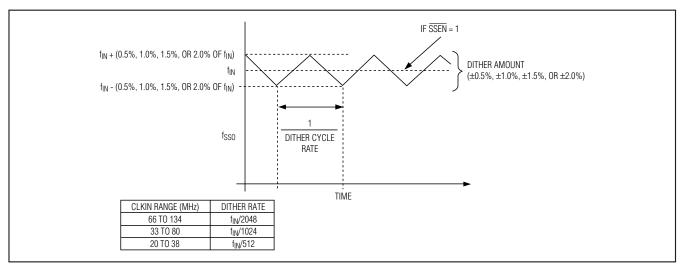

### **Spread-Spectrum Dither Rate**

The output spread-spectrum dither rate is determined by the input frequency to maximize EMI reduction and to ensure that the dither rate is always above the audio frequency range. The user must configure CRSEL, based on Table 2, depending on the input frequency (fin) so that the appropriate dither rate is programmed.

Table 2.

| CRSEL | CLKIN RANGE     | DITHER RATE           |

|-------|-----------------|-----------------------|

| 0     | 66MHz to 134MHz | f <sub>IN</sub> /2048 |

| Float | 33MHz to 80MHz  | f <sub>IN</sub> /1024 |

| 1     | 20MHz to 38MHz  | fini/512              |

### Spread-Spectrum Enable

On power-up, the output clock (SSO) remains tri-stated until the internal PLL reaches a stable frequency. The SSEN input can be used to disable the spread-spectrum modulation and to tri-state the SSO output. If the SSEN pin is pulled high, the spread-spectrum modulation is turned off, but the device still uses the internal PLL to generate the clock signal at SSO. If the SSEN pin is floated, the output will be tri-stated.

### **Application Information**

### **Power-Supply Decoupling**

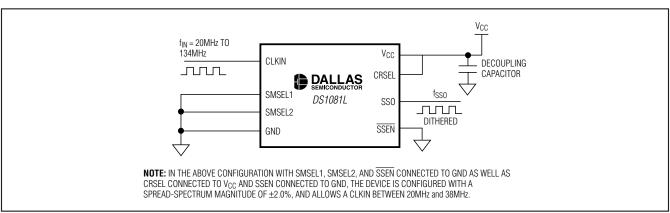

To achieve best results, it is highly recommended that a decoupling capacitor is used on the IC power-supply pins. Typical values of decoupling capacitors are  $0.01\mu F$  and  $0.1\mu F$ . Use a high-quality, ceramic, surface-mount capacitor, and mount it as close as possible to the V<sub>CC</sub> and GND pins of the IC to minimize lead inductance.

Figure 1. DS1081L Spread-Spectrum Frequency Modulation

### **Typical Operating Circuit**

### **Package Information**

For the latest package outline information, go to www.maxim-ic.com/DallasPackInfo.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

\_\_\_\_ 5

© 2007 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.

▶ DALLAS is a registered trademark of Dallas Semiconductor Corporation.