#

## ULTRA MOBILE PC CLOCK FOR EMBEDDED APPLICATIONS

## ICS9EMS9633

## **Recommended Application:**

Poulsbo Based Ultra-Mobile PC (UMPC) for Embedded Applications

## **Output Features:**

- 3 CPU low power differential push-pull pairs

- 3 SRC low power differential push-pull pairs

- 1 LCD100 SSCD low power differential push-pull pair

- 1 DOT96 low power differential push-pull pair

- 1 REF, 14.31818MHz, 3.3V SE output

## Features/Benefits:

- Industrial temperature range compliant

- Supports ULV CPUs with 67 to 167 MHz CPU outputs

- Dedicated TEST/SEL and TEST/MODE pins saves isolation resistors on pins

- CPU STOP# input for power manangment

- Fully integrated Vreg

- Integrated series resistors on differential outputs

- 1.5V VDD IO operation, 3.3V VDD core and REF supply pin for REF

- -40 to +85C operating range

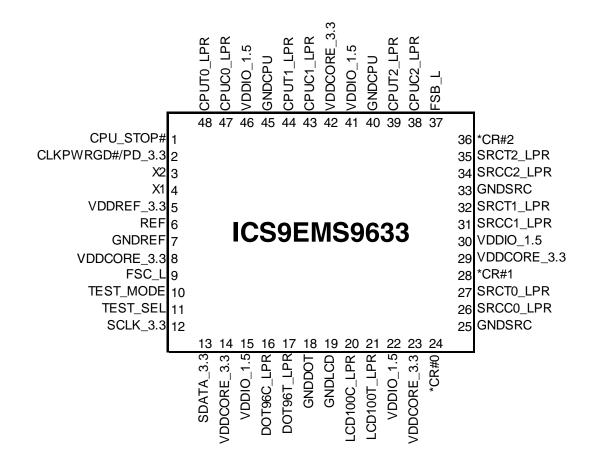

| -           |             |              |                  |

|-------------|-------------|--------------|------------------|

| REF         | 1           | 48           | VDDREF_3.3       |

| GNDREF      | 2           | 47           | X1               |

| VDDCORE_3.3 | 3           | 46           | X2               |

| FSC_L       | 4           | 45           | CLKPWRGD#/PD_3.3 |

| TEST_MODE   | 5           | 44           | CPU_STOP#        |

| TEST_SEL    | 6           | 43           | CPUT0_LPR        |

| SCLK        | 7           | 42           | CPUC0_LPR        |

| SDATA       | 8           | 41           | VDDIO_1.5        |

| VDDCORE_3.3 | 9 <b>C</b>  | <b>Y</b> 40  | GNDCPU           |

| VDDIO_1.5   | 10 <b>Ç</b> |              | CPUT1_LPR        |

| DOT96C_LPR  | 11 9        | <b>O</b> 38  | CPUC1_LPR        |

| DOT96T_LPR  | 12          | 37           | VDDCORE_3.3      |

| GNDDOT      | 13          | <u> </u>     | VDDIO_1.5        |

| GNDLCD      | 14 🧧        | ≥ 35<br>□ 34 | GNDCPU           |

| LCD100C_LPR |             |              | CPUT2_LPR        |

| LCD100T_LPR | 16 <b>C</b> | <b>ア</b> 33  | CPUC2_LPR        |

| VDDIO_1.5   | 17          | 32           | FSB_L            |

| VDDCORE_3.3 | 18          | 31           | *CR#2            |

| *CR#0       | 19          | 30           | SRCT2_LPR        |

| GNDSRC      | 20          | 29           | SRCC2_LPR        |

| SRCC0_LPR   | 21          | 28           | GNDSRC           |

| SRCT0_LPR   | 22          | 27           | SRCT1_LPR        |

| *CR#1       | 23          | 26           | SRCC1_LPR        |

| VDDCORE_3.3 | 24          | 25           | VDDIO_1.5        |

|             |             |              |                  |

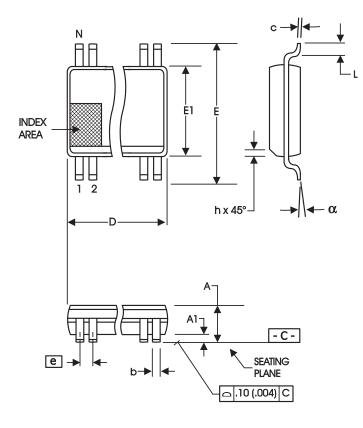

48 SSOP Package

\* indicates inputs with internal pull up of ~10Kohm to 3.3V

IDT<sup>™</sup>/ICS<sup>™</sup> Ultra Mobile PC Clock for Embedded Applications

## SSOP Pin Configuration

## **SSOP Pin Description**

| PIN # | PIN NAME    | TYPE | DESCRIPTION                                                                         |

|-------|-------------|------|-------------------------------------------------------------------------------------|

| 1     | REF         | OUT  | 14.318 MHz reference clock.                                                         |

| 2     | GNDREF      | PWR  | Ground pin for the REF outputs.                                                     |

| 3     | VDDCORE_3.3 | PWR  | 3.3V power for the PLL core                                                         |

| 4     | FSC_L       | IN   | Low threshold input for CPU frequency selection. Refer to input electrical          |

| 4     | F30_L       |      | characteristics for Vil_FS and Vih_FS values.                                       |

| 5     | TEST_MODE   | IN   | TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode        |

|       |             |      | while in test mode. Refer to Test Clarification Table.                              |

|       |             |      | TEST_SEL: latched input to select TEST MODE                                         |

| 6     | TEST_SEL    | IN   | 1 = All outputs are tri-stated for test                                             |

|       |             |      | 0 = All outputs behave normally.                                                    |

| 7     | SCLK        | IN   | Clock pin of SMBus circuitry, 5V tolerant.                                          |

| 8     | SDATA       | I/O  | Data pin for SMBus circuitry, 3.3V tolerant.                                        |

| 9     | VDDCORE_3.3 | PWR  | 3.3V power for the PLL core                                                         |

| 10    | VDDIO_1.5   | PWR  | Power supply for low power differential outputs, nominal 1.5V.                      |

| 11    | DOT96C_LPR  | Ουτ  | Complement clock of low power differential pair for 96.00MHz DOT clock. No 50ohm    |

|       |             |      | resistor to GND needed. No Rs needed.                                               |

| 12    | DOT96T_LPR  | ОЛТ  | True clock of low power differential pair for 96.00MHz DOT clock. No 50ohm resistor |

| 12    |             | 001  | to GND needed. No Rs needed.                                                        |

| 13    | GNDDOT      | PWR  | Ground pin for DOT clock output                                                     |

| 14    | GNDLCD      | PWR  | Ground pin for LCD clock output                                                     |

| 15    | LCD100C LPR | OUT  | Complement clock of low power differential pair for LCD100 SS clock. No 50ohm       |

| 15    |             | 001  | resistor to GND needed. No Rs needed.                                               |

| 16    | LCD100T_LPR | OUT  | True clock of low power differential pair for LCD100 SS clock. No 50ohm resistor to |

| 10    |             | 001  | GND needed. No Rs needed.                                                           |

| 17    | VDDIO_1.5   | PWR  | Power supply for low power differential outputs, nominal 1.5V.                      |

| 18    | VDDCORE_3.3 | PWR  | 3.3V power for the PLL core                                                         |

| 19    | *CR#0       | IN   | Clock request for SRC0, 0 = enable, 1 = disable                                     |

| 20    | GNDSRC      | PWR  | Ground pin for the SRC outputs                                                      |

| 21    | SRCC0_LPR   | OUT  | Complementary clock of differential 0.8V push-pull SRC output with integrated 33ohm |

| 21    |             | 001  | series resistor. No 500hm resistor to GND needed.                                   |

| 22    | SRCT0_LPR   | OUT  | True clock of differential 0.8V push-pull SRC output with integrated 33ohm series   |

| ~~    |             | 001  | resistor. No 500hm resistor to GND needed.                                          |

| 23    | *CR#1       | IN   | Clock request for SRC1, 0 = enable, 1 = disable                                     |

| 24    | VDDCORE_3.3 | PWR  | 3.3V power for the PLL core                                                         |

## **SSOP Pin Description (continued)**

| PIN # | PIN NAME         | TYPE | DESCRIPTION                                                                           |

|-------|------------------|------|---------------------------------------------------------------------------------------|

| 25    | VDDIO_1.5        | PWR  | Power supply for low power differential outputs, nominal 1.5V.                        |

| 26    | SRCC1_LPR        | OUT  | Complementary clock of differential 0.8V push-pull SRC output with integrated 33ohm   |

| 26    | SRCC1_LPR        | 001  | series resistor. No 500hm resistor to GND needed.                                     |

| 07    |                  | OUT  | True clock of differential 0.8V push-pull SRC output with integrated 33ohm series     |

| 27    | SRCT1_LPR        | 001  | resistor. No 50ohm resistor to GND needed.                                            |

| 28    | GNDSRC           | PWR  | Ground pin for the SRC outputs                                                        |

| 29    | SRCC2_LPR        | OUT  | Complementary clock of differential 0.8V push-pull SRC output with integrated 33ohm   |

| 29    | Shoo2_lph        | 001  | series resistor. No 500hm resistor to GND needed.                                     |

| 20    |                  | OUT  | True clock of differential 0.8V push-pull SRC output with integrated 33ohm series     |

| 30    | SRCT2_LPR        | 001  | resistor. No 50ohm resistor to GND needed.                                            |

| 31    | *CR#2            | IN   | Clock request for SRC2, 0 = enable, 1 = disable                                       |

| 20    | FSB_L            | IN   | Low threshold input for CPU frequency selection. Refer to input electrical            |

| 32    | F3D_L            | IIN  | characteristics for Vil_FS and Vih_FS values.                                         |

| 33    | CPUC2_LPR        | OUT  | Complementary clock of differential pair 0.8V push-pull CPU outputs with integrated   |

| 33    | CFUC2_LFN        | 001  | 33ohm series resistor. No 50 ohm resistor to GND needed.                              |

| 34    | CPUT2_LPR        | OUT  | True clock of differential pair 0.8V push-pull CPU outputs with integrated 330hm      |

| 34    | CF012_LFR        | 001  | series resistor. No 50 ohm resistor to GND needed.                                    |

| 35    | GNDCPU           | PWR  | Ground pin for the CPU outputs                                                        |

| 36    | VDDIO_1.5        | PWR  | Power supply for low power differential outputs, nominal 1.5V.                        |

| 37    | VDDCORE_3.3      | PWR  | 3.3V power for the PLL core                                                           |

| 38    | CPUC1_LPR        | OUT  | Complementary clock of differential pair 0.8V push-pull CPU outputs with integrated   |

| 30    | CFUCI_LFN        | 001  | 33ohm series resistor. No 50 ohm resistor to GND needed.                              |

| 39    | CPUT1_LPR        | OUT  | True clock of differential pair 0.8V push-pull CPU outputs with integrated 330hm      |

| 39    | CFOTT_EFR        | 001  | series resistor. No 50 ohm resistor to GND needed.                                    |

| 40    | GNDCPU           | PWR  | Ground pin for the CPU outputs                                                        |

| 41    | VDDIO_1.5        | PWR  | Power supply for low power differential outputs, nominal 1.5V.                        |

| 42    | CPUC0_LPR        | OUT  | Complementary clock of differential pair 0.8V push-pull CPU outputs with integrated   |

| 72    |                  | 001  | 33ohm series resistor. No 50 ohm resistor to GND needed.                              |

| 43    | CPUT0_LPR        | OUT  | True clock of differential pair 0.8V push-pull CPU outputs with integrated 33ohm      |

| -0    |                  | 001  | series resistor. No 50 ohm resistor to GND needed.                                    |

| 44    | CPU_STOP#        | IN   | Stops all CPU clocks, except those set to be free running clocks                      |

|       |                  |      | This 3.3V LVTTL input is a level sensitive strobe used to determine when latch inputs |

| 45    | CLKPWRGD#/PD_3.3 | IN   | are valid and are ready to be sampled. This is an active low input. / Asynchronous    |

| ru    |                  |      | active high input pin used to place the device into a power down state.               |

|       |                  |      |                                                                                       |

| 46    | X2               | OUT  | Crystal output, Nominally 14.318MHz                                                   |

| 47    | X1               | IN   | Crystal input, Nominally 14.318MHz.                                                   |

| 48    | VDDREF_3.3       | PWR  | Power pin for the XTAL and REF clocks, nominal 3.3V                                   |

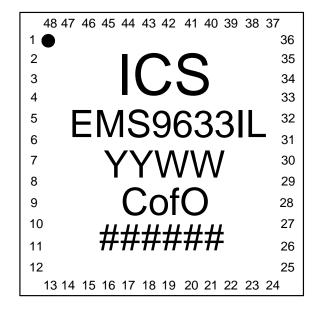

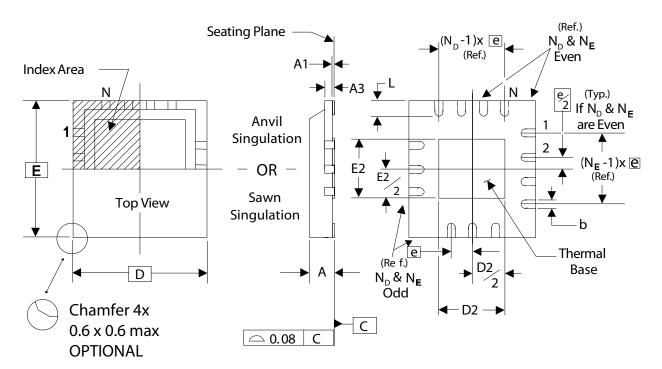

## **MLF Pin Configuration**

#### 48-pin MLF, 6x6 mm, 0.4mm pitch

\* indicates inputs with internal pull up of ~10Kohm to 3.3V

## **MLF Pin Description**

| PIN # | PIN NAME         | TYPE | DESCRIPTION                                                                                                                                                                                                                                      |

|-------|------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CPU_STOP#        | IN   | Stops all CPU clocks, except those set to be free running clocks                                                                                                                                                                                 |

| 2     | CLKPWRGD#/PD_3.3 | IN   | This 3.3V LVTTL input is a level sensitive strobe used to determine when latch inputs are valid and are ready to be sampled. This is an active low input. / Asynchronous active high input pin used to place the device into a power down state. |

| 3     | X2               | OUT  | Crystal output, Nominally 14.318MHz                                                                                                                                                                                                              |

| 4     | X1               | IN   | Crystal input, Nominally 14.318MHz.                                                                                                                                                                                                              |

| 5     | VDDREF_3.3       | PWR  | Power pin for the XTAL and REF clocks, nominal 3.3V                                                                                                                                                                                              |

| 6     | REF              | OUT  | 14.318 MHz reference clock.                                                                                                                                                                                                                      |

| 7     | GNDREF           | PWR  | Ground pin for the REF outputs.                                                                                                                                                                                                                  |

| 8     | VDDCORE_3.3      | PWR  | 3.3V power for the PLL core                                                                                                                                                                                                                      |

| 9     | FSC_L            | IN   | Low threshold input for CPU frequency selection. Refer to input electrical characteristics for Vil_FS and Vih_FS values.                                                                                                                         |

| 10    | TEST_MODE        | IN   | TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer to Test Clarification Table.                                                                                                              |

| 11    | TEST_SEL         | IN   | TEST_SEL: latched input to select TEST MODE<br>1 = All outputs are tri-stated for test<br>0 = All outputs behave normally.                                                                                                                       |

| 12    | SCLK_3.3         | IN   | Clock pin of SMBus circuitry, 3.3V tolerant.                                                                                                                                                                                                     |

| 13    | SDATA_3.3        | I/O  | Data pin for SMBus circuitry, 3.3V tolerant.                                                                                                                                                                                                     |

| 14    | VDDCORE_3.3      | PWR  | 3.3V power for the PLL core                                                                                                                                                                                                                      |

| 15    | VDDIO_1.5        | PWR  | Power supply for low power differential outputs, nominal 1.5V.                                                                                                                                                                                   |

| 16    | DOT96C_LPR       | OUT  | Complement clock of low power differential pair for 96.00MHz DOT clock. No 50ohm resistor to GND needed. No Rs needed.                                                                                                                           |

| 17    | DOT96T_LPR       | OUT  | True clock of low power differential pair for 96.00MHz DOT clock. No 500hm resistor to GND needed. No Rs needed.                                                                                                                                 |

| 18    | GNDDOT           | PWR  | Ground pin for DOT clock output                                                                                                                                                                                                                  |

| 19    | GNDLCD           | PWR  | Ground pin for LCD clock output                                                                                                                                                                                                                  |

| 20    | LCD100C_LPR      | OUT  | Complement clock of low power differential pair for LCD100 SS clock. No 50ohm resistor to GND needed. No Rs needed.                                                                                                                              |

| 21    | LCD100T_LPR      | OUT  | True clock of low power differential pair for LCD100 SS clock. No 50ohm resistor to GND needed. No Rs needed.                                                                                                                                    |

| 22    | VDDIO_1.5        | PWR  | Power supply for low power differential outputs, nominal 1.5V.                                                                                                                                                                                   |

| 23    | VDDCORE_3.3      | PWR  | 3.3V power for the PLL core                                                                                                                                                                                                                      |

| 24    | *CR#0            | IN   | Clock request for SRC0, 0 = enable, 1 = disable                                                                                                                                                                                                  |

## **MLF Pin Description (continued)**

| PIN # | PIN NAME    | TYPE | DESCRIPTION                                                                         |

|-------|-------------|------|-------------------------------------------------------------------------------------|

| 25    | GNDSRC      | PWR  | Ground pin for the SRC outputs                                                      |

| 26    | SRCC0_LPR   | OUT  | Complementary clock of differential 0.8V push-pull SRC output with integrated 33ohm |

| 26    | SRCCU_LPR   | 001  | series resistor. No 500hm resistor to GND needed.                                   |

| 27    | SRCT0_LPR   | OUT  | True clock of differential 0.8V push-pull SRC output with integrated 33ohm series   |

| 21    | SHCTU_LFH   | 001  | resistor. No 500hm resistor to GND needed.                                          |

| 28    | *CR#1       | IN   | Clock request for SRC1, 0 = enable, 1 = disable                                     |

| 29    | VDDCORE_3.3 | PWR  | 3.3V power for the PLL core                                                         |

| 30    | VDDIO_1.5   | PWR  | Power supply for low power differential outputs, nominal 1.5V.                      |

| 31    | SRCC1_LPR   | OUT  | Complementary clock of differential 0.8V push-pull SRC output with integrated 33ohm |

| 51    | SHOOT_EFN   | 001  | series resistor. No 500hm resistor to GND needed.                                   |

| 32    | SRCT1_LPR   | OUT  | True clock of differential 0.8V push-pull SRC output with integrated 33ohm series   |

| 32    | SHOTT_LFR   | 001  | resistor. No 500hm resistor to GND needed.                                          |

| 33    | GNDSRC      | PWR  | Ground pin for the SRC outputs                                                      |

| 34    | SRCC2_LPR   | OUT  | Complementary clock of differential 0.8V push-pull SRC output with integrated 33ohm |

| 34    | Shooz_LFh   | 001  | series resistor. No 500hm resistor to GND needed.                                   |

| 35    | SRCT2_LPR   | OUT  | True clock of differential 0.8V push-pull SRC output with integrated 33ohm series   |

| 35    | ShC12_LFN   | 001  | resistor. No 50ohm resistor to GND needed.                                          |

| 36    | *CR#2       | IN   | Clock request for SRC2, 0 = enable, 1 = disable                                     |

| 37    | FSB_L       | IN   | Low threshold input for CPU frequency selection. Refer to input electrical          |

| 37    | F3D_L       |      | characteristics for Vil_FS and Vih_FS values.                                       |

| 38    | CPUC2_LPR   | OUT  | Complementary clock of differential pair 0.8V push-pull CPU outputs with integrated |

| 30    | CF0C2_LFN   | 001  | 33ohm series resistor. No 50 ohm resistor to GND needed.                            |

| 39    | CPUT2_LPR   | OUT  | True clock of differential pair 0.8V push-pull CPU outputs with integrated 33ohm    |

| 39    | CF012_LFR   | 001  | series resistor. No 50 ohm resistor to GND needed.                                  |

| 40    | GNDCPU      | PWR  | Ground pin for the CPU outputs                                                      |

| 41    | VDDIO_1.5   | PWR  | Power supply for low power differential outputs, nominal 1.5V.                      |

| 42    | VDDCORE_3.3 | PWR  | 3.3V power for the PLL core                                                         |

| 43    | CPUC1_LPR   | OUT  | Complementary clock of differential pair 0.8V push-pull CPU outputs with integrated |

| 43    | CFUCI_LFN   | 001  | 33ohm series resistor. No 50 ohm resistor to GND needed.                            |

| 44    | CPUT1_LPR   | OUT  | True clock of differential pair 0.8V push-pull CPU outputs with integrated 33ohm    |

| 44    | CFOTT_EFR   | 001  | series resistor. No 50 ohm resistor to GND needed.                                  |

| 45    | GNDCPU      | PWR  | Ground pin for the CPU outputs                                                      |

| 46    | VDDIO_1.5   | PWR  | Power supply for low power differential outputs, nominal 1.5V.                      |

| 47    | CPUC0 LPR   | OUT  | Complementary clock of differential pair 0.8V push-pull CPU outputs with integrated |

| 47    |             | 001  | 33ohm series resistor. No 50 ohm resistor to GND needed.                            |

| 48    | CPUT0 LPR   | OUT  | True clock of differential pair 0.8V push-pull CPU outputs with integrated 33ohm    |

| 40    |             | 001  | series resistor. No 50 ohm resistor to GND needed.                                  |

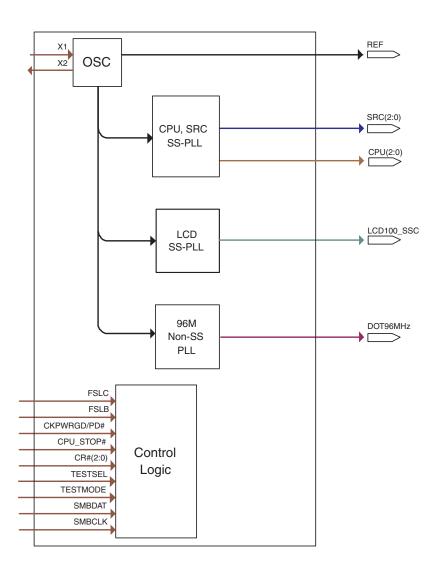

## **Funtional Block Diagram**

## **Power Groups**

| Pin N  | umber  | Description |                   |  |  |  |

|--------|--------|-------------|-------------------|--|--|--|

| VDD    | GND    | Description |                   |  |  |  |

| 41, 46 | 40, 45 | CPUCLK      | Low power outputs |  |  |  |

| 42     | 40, 45 | CFUCLK      | VDDCORE_3.3V      |  |  |  |

| 30     | 25, 33 | SRCCLK      | Low power outputs |  |  |  |

| 29     |        | SHOOLK      | VDDCORE_3.3V      |  |  |  |

| 22     | 19     | LCDCLK      | Low power outputs |  |  |  |

| 23     | 19     | LODOLK      | VDDCORE_3.3V      |  |  |  |

| 15     | 18     | DOT 96Mhz   | Low power outputs |  |  |  |

| 14     | 10     | DOT 90MINZ  | VDDCORE_3.3V      |  |  |  |

| 5      | 7      | Xtal, REF   |                   |  |  |  |

IDT<sup>™</sup>/ICS<sup>™</sup> Ultra Mobile PC Clock for Embedded Applications

Downloaded from Elcodis.com electronic components distributor

## **Absolute Maximum Ratings**

| PARAMETER              | SYMBOL             | CONDITIONS        | MIN       | MAX              | UNITS | Notes |

|------------------------|--------------------|-------------------|-----------|------------------|-------|-------|

| 3.3V Supply Voltage    | VDDxxx_3.3         | Supply Voltage    |           | 3.9              | V     | 1,2   |

| 1.5V Supply Voltage    | VDDxxx_1.5         | Supply Voltage    |           | 3.9              | V     | 1,2   |

| 3.3_Input High Voltage | V <sub>IH3.3</sub> | 3.3V Inputs       |           | VDD_3.3+<br>0.3V | V     | 1,2,3 |

| Minimum Input Voltage  | V <sub>IL</sub>    | Any Input         | GND - 0.5 |                  | V     | 1     |

| Storage Temperature    | Ts                 | -                 | -65       | 150              | °C    | 1,2   |

| Input ESD protection   | ESD prot           | Human Body Model  | 2000      |                  | V     | 1,2   |

|                        | LOD prot           | Man Machine Model | 200       |                  | V     | 1,2   |

#### Notes:

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Operation under these conditions is neither implied, nor guaranteed.

<sup>3</sup> Maximum input voltage is not to exceed maximum VDD

## **Electrical Characteristics - Input/Supply/Common Output Parameters**

| PARAMETER                               | SYMBOL                    | CONDITIONS                                                                                                          | MIN                   | MAX                  | UNITS | Notes |

|-----------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|-------|-------|

| Ambient Operating Temp                  | T <sub>ambientITEMP</sub> | No Airflow                                                                                                          | -40                   | 85                   | °C    | 1     |

| 3.3V Supply Voltage                     | VDDxxx_3.3                | 3.3V +/- 5%                                                                                                         | 3.135                 | 3.465                | V     | 1     |

| 1.5V Supply Voltage                     | VDDxxx_1.5                | 1.5V - 5% to 3.3V + 5%                                                                                              | 1.425                 | 3.465                | V     | 1     |

| 3.3V Input High Voltage                 | V <sub>IHSE3.3</sub>      | Single-ended inputs                                                                                                 | 2                     | V <sub>DD</sub> +0.3 | V     | 1     |

| 3.3V Input Low Voltage                  | V <sub>ILSE3.3</sub>      | Single-ended inputs                                                                                                 | V <sub>ss</sub> - 0.3 | 0.8                  | V     | 1     |

| Input Leakage Current                   | I <sub>IN</sub>           | $V_{IN} = V_{DD}$ , $V_{IN} = GND$                                                                                  | -5                    | 5                    | uA    | 1     |

| Input Leakage Current                   | I <sub>INRES</sub>        | Inputs with pull or pull down<br>resistors. (CR# pins)<br>V <sub>IN</sub> = V <sub>DD</sub> , V <sub>IN</sub> = GND | -200                  | 200                  | uA    | 1     |

| Output High Voltage                     | V <sub>OHSE</sub>         | Single-ended outputs, $I_{OH} = -1mA$                                                                               | 2.4                   |                      | V     | 1     |

| Output Low Voltage                      | V <sub>OLSE</sub>         | Single-ended outputs, $I_{OL} = 1 \text{ mA}$                                                                       |                       | 0.4                  | V     | 1     |

| Low Threshold Input-<br>High Voltage    | $V_{\rm IH\_FS}$          | 3.3 V +/-5%                                                                                                         | 0.7                   | 1.5                  | V     | 1     |

| Low Threshold Input-<br>Low Voltage     | $V_{IL_FS}$               | 3.3 V +/-5%                                                                                                         | V <sub>SS</sub> - 0.3 | 0.35                 | V     | 1     |

|                                         | I <sub>DD_DEFAULT</sub>   | 3.3V supply, LCDPLL off                                                                                             |                       | 65                   | mA    | 1     |

| Operating Supply Current                | IDD_LCDEN                 | 3.3V supply, LCDPLL enabled                                                                                         |                       | 70                   | mA    | 1     |

|                                         | I <sub>DD_IO</sub>        | 1.5V supply, Differential IO current,<br>all outputs enabled                                                        |                       | 55                   | mA    | 1     |

|                                         | I <sub>DD_PD3.3</sub>     | 3.3V supply, Power Down Mode                                                                                        |                       | 2                    | mA    | 1     |

| Power Down Current                      | I <sub>DD_PDIO</sub>      | 1.5V IO supply, Power Down Mode                                                                                     |                       | 0.5                  | mA    | 1     |

| Input Frequency                         | F <sub>i</sub>            | $V_{DD} = 3.3 V$                                                                                                    |                       | 15                   | MHz   | 2     |

| Pin Inductance                          | L <sub>pin</sub>          |                                                                                                                     |                       | 7                    | nH    | 1     |

|                                         | C <sub>IN</sub>           | Logic Inputs                                                                                                        | 1.5                   | 5                    | pF    | 1     |

| Input Capacitance                       | C <sub>OUT</sub>          | Output pin capacitance                                                                                              |                       | 6                    | pF    | 1     |

|                                         | C <sub>INX</sub>          | X1 & X2 pins                                                                                                        |                       | 5                    | рF    | 1     |

| Spread Spectrum Modulation<br>Frequency | f <sub>SSMOD</sub>        | Triangular Modulation                                                                                               | 30                    | 33                   | kHz   | 1     |

| PARAMETER         | SYMBOL             | CONDITIONS                                                | MIN | MAX | UNITS | Notes |

|-------------------|--------------------|-----------------------------------------------------------|-----|-----|-------|-------|

| Clk Stabilization | T <sub>STAB</sub>  | From VDD Power-Up or de-<br>assertion of PD# to 1st clock |     | 1.8 | ms    | 1     |

| Tdrive_SRC        | T <sub>DRSRC</sub> | SRC output enable after<br>CR# assertion                  |     | 15  | ns    | 1     |

| Tdrive_PD#        | T <sub>DRPD</sub>  | Differential output enable after<br>PD# de-assertion      |     | 300 | us    | 1     |

| Tdrive_CPU        | T <sub>DRSRC</sub> | CPU output enable after<br>CPU_STOP# de-assertion         |     | 10  | ns    | 1     |

| Tfall_PD#         | T <sub>FALL</sub>  | Fall/rise time of PD# and                                 |     | 5   | ns    | 1     |

| Trise_PD#         | T <sub>RISE</sub>  | CPU_STOP# inputs                                          |     | 5   | ns    | 1     |

## **AC Electrical Characteristics - Input/Common Parameters**

## **AC Electrical Characteristics - Low Power Differential Outputs**

| SYMBOL                | CONDITIONS                                                                                                                                                                                                     | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UNITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>slR</sub>      | Differential Measurement                                                                                                                                                                                       | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V/ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| t <sub>FLR</sub>      | Differential Measurement                                                                                                                                                                                       | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V/ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1,2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| t <sub>slvar</sub>    | Single-ended Measurement                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>HIGH</sub>     | Includes overshoot                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>LOW</sub>      | Includes undershoot                                                                                                                                                                                            | -300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>SWING</sub>    | Differential Measurement                                                                                                                                                                                       | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>XABS</sub>     | Single-ended Measurement                                                                                                                                                                                       | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1,3,4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>XABSVAR</sub>  | Single-ended Measurement                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1,3,5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D <sub>CYC</sub>      | Differential Measurement                                                                                                                                                                                       | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CPUJ <sub>C2C</sub>   | Differential Measurement                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SRCJ <sub>C2C</sub>   | Differential Measurement                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DOTJ <sub>C2C</sub>   | Differential Measurement                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CPU <sub>SKEW10</sub> | Differential Measurement                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SRC <sub>SKEW</sub>   | Differential Measurement                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | $\begin{array}{c} t_{SLR} \\ t_{FLR} \\ t_{SLVAR} \\ V_{HIGH} \\ V_{LOW} \\ V_{SWING} \\ V_{XABS} \\ V_{XABS} \\ V_{XABSVAR} \\ D_{CYC} \\ CPUJ_{C2C} \\ SRCJ_{C2C} \\ DOTJ_{C2C} \\ CPU_{SKEW10} \end{array}$ | t_{SLR} Differential Measurement   t_{FLR} Differential Measurement   t_{SLVAR} Single-ended Measurement   V_HIGH Includes overshoot   V_LOW Includes undershoot   V_SWING Differential Measurement   V_XABS Single-ended Measurement   V_XABS Single-ended Measurement   V_XABS Single-ended Measurement   DCYC Differential Measurement   CPUJ <sub>C2C</sub> Differential Measurement   SRCJ <sub>C2C</sub> Differential Measurement   DOTJ <sub>C2C</sub> Differential Measurement   DOTJ <sub>C2C</sub> Differential Measurement   CPU <sub>SKEW10</sub> Differential Measurement | t<br>SLRDifferential Measurement0.5t<br>FLRDifferential Measurement0.5t<br>SLVARSingle-ended Measurement0.5t<br>SLVARSingle-ended Measurement0.5V<br>HIGHIncludes overshoot0.5V<br>LOWIncludes overshoot-300V<br>SWINGDifferential Measurement300V<br>XABSSingle-ended Measurement300V<br>XABSVARSingle-ended Measurement45CPUJ<br>C2CDifferential Measurement45CPUJ<br>C2CDifferential Measurement0SRCJ<br>C2CDifferential Measurement0DOTJ<br>C2CDifferential Measurement0CPU<br>SKEW10Differential Measurement0 | $t_{SLR}$ Differential Measurement0.56 $t_{FLR}$ Differential Measurement0.56 $t_{FLR}$ Differential Measurement0.56 $t_{SLVAR}$ Single-ended Measurement125 $V_{HIGH}$ Includes overshoot1150 $V_{LOW}$ Includes undershoot-300 $V_{SWING}$ Differential Measurement300 $V_{XABS}$ Single-ended Measurement300 $V_{XABS}$ Single-ended Measurement300 $V_{XABSVAR}$ Single-ended Measurement45 $D_{CYC}$ Differential Measurement45 $D_{CYC}$ Differential Measurement85 $SRCJ_{C2C}$ Differential Measurement125 $DOTJ_{C2C}$ Differential Measurement250 $CPU_{SKEW10}$ Differential Measurement100 | $t_{SLR}$ Differential Measurement0.56V/ns $t_{FLR}$ Differential Measurement0.56V/ns $t_{FLR}$ Differential Measurement0.56V/ns $t_{SLVAR}$ Single-ended Measurement125ps $V_{HIGH}$ Includes overshoot1150mV $V_{LOW}$ Includes undershoot-300mV $V_{SWING}$ Differential Measurement300mV $V_{XABS}$ Single-ended Measurement300550mV $V_{XABS}$ Single-ended Measurement300550mV $V_{XABSVAR}$ Single-ended Measurement4555% $CPUJ_{C2C}$ Differential Measurement4555% $CPUJ_{C2C}$ Differential Measurement125ps $DOTJ_{C2C}$ Differential Measurement250ps $DOTJ_{C2C}$ Differential Measurement100ps |

## **Electrical Characteristics - REF-14.318MHz**

| PARAMETER               | SYMBOL                | CONDITIONS                                                      | MIN     | MAX      | UNITS | Notes |

|-------------------------|-----------------------|-----------------------------------------------------------------|---------|----------|-------|-------|

| Long Accuracy           | ppm                   | see Tperiod min-max values                                      | -300    | 300      | ppm   | 1,2   |

| Clock period            | T <sub>period</sub>   | 14.318MHz output nominal                                        | 69.8203 | 69.8622  | ns    | 2     |

| Absolute min/max period | T <sub>abs</sub>      | 14.318MHz output nominal                                        | 69.8203 | 70.86224 | ns    | 2     |

| Output High Voltage     | V <sub>OH</sub>       | I <sub>он</sub> = -1 mА                                         | 2.4     |          | V     | 1     |

| Output Low Voltage      | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA                                          |         | 0.4      | V     | 1     |

| Output High Current     | I <sub>OH</sub>       | V <sub>OH</sub> @MIN = 1.0 V,<br>V <sub>OH</sub> @MAX = 3.135 V | -33     | -33      | mA    | 1     |

| Output Low Current      | I <sub>oL</sub>       | V <sub>OL</sub> @MIN = 1.95 V,<br>V <sub>OL</sub> @MAX = 0.4 V  | 30      | 38       | mA    | 1     |

| Rising Edge Slew Rate   | t <sub>sLR</sub>      | Measured from 0.8 to 2.0 V                                      | 1       | 4        | V/ns  | 1     |

| Falling Edge Slew Rate  | t <sub>FLR</sub>      | Measured from 2.0 to 0.8 V                                      | 1       | 4        | V/ns  | 1     |

| Duty Cycle              | d <sub>t1</sub>       | V <sub>T</sub> = 1.5 V                                          | 45      | 55       | %     | 1     |

| Jitter                  | t <sub>jcyc-cyc</sub> | V <sub>T</sub> = 1.5 V                                          |         | 1000     | ps    | 1     |

IDT™/ICS™ Ultra Mobile PC Clock for Embedded Applications

| PARAMETER                | SYMBOL             | CONDITIONS            | MIN | MAX  | UNITS | Notes |

|--------------------------|--------------------|-----------------------|-----|------|-------|-------|

| SMBus Voltage            | V <sub>DD</sub>    |                       | 2.7 | 3.3  | V     | 1     |

| Low-level Output Voltage | V <sub>OLSMB</sub> | @ I <sub>PULLUP</sub> |     | 0.4  | V     | 1     |