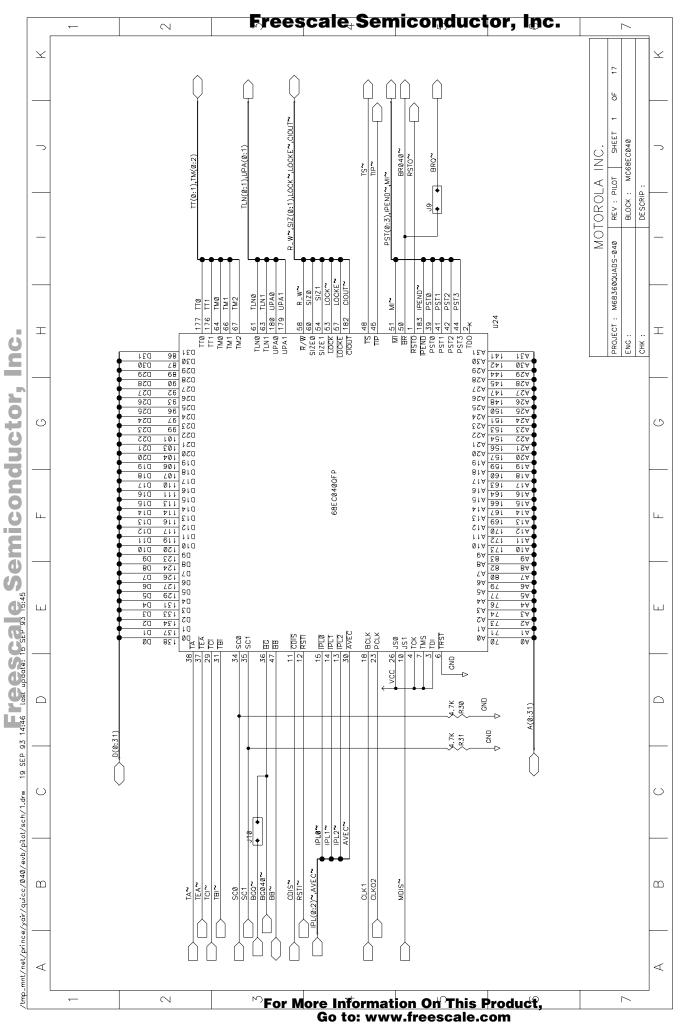

MOTOROLFA eescale Semiconducto nuibace Rocessor & MEMORY TECHNOLOGIES GROUP

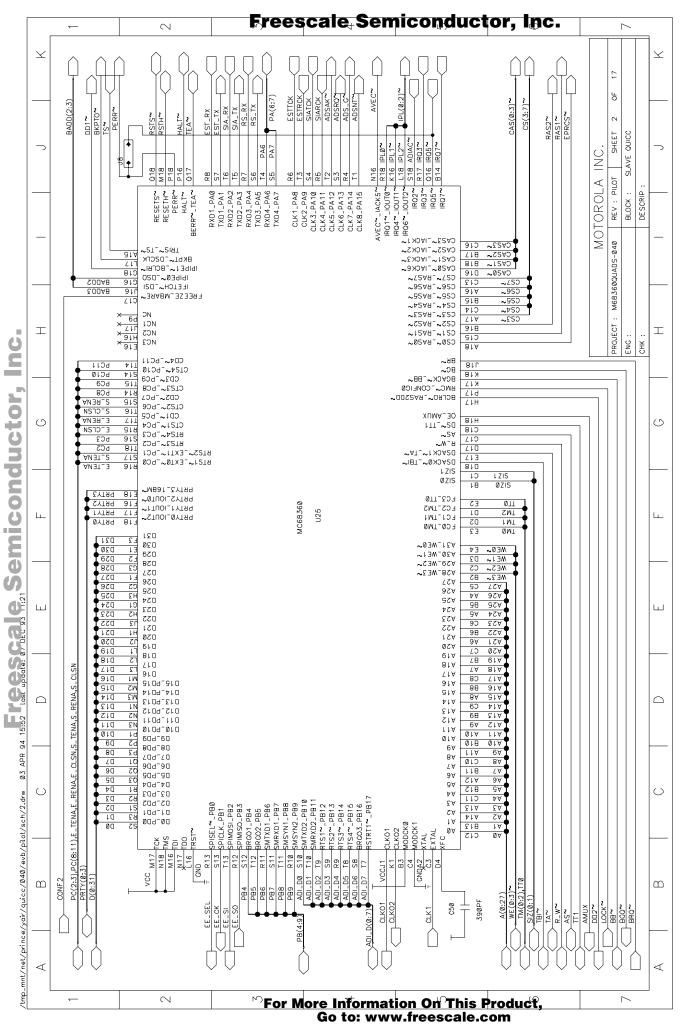

## M68360QUADS-040

## User's Manual

**ISSUE 1.0 - DRAFT**

#### TABLE OF CONTENTS

| 1 - |            |              | GENERAL INFORMATION                           | 7        |

|-----|------------|--------------|-----------------------------------------------|----------|

| •   | 1.1        |              | INTRODUCTION                                  | 7        |

|     | 1.2        |              | RELATED DOCUMENTATION                         | 7        |

|     | 1.3        |              | ABBREVIATIONS USED IN THE DOCUMENT            | 7        |

|     | 1.4        |              | SPECIFICATIONS                                | 7        |

|     | 1.5        |              | COOLING REQUIREMENTS                          | 8        |

|     | 1.6        |              | FEATURES                                      | 9        |

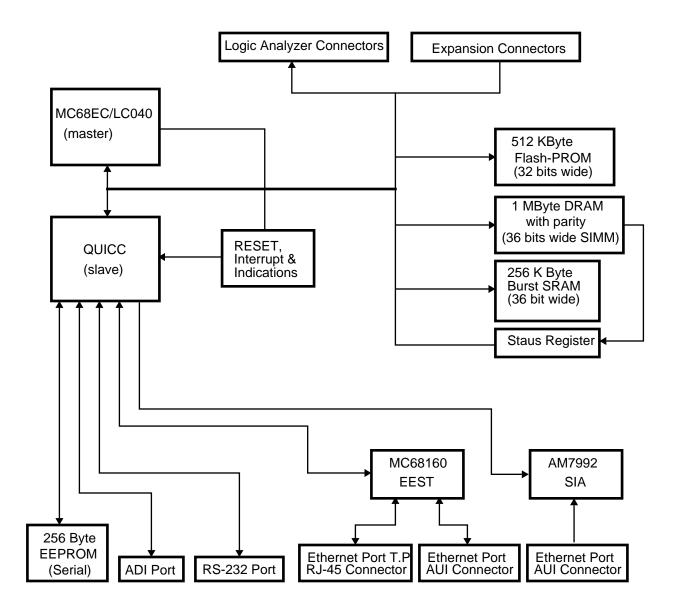

|     | 1.7        |              | HARDWARE BLOCK DIAGRAM                        | 10       |

| 2 - |            |              | Hardware Preparation and Installation         | 11       |

|     | 2.1        |              | INTRODUCTION                                  | 11       |

|     | 2.2        |              | UNPACKING INSTRUCTIONS                        | 11       |

|     | 2.3        |              | HARDWARE PREPARATION                          | 11       |

|     |            | 2.3.1        | ADI Port Address Selection                    | 13       |

|     |            | 2.3.2        | Caches Enable / Disable                       | 14       |

|     |            | 2.3.3        | MMU Enable / Disable                          | 14       |

|     |            | 2.3.4        | Parity Error Interrupt Generation             | 14       |

|     |            | 2.3.5        | Arbitration Configuration                     | 14       |

|     |            | 2.3.6        | EEST Configuration<br>User Selectable Options | 14<br>14 |

|     | 2.4        | 2.3.7        | INSTALLATION INSTRUCTIONS                     | 14       |

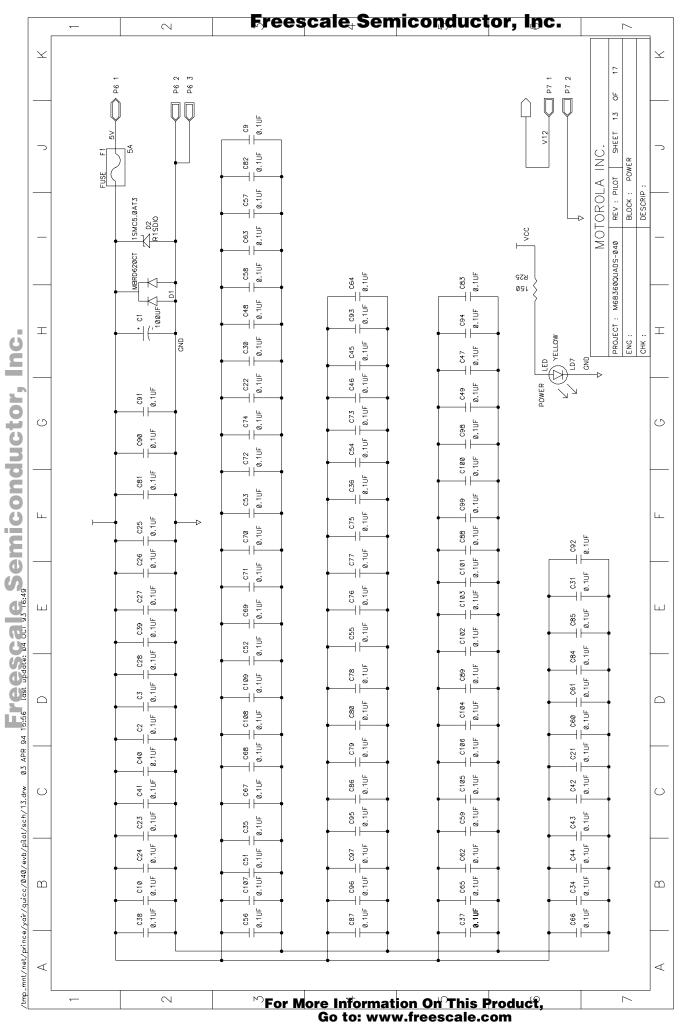

|     | 2.4        | 2.4.1        | +5V Power Supply Connection                   | 14       |

|     |            | 2.4.1        | P7: +12V Power Supply Connection              | 15       |

|     |            | 2.4.3        | ADI Installation                              | 15       |

|     |            | 2.4.4        | Host computer to M68360QUADS-040 Connection   | 15       |

|     |            | 2.4.5        | Terminal to M68360QUADS-040 RS-232 Connection | 16       |

| 3 - |            |              | OPERATING INSTRUCTIONS                        | 17       |

|     | 3.1        |              | INTRODUCTION                                  | 17       |

|     | 3.2        |              | CONTROLS AND INDICATORS                       | 17       |

|     |            | 3.2.1        | SOFT RESET Switch SW1                         | 17       |

|     |            | 3.2.2        | ABORT Switch SW2                              | 17       |

|     |            | 3.2.3        | HARD RESET - Switches SW1 & SW2               | 17       |

|     |            | 3.2.4        | EEST Configuration Jumpers J1 to J6           | 17       |

|     |            | 3.2.         |                                               | 17       |

|     |            |              | 4.2 APORT Jumper - J2                         | 17       |

|     |            | 3.2.         |                                               | 17       |

|     |            | 3.2.         |                                               | 17       |

|     |            | 3.2.<br>3.2. | •                                             | 18<br>18 |

|     |            | 3.2.5        | Hardware Breakpoint Usage Jumper - J7         | 18       |

|     |            | 3.2.5        | Parity Error Interrupt Jumper - J8            | 18       |

|     |            | 3.2.7        | Bus Request Jumper - J9                       | 18       |

|     |            | 3.2.8        | Bus Grant Jumper - J10                        | 18       |

|     |            | 3.2.9        | HALT Indicator - LD10                         | 18       |

|     |            | 3.2.10       | 040RUN Indicator - LD8                        | 18       |

|     |            | 3.2.11       | DMARUN Indicator - LD9                        | 19       |

|     |            | 3.2.12       | Ethernet TX Indicator - LD3                   | 19       |

|     |            | 3.2.13       | Ethernet RX Indicator - LD2                   | 19       |

|     |            | 3.2.14       | Ethernet CLSN Indicator LD4                   | 19       |

|     |            | 3.2.15       | Ethernet LIL Indicator - LD5                  | 19       |

|     |            | 3.2.16       | Ethernet PLR Indicator - LD6                  | 19       |

|     |            | 3.2.17       | Ethernet JABB Indicator - LD1                 | 19       |

|     | <b>~</b> ~ | 3.2.18       | POWER Indicator - LD7                         | 19       |

|     | 3.3        | 0.0.4        | MEMORY MAP                                    | 19       |

|     |            | 3.3.1        | Main Memory Map                               | 20       |

#### **TABLE OF CONTENTS**

|     | <b>.</b> (       |                                                                     |          |

|-----|------------------|---------------------------------------------------------------------|----------|

|     | 3.4              | Programming the slave QUICC                                         | 21       |

|     | 3.4.1            | Module Base Address Register                                        | 21       |

|     | 3.4.2            | Module Configuration Register                                       | 21       |

|     | 3.4.3            | CLKO Control Register                                               | 21       |

|     | 3.4.4            | PLL Control Register                                                | 21       |

|     | 3.4.5            | Port E Pin Assignment Register                                      | 21       |

|     | 3.4.6            | System Protection Control                                           | 21       |

|     | 3.4.7            | Global Memory Register                                              | 22       |

|     | 3.4.8            | Base Register 0 and Option Register 0                               | 22       |

|     | 3.4.9            | Base Register 1 and Option Register 1                               | 22       |

|     | 3.4.10           | Base Register 2 and Option Register 2                               | 23       |

|     | 3.4.11           | Base Register 3 and Option Register 3                               | 23       |

|     | 3.4.12           | Base Register 4 and Option Register 4                               | 23       |

|     | 3.4.13           | Base Register 5 and Option Register 5                               | 24       |

|     | 3.4.14<br>3.4.15 | Base Register 6 and Option Register 6                               | 24<br>24 |

|     | 3.4.15<br>3.4.16 | Base Register 7 and Option Register 7<br>Port A Open Drain Register | 24       |

|     | 3.4.10           | Port A Data Register                                                | 24       |

|     | 3.4.17           | Port A Data Direction Register                                      | 24       |

|     | 3.4.10           | Port A Pin Assignment Register                                      | 24       |

|     | 3.4.20           | Port B Open Drain Register                                          | 24       |

|     | 3.4.21           | Port B Data Register                                                | 24       |

|     | 3.4.22           | Port B Data Direction Register                                      | 25       |

|     | 3.4.23           | Port B Pin Assignment Register                                      | 25       |

|     | 3.4.24           | Port C Data Register                                                | 25       |

|     | 3.4.25           | Port C Data Direction Register                                      | 25       |

|     | 3.4.26           | Port C Pin Assignment Register                                      | 25       |

|     | 3.4.27           | Port C Special Options Register                                     | 25       |

| 4 - |                  | FUNCTIONAL DESCRIPTION                                              | 26       |

|     | 4.1              | INTRODUCTION                                                        | 26       |

|     | 4.2              | Master MC68EC040                                                    | 26       |

|     | 4.2.1            | RESET for the 68EC040 & the QUICC                                   | 26       |

|     | 4.2.2            | Utilizing the MC68EC040 Data Cache                                  | 27       |

|     | 4.3              | Interrupts on the M68360QUADS-040                                   | 27       |

|     | 4.3.1            | ABORT Push-button                                                   | 27       |

|     | 4.3.2            | Host - NMI                                                          | 28       |

|     | 4.3.3            | Hardware-Breakpoint Interrupt                                       | 28       |

|     | 4.3.4            | Parity Error Interrupt                                              | 28       |

|     | 4.3.5            | Host Request / Acknowledge Interrupt                                | 28       |

|     | 4.4              | Bus Arbitration                                                     | 28       |

|     | 4.5              | System Utilities                                                    | 29       |

|     | 4.5.1            | Breakpoints Generator                                               | 29       |

|     | 4.5.2            | Bus Monitor                                                         | 29       |

|     | 4.5.3            | Spurious Interrupt Monitor                                          | 30       |

|     | 4.5.4            | software Watch-Dog                                                  | 30       |

|     | 4.5.5            | Periodic Interval Timer - PIT                                       | 30       |

|     | 4.6              | Clock Generator                                                     | 30       |

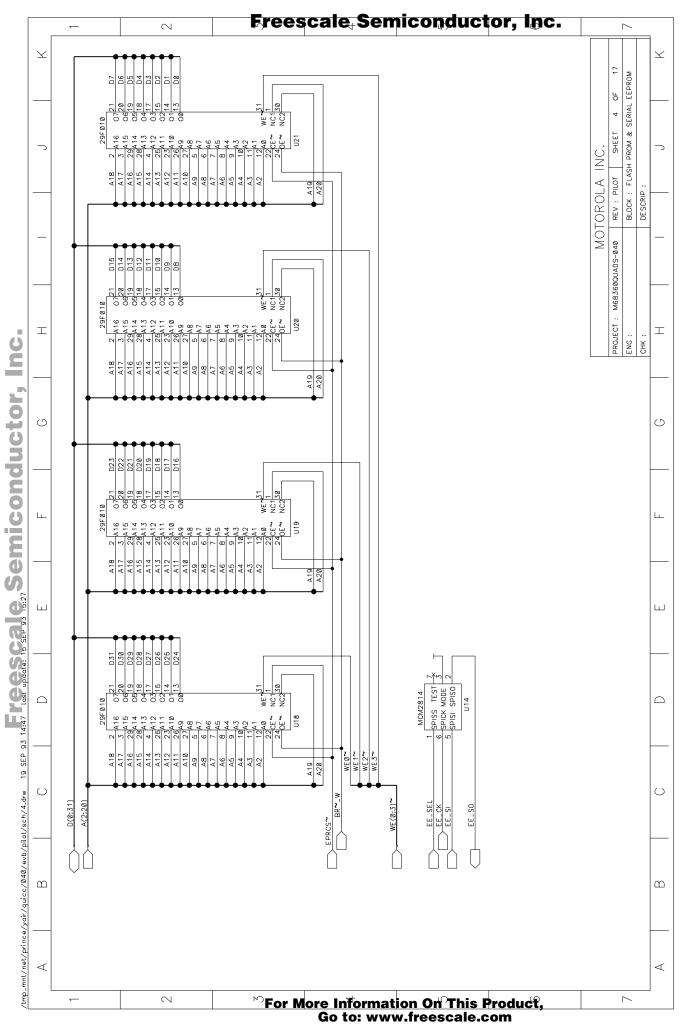

|     | 4.7              | Flash PROM                                                          | 30       |

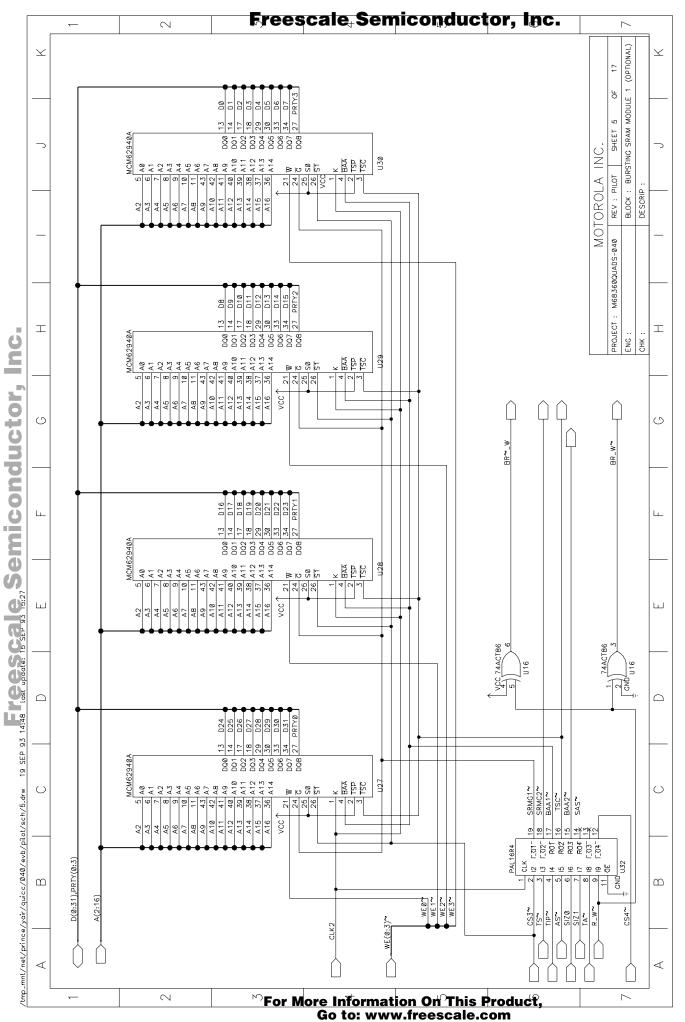

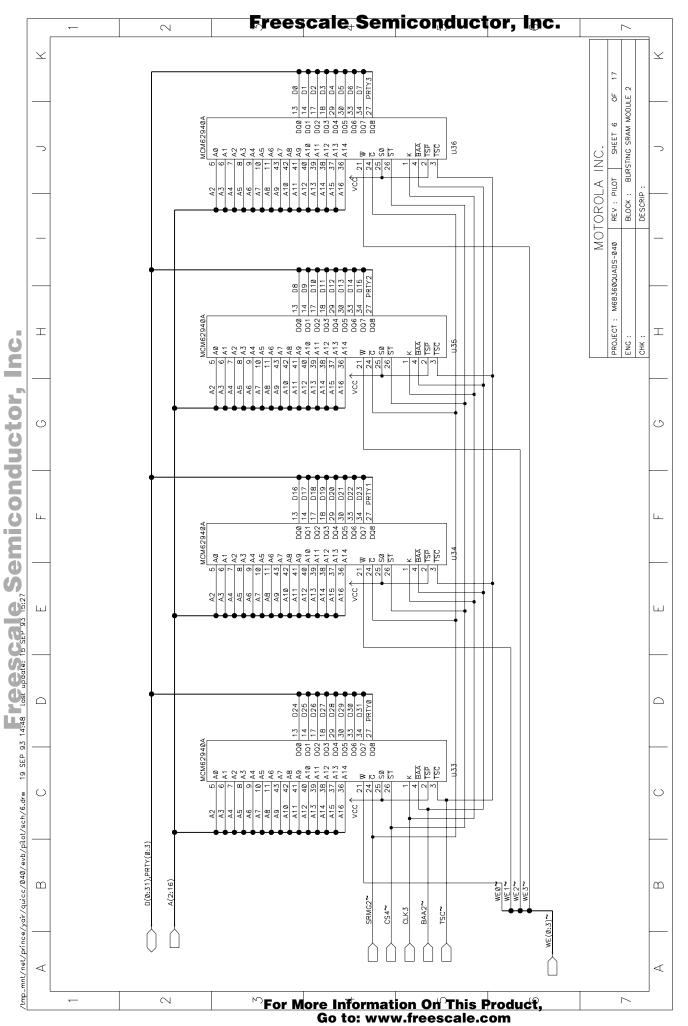

|     | 4.8              | Bursting SRAM                                                       | 30       |

|     | 4.9              | EEPROM                                                              | 31       |

|     | 4.10             | DRAM                                                                | 31       |

|     | 4.11             | Slave QUICC                                                         | 31       |

|     | 4.11.1           | DRAM Controller                                                     | 32       |

#### For More Information On This Product, Go to: www.freescale.com

#### **TABLE OF CONTENTS**

|            | 4.11.2               | Chip Select TA~ and DSACK~ Generator                                | 32       |

|------------|----------------------|---------------------------------------------------------------------|----------|

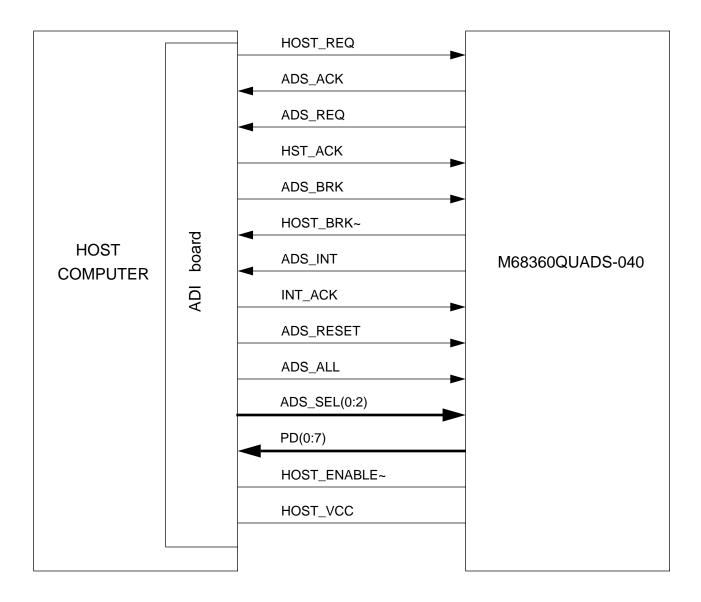

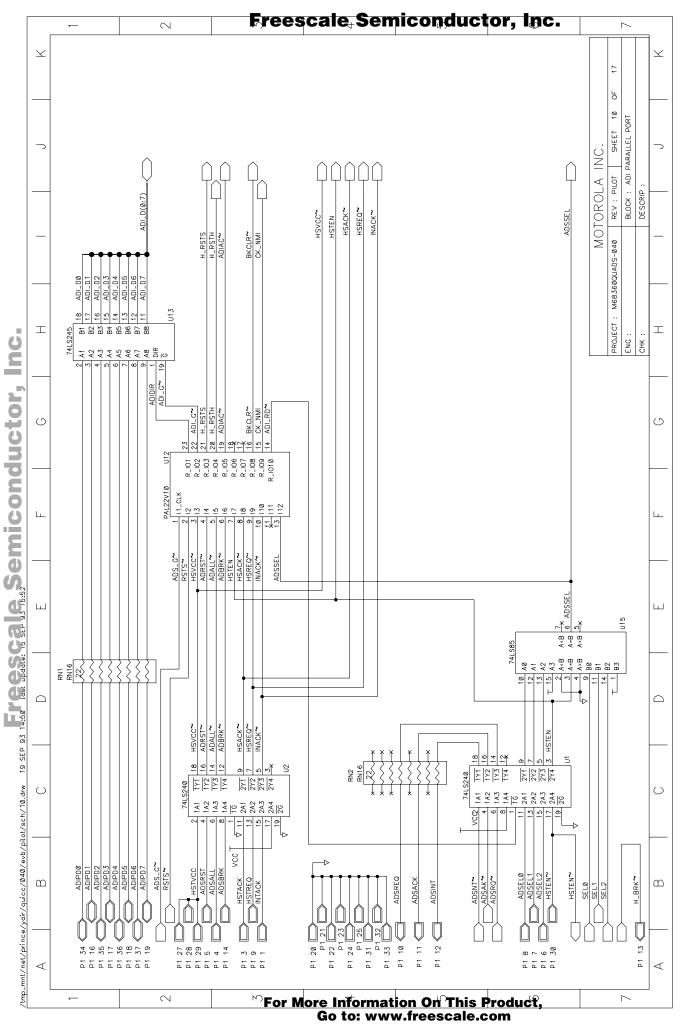

|            | 4.11.3               | ADI Port                                                            | 32       |

|            | 4.11.3.1             | ADI Port Signal Description                                         | 33       |

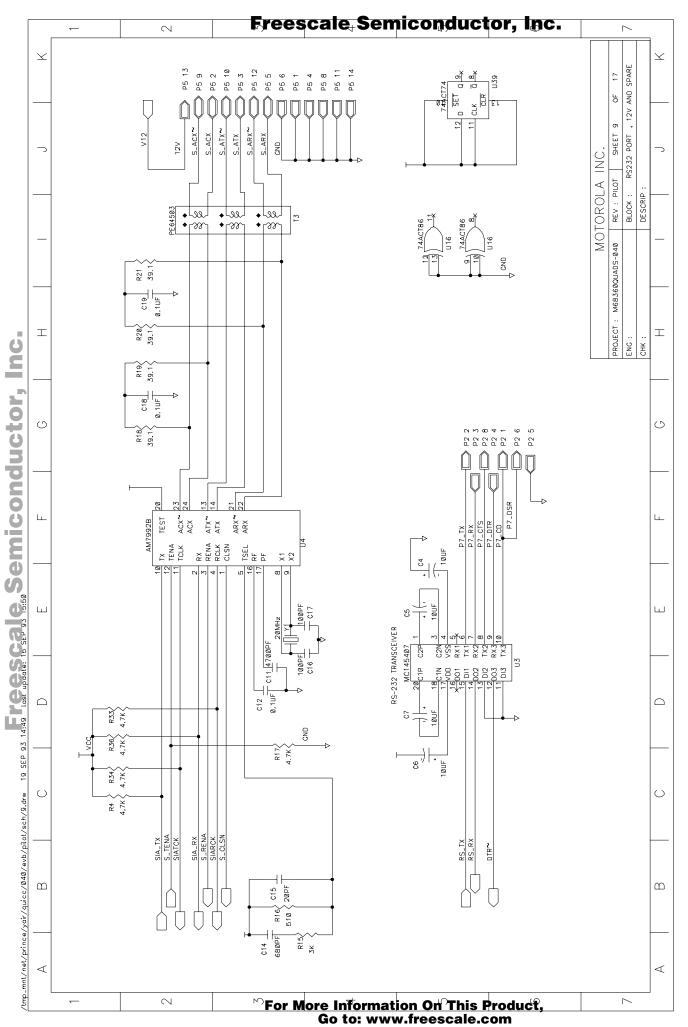

|            | 4.11.4               | RS-232 Serial Port                                                  | 34       |

|            | 4.11.4.1             | RS-232 Port Signal Description                                      | 35       |

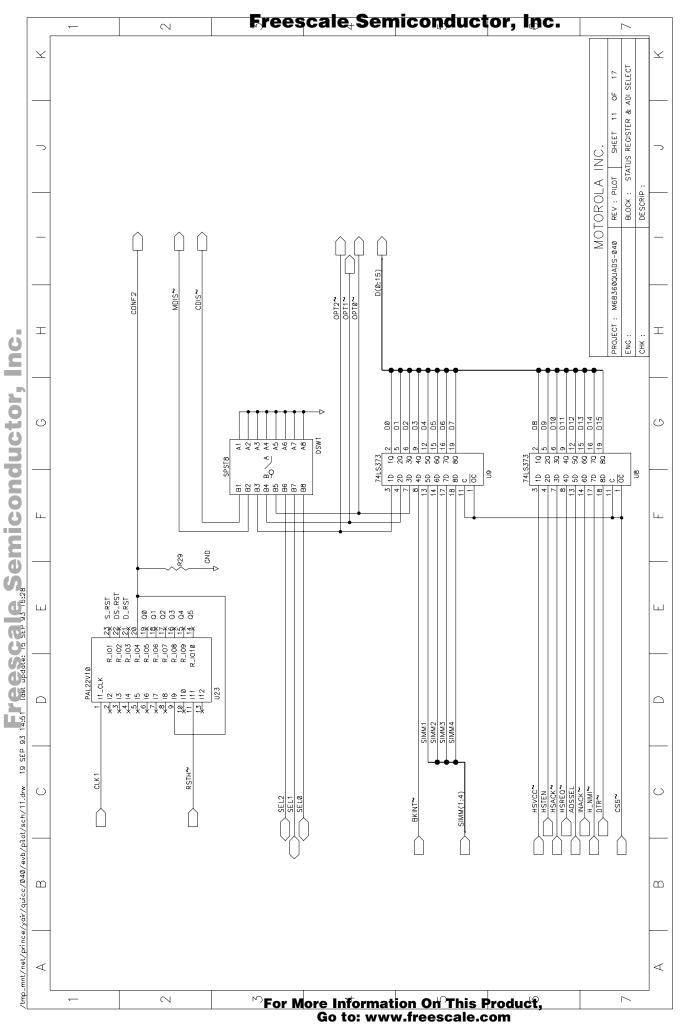

|            | 4.11.5               | M68360QUADS-040 Status Register                                     | 35       |

|            | 4.11.5.1             | Status Register Bits Description                                    | 35       |

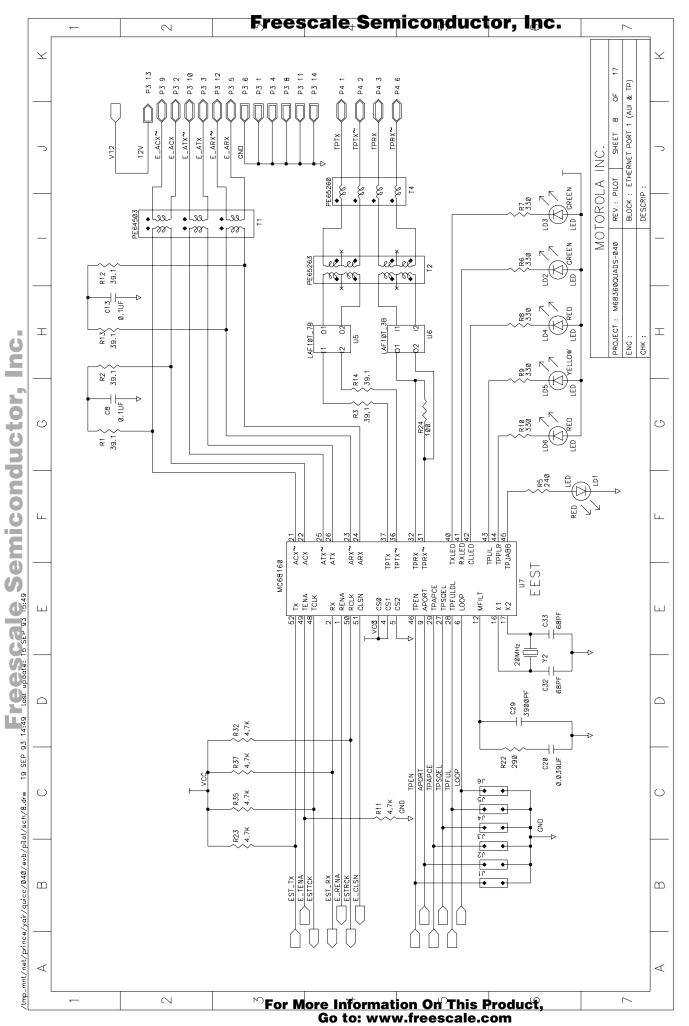

|            | 4.11.6               | Ethernet Controller                                                 | 36       |

|            | 4.11.6.1             | Ethernet AUI Ports Signal Description                               | 36       |

|            | 4.11.6.2             | Ethernet Twisted-Pair Port Signal Description                       | 37       |

|            | 4.11.7               | Serial EEPROM                                                       | 37       |

|            | 4.11.8               | Slave QUICC General Purpose I/O Pins                                | 37       |

|            | 4.11.8.1             | Slave QUICC Port A                                                  | 37       |

|            | 4.11.8.2<br>4.11.8.3 | Slave QUICC Port B<br>Slave QUICC Port C                            | 38       |

|            | 4.11.8.4             | Slave QUICC Port E                                                  | 39<br>40 |

| 5 -        |                      | PORT INFORMATION                                                    | 40<br>41 |

| 5.1        |                      | INTRODUCTION                                                        | 41       |

| 5.2        |                      | INTERCONNECT SIGNALS                                                | 41       |

| 0.2        | 5.2.1                | Connector P1 Interconnect Signals                                   | 41       |

|            | 5.2.2                | Connector P2 Interconnect Signals                                   | 42       |

|            | 5.2.3                | Connector P3 Interconnect Signals                                   | 42       |

|            | 5.2.4                | Connector P4 Interconnect Signals                                   | 43       |

|            | 5.2.5                | Connector P5 Interconnect Signals                                   | 43       |

|            | 5.2.6                | Connector P6 Interconnect Signals                                   | 44       |

|            | 5.2.7                | Connector P7 Interconnect Signals                                   | 44       |

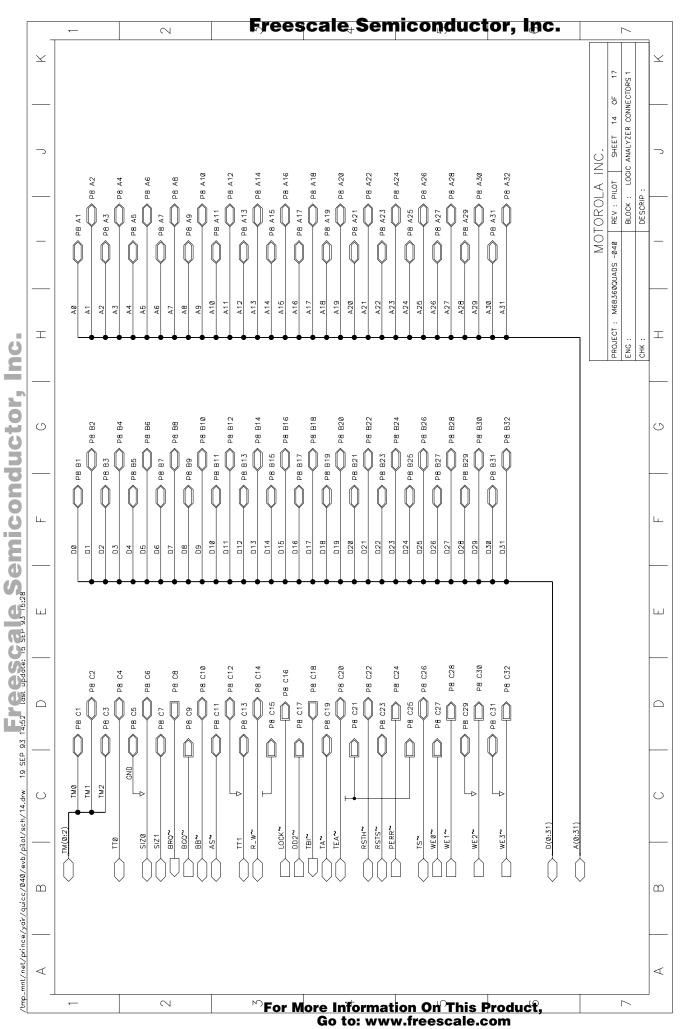

|            | 5.2.8                | Connector P8 Interconnect Signals                                   | 44       |

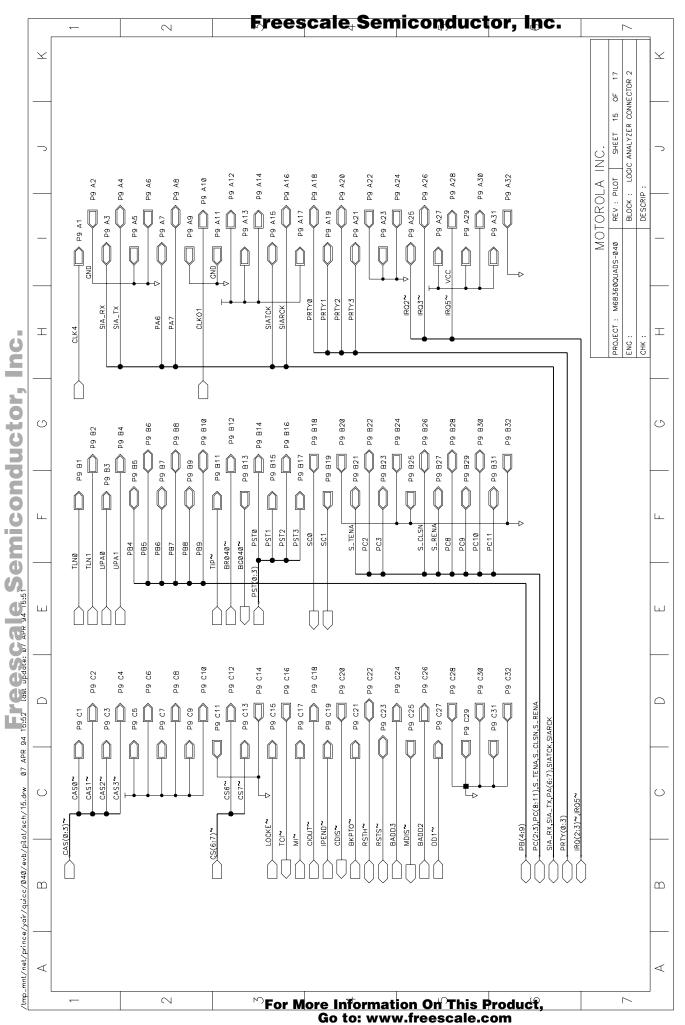

|            | 5.2.9                | Connector P9 Interconnect Signals                                   | 45       |

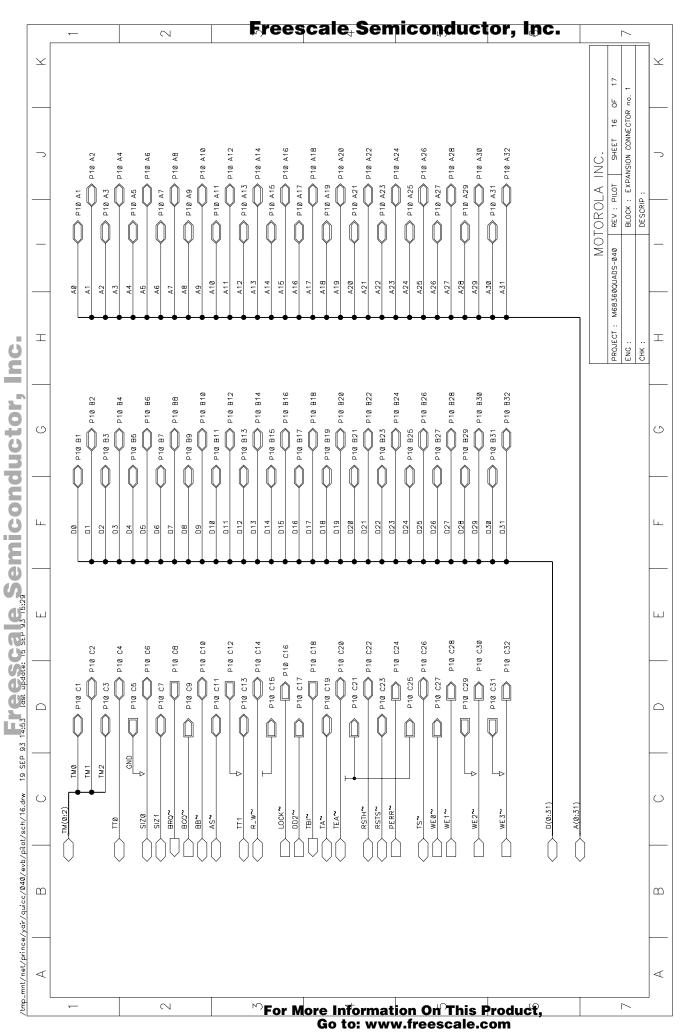

|            | 5.2.10               | Connector P10 Interconnect Signals                                  | 47       |

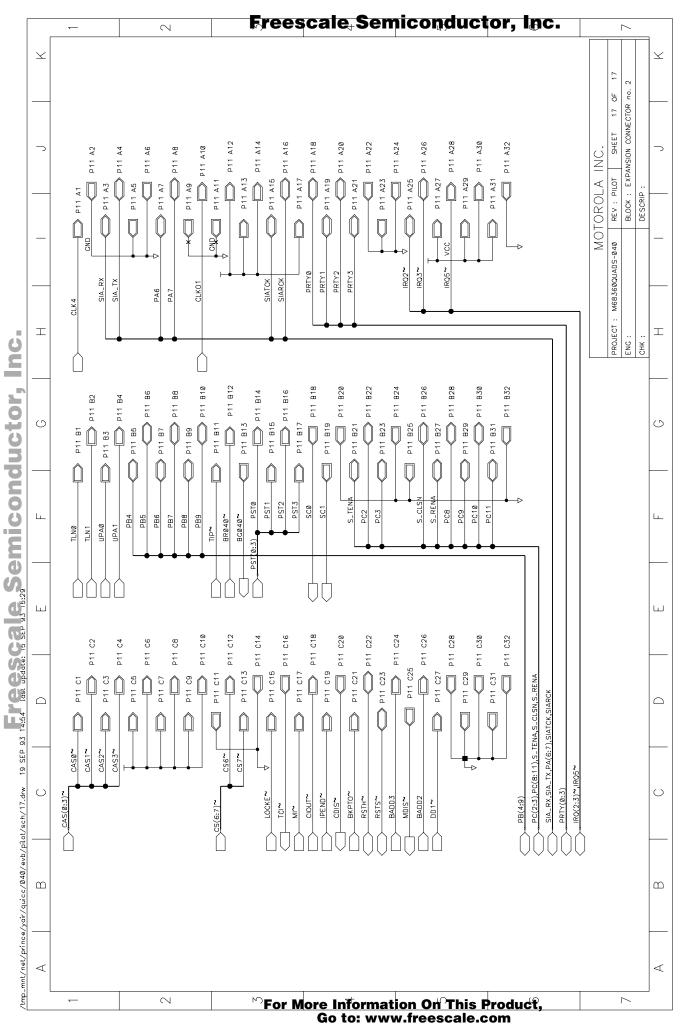

|            | 5.2.11               | Connector P11 Interconnect Signals                                  | 47       |

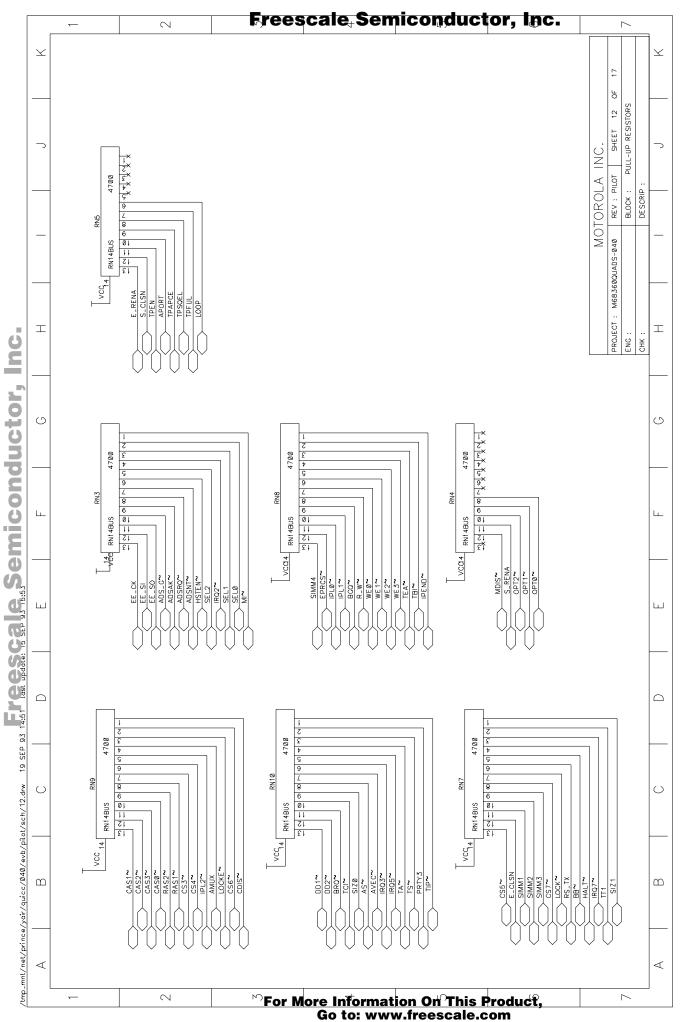

| 5.3        |                      | M68360QUADS-040 Parts List                                          | 47       |

| A.1        |                      | INTRODUCTION                                                        | 51       |

| A.2        |                      | IBM-PC/XT/AT to M68360QUADS-040 Interface                           | 51       |

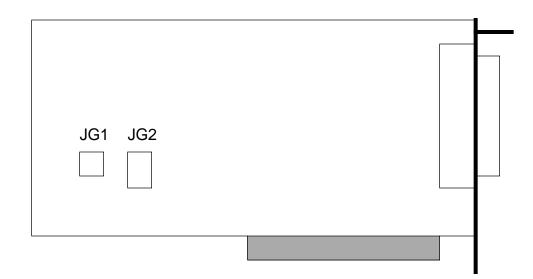

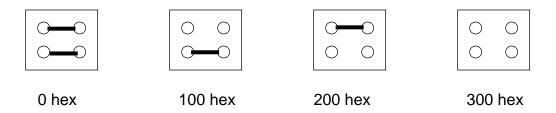

|            | A.2.1                | ADI Installation in IBM-PC/XT/AT                                    | 51       |

| A.3        |                      | SUN-4 to M68360QUADS-040 Interface                                  | 52       |

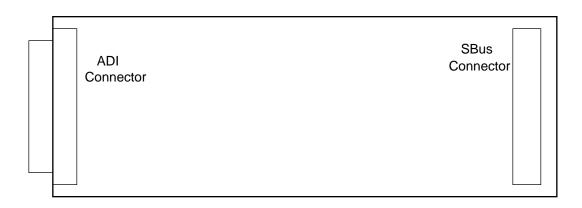

|            | A.3.1                | ADI Installation in the SUN-4                                       | 53       |

|            |                      |                                                                     | 55       |

| B.1<br>B.2 |                      | INTRODUCTION                                                        | 55<br>55 |

| в.2<br>В.3 |                      | ADI Port Concept and Operation Description<br>Handshake Description | 55<br>55 |

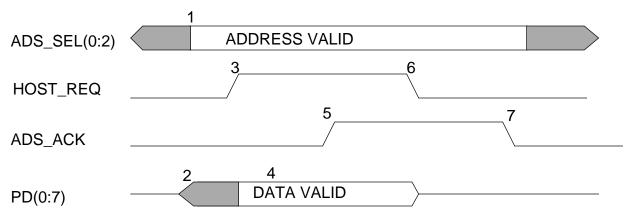

| D.3        | ,<br>B.3.1           | Write Cycle from Host to M68360QUADS-040                            | 56       |

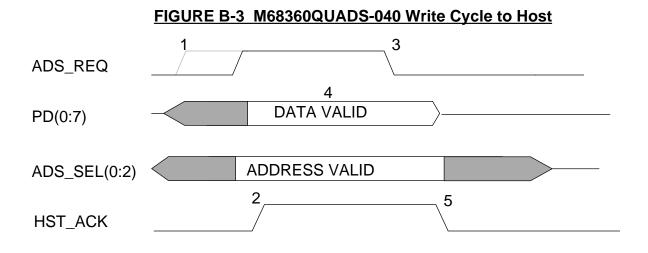

|            | B.3.2                | Write Cycle from M68360QUADS-040 to Host                            | 57       |

|            | B.3.3                | M68360QUADS-040 Interrupt to the Host                               | 58       |

|            | B.3.4                | Host Interrupt to the M68360QUADS-040                               | 59       |

|            | B.3.5                | Host Reset to the M68360QUADS-040                                   | 59       |

|            | B.3.6                | Addressing All M68360QUADS-040                                      | 59       |

| APPEN      | DIX C - PALS         |                                                                     | 60       |

| C.1        |                      | U10 - Indicators Logic                                              | 60       |

| C.2        |                      | U11 - Reset & Abort Generator                                       | 61       |

| C.3        |                      | U12 - ADI Controller                                                | 64       |

| C.4        |                      | U23 - Core Disable Logic                                            | 65       |

| C.5        | 5                    | U32 - Bursting Sram Controller                                      | 68       |

|            |                      |                                                                     |          |

#### For More Information On This Product, Go to: www.freescale.com

#### **LIST OF FIGURES**

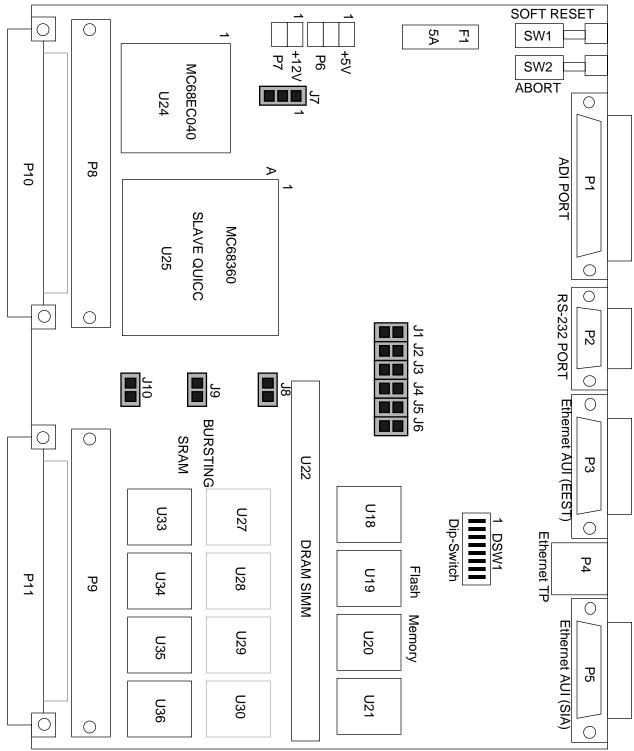

| FIGURE 2-1 | M68360QUADS Location diagram                   | 12     |

|------------|------------------------------------------------|--------|

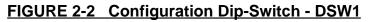

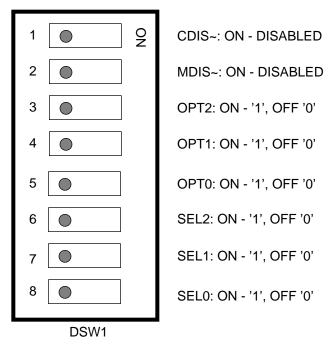

| FIGURE 2-2 | Configuration Dip-Switch - DSW1                | 13     |

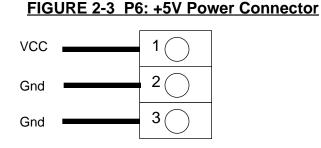

| FIGURE 2-3 | P6: +5V Power Connector                        | 15     |

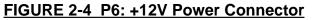

| FIGURE 2-4 | P6: +12V Power Connector                       | 15     |

| FIGURE 2-5 | P1 - ADI Port Connector                        | 16     |

| FIGURE 2-6 | P2 - RS-232 Serial Port Connector              | 16     |

| FIGURE 4-1 | Arbitration Scheme:                            | 29     |

| FIGURE 4-2 | ADI Port Connector                             | 33     |

| FIGURE 4-3 | RS-232 Serial Port Connector                   | 35     |

| FIGURE 4-4 | Status Register                                | 35     |

| FIGURE 4-5 | Ethernet AUI Port Connector                    | 36     |

| FIGURE 4-6 | Ethernet Twisted-Pair Port Connector           | 37     |

| FIGURE A-1 | Physical Location of jumper JG1 and JG2        | 52     |

| FIGURE A-2 | JG1 Configuration Options                      | 52     |

| FIGURE A-3 | ADI board for SBus                             | 53     |

| FIGURE B-1 | Host Computer (ADI) to M68360QUADS-040 Connect | ion 56 |

| FIGURE B-2 | Host Write to M68360QUADS-040                  | 57     |

| FIGURE B-3 | M68360QUADS-040 Write Cycle to Host            | 58     |

| FIGURE B-4 | M68360QUADS-040 Interrupt to Host              | 59     |

#### LIST OF TABLES

| TABLE 1-1. | M68360QUADS-040 Specifications           | 1  |

|------------|------------------------------------------|----|

| TABLE 3-1. | EC040 Cycle Types and Responding Devices | 13 |

| TABLE 3-2  | M68360QUADS-040 Main Memory Map          | 14 |

| TABLE 4-1. | DRAM SIMM Types                          | 27 |

| TABLE 4-2  | Port A Pins Description                  | 34 |

| TABLE 4-3  | Port B Pins Description                  | 35 |

| TABLE 4-4  | Port C Pins Description                  | 36 |

| TABLE 5-1  | Connector P1 Interconnect Signals        | 37 |

| TABLE 5-2  | Connector P2 Interconnect Signals        | 38 |

| TABLE 5-3  | Connector P3 Interconnect Signals        | 38 |

| TABLE 5-4  | Connector P8 Interconnect Signals        | 39 |

| TABLE 5-5  | Connector P5 Interconnect Signals        | 39 |

| TABLE 5-6  | Connector P6 Interconnect Signals        | 40 |

| TABLE 5-7  | Connector P7 Interconnect Signals        | 40 |

| TABLE 5-8  | Connector P8 Interconnect Signals        | 40 |

| TABLE 5-9  | Connector P9 Interconnect Signals        | 41 |

| TABLE 5-10 | Parts List                               | 43 |

#### **1 - GENERAL INFORMATION**

#### 1.1 INTRODUCTION

This document describes the evaluation board for the MC68EC040 - MC68360 combination called the M68360QUADS-040. This board is constructed with an MC68EC040 as the master processor and a MC68360 (QUICC) as a slave in MC68EC040 companion mode. The purpose of this board is to evaluate the performance of the above combination, rather than serve as a development system.

#### 1.2 RELATED DOCUMENTATION

- MC68360 User's Manual.

- MC68EC040 User's Manual.

- MC68LC040 User's Manual.

- ADI board specification.

#### 1.3 ABBREVIATIONS USED IN THE DOCUMENT

- QUADS Application Development System for the QUICC device.

- ADI Application Development Interface.

- UART Universal Asynchronous Receiver/Transmitter.

- SIMM Single In-line Memory Module.

- AUI Attachment Unit Interface.

- SPI Serial Peripheral Interface

- NMI Non Maskable Interrupt

- EEST Enhanced Ethernet Serial Transceiver the MC68160

- SIA Serial Interface Adapter, the Am7992

- TP Twisted Pair

- nsec nano second

#### <u>1.4</u> <u>SPECIFICATIONS</u>

The M68360QUADS-040 specifications are given in TABLE 1-1. Paragraph 1.5 details the cooling requirements.

#### TABLE 1-1. M68360QUADS-040 Specifications

| CHARACTERISTICS                               | SPECIFICATIONS                                                                                     |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------|

| Power requirements (no other boards attached) | +5Vdc @ 3.5 A (typical), 5 A (maximum)<br>+12Vdc - Determined by the Ethernet network <sup>a</sup> |

| Microprocessor                                | XC68EC/LC040FE33 <sup>b</sup> @ 25 MHz                                                             |

| CHARACTERISTICS       | SPECIFICATIONS                                                                                          |

|-----------------------|---------------------------------------------------------------------------------------------------------|

| Addressing            |                                                                                                         |

| Total address range:  |                                                                                                         |

| on-board -            | 256 MBytes <sup>c</sup>                                                                                 |

| Off-board -           | 4 GigaBytes                                                                                             |

| Flash Memory          | 512 KByte, 32 bits wide expandable to 2 MBytes                                                          |

| Dynamic RAM           | 1 MByte, 36 bits wide SIMM (32 bit data, 4 bit parity) option to use higher density SIMM, up to 8 MByte |

| EEPROM                | 256 Byte, serial EEPROM                                                                                 |

| Operating temperature | 0°C - 30°C                                                                                              |

| Storage temperature   | -25°C to 85°C                                                                                           |

| Relative humidity     | 5% to 90% (non-condensing)                                                                              |

| Dimensions:           |                                                                                                         |

| Height                | 9.173 inches (233 mm)                                                                                   |

| Depth                 | 6.3 inches (160 mm)                                                                                     |

| Thickness             | 0.063 inches (1.6 mm)                                                                                   |

#### TABLE 1-1. M68360QUADS-040 Specifications

a. The 12V supply is not used on the board, it is connected only to the Ethernet AUI connectors P3 & P5 to be supplied to the network. Therefore, the power consumption of that supply is independent of the M68360QUADS-040.

b. 33 MHz components are used to get better s.u. timing between the QUICC & the EC040.

c. Since A28 to A31 of the slave QUICC are used as Write-Enable signals, the on-board addressing space is reduced to 256 MBytes.

#### 1.5 COOLING REQUIREMENTS

The M68360QUADS-040 is specified, designed, and tested to operate reliably with an ambient air temperature range from 0°C to 30°C. This, due to the overheating problems of the XC68EC040 as the 68EC040 **must** have a heat-sink attached to it for proper operation at room<sup>1</sup> temperature. Therefore, the ambient temperature of operation for the M68360QUADS-040 **should never exceed 30°C**.

<sup>1.</sup> If no heat sink is attached to the 68EC040, maximum ambient temperature allowed @ 25 Mhz is -4 °C !!!

#### 1.6 FEATURES

Following are the main features of the M68360QUADS-040:

- □ Master MC68EC040FE33 with 32-bit address bus, 32 bit data bus, instruction and data caches.

- □ Supports also MC68LC040.

- 1 Mbyte Dynamic RAM, 60 nsec access time, 36 bits wide (data and parity) SIMM, accessed with 3,2,2,2 clock cycles. Support for dram SIMMs upto 8 Mbyte with automatic size and speed detection.

- 512 Kbyte Flash PROM, On-board (5V) programmable, individual sector protection, 32 bits wide, 120 nsec access time, support is given up to 2 Mbyte.

- 128K byte synchronous bursting sram, 36 bits wide, 12 nsec access time. Accessed with 3,1,1,1 clock cycles. Option for additional 128K Byte identical bank.

- □ 256 byte serial EEPROM, accessed by the SPI port.

- □ Application Development Interface (ADI) port via 37 pin D-type connector.

- □ Serial RS-232 port for terminal or host computer connection via 9 pin Dtype connector.

- **Two** Ethernet ports:

- 1. The first using Motorola's MC68160 (EEST) with both AUI and TP connectors.

- 2. The second using AMD's Am7992 (SIA) with AUI connector.

- SCC2 (connected to the second Ethernet port) may be used for other purpose, by removing the SIA from its socket.

- □ Expansion and Logic Analyzer connectors for both slave QUICC and MC68EC040.

- □ Slave QUICC (core disabled in 68EC040 companion mode) providing the following functions:

- 1. DRAM Controller

- 2. Chip Select, TA~ and DSACK~ generator.

- 3. Parallel port (ADI) controller.

- 4. UART for terminal or host computer connection.

#### Frenssale Semiranductor, Mina

- 5. Dual-port Ethernet controller.

- VMEbus double-height board dimensions

- □ SOFT-RESET, HARD-RESET and ABORT switches.

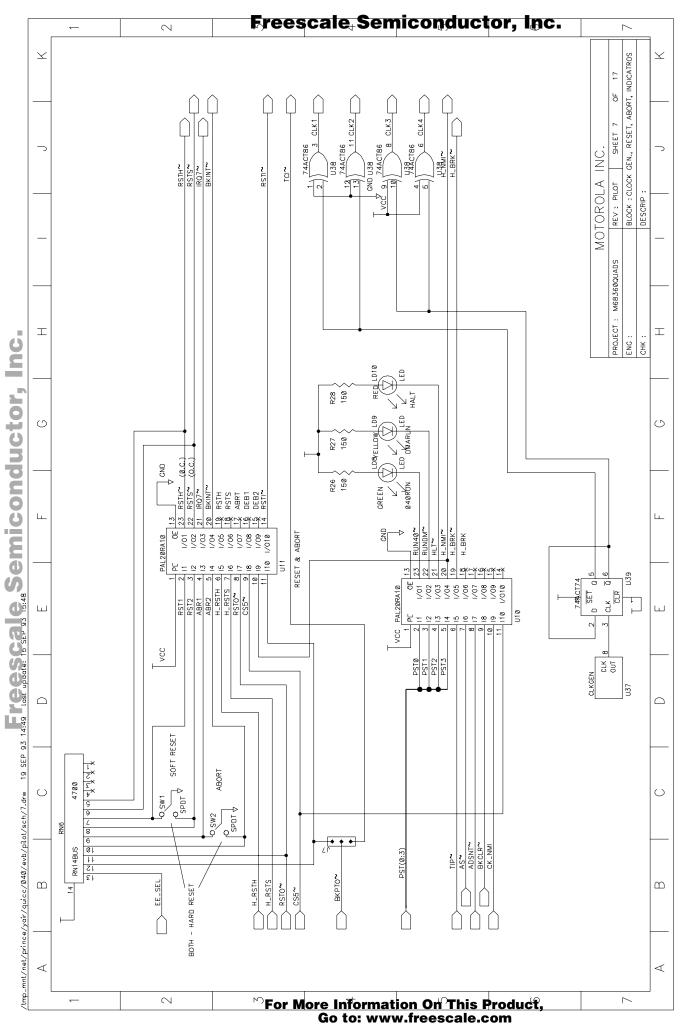

- □ Status LEDs for power, EC040 run, DMA run, HALT and Ethernet signals.

- $\Box$  Single +5Vdc power supply.

#### 1.7 HARDWARE BLOCK DIAGRAM

#### For More Information On This Product, Go to: www.freescale.com

#### 2 - Hardware Preparation and Installation

#### 2.1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation, and installation instructions for the M68360QUADS-040.

#### 2.2 UNPACKING INSTRUCTIONS

#### <u>NOTE</u>

If the shipping carton is damaged upon receipt, request carrier's agent be present during unpacking and inspection of equipment.

Unpack equipment from shipping carton. Refer to packing list and verify that all items are present. Save packing material for storing and reshipping of equipment.

**CAUTION**

AVOID TOUCHING AREAS OF INTEGRATED CIRCUITRY; STATIC DISCHARGE CAN DAMAGE CIRCUITS.

#### 2.3 HARDWARE PREPARATION

To select the desired configuration and ensure proper operation of the M68360QUADS-040 board, changes of the Dip-Switch settings may be required before installation. The location of the switches, LEDs, Dip-Switches, and connectors is illustrated in FIGURE 2-1. The board has been factory tested and is shipped with Dip-Switch settings as described in the following paragraphs. Parameters can be changed for the following conditions:

- ADI port address

- Enable/Disable MC68EC040's caches (both Instruction and Data)

- Eanble / Disable MC68LC040's Memory Management Unit<sup>1</sup>

- Hardware BreakPoint logic operation

- Parity Error Interrupt generation

- Arbitration Configuration

- EEST Twisted Pair Interface configuration

- User Selectable Options

#### Frenssale Semiganductor, Minga

#### FIGURE 2-1 M68360QUADS Location diagram

# For More Information On This Product, Go to: www.freescale.com

#### 2.3.1 ADI Port Address Selection

The M68360QUADS-040 can have eight possible slave addresses set for its ADI port, enabling up to eight M68360QUADS-040 boards to be connected to the same ADI board in the host computer. The selection of the slave address is done by setting switches 6, 7 & 8 in the Dip-Switch. Switch 6 stands for the most-significant bit of the address and switch 8 stands for the least-significant bit. If the switch is in the 'ON' state, it stands for logical '1'. In FIGURE 2-2 DSW1 is shown to be configured to address '0'.

Table 2-1 describes the switch settings for each slave address:

**Table 2-1 ADI Address Selection**

| ADDRESS | Switch 6 | Switch 7 | Switch 8 |

|---------|----------|----------|----------|

| 0       | OFF      | OFF      | OFF      |

| 1       | OFF      | OFF      | ON       |

| 2       | OFF      | ON       | OFF      |

| 3       | OFF      | ON       | ON       |

| 4       | ON       | OFF      | OFF      |

| 5       | ON       | OFF      | ON       |

| 6       | ON       | ON       | OFF      |

| 7       | ON       | ON       | ON       |

#### 2.3.2 Caches Enable / Disable

Switch #1 on DSW1 enables / disables the MC68EC040 caches. When it is in 'OFF' position (FACTORY SETUP) both caches may be enabled by software. When it is in 'ON' position, both instruction and data caches can not be enabled by software.

#### 2.3.3 MMU Enable / Disable

Switch #2 on DSW1 enables / disables the Memory Management Unit, which exists only on a MC68LC040 processor. When a MC68EC040 is installed, this switch has no effect. When switch #2 is in 'OFF' position the MMU (if exists) is enabled, when in 'ON' position - the MMU (if exists) is disabled.

Hardware Break Point Logic Configuration

The Hardware BreakPoint Out signal (BKPTO~) of the QUICC may be used for 2 purposes:

- 1. Generating level 7 interrupt (NMI) to the EC040, serving its original purpose.

- 2. A caching shield logic, to avoid redundant caching of data into the data cache

The selection between the above is done via jumper J7. When pins 1 and 2 of J7 are connected, the breakpoint logic functions in its original goal. When pins 2 and 3 of J7 are connected, the breakpoint logic serves a data caching shield.

J7 is configured at factory to position 1-2.

#### 2.3.4 Parity Error Interrupt Generation

When the QUICC's parity logic is operating, i.e., parity is generated and checked by the memory controller, it is possible to generate level 5 interrupt to the EC040 when parity error is encountered. When jumper J8 is connected, the QUICC's Parity Error line (PERR~) is connected to the QUICC's level 5 interrupt request line - IRQ5~ to generate level 5 interrupt upon parity error occurrence. When J8 is disconnected, no parity error interrupt is generated.

J8 is disconnected at factory.

#### 2.3.5 Arbitration Configuration

To allow for external master to be connected off-board, the arbitration scheme must be changed.

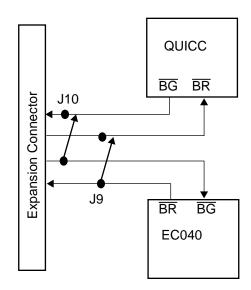

Jumper J9 connects between the EC040 Bus Request Output (BR040~) and QUICC's Bus Request Input (BRQ~), while J10 connects between the QUICC's Bus Grant Output (BGQ~) and the EC040's Bus Grant Input (BG040~). When BOTH J9 and J10 are connected, arbitration is done by the QUICC's arbiter. When BOTH J9 and J10 are DISCONNECTED, an external arbiter may be introduced via the expansion connectors.

BOTH J9 & J10 are connected at factory.

#### 2.3.6 EEST Configuration

The configuration of the MC68160 - EEST is determined by the position of jumpers J1 to J6. For the concise description of the role of each jumper see section 3.2.4 on page 17. The EEST is factory set to AUI interface, i.e., jumpers J1, J2 & J6 connected and J2 - J5 disconnected.

#### 2.3.7 User Selectable Options

Since the state of switches #3 to #5 is readable to software via the board status-register, it is possible to use them for software configuration, modes' selection, etc. For further information on that subject see 4.11.5 on page 35.

#### 2.4 INSTALLATION INSTRUCTIONS

When the M68360QUADS-040 has been configured as desired by the user, it can be installed according to the required working environment as follows:

#### 2.4.1 +5V Power Supply Connection

The M68360QUADS-040 requires +5 Vdc @ 5 A max, power supply for operation. Connect the +5V power supply to connector P11 as shown below:

P5 is a 3 terminal block power connector with power plug. The plug is designed to accept 14 to 22 AWG wires. It is recommended to use 14 to 18 AWG wires. To provide solid ground, two Gnd terminals are supplied. It is recommended to connect both Gnd wires to the common of the power supply, while VCC is connected with a single wire.

#### <u>NOTE</u>

Since hardware applications can be connected to the M68360QUADS-040 using the expansion connectors P8 and P10, the additional power consumption should be taken into consideration when a power supply is connected to the M68360QUADS-040.

#### 2.4.2 P7: +12V Power Supply Connection

The M68360QUADS-040 requires +12 Vdc @ 1 A max, power supply for the Ethernet AUI port. The M68360QUADS-040 can work properly without the +12V power supply, if the AUI port is not in use or if the AUI port is used with an AUI hub that does not require 12 V to be provided by the network termination equipment.

Connect the +12V power supply to connector P6 as shown below:

P6 is a 2 terminal block power connector with power plug. The plug is designed to accept 14 to 22 AWG wires. It is recommended to use 14 to 18 AWG wires.

#### 2.4.3 ADI Installation

For ADI installation on various host computers, refer to APPENDIX A - on page 51.

#### 2.4.4 Host computer to M68360QUADS-040 Connection

The M68360QUADS-040 ADI interface connector, P1, is a 37 pin, male, D type connector. The connection between the M68360QUADS-040 and the host computer is by a 37 line flat cable, supplied with the ADI board. FIGURE 2-5 below shows the pin configuration of the connector.

#### Frenssale Semiganductor, Minga

#### FIGURE 2-5 P1 - ADI Port Connector

| Gnd<br>Gnd<br>Gnd<br>Gnd<br>(+ 12 v) N.C.<br>HOST_VCC<br>HOST_VCC<br>HOST_VCC<br>HOST_VCC<br>HOST_ENABLE~<br>Gnd<br>Gnd<br>PD0<br>PD2<br>PD4<br>PD6 | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | INT_ACK<br>N.C.<br>HST_ACK<br>ADS_ALL<br>ADS_RESET<br>ADS_SEL2<br>ADS_SEL1<br>ADS_SEL0<br>HOST_REQ<br>ADS_REQ<br>ADS_REQ<br>ADS_ACK<br>ADS_INT<br>HOST_BRK~<br>ADS_BRK<br>N.C.<br>PD1<br>PD3<br>PD5<br>PD7 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

NOTE: Pin 26 on the ADI is connected to +12 v power supply, but it is not used in the M68360QUADS-040.

#### 2.4.5 Terminal to M68360QUADS-040 RS-232 Connection

In the stand-alone operation mode, a VT100 compatible terminal should be connected to the RS-232 connector P2. The RS-232 connector is a 9 pin, female, D-type connector as shown in FIGURE 2-6.

#### FIGURE 2-6 P2 - RS-232 Serial Port Connector

| CD   | 1      | ~ |      |

|------|--------|---|------|

| тх 🗄 | 2      | 6 | DSR  |

|      |        | 7 | RTS  |

| RX   | 3      | 8 | CTS  |

| DTR  | 4      | • |      |

|      | -<br>- | 9 | N.C. |

| GND  | 5      |   |      |

NOTE: The RTS line (pin 7) is not connected in the M68360QUADS-040.

#### For More Information On This Product, Go to: www.freescale.com

#### **3 - OPERATING INSTRUCTIONS**

#### 3.1 INTRODUCTION

This chapter provides necessary information to use the M68360QUADS-040 in host-controlled and standalone configurations. This includes controls and indicators, memory map details, and software initialization of the board.

#### 3.2 CONTROLS AND INDICATORS

The M68360QUADS-040 has the following switches and indicators.

#### 3.2.1 SOFT RESET Switch SW1

The SOFT RESET switch, SW1, resets all M68360QUADS-040 devices, and resets the EC040, and performs soft reset to the QUICC internal modules, maintaining QUICC's configuration (clocks & chipselects). The switch signal is debounced, and it is not possible to disable it by software.

#### 3.2.2 ABORT Switch SW2

The ABORT switch is normally used to abort program execution by issuing a level 7 interrupt to the EC040 to return control to the QUICC040Bug. The ABORT switch signal is debounced and can not be disabled by software.

#### 3.2.3 HARD RESET - Switches SW1 & SW2

When BOTH switches - SW1 and SW2 are depressed simultaneously, HARD reset is generated to both the EC040 and QUICC. When the QUICC is HARD reset, all its configuration is lost and has to be re-initialized.

#### 3.2.4 EEST Configuration Jumpers J1 to J6

The following jumpers J1 to J6 are used to determine the EEST operation modes according to the description below:

#### 3.2.4.1 TPEN Jumper - J1

The TPEN (Twisted Pair Enable) jumper, determines the interface type of the EEST ethernet port. When in position along with J2, the EEST port uses the AUI interface. When removed and J2 in position, the interface type is twisted pair.

#### WARNING

Whenever J2 is to be removed, J1 MUST be removed PRIOR to the removal of J2. Failure in doing so, might result in permanent damage to EEST device (U7).

#### 3.2.4.2 APORT Jumper - J2

When the APORT (Automatic Port Selection Enable) jumper - J2 is in position, the interface type of the EEST device is selected manually via J1. When J2 is removed, the selection is done automatically according to the presence of link beats on the twisted pair receive input.

#### 3.2.4.3 TPAPCE Jumper - J3

When the TPAPCE (Twisted Pair Automatic Polarity Correction Enable) jumper - J3 is removed, the EEST device corrects internally polarity faults and indicates them via the TPPLR led - LD6. When J3 is in position, automatic polarity correction is disabled.

#### 3.2.4.4 TPSQEL Jumper - J4

#### Fremssale Semiconductor, Minga

When the TPSQEL (Twisted Pair Signal Quality Error Test Enable) jumper - J4 is in position, the collision detect circuitry test is enabled, i.e., simulated collision is generated to the EEST collision detect circuitry. The generated collision does not have any effect over the TP media. When J4 is removed, the above test is disabled.

#### 3.2.4.5 TPFULDL Jumper - J5

When the TPFULDL (Twisted Pair Full Duplex Mode Select) jumper - J5 is in position, simultaneous receive and transmit are enabled for the TP port without collision indication. When J5 is removed, the above is disabled.

#### 3.2.4.6 LOOP - Diagnostic Loopback Jumper - J6

When the LOOP jumper - J6 is removed, diagnostic loop-back mode is enabled for the EEST regardless of the interface type selected. In this mode, data is transmitted back into the receiver but not to the medium. When J6 is in position, the diagnostic loop-back mode is disabled.

#### 3.2.5 Hardware Breakpoint Usage Jumper - J7

When J7 is connected between pins 1-2, the hardware BreaKPoinT Out (BKPTO~) signal of the QUICC is connected to the interrupt logic. When breakpoint is reached, level 7 interrupt is generated to the EC040.

When J7 is connected between pins 2 - 3, BKPTO~ is connected to the Transfer cache Inhibit (TCI~) signal of the EC040. That way desired memory areas may be "shielded" and prevented from being cached. This allows for better utilization of the EC040 data cache, keeping one-time accessed data out of the data cache.

#### 3.2.6 Parity Error Interrupt Jumper - J8

When J8 is positioned in place and parity is enabled, occurrence of parity error, causes a level 5 interrupt to the EC040 via the QUICC's interrupt controller. When J8 is removed, parity error interrupts are disabled.

#### 3.2.7 Bus Request Jumper - J9

When J9 is in position, the Bus Request (BR~) Output of the EC040 is connected to the Bus Request Input of the QUICC. This is the normal operating mode. When J9 is removed, the Bus Request Output of the EC040 is disconnected from the Bus Request Input of the QUICC, allowing for an external (off-board) arbiter to be located between them.

#### 3.2.8 Bus Grant Jumper - J10

When J10 is in position the Bus Grant (BG~) Output of the QUICC is connected to the Bus Grant Input of the EC040. This is the normal operating mode. When J10 is removed, the Bus Grant Output of the QUICC is disconnected from the Bus Grant Input of the EC040, allowing for an external (off-board) arbiter to be located between them.

#### <u>NOTE</u>

For proper operation of the M68360QUADS-040, BOTH J9 and J10 must be In Position, unless an external arbiter is connected via the expansion connectors.

#### 3.2.9 HALT Indicator - LD10

The red LED HALT indicator LD1 is lit whenever the EC040 enters the HALT state. For example, when the EC040 can not recover from an error, it frees the bus and enters the HALT state.

#### 3.2.10 040RUN Indicator - LD8

The green LED 040RUN indicator is connected to the Transfer In Progress (TIP\*) signal. It is lit if the TIP\* signal is low (asserted) and it indicates the activity on the bus.

#### 3.2.11 DMARUN Indicator - LD9

The yellow DMARUN indicator is connected to AS\* signal of the slave QUICC, this to indicate bus activity of one of the QUICC's DMA channels.

#### 3.2.12 Ethernet TX Indicator - LD3

The green LED Ethernet Transmit indicator blinks whenever the EEST is transmitting data through one of the Ethernet ports P3 or P4.

#### 3.2.13 Ethernet RX Indicator - LD2

The green LED Ethernet Receive indicator blinks whenever the EEST is receiving data from one of the Ethernet ports P3 or P4.

#### 3.2.14 Ethernet CLSN Indicator LD4

The red LED Ethernet Collision indicator CLSN, blinks whenever a collision is detected in the AUI P3 port or the TP P4 port, or a jabber condition is detected in TP mode.

#### 3.2.15 Ethernet LIL Indicator - LD5

The yellow LED Ethernet Twisted Pair Link Integrity indicator - LIL, lights to indicate good link integrity on the TP P4 port. The LED is off when the link integrity fails, or when the AUI port is selected.

#### 3.2.16 Ethernet PLR Indicator - LD6

The red LED Ethernet TP Polarity indicator - PLR, lights if the wires connected to the receiver input of TP P4 port are reversed. The LED is lit by the EEST, and remains on when the EEST has automatically corrected for the reversed wires.

#### 3.2.17 Ethernet JABB Indicator - LD1

The red LED Ethernet TP Jabber indicator - JABB, lights whenever a jabber condition is detected on the TP P4 port.

#### 3.2.18 POWER Indicator - LD7

The yellow POWER indicator, indicates the presence of the +5V supply at P5.

#### 3.3 MEMORY MAP

At the beginning of each cycle, the chip-select generator of the slave QUICC determines the kind of memory cycle and which device is selected. Cycle types and address spaces are determined for EC040 cycles by the Transfer Modifier lines TM0 - TM2 and the Transfer Type lines TT0 - TT1 and by Function Codes FC0 - FC3 for QUICC's DMA cycles. The cycle types and the devices that respond are described in TABLE 3-1.

| TM(2:0) | TT(1:0) | Address Space                         | Responding Devices |

|---------|---------|---------------------------------------|--------------------|

| 000     | 00      | Data cache Push                       | All                |

| 001     | 0X      | User Data                             | All                |

| 010     | 00      | User Program                          | All                |

| 011     | 00      | MMU Table<br>Search <sup>a</sup> Data | All                |

#### TABLE 3-1. EC040 Cycle Types and Responding Devices

| TM(2:0) | TT(1:0) | Address Space                         | Responding Devices                        |

|---------|---------|---------------------------------------|-------------------------------------------|

| 100     | 00      | MMU Table<br>Search <sup>b</sup> Code | All                                       |

| 101     | 0X      | Supervisor Data                       | All                                       |

| 110     | 00      | Supervisor Program                    | All                                       |

| 111     | 00      | Supervisor CPU                        | QUICC's MBAR register                     |

| 111     | 11      | Supervisor CPU                        | QUICC during interrupt acknowledge cycle. |

#### TABLE 3-1. EC040 Cycle Types and Responding Devices

Freescale Semiconductor, Mng

a. For 68LC040 only, reserved otherwise

b. For 68LC040 only, reserved otherwise

#### 3.3.1 Main Memory Map

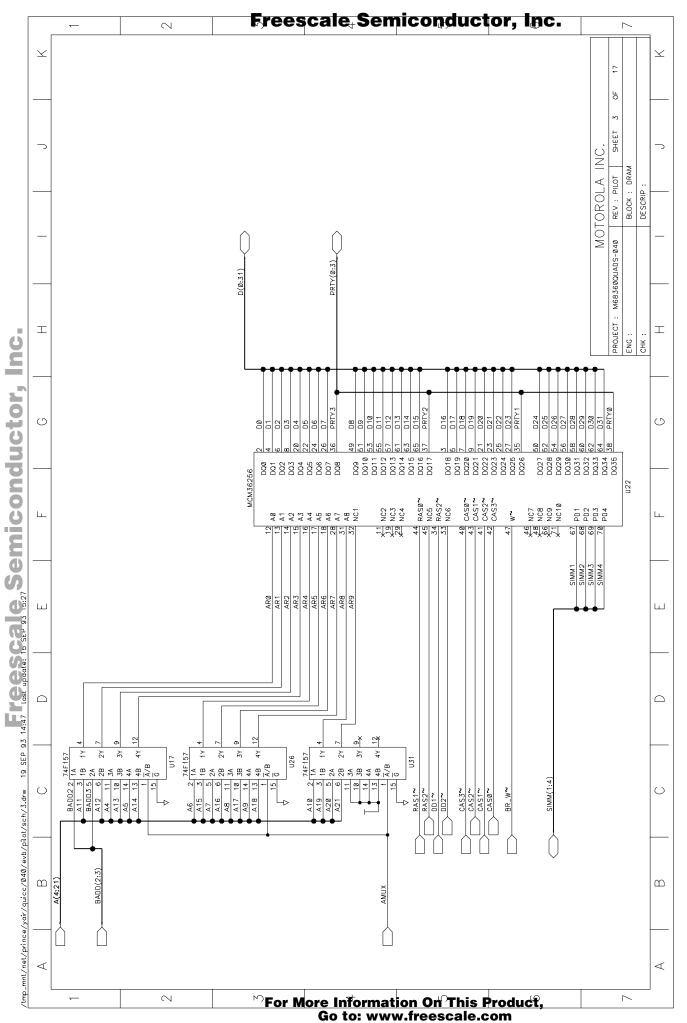

The memory map of devices that respond to User Data, User Program, Supervisory Data, Supervisory Program, and DMA access is shown in TABLE 3-2.

| ADDESS RANGE                                                                          | Accessed Device                                                                      | Data Size       | NOTES |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------|-------|

| 00000000 - 001FFFFF                                                                   | Flash PROM                                                                           | 32              | 2     |

| 00200000 - 003BFFFF                                                                   | Empty Space                                                                          |                 |       |

| 003C0000 - 003CFFFF                                                                   | Bursting SRAM - BANK 1 <sup>a</sup>                                                  | 32 + Parity     |       |

| 003E0000 - 003EFFFF                                                                   | Bursting SRAM - BANK 2                                                               | 32 + Parity     |       |

| 00400000 - 004FFFF<br>00400000 - 005FFFF<br>00400000 - 007FFFF<br>00400000 - 008FFFFF | DRAM SIMM MCM36256<br>DRAM SIMM MCM36512<br>DRAM SIMM MCM36100<br>DRAM SIMM MCM36200 | 32 + Parity     | 3     |

| 01210000 - 01211FFF                                                                   | Slave QUICC Internal Memory                                                          | 32              | 1     |

| 01230000 - 01231FFF                                                                   | M68360QUADS-040 Status Register                                                      | 16 <sup>b</sup> | 2     |

#### TABLE 3-2 M68360QUADS-040 Main Memory Map

a. Not populated - optional.

b. Connected to D0 - D15

#### NOTES:

- 1. Refer to the MC68360 QUICC User's Manual for complete description of the QUICC internal memory.

- 2. The device appears repeatedly in multiples of its size. For example, the Status Register appears at memory locations 01230002, 01230006, 012300A etc...

- 3. The DRAM SIMM installed in the M68360QUADS-040 is MCM36256 256Kx36 bit. The user may replace the DRAM module with a higher density SIMM and increase the DRAM space up to 8 MBytes.

#### For More Information On This Product, Go to: www.freescale.com

### 3.4 Programming the slave QUICC

The slave QUICC (core disabled) provides the following functions on the M68360QUADS-040:

Freescale Semiconductor, Mng

- 1. DRAM Controller

- 2. Chip Select and DSACK~ generator.

- 3. Parallel port (ADI).

- 4. UART for terminal or host computer connection.

- 5. Dual Ethernet controller.

- 6. Interrupter

- 7. Serial EEPROM interface.

- 8. General Purpose I/O signals.

The slave QUICC internal registers must be programmed after hardware reset as described in the following paragraphs. The addresses and programming values are in hexadecimal base.

Please refer to the MC68360 QUICC User's Manual for more information.

#### 3.4.1 Module Base Address Register

The slave QUICC's module base address register (MBAR) controls the location of its internal memory and registers and their access space. The slave QUICC MBAR resides at a fixed location in '0003FF00' in the CPU space.

The MBAR must be initialized to '00122001' to obtain the memory map as described in TABLE 3-2

#### 3.4.2 Module Configuration Register

The module configuration register (MCR) controls the SIM60 configuration in the slave QUICC. The MCR is initialized to 60018C3F after reset.

#### 3.4.3 CLKO Control Register

The CLKO control register (CLKOCR) controls the operation of the CLKO(1:2) pins. This register must be initialized to '03' after reset to enable CLKO2 and disable CLKO1.

#### 3.4.4 PLL Control Register

The PLL control register (PLLCR) controls the operation of the PLL. There is no need to program the PLLCR after hard reset, because the configuration of the MODCK(0:1) pins on the QUADS determines its value. It is recommended to set the PLLWR bit to prevent accidental writing.

#### 3.4.5 Port E Pin Assignment Register

Port E pins can be programmed by the port E pin assignment register (PEPAR). The PEPAR must be initialized to '37C0' to configure Port E of the slave QUICC as follows:

- The output of the slave QUICC interrupt request is on IOUT(0:2)~ pins.

- RAS1~ and RAS2~ double drive function is used to drive the DRAM.

- The A(31:28) pins of the slave QUICC are configured as write enables.

- The OE~/AMUX pin is configured as AMUX to drive the external multiplexers of the DRAM.

- The CAS(0:3)~ output function is used for the DRAM.

- CS7~ output function is enabled.

- AVECO~ function is chosen.

#### 3.4.6 System Protection Control

The system protection register (SYPCR) controls the system monitors, the software watchdog, and the bus monitor timing. This register must be initialized to '34' to disable the software watchdog, disable the double

#### Fremssale Semigenductor, Minga

bus fault monitor and to enable the bus monitor function to respond after 1 K clock cycles in the slave QUICC.

#### 3.4.7 Global Memory Register

The global memory register (GMR) contains selections for the memory controller of the slave QUICC. The GMR must be initialized according to the size and the access time of the DRAM SIMM installed on the M68360QUADS as follows:

- For 60, 70, 80 & 100 nsec DRAM type MCM36256 or MCM36100, the GMR must be initialized to '18A40000'.

- For 60, 70, 80 & 100 nsec DRAM type MCM36512 or MCM36200, the GMR must be initialized to '0CA40000'.

The GMR defines the following parameters:

- The DRAM refresh period is 15.36 μsec.

- The DRAM refresh cycle length 4 clocks long.

- The DRAM module port size is 32 bits.

- No extra wait between 040 dram accesses (4 phase precharge time)

- No extra wait between QUICC dram accesses (4 phase precharge time)

- Same length QUICC DRAM reads / writes

- Same length 040 SRAM reads / writes

- Parity is disabled.

- The CS~/RAS~ lines of the slave QUICC will not assert when accessing the CPU space.

- Internal address multiplexing for the DRAM is disabled.

#### 3.4.8 Base Register 0 and Option Register 0

Base register 0 (BR0) and Option register 0 (OR0) control the operation of CS0~ pin of the slave QUICC, which serves as the Flash Prom chip-select.

BR0 is initialized to 00000001 to determine the following:

- Base address 0.

- No burst support for EC040 access

- Parity disabled

#### 3.4.9 Base Register 1 and Option Register 1

Base register 1 (BR1) and Option register 1 (OR1) control the operation of RAS1~ pin of the slave QUICC. This pin is connected to the RAS signal of the first bank in the DRAM module.

BR1 must be initialized to '00400021', regardless of the type and the access time of the DRAM to establish the following:

- Base address 400000.

- Burst support for EC040 access

- Parity disabled

OR1 must be initialized according to the type of the DRAM SIMM installed on the M68360QUADS-040 as follows:

- For MCM36256 or MCM36512 types:

- For 100 nsec access time 3FF00001

- For 80 nsec or 70 nsec access time 2FF00001

- For 60 nsec access time 1FF00001

- For MCM36100 or MCM36200 types:

- For 100 nsec access time 3FC00001

- For 80 nsec or 70 nsec access time 2FC00001

- For 60 nsec access time 1FC00001

#### <u>NOTE</u>

To ensure proper operation of the DRAM, its RAS signal should be asserted and negated 8 times after power-up. Therefore after power-up, each dram bank should be read 8 times to comply with the requirement above.

#### 3.4.10 Base Register 2 and Option Register 2

Base register 2 (BR2) and Option register 2 (OR2) control the operation of RAS2~ pin of the slave QUICC. This pin is connected to the second<sup>1</sup> bank of the DRAM module.

BR2 must be initialized according to the type of DRAM SIMM installed on the M68360QUADS-040 as follows:

- For MCM36256 or MCM36100 types, BR2 is not initialized leaving RAS2 inactive.

- For MCM36512 type, BR2 must be initialized to 500021

- For MCM36200 type, BR2 must be initialized to 800021

OR2 initialization depends also of the DRAM SIMM type installed on the M68360QUADS-040 as to the following:

- For MCM36256 or MCM36512 types:

- For 100 nsec access time 3FF00001

- For 80 nsec or 70 nsec access time 2FF00001

- For 60 nsec access time 1FF00001

- For MCM36100 or MCM36200 types:

- For 100 nsec access time 3FC00021

- For 80 nsec or 70 nsec access time 2FC00001

- For 60 nsec access time 1FC00001

#### 3.4.11 Base Register 3 and Option Register 3

Base register 3 (BR3) and Option register 3 (OR3) control the operation of CS3~ pin of the slave QUICC, which controls the first bank of the Bursting SRAM. BR3 must be initialized to '003C0021', and OR3 must be initialized to '1FFE0000' to obtain the memory map as described in TABLE 3-2.

#### 3.4.12 Base Register 4 and Option Register 4

Base register 4 (BR4) and Option register 4 (OR4) control the operation of CS4~ pin of the slave QUICC, which controls the second bank of the Bursting SRAM. BR4 must be initialized to '003E0021', and OR4 must be initialized to '1FFE0000' to obtain the memory map as described in TABLE 3-2.

1. If available

#### 3.4.13 Base Register 5 and Option Register 5

Base register 5 (BR5) and Option register 5 (OR5) control the operation of CS5~ pin of the slave QUICC, which is connected to the Status Register and to the level -7 interrupt logic. When CS5~ is asserted (for read-only) both the Status Register is read and all existing level - 7 status bits are cleared.

BR5 must be initialized to '01230003', and OR5 must be initialized to '0FFFF800' to obtain the memory map as described in TABLE 3-2.

#### 3.4.14 Base Register 6 and Option Register 6

Since CS6~ is not being used on the M68360QUADS-040, BR6 and OR6 are not initialized by the debugger. CS6~ is available for user's applications via the expansion connector - P11.

#### 3.4.15 Base Register 7 and Option Register 7

Since CS7~ is not being used on the M68360QUADS-040, BR7 and OR7 are not initialized by the debugger. CS7~ is available for user's applications via the expansion connector - P11.

#### 3.4.16 Port A Open Drain Register

Port A of the slave QUICC is 16 pins port, and each pin may be configured as general purpose I/O pin or as dedicated peripheral interface pin. The port A open drain register (PAODR) configures the drivers of port A pins as open-drain or as active drivers. The PAODR must be initialized to '0000' to select the active drivers configuration.

#### 3.4.17 Port A Data Register

The Port A data register (PADAT) can be read to check the data at the pin. If a port pin is configured as general purpose output pin, the value in the PADAT for that pin is driven onto the pin.

On the M68360QUADS-040, port A is used for serial channels as well as for ADI parallel port. PADAT must be initialized to '3F00' before configuring the other port registers.

#### 3.4.18 Port A Data Direction Register

The port A data direction register (PADIR) has different functions according to the configuration of the port pins. If a pin is a general purpose I/O pin, the value in the PADIR for that pin defines the direction of the pin. If a pin is a dedicated peripheral interface pin, the value in the PADIR for that pin may select one of two dedicated functions of the pin. PADIR must be initialized to 'F000'.

#### 3.4.19 Port A Pin Assignment Register

The port A pin assignment register (PAPAR) configures the function of the port pins. If the value in the PAPAR for a pin is '0', the pin is general purpose I/O, otherwise the pin is a dedicated peripheral interface pin. The PAPAR must be initialized to '0F3F'.

#### 3.4.20 Port B Open Drain Register

Port B of the slave QUICC is a 18 bit port, and each pin may be configured as general purpose I/O pin or as dedicated peripheral interface pin. The port B open drain register (PBODR) configures the drivers of port B pins as open-drain or as active drivers. The PBODR must be initialized to '0000' to select the active drivers configuration.

#### 3.4.21 Port B Data Register

Port B data register (PBDAT) can be read to check the data at the pin. If a port pin is configured as general purpose output pin, the value in the PBDAT for that pin is driven onto the pin. It is recommended to initialize PBDAT to '3FFFF' before configuring the other port registers.

#### 3.4.22 Port B Data Direction Register

The port B data direction register (PBDIR) has different functions according to the configuration of the port pins. If a pin is general purpose I/O pin, the value in the PBDIR for that pin defines the direction of the pin. If a pin is dedicated peripheral interface pin, the value in the PBDIR for that pin may select one of two dedicated functions of the pin. The PBDIR must be initialized to '0000F'. Pins 10 to 17 are connected to the ADI port data bus, therefore their direction must be changed by software according to the data flow.

#### 3.4.23 Port B Pin Assignment Register

The port B pin assignment register (PBPAR) configures the function of the port pins. If the value in the PBPAR for a pin is '0', the pin is general purpose I/O, otherwise the pin is a dedicated peripheral interface pin. The PBPAR must be initialized to '0000F'.

#### 3.4.24 Port C Data Register

Port C of the slave QUICC is a 12 bit port, and each pin may be configured as general purpose I/O pin or as dedicated peripheral interface pin, with interrupt capability. The Port C data register (PCDAT) can be read to check the data at the pin. If a port pin is configured as general purpose output pin, the value in the PCDAT for that pin is driven onto the pin. It is recommended to initialize PCDAT to '000' before configuring the other port registers.

#### 3.4.25 Port C Data Direction Register

The port C data direction register (PCDIR) has different functions according to the configuration of the port pins. If a pin is general purpose I/O pin, the value in the PCDIR for that pin defines the direction of the pin. If a pin is dedicated peripheral interface pin, the value in the PCDIR for that pin may select one of three dedicated functions of the pin. The PCDIR must be initialized to '000'.

#### 3.4.26 Port C Pin Assignment Register

The port C pin assignment register (PCPAR) configures the function of the port pins, along with PCDIR and PCSO. The PCPAR must be initialized to '000'.

#### 3.4.27 Port C Special Options Register

The port C special options register (PCSO) configures the CDx and CTSx pins. Port C can detect changes on the CTS and CD lines and assert the corresponding interrupt while the SCC simultaneously uses those lines. The PCSO must be initialized to '030'.

#### 4 - FUNCTIONAL DESCRIPTION

#### 4.1 INTRODUCTION

This chapter details the hardware design of the M68360QUADS-040, and describes each module in order to simplify the design.

#### 4.2 Master MC68EC040

The CPU on the M68360QUADS-040 is a 33 MHz MC68EC040, running at 25 MHz, which uses the slave QUICC's "68EC040 companion mode" as the memory controller, the interrupt controller, bus arbiter and other system functions usually provided by dedicated logic or peripherals. Due to this "companion" mode support, the MC68EC040 interfaces gluelessly to the QUICC, while some of the QUICC pins change their function to match these of the 68EC040.

The MC68EC040 is unbuffered from the slave QUICC and the other peripherals (except for the externally multiplexed DRAM address lines). In order to demonstrate the "glueless" concept under practical test and evaluation.

Address lines A(28:31) of the slave QUICC are used in their alternate function as WE(0:3)~ to avoid having to generate them externally. As a result only 256 MByte of memory may be accessed by both the 68EC040 and the QUICC with chip-select support.

All the pins of the MC68EC040 device are available **unbuffered** to the user through the logic analyzer connectors. The user can monitor the 040 activity during its development stage.

#### 4.2.1 RESET for the 68EC040 & the QUICC

There are four basic types of reset, regarding their source and consequence, available on the M68360QUADS-040 board:

- 1. QUICC Generated Reset These types of reset are generated internally by the QUICC and include: Power-up & Software Watch-Dog. Double-Bus-Fault reset is not supported when the QUICC is in EC040 companion mode.

- 2. SOFT Reset may be caused by either depressing the SOFT-RESET push-button or when the ADI-port's soft-reset signal is asserted by the remote host. When either happens, the 040 is reset while the QUICC is soft-reset, i.e., the configuration of the QUICC is unchanged, preserving the contents of the DRAM.

- 3. HARD-RESET may be generated by either depressing SOFT-RESET in conjunction with the ABORT push-button or when the ADI-port's hard-reset signal is asserted by the remote host. When either happens, the 040 is reset and the QUICC is hard-reset, i.e., all the QUICC's sub-modules are reset, including configuration and clock logic.

- 4. RESET Instruction When the RESET instruction is executed by the MC68EC040, RESETS\* line is asserted to the QUICC, which in turn, asserts this line to complete 512 clock cycles. Execution of RESET instruction does not cause the reset of the MC68EC040 itself, therefore not interrupting the software flow.<sup>1</sup>

<sup>1.</sup> It was observed that the EC040 may start the next bus cycle faster than the QUICC can recover from the reset; therefore, it is recommended that the RESET instruction is loaded to an even cache-line address and executed from the cache.

#### 4.2.2 Utilizing the MC68EC040 Data Cache

In order to achieve best performance out of the MC68EC040, both caches, Instruction and Data, are used. Since the bus interface of the EC040 and the QUICC's DMA are different, snooping is not supported on the M68360QUADS-040. Therefore, when the Data cache is enabled and used, two basic problems arise:

- 1. When registers or buffer descriptors are changed values by hardware or DMA are to be polled, they should not be cached, otherwise they will be polled indefinitely from the data cache, while their value may change outside, unnoticed by application software.

- 2. Transmit or Receive buffers should not be cached, since they are being used only once, therefore, not only caching them will not contribute to better performance, but rather will harm it, since it will keep the replacement mechanism busier.

To answer the above problems, the following measures were taken on the M68360QUADS-040:

- 1. The QUICC internal memory map area, including the registers and buffer-descriptors spaces, was moved to the second 16 Mbyte block<sup>1</sup>, where it is marked as Non-cashable in the DTTR1 register of the 68EC040.

- 2. To allow for memory areas containing Transmit or Receive buffers to avoid being cached, the Hardware Breakpoint mechanism may be utilized as a caching shield. The BKPTO\* signal of the QUICC is connected via a jumper J7, to the TCI\* signal of the EC040, which when asserted at the beginning of a data-cache line read cycle, avoids the caching of that line in the data-cache. As the BKAR and BKCR are programmed to match the address, size, and attributes of the desired memory space<sup>2</sup> to be shielded, BKPTO\* will be asserted on the relevant access to that space and avoid redundant caching.

#### 4.3 Interrupts on the M68360QUADS-040

In slave mode (including 68EC040 companion) the QUICC serves as an interrupt encoder for the master processor. It integrates all internal and external interrupt sources and encodes them to IOUT(0:2)~ to be connected to standard 68000 IPL~ lines. Since the parity lines are used on the M68360QUADS-040, IOUT(0:2)~ are used on the expense of IRQ1~, IRQ4~ and IRQ6~ of the slave QUICC.

There are 5 external<sup>3</sup> interrupt sources on the M68360QUADS-040:

- 1. ABORT push-button non-maskable, level 7.

- 2. Host NMI via ADI port non-maskable, level 7.

- 3. Hardware-Breakpoint non-maskable, optional, level 7.

- 4. Parity error, generated by the slave QUICC's parity logic maskable, level 5.

- 5. Host Request / Acknowledge from ADI port maskable, level 2.

All the level - 7 interrupt source are registered and two of them are available in the status register, this to allow software to detect the source of the of the interrupt. The interrupts on levels 5 and 2 are most likely to use the autovector mechanism of the QUICC.

#### 4.3.1 ABORT Push-button

When the ABORT push button - SW2 is depressed, a non-maskable, level-7 interrupt is generated to the EC040 by the QUICC. When the ABORT push-button is depressed in conjunction with the SOFT-RESET

<sup>1.</sup> There is no MMU on the MC68EC040, therefore use must be done with one of the two DTTRs - Data Transparent Translation Registers, of the EC040. These registers can address memory blocks no smaller than 16 MBytes. Since the first 16 MByte block on board, holds memories that are to be data-cached, the QUICC was moved to the second block. 2. Not bigger than 32K Bytes.

<sup>3.</sup> Off QUICC.

#### Fremssale Semiganductor, Minga

push-button - SW1, HARD - reset is generated to board. Indication for the occurrence of that interrupt is concluded from the absence of both Host NMI and Hardware-Breakpoint indications in the status register.

#### 4.3.2 Host - NMI

When a host is connected to the M68360QUADS-040 via the ADI port, it is possible for the host to generate a level - 7 interrupt via the ADI port, allowing for full<sup>1</sup> remote control over the board. To generate that interrupt, the host computer needs to assert and deassert the ADS\_BRK signal of the ADI port. That interrupt is indicated via the H\_NMI~ bit in the status register.

#### 4.3.3 Hardware-Breakpoint Interrupt<sup>2</sup>

To support Hardware-Breakpoint, the BKPTO~ signal of the QUICC may be connected via jumper - J7 (1-2) to the level - 7 interrupt generation logic. When a Hardware Breakpoint is reached and J7 pins 2-3 are connected, a level - 7 interrupt is generated, and the indication is shown by the BKINT~ bit in the status register.

#### 4.3.4 Parity<sup>3</sup> Error Interrupt

It is possible to generate a level - 5, maskable interrupt to the EC040 in case a parity error occurs during dram or bursting sram read. The QUICC's PERR~ (Parity Error) signal is connected to IRQ5~ signal of the QUICC.

#### 4.3.5 Host Request / Acknowledge Interrupt<sup>4</sup>

To support interrup based handshaking with the host computer via the ADI port, it is possible for the assertion (by the host computer) of either HOST\_REQ or HOST\_ACK signals, when the board is selected, to generate a level 2, maskable interrupt to the EC040.

#### 4.4 Bus Arbitration

When a QUICC is configured in 68EC040 companion mode, its arbiter lines do not change function and the QUICC remainsbus arbiter (rather than a requester as in other slave modes). The 68EC040 arbitration lines are connected gluelessly to those of the QUICC. The LOCK~ signal of the 68EC040 is connected also to support indivisible bus cycles.

When the QUICC doesn't need the bus, it asserts BG~ constantly for the 040 to reduce arbitration overhead time for the 040, and therefore improving its performance. To support external master connection via the expansion connectors, the BR\* BG\* pairs are connected to each other via jumpers and appear also at the expansion connector, thus enabling an external arbitration be located off-board. The arbitration logic scheme is demonstrated in FIGURE 4-1 on page 29.

<sup>1.</sup> In conjunction with remote SOFT & HARD resets capability.

<sup>2.</sup> It is important to remember that the Hardware-Breakpoint and the memory caching shield operation is MUTUALY EXCLUSIVE, that is, when the data-caching shield is operating (J7 2-3) the Hardware - Breakpoint use is not available and vice-versa.

<sup>3.</sup> Parity in not enabled during normal operation. It is up to the users to enable the parity logic to their desire.

<sup>4.</sup> During normal operation these interrupts are masked and a polling handshake takes place between the board and the host computer.

#### FIGURE 4-1 Arbitration Scheme:

Since the level of priority associated with the BR~ input is lower (8) than the SDMA's, no use is done with the BCLRO~ signal of the QUICC is not used. In sake of simplicity, no use is done with the IPEND~ is not used as a BCLI~ for the QUICC.

#### 4.5 System Utilities

The slave QUICC provides the M68360QUADS-040 with the following system utilities, usually provided by external logic:

- 1. Breakpoint generation

- 2. Bus Monitor (also known as hardware watch-dog)

- 3. Spurious Interrupt Monitor

- 4. Software watch-dog

- 5. Periodic Interval Timer (also known as real-time-clock or tic-timer)

#### 4.5.1 Breakpoints Generator

The QUICC may be used as a hardware breakpoint generator for the 68EC040. When the 68EC040 initiates a bus cycle by asserting TS~, the breakpoint logic compares the cycle's address to the address in the BKAR and to the access attributes in the BKCR. If there is a match, the BKPTO\* signal is asserted by the QUICC. Since TS~ is asserted only at the beginning of the cycle, no address comparison is done for the rest of the access (burst access). The BKPTO\* of the slave QUICC is wired via a jumper to generate a non-maskable interrupt on level 7.

If the EC040 performs a breakpoint instruction, the QUICC will not respond, letting the bus monitor terminate the cycle with TEA~.

#### 4.5.2 Bus Monitor

The QUICC monitors for unterminated bus cycles, performed either by the 68EC040 or by the QUICC's internal masters. If a bus cycle fails to terminate with TA~ or TEA~ (DSACK~ or BERR) during a programmable period of time, the bus monitor terminates the cycle, by asserting TEA~ for the EC040 (or BERR~ for an internal master). Upon reset, the bus monitor is initialized to expire after 1K system clocks (CLKO1 clocks).

#### 4.5.3 Spurious Interrupt Monitor

In EC040 mode, the QUICC monitors for spurious interrupt cycles performed by the EC040. This support is limited to those levels supported internally by the QUICC interrupter, i.e., only on those levels used by the CPM and the SIM60. If such a condition occurs, the QUICC terminates the cycle with TEA~.

#### 4.5.4 software Watch-Dog

The software watch-dog on the M68360QUADS-040 may be programmed to generate a system reset when an application software is stuck in an endless loop. The software watch dog is disabled after reset and it may be enabled if the users want it enabled.

#### 4.5.5 Periodic Interval Timer - PIT

If desired, the QUICC's PIT may be used to generate periodic interrupt in favor of real-time kernel. The PIT is disabled after reset.

#### 4.6 Clock Generator

There are two main clocks available on the M68360QUADS-040:

- 1. 25Mhz system clock, which supplies BCLK for the EC040 and EXTAL clock input for the QUICC. This clock is supplied via four buffers to the different board area.

- 50Mhz clock, which supplies the PCLK for the EC040 and is generated using the QUICC's PLL via CLKO2. During reset, CLKO2 reflects the state of the EXTAL input and becomes 2 X EXTAL after the QUICC's PLL is locked.

The 25Mhz clock is generated by an external crystal oscillator (U37) which is divided by 2 to yield a 50% duty cycle (U39) which is buffered (U38) and distributed to all board consumers.

#### 4.7 Flash PROM

The Flash PROM on the M68360QUADS-040 is constructed of four Am29F010-12 devices providing a total of 512 KBytes. The Am29F010 is a 5 V programmable, with 8 - sectors' protection capability, 120 nsec access time, 128 KByte device, accessed with 3 wait-states @ 25 Mhz system clock. An option is made to use bigger Flash PROMs up to the Am29F040. The Flash PROM is used to store the resident debugger and other necessary drivers, which reside in 4 protected sectors. The rest of the sectors are available for on-board user programming. The Flash PROM is selected using the Global CS (CS0) of the slave QUICC.

To program the Flash PROM, the program (and / or data) should be downloaded to the DRAM (or BSRAM) and then programmed into the Flash Prom by a dedicated debugger command. If a dedicated programming routine is to be used it is important to remember that the Flash Prom can NOT be accessed normally during the programming process. Therefore, the programming routine should reside in another memory.

#### 4.8 Bursting SRAM

The bursting sram on the M68360QUADS-040 is constructed of two<sup>1</sup> banks, each containing 4 MCM62940AFN12 32K X 9SRAM chips. This RAM provides fast access times for the EC040: 3,1,1,1 clock cycles for burst access and 3 clock cycles for normal access.

If desired, the volume of the BSRAM may be doubled, this, by soldering identical memory components to the empty locations designated by U27, U28, U29 & U30.

30

<sup>1.</sup> One populated and the other optional

#### Fremssale Semiconductor, Mina

FUNCTIONAL DESCRIPTION

#### WARNNING

Additional BSRAM components should be soldered with care. Otherwise permanent damage may be inflicted to the M68360QUADS-040.

The bursting sram may be accessed by both the EC040 and the DMA, however access by the QUICC must be **EVEN WORD** aligned.

#### 4.9 EEPROM

The EEPROM used in the M68360QUADS-040 is Motorola MCM2814, 256 byte serial EEPROM (U14). The slave QUICC provides 4 signals to control accesses to the EEPROM.

The MCM2814 has internal hardware protection against inadvertent writes to the EEPROM that might happen at power up or power down time.

#### <u>4.10</u> DRAM

The M68360QUADS-040 is supplied with 1 Mbyte of Dynamic RAM, which is implemented by the MCM36256S-60 DRAM module. The module is a 72 lead SIMM, 60 nsec access time, organized as 256K x 36 bit for data and parity signals, and is accessed with 3,2,2,2 clock cycles during burst cycles and 3 clocks during normal read / write access.