#### **Features**

- Single Voltage Read/Write Operation: 2.65V to 3.6V

- Access Time 70 ns

- Sector Erase Architecture

- Sixty-three 32K Word (64K Bytes) Sectors with Individual Write Lockout

- Eight 4K Word (8K Bytes) Sectors with Individual Write Lockout

- Fast Word Program Time 10 μs

- Fast Sector Erase Time 100 ms

- Suspend/Resume Feature for Erase and Program

- Supports Reading and Programming from Any Sector by Suspending Erase of a Different Sector

- Supports Reading Any Word by Suspending Programming of Any Other Word

- Low-power Operation

- 10 mA Active

- 15 µA Standby

- VPP Pin for Write Protection and Accelerated Program Operation

- WP Pin for Sector Protection

- RESET Input for Device Initialization

- Flexible Sector Protection

- TSOP and CBGA Package Options

- Top or Bottom Boot Block Configuration Available

- 128-bit Protection Register

- Minimum 100,000 Erase Cycles

- Common Flash Interface (CFI)

- Green (Pb/Halide-free) Packaging

### 1. Description

The AT49BV320D(T) is a 2.7-volt 32-megabit Flash memory organized as 2,097,152 words of 16 bits each. The memory is divided into 71 sectors for erase operations. The device is offered in a 48-lead TSOP package and a 47-ball CBGA package. The device has  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  control signals to avoid any bus contention. This device can be read or reprogrammed using a single power supply, making it ideally suited for in-system programming.

The device powers on in the read mode. Command sequences are used to place the device in other operation modes such as program and erase. The device has the capability to protect the data in any sector (see "Flexible Sector Protection" on page 6).

To increase the flexibility of the device, it contains an Erase Suspend and Program Suspend feature. This feature will put the erase or program on hold for any amount of time and let the user read data from or program data to any of the remaining sectors within the memory.

The VPP pin provides data protection. When the  $V_{PP}$  input is below 0.4V, the program and erase functions are inhibited. When  $V_{PP}$  is at 1.65V or above, normal program and erase operations can be performed. With  $V_{PP}$  at 10.0V, the program (Dual-word Program command) operation is accelerated.

32-megabit (2M x 16) 3-volt Only Flash Memory

AT49BV320D AT49BV320DT

#### 21. Command Definition Table

|                                     | Bus    |      | Bus<br>/cle | 2nd<br>Cy           |                                 | 3rd  <br>Cyc |                  |

|-------------------------------------|--------|------|-------------|---------------------|---------------------------------|--------------|------------------|

| Command Sequence                    | Cycles | Addr | Data        | Addr                | Data                            | Addr         | Data             |

| Read                                | 1      | XX   | FF          |                     |                                 |              |                  |

| Sector Erase/Confirm                | 2      | XX   | 20          | SA <sup>(2)</sup>   | D0                              |              |                  |

| Word Program                        | 2      | XX   | 40/10       | Addr                | D <sub>IN</sub>                 |              |                  |

| Dual-word Program <sup>(3)</sup>    | 3      | XX   | E0          | Addr0               | D <sub>INO</sub>                | Addr1        | D <sub>IN1</sub> |

| Erase/Program Suspend               | 1      | XX   | В0          |                     |                                 |              |                  |

| Erase/Program Resume                | 1      | XX   | D0          |                     |                                 |              |                  |

| Product ID Entry                    | 1      | XX   | 90          |                     |                                 |              |                  |

| Sector Softlock                     | 2      | XX   | 60          | SA <sup>(2)</sup>   | 01                              |              |                  |

| Sector Hardlock                     | 2      | XX   | 60          | SA <sup>(2)</sup>   | 2F                              |              |                  |

| Sector Unlock                       | 2      | XX   | 60          | SA <sup>(2)</sup>   | D0                              |              |                  |

| Read Status Register                | 2      | XX   | 70          | XX                  | D <sub>OUT</sub> <sup>(4)</sup> |              |                  |

| Clear Status Register               | 1      | XX   | 50          |                     |                                 |              |                  |

| Program Protection Register         | 2      | XX   | C0          | Addr <sup>(5)</sup> | D <sub>IN</sub>                 |              |                  |

| Lock Protection Register – Sector B | 2      | XX   | C0          | 80                  | FFFD                            |              |                  |

| Status of Sector B Protection       | 2      | XX   | 90          | 80                  | D <sub>OUT</sub> <sup>(6)</sup> |              |                  |

| CFI Query                           | 1      | XX   | 98          |                     |                                 |              |                  |

- Notes: 1. The DATA FORMAT shown for each bus cycle is as follows; I/O7 I/O0 (Hex). I/O15 I/O8 are don't care. The ADDRESS FORMAT shown for each bus cycle is as follows: A7 - A0 (Hex). Address A20 through A8 are don't care.

- 2. SA = sector address. Any word address within a sector can be used to designate the sector address (see pages 17 20 for details).

- 3. This fast programming option enables the user to program two words in parallel only when  $V_{PP} = 9.5V$ . The addresses, Addr0 and Addr1, of the two words, D<sub>IN0</sub> and D<sub>IN1</sub>, must only differ in address A0. This command should be used during manufacturing purposes only.

- 4. The status register bits are output on I/O7 I/O0.

- 5. Any addresses within the user programmable protection register region. Address locations are shown on "Protection Register Addressing Table" on page 16.

- 6. If data bit D1 is "0", sector B is locked. If data bit D1 is "1", sector B can be reprogrammed.

### 22. Absolute Maximum Ratings\*

|                                                                     | <u> </u>                       |

|---------------------------------------------------------------------|--------------------------------|

| Temperature under Bias                                              | 55°C to +125°C                 |

| Storage Temperature                                                 | 65°C to +150°C                 |

| All Input Voltages<br>(including NC Pins)<br>with Respect to Ground | 0.6V to +6.25V                 |

| All Output Voltages with Respect to Ground                          | 0.6V to V <sub>CC</sub> + 0.6V |

| Voltage on V <sub>PP</sub> with Respect to Ground                   | 0.6V to +10.0V                 |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 26. DC and AC Operating Range

|                              | AT49BV320D(T)-70 |               |

|------------------------------|------------------|---------------|

| Operating Temperature (Case) | Ind.             | -40°C - 85°C  |

| V <sub>CC</sub> Power Supply | •                | 2.65V to 3.6V |

#### 27. Operating Modes

| Mode                         | CE              | ŌĒ               | WE              | RESET           | V <sub>PP</sub> <sup>(1)</sup>   | Ai                                                | I/O                              |

|------------------------------|-----------------|------------------|-----------------|-----------------|----------------------------------|---------------------------------------------------|----------------------------------|

| Read                         | V <sub>IL</sub> | $V_{IL}$         | V <sub>IH</sub> | V <sub>IH</sub> | X <sup>(2)</sup>                 | Ai                                                | D <sub>OUT</sub>                 |

| Program/Erase <sup>(3)</sup> | V <sub>IL</sub> | $V_{IH}$         | $V_{IL}$        | V <sub>IH</sub> | V <sub>IHPP</sub> <sup>(4)</sup> | Ai                                                | D <sub>IN</sub>                  |

| Standby/Program Inhibit      | V <sub>IH</sub> | X <sup>(2)</sup> | Х               | V <sub>IH</sub> | Х                                | X                                                 | High-Z                           |

|                              | Х               | Х                | V <sub>IH</sub> | V <sub>IH</sub> | Х                                |                                                   |                                  |

| Program Inhibit              | Х               | V <sub>IL</sub>  | Х               | V <sub>IH</sub> | Х                                |                                                   |                                  |

|                              | Х               | Х                | Х               | V <sub>IH</sub> | V <sub>ILPP</sub> <sup>(5)</sup> |                                                   |                                  |

| Output Disable               | Х               | $V_{IH}$         | Х               | V <sub>IH</sub> | Х                                |                                                   | High-Z                           |

| Reset                        | Х               | Х                | Х               | V <sub>IL</sub> | Х                                | Х                                                 | High-Z                           |

| Product Identification       |                 |                  |                 |                 |                                  | A0 = V <sub>IL</sub> , A1 - A20 = V <sub>IL</sub> | Manufacturer Code <sup>(6)</sup> |

| Software                     |                 |                  |                 | V <sub>IH</sub> |                                  | $A0 = V_{IH}, A1 - A20 = V_{IL}$                  | Device Code <sup>(6)</sup>       |

Notes: 1. The VPP pin can be tied to  $V_{CC}$ . For faster program operations,  $V_{PP}$  can be set to 9.5V  $\pm$  0.5V.

- X can be V<sub>IL</sub> or V<sub>IH</sub>.

Refer to AC programming waveforms on page 26.

- 4.  $V_{IHPP}$  (min) = 1.65V.

- 5.  $V_{ILPP}$  (max) = 0.4V.

- 6. Manufacturer Code: 001FH, Device Code: 90C5H AT49BV320D; 90C4H AT49BV320DT

### 28. DC Characteristics

| Symbol              | Parameter                            | Condition                                                                     | Min                    | Тур | Max  | Units |

|---------------------|--------------------------------------|-------------------------------------------------------------------------------|------------------------|-----|------|-------|

| ILI                 | Input Load Current                   | $V_{IN} = 0V \text{ to } V_{CC}$                                              |                        |     | 2    | μΑ    |

| I <sub>LO</sub>     | Output Leakage Current               | $V_{I/O} = 0V \text{ to } V_{CC}$                                             |                        |     | 2    | μΑ    |

| I <sub>SB</sub>     | V <sub>CC</sub> Standby Current CMOS | $\overline{\text{CE}} = \text{V}_{\text{CC}} - 0.3 \text{V to V}_{\text{CC}}$ |                        | 15  | 25   | μA    |

| I <sub>CC</sub> (1) | V <sub>CC</sub> Active Read Current  | f = 5 MHz; I <sub>OUT</sub> = 0 mA                                            |                        | 10  | 15   | mA    |

| I <sub>CC1</sub>    | V <sub>CC</sub> Programming Current  |                                                                               |                        |     | 25   | mA    |

| I <sub>PP1</sub>    | V <sub>PP</sub> Input Load Current   |                                                                               |                        |     | 10   | μΑ    |

| V <sub>IL</sub>     | Input Low Voltage                    |                                                                               |                        |     | 0.6  | V     |

| V <sub>IH</sub>     | Input High Voltage                   |                                                                               | V <sub>CCQ</sub> - 0.6 |     |      | V     |

| V <sub>OL</sub>     | Output Low Voltage                   | I <sub>OL</sub> = 2.1 mA                                                      |                        |     | 0.45 | V     |

| V <sub>OH</sub>     | Output High Voltage                  | I <sub>OH</sub> = -100 μA                                                     | V <sub>CCQ</sub> - 0.1 |     |      | V     |

Note: 1. In the erase mode,  $I_{CC}$  is 25 mA.

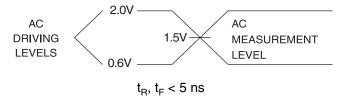

# 29. Input Test Waveforms and Measurement Level

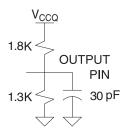

# 30. Output Test Load

# 31. Pin Capacitance

$f = 1 \text{ MHz}, T = 25^{\circ}C^{(1)}$

| Symbol           | Тур | Max | Units | Conditions     |

|------------------|-----|-----|-------|----------------|

| C <sub>IN</sub>  | 4   | 6   | pF    | $V_{IN} = 0V$  |

| C <sub>OUT</sub> | 8   | 12  | pF    | $V_{OUT} = 0V$ |

Note: This parameter is characterized and is not 100% tested.

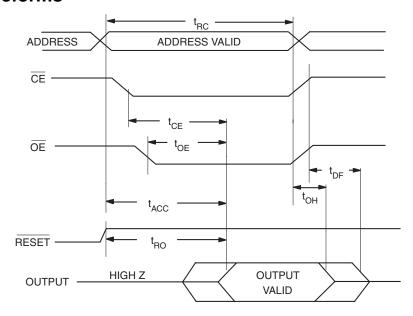

#### 32. AC Read Characteristics

|                                   |                                                                                         | AT49BV3 | AT49BV320D(T)-70 |       |

|-----------------------------------|-----------------------------------------------------------------------------------------|---------|------------------|-------|

| Symbol                            | Parameter                                                                               | Min     | Max              | Units |

| t <sub>RC</sub>                   | Read Cycle Time                                                                         | 70      |                  | ns    |

| t <sub>ACC</sub>                  | Address to Output Delay                                                                 |         | 70               | ns    |

| t <sub>CE</sub> <sup>(1)</sup>    | CE to Output Delay                                                                      |         | 70               | ns    |

| t <sub>OE</sub> <sup>(2)</sup>    | OE to Output Delay                                                                      | 0       | 20               | ns    |

| t <sub>DF</sub> <sup>(3)(4)</sup> | CE or OE to Output Float                                                                | 0       | 25               | ns    |

| t <sub>OH</sub>                   | Output Hold from $\overline{OE}$ , $\overline{CE}$ or Address, whichever occurred first | 0       |                  | ns    |

| t <sub>RO</sub>                   | RESET to Output Delay                                                                   |         | 100              | ns    |

# 33. AC Read Waveforms $^{(1)(2)(3)(4)}$

- Notes: 1.  $\overline{CE}$  may be delayed up to  $t_{ACC}$   $t_{CE}$  after the address transition without impact on  $t_{ACC}$ .

2.  $\overline{OE}$  may be delayed up to  $t_{CE}$   $t_{OE}$  after the falling edge of  $\overline{CE}$  without impact on  $t_{CE}$  or by  $t_{ACC}$   $t_{OE}$  after an address change without impact on  $t_{ACC}$ .

3.  $t_{DF}$  is specified from  $\overline{OE}$  or  $\overline{CE}$ , whichever occurs first (CL = 5 pF).

- 4. This parameter is characterized and is not 100% tested.

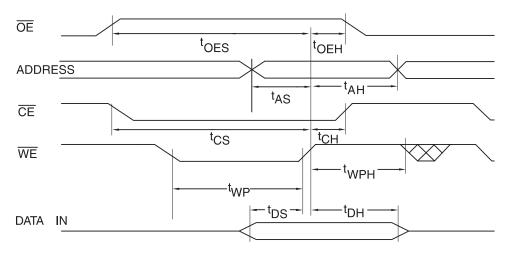

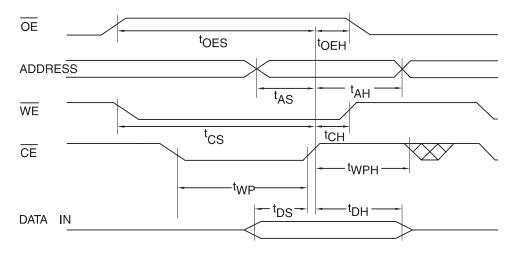

#### 34. AC Word Load Characteristics

| Symbol                             | Parameter                              | Min | Max | Units |

|------------------------------------|----------------------------------------|-----|-----|-------|

| t <sub>AS</sub> , t <sub>OES</sub> | Address, OE Setup Time                 | 20  |     | ns    |

| t <sub>AH</sub>                    | Address Hold Time                      | 0   |     | ns    |

| t <sub>CS</sub>                    | Chip Select Setup Time                 | 0   |     | ns    |

| t <sub>CH</sub>                    | Chip Select Hold Time                  | 0   |     | ns    |

| t <sub>WP</sub>                    | Write Pulse Width (WE or CE)           | 25  |     | ns    |

| t <sub>WPH</sub>                   | Write Pulse Width High                 | 15  |     | ns    |

| t <sub>DS</sub>                    | Data Setup Time                        | 25  |     | ns    |

| t <sub>DH</sub> , t <sub>OEH</sub> | Data, $\overline{\text{OE}}$ Hold Time | 0   |     | ns    |

#### 35. AC Word Load Waveforms

#### 35.1 WE Controlled

#### 35.2 CE Controlled

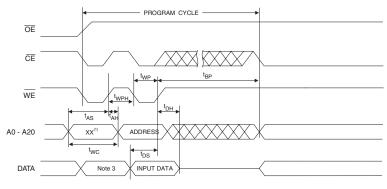

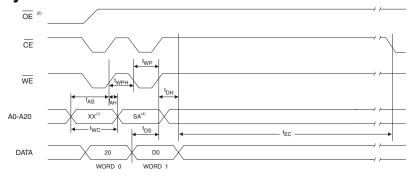

# 36. Program Cycle Characteristics

| Symbol            | Parameter                                      | Min | Тур | Max | Units   |

|-------------------|------------------------------------------------|-----|-----|-----|---------|

| t <sub>BP</sub>   | Word Programming Time                          |     | 10  | 120 | μs      |

| t <sub>BPD</sub>  | Word Programming Time in Dual Programming Mode |     | 5   | 60  | μs      |

| t <sub>AS</sub>   | Address Setup Time                             | 20  |     |     | ns      |

| t <sub>AH</sub>   | Address Hold Time                              | 0   |     |     | ns      |

| t <sub>DS</sub>   | Data Setup Time                                | 25  |     |     | ns      |

| t <sub>DH</sub>   | Data Hold Time                                 | 0   |     |     | ns      |

| t <sub>WP</sub>   | Write Pulse Width                              | 25  |     |     | ns      |

| t <sub>WPH</sub>  | Write Pulse Width High                         | 15  |     |     | ns      |

| t <sub>WC</sub>   | Write Cycle Time                               | 70  |     |     | ns      |

| t <sub>RP</sub>   | Reset Pulse Width                              | 500 |     |     | ns      |

| t <sub>SEC1</sub> | Sector Erase Cycle Time (4K Word Sectors)      |     | 0.1 | 2   | seconds |

| t <sub>SEC2</sub> | Sector Erase Cycle Time (32K Word Sectors)     |     | 0.5 | 6.0 | seconds |

| t <sub>ES</sub>   | Erase Suspend Time                             |     |     | 15  | μs      |

| t <sub>PS</sub>   | Program Suspend Time                           |     |     | 10  | μs      |

### 37. Program Cycle Waveforms

# 38. Sector Erase Cycle Waveforms

Notes: 1. Any address can be used to load the data.

- 2.  $\overline{OE}$  must be high only when  $\overline{WE}$  and  $\overline{CE}$  are both low.

- 3. The data can be 40H or 10H.

- 4. The address depends on what sector is to be erased.

# 26 AT49BV320D(T)

# 40. Ordering Information

### 40.1 Green Package (Pb/Halide-free)

| t <sub>ACC</sub>    | I <sub>CC</sub> (mA) |                                      |                                    |                | Operation Range |  |

|---------------------|----------------------|--------------------------------------|------------------------------------|----------------|-----------------|--|

| (ns) Active Standby |                      | Standby                              | Ordering Code                      | Package        |                 |  |

| 70                  | 25                   | 0.025                                | AT49BV320D-70CU<br>AT49BV320D-70TU | 47C1<br>48T    | Industrial      |  |

| 70 25 0.025         | 0.025                | AT49BV320DT-70CU<br>AT49BV320DT-70TU | 47C1<br>48T                        | (-40° to 85°C) |                 |  |

|      | Package Type                                              |  |  |  |  |

|------|-----------------------------------------------------------|--|--|--|--|

| 47C1 | 47-ball, Plastic Chip-Size Ball Grid Array Package (CBGA) |  |  |  |  |

| 48T  | 48-lead, Plastic Thin Small Outline Package (TSOP)        |  |  |  |  |

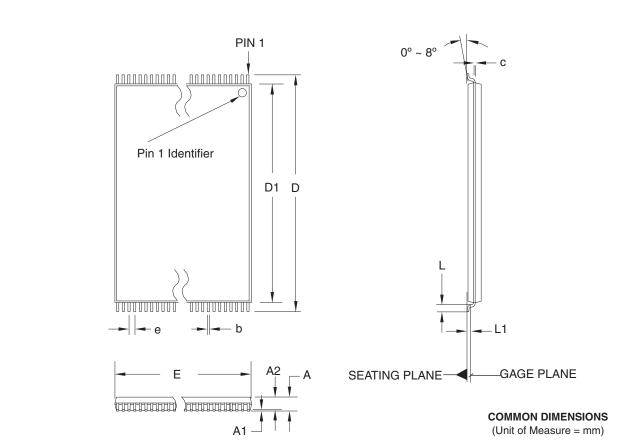

#### 41.2 48T - TSOP

Notes:

- 1. This package conforms to JEDEC reference MO-142, Variation DD.

- 2. Dimensions D1 and E do not include mold protrusion. Allowable protrusion on E is 0.15 mm per side and on D1 is 0.25 mm per side.

- 3. Lead coplanarity is 0.10 mm maximum.

| SYMBOL | MIN   | NOM       | MAX   | NOTE   |

|--------|-------|-----------|-------|--------|

| Α      | _     | _         | 1.20  |        |

| A1     | 0.05  | _         | 0.15  |        |

| A2     | 0.95  | 1.00      | 1.05  |        |

| D      | 19.80 | 20.00     | 20.20 |        |

| D1     | 18.30 | 18.40     | 18.50 | Note 2 |

| E      | 11.90 | 12.00     | 12.10 | Note 2 |

| L      | 0.50  | 0.60      | 0.70  |        |

| L1     | (     | ).25 BASI | )     |        |

| b      | 0.17  | 0.22      | 0.27  |        |

| С      | 0.10  | _         | 0.21  |        |

| е      | (     | 0.50 BASI | 0     |        |

|                              | TITLE                                       | DRAWING NO. REV.         |

|------------------------------|---------------------------------------------|--------------------------|

| 2325 Orchard<br>San Jose, CA | * 1 401 40-1630 UZ X ZU MM PACKAOEI PIASIIC | Thin Small Outline 48T B |